Professional Documents

Culture Documents

Bals3033 Logic System Design

Bals3033 Logic System Design

Uploaded by

Zhong Kiat TehCopyright:

Available Formats

You might also like

- Customer Service Module Lesson PlanDocument10 pagesCustomer Service Module Lesson PlanDavinia Botía Corral100% (3)

- Online Assessment April 2020: This Question Paper Consists of 5 Questions On 6 Printed PagesDocument6 pagesOnline Assessment April 2020: This Question Paper Consists of 5 Questions On 6 Printed PagesZhong Kiat TehNo ratings yet

- EE202QDocument7 pagesEE202QBelon Kaler Biyru IINo ratings yet

- 0910sem2 Ee4218Document7 pages0910sem2 Ee4218Atlee Young100% (1)

- DLD Ques2Document2 pagesDLD Ques2mahbub mitulNo ratings yet

- Gujarat Technological UniversityDocument4 pagesGujarat Technological UniversityParamveersinh DabhiNo ratings yet

- Southern University CollegeDocument4 pagesSouthern University CollegeZhong Kiat TehNo ratings yet

- EME4433 1217 Assignment QPDocument4 pagesEME4433 1217 Assignment QPAtif SyedNo ratings yet

- UFMFF8-30-1 Exam Paper 2016-2017Document8 pagesUFMFF8-30-1 Exam Paper 2016-2017Irfan MemonNo ratings yet

- DLD Ques5Document2 pagesDLD Ques5mahbub mitulNo ratings yet

- Apr - May 2023Document3 pagesApr - May 2023Pandyselvi BalasubramanianNo ratings yet

- Sample - Final Exam - DLDDocument5 pagesSample - Final Exam - DLDadlinarashid03No ratings yet

- 19EC303 DPSD Learners Copy 11 03 24Document56 pages19EC303 DPSD Learners Copy 11 03 24Marshmellow FFNo ratings yet

- Elec103p Exam 2015Document8 pagesElec103p Exam 2015cweqingNo ratings yet

- Bals3033 Logic System DesignDocument5 pagesBals3033 Logic System DesignZhong Kiat TehNo ratings yet

- Ect203 Scheme 2021Document9 pagesEct203 Scheme 2021ShakiraNo ratings yet

- Solution PDFDocument5 pagesSolution PDFCedric SunNo ratings yet

- APR2013P21Document63 pagesAPR2013P21qsashutoshNo ratings yet

- ELEC103P Exam 2018Document7 pagesELEC103P Exam 2018cweqingNo ratings yet

- Switching Theory and Logic DesignDocument10 pagesSwitching Theory and Logic DesignRajkumarBattuNo ratings yet

- Indian Institute of Technology (IIT) - BHU: EO-301, D C SDocument7 pagesIndian Institute of Technology (IIT) - BHU: EO-301, D C SAyush Gupta 4-Year B.Tech. Electrical EngineeringNo ratings yet

- CS3CO29-EC-EI3CO07-IT3CO09-OE00005 Digital ElectronicsDocument3 pagesCS3CO29-EC-EI3CO07-IT3CO09-OE00005 Digital Electronicschouhanraman822No ratings yet

- CSS 22531 EgDocument4 pagesCSS 22531 Egrushikarande0024No ratings yet

- Digital Electronic Circuits (ELE-208) RCSDocument2 pagesDigital Electronic Circuits (ELE-208) RCSSudhakar JoshiNo ratings yet

- DE - KOE 039 - Question BankDocument6 pagesDE - KOE 039 - Question Bankyash vatsNo ratings yet

- Ect203 Scheme 2020Document8 pagesEct203 Scheme 2020ShakiraNo ratings yet

- Semester 1 Examinations 2018/2019: Programme (S)Document6 pagesSemester 1 Examinations 2018/2019: Programme (S)fuckoffmanNo ratings yet

- Acseh0304 (DLD) 2Document5 pagesAcseh0304 (DLD) 2yt608118No ratings yet

- CT Dec 2019 v2Document6 pagesCT Dec 2019 v2muthukumaran TanujNo ratings yet

- BDA 30703 Sem 1 1213 PDFDocument7 pagesBDA 30703 Sem 1 1213 PDFJevine LaiNo ratings yet

- Digital Control Systems May 2007 Question PaperDocument8 pagesDigital Control Systems May 2007 Question Paperelimelek100% (3)

- EG2061 Electronics and ControlDocument9 pagesEG2061 Electronics and ControlTudor Octavian RusuNo ratings yet

- Second Semester Examinations 2016/2017: Answer FOUR QuestionsDocument6 pagesSecond Semester Examinations 2016/2017: Answer FOUR Questionshussein hammoudNo ratings yet

- EE234 Final Exam Fall 2023-11 - AnnotatedDocument8 pagesEE234 Final Exam Fall 2023-11 - Annotatedpizza8019No ratings yet

- DLD - Question - Final 2022Document2 pagesDLD - Question - Final 2022Md Israfil HossainNo ratings yet

- r05220403 Switching Theory and Logic DesignDocument8 pagesr05220403 Switching Theory and Logic DesignSRINIVASA RAO GANTANo ratings yet

- Sco 211 Automata TheoryDocument4 pagesSco 211 Automata TheoryCaleb kipkorirNo ratings yet

- Eee 3131 Final Exam 2022-1Document6 pagesEee 3131 Final Exam 2022-1Billy MulengaNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- See Adld 2020Document2 pagesSee Adld 20201ms21ec132No ratings yet

- En123 - SM2 2022 Department of Electrical & Communications Engineering DepartmentDocument6 pagesEn123 - SM2 2022 Department of Electrical & Communications Engineering DepartmentDavid Jnr PeraNo ratings yet

- End CS 205 - 2017Document4 pagesEnd CS 205 - 2017Chathuranga RuwanpathiranaNo ratings yet

- Question Paper Winter 2019Document3 pagesQuestion Paper Winter 2019AartiNo ratings yet

- Dlda 2Document2 pagesDlda 2Manoj NaikNo ratings yet

- L-3/T - 2/EEE Date: 28/0312022: IS) +D (I, 3,6,7)Document19 pagesL-3/T - 2/EEE Date: 28/0312022: IS) +D (I, 3,6,7)Sanjid ElahiNo ratings yet

- DLD Ques1Document2 pagesDLD Ques1mahbub mitulNo ratings yet

- STLD Regular Jntu Question Papers 2008Document9 pagesSTLD Regular Jntu Question Papers 2008anjaneyulud100% (1)

- B38DB ClassExs2sDocument33 pagesB38DB ClassExs2sNabil IshamNo ratings yet

- STLD 2009 RegularDocument4 pagesSTLD 2009 RegularrangerNo ratings yet

- United International University (UIU) : Dept. of Computer Science& Engineering (CSE)Document2 pagesUnited International University (UIU) : Dept. of Computer Science& Engineering (CSE)mahbub mitulNo ratings yet

- CSS 22531-2023-Summer-Question-Paper EGDocument4 pagesCSS 22531-2023-Summer-Question-Paper EGrushikarande0024No ratings yet

- Csi Zg518 Ec-3r First Sem 2023-2024Document8 pagesCsi Zg518 Ec-3r First Sem 2023-2024vewij82511No ratings yet

- Contest WebDocument24 pagesContest WebliwfsvleexpxwhnsnvNo ratings yet

- Mca 1 Sem Computer Organization and Architecture Kca105 2022Document1 pageMca 1 Sem Computer Organization and Architecture Kca105 2022kimog66911No ratings yet

- Birla Institute of Technology and Science, Pilani I SEMESTER 2004-05Document6 pagesBirla Institute of Technology and Science, Pilani I SEMESTER 2004-05navaneeth_kumarNo ratings yet

- Ecs-301 Digital Logic Design 2010-11Document4 pagesEcs-301 Digital Logic Design 2010-11Satyedra MauryaNo ratings yet

- Summer2022 AnnotatedDocument4 pagesSummer2022 AnnotatedSarojkumar BhosleNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- GARCH Models: Structure, Statistical Inference and Financial ApplicationsFrom EverandGARCH Models: Structure, Statistical Inference and Financial ApplicationsRating: 5 out of 5 stars5/5 (1)

- 02 - Chap 2 - AC Power Analysis - 2021CDocument68 pages02 - Chap 2 - AC Power Analysis - 2021CZhong Kiat TehNo ratings yet

- Three-Phase CircuitsDocument69 pagesThree-Phase CircuitsZhong Kiat TehNo ratings yet

- Frequency ResponseDocument97 pagesFrequency ResponseZhong Kiat TehNo ratings yet

- IRJET V5I3579 With Cover Page v2Document6 pagesIRJET V5I3579 With Cover Page v2Zhong Kiat TehNo ratings yet

- Home - Management With Cover Page v2Document10 pagesHome - Management With Cover Page v2Zhong Kiat TehNo ratings yet

- Designand Implementationofan Internetof Things Based Smart Energy MeteringDocument5 pagesDesignand Implementationofan Internetof Things Based Smart Energy MeteringZhong Kiat TehNo ratings yet

- Southern: Final Examination Semester I/Year 2019Document8 pagesSouthern: Final Examination Semester I/Year 2019Zhong Kiat TehNo ratings yet

- Online Assessment April 2020: This Question Paper Consists of 5 Questions On 6 Printed PagesDocument6 pagesOnline Assessment April 2020: This Question Paper Consists of 5 Questions On 6 Printed PagesZhong Kiat TehNo ratings yet

- Southern University CollegeDocument4 pagesSouthern University CollegeZhong Kiat TehNo ratings yet

- Chapter 6. Infiltration and VentilationDocument1 pageChapter 6. Infiltration and VentilationKarthikeyan SankarrajanNo ratings yet

- Part List 2630.180 - 2640.180Document20 pagesPart List 2630.180 - 2640.180Otoniel Cardenas100% (1)

- Training Memorandum of Agreement/Waiver: Polytechnic University of The Philippines Quezon City BranchDocument3 pagesTraining Memorandum of Agreement/Waiver: Polytechnic University of The Philippines Quezon City BranchAnton ArponNo ratings yet

- Seminar: Faizan Khan, Tobias Tritschler, Susan R Kahn, Marc A RodgerDocument14 pagesSeminar: Faizan Khan, Tobias Tritschler, Susan R Kahn, Marc A RodgerJuan Camilo Morales TabordaNo ratings yet

- RDF 027 SSBT Activity Plan Day 3 (Collision Between Paula C and Darya Gayatri) Rev 2.0Document9 pagesRDF 027 SSBT Activity Plan Day 3 (Collision Between Paula C and Darya Gayatri) Rev 2.0Kris TinaNo ratings yet

- GBP Statement: Account SummaryDocument16 pagesGBP Statement: Account SummaryKris TheVillainNo ratings yet

- Robot Welding in ShipbuildingDocument5 pagesRobot Welding in Shipbuildingvictor navarro chiletNo ratings yet

- Survey of Road DataDocument23 pagesSurvey of Road DataMuddasar AhmedNo ratings yet

- Lab Assignment 041035Document10 pagesLab Assignment 041035123fakehaNo ratings yet

- Jawaban Suzette WashingtonDocument1 pageJawaban Suzette Washingtonakmal muzamarNo ratings yet

- Digital Prescription and Disease Prediction Using Machine LearningDocument8 pagesDigital Prescription and Disease Prediction Using Machine LearningInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Honor H30-U10 V100R001C432B109 Upgrade GuidelineDocument15 pagesHonor H30-U10 V100R001C432B109 Upgrade GuidelineFahad HussainNo ratings yet

- ExerciseDocument9 pagesExerciseChi NguyễnNo ratings yet

- Spatio-Temporal Assessment of Urban Heat Island Effects in Kuala Lumpur Metropolitan City Using Landsat ImagesDocument9 pagesSpatio-Temporal Assessment of Urban Heat Island Effects in Kuala Lumpur Metropolitan City Using Landsat ImagesAshraf RamadanNo ratings yet

- Eusebio Vs EusebioDocument2 pagesEusebio Vs EusebioNC BergoniaNo ratings yet

- My CV PDFDocument2 pagesMy CV PDFAli ArslanNo ratings yet

- The Adoption of The Principles of Equity Jurisprudence Into The ADocument12 pagesThe Adoption of The Principles of Equity Jurisprudence Into The AAjinkya PatilNo ratings yet

- T TestDocument12 pagesT TestNantiwa NaulsreeNo ratings yet

- VD - Part 03 - Body DesignDocument49 pagesVD - Part 03 - Body DesignEmre DemiralpNo ratings yet

- Overview:: Factors Affecting Demand of Cadbury Products in IndiaDocument7 pagesOverview:: Factors Affecting Demand of Cadbury Products in IndiaNajish FarhanNo ratings yet

- CUENCAS Allen - Classification - 2015Document52 pagesCUENCAS Allen - Classification - 2015Camila AldereteNo ratings yet

- Rights in Land and Pattadar Pass Books Rules 1989Document42 pagesRights in Land and Pattadar Pass Books Rules 1989raju634No ratings yet

- RW E-Jet User Manual V20-2-4 RottweilDocument107 pagesRW E-Jet User Manual V20-2-4 RottweilPaulo MagalhaesNo ratings yet

- AGPU Everything-About-PVC enDocument16 pagesAGPU Everything-About-PVC enPierluigi GhioneNo ratings yet

- THE IKEA APPROACH - ViralDocument2 pagesTHE IKEA APPROACH - ViralfredrickyadavNo ratings yet

- EPR Sample PreparationDocument4 pagesEPR Sample PreparationPaulNo ratings yet

- Bolivia - Bilateral Relations: GeneralDocument11 pagesBolivia - Bilateral Relations: Generalbansalanuj24No ratings yet

- Universal Precautions in Infection PreventionDocument18 pagesUniversal Precautions in Infection PreventionadiNo ratings yet

- Fiber Glass Reinforced HDDDocument8 pagesFiber Glass Reinforced HDDGilvan SilvaNo ratings yet

Bals3033 Logic System Design

Bals3033 Logic System Design

Uploaded by

Zhong Kiat TehOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Bals3033 Logic System Design

Bals3033 Logic System Design

Uploaded by

Zhong Kiat TehCopyright:

Available Formats

SOUTHERN UNIVERSITY COLLEGE

SEMESTER C

YEAR 2020 / 2021

FINAL EXAM

BALS3033 LOGIC SYSTEM DESIGN

DATE : 20/1/2021 DURATION : 2 HOURS 30 MINUTES

BACHELOR OF ENGINEERING (HONOURS) IN ELECTRONIC ENGINEERING

YEAR THREE

Instruction to Candidates :

1. Answer ALL questions. All questions carry equal marks.

2. All answers must be written on the answer sheet with pen.

3. Begin to answer each new question on a new page.

4. Programmable and Semi-Programmable Scientific Calculators are PROHIBITED to use.

5. Return the question paper together with your answer booklet.

This question paper consists of 4 questions on 5 printed pages.

2

BALS3033 LOGIC SYSTEM DESIGN

Q1. (a) Justify why the Hardware Description Language Design is more reliable

compare to Schematic Design. (6 marks)

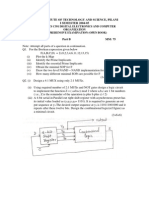

(b)

Figure 1

(i) Write the structural Verilog code for the combinational circuit shown

in Figure 1. (12 marks)

(ii) Write the behavioral Verilog code for the combinational circuit

shown in Figure 1. (7 marks)

[Total : 25 marks]

Q2. (a) Determine if there are differences if the following two modules are

synthesized. (4 marks)

module reg1(Q1,Q2,Q3,Q4,A,CLK); module reg1(Q1,Q2,Q3,Q4,A,CLK);

input A; input A;

input CLK; input CLK;

output Q1, Q2, Q3, Q4; output Q1, Q2, Q3, Q4;

reg Q1, Q2, Q3, Q4; reg Q1, Q2, Q3, Q4;

always @(posedge CLK) always @(posedge CLK)

begin begin

Q1<=A; Q4<=Q3;

Q2<=Q1; Q3<=Q2;

Q3<=Q2; Q2<=Q1;

Q4<=Q3; Q1<=A;

end end

endmodule endmodule

This question paper consists of 4 questions on 5 printed pages.

3

BALS3033 LOGIC SYSTEM DESIGN

Q2. (Continued)

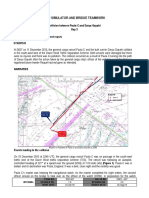

(b) A 4-to-1 multiplexer (as shown in Figure 2) has an inherent delay that causes

the change in output to occur 10ns after a change in input.

Figure 2

(i) Write a conditional signal assignment statement to represent the 4-to-1

MUX. (2 marks)

(ii) Repeat (i) using an if-else statement. (5 marks)

(iii) Repeat (i) using a case statement. (6 marks)

(c) Construct a Verilog code to implement the circuit in Figure 3. (8 marks)

X1

X2

Inpu U1 U2

T Q T Q T Q T Q

Q[0] Q[1] Q[2] Q[3]

t T0 T1 T2 T3

Clock Qbar Qbar Qbar Qbar

reset

Figure 3

[Total : 25 marks]

This question paper consists of 4 questions on 5 printed pages.

4

BALS3033 LOGIC SYSTEM DESIGN

Q3. (a) (i) Determine the state table and state diagram using a Moore system

whose output changes whenever it detects a sequence 110, as shown in

the table. Assume that initially, the output is 0.

x 0 0 1 0 1 1 1 0 1 1 0 0 1 1 0 1 0 1 - -

z 0 0 0 0 0 0 0 0 1 1 1 0 0 0 0 1 1 1 1 1

(6 marks)

(ii) Consider a sequence detector that receives a bit-serial input Y and

asserts an output Z=1 if and only if there have been exactly four 1’s

detected consequently in a row. Use symbolic states with letters such

as A, B and etc. Assume that “A” is start state, in which the machine

can start out or reset. Develop the state table by using Mealy machine

state diagram (8 marks)

(b) Figure 4 shows the Finite State Machine (FSM), where C is an input, and a

and b are output.

Figure 4

(i) Construct a next-state table for the FSM circuit. (4 marks)

(ii) Develop the next-state equations and output equations. (3 marks)

(iii) Develop the Finite State Diagram (4 marks)

[Total : 25 marks]

This question paper consists of 4 questions on 5 printed pages.

5

BALS3033 LOGIC SYSTEM DESIGN

Q4. A4 4 keypad scanner for the keypad layout is shown in Figure 5.

Figure 5

(a) Assuming only one key can be pressed at a time, interpret the equations for a

number decoder given , , , and , , , , whose output

corresponds to the binary value of the key. For example, the F key will return

1111 in binary, or 15. (5 marks)

(b) Design a debouncing circuit that detects whether a key has been pressed or

depressed. Assume switch bounce will die in one or two clock cycles/ when a

key has been pressed, K=1 and Kd is the debounced signal. (2 marks)

(c) Draw a state diagram that performs the keyscan and issues a valid pulse when

a valid key has been pressed using inputs from (b). (4 marks)

(d) Write a Verilog code for your keypad scanner and include the decoder, the

debouncing circuit, and the scanner. (14 marks)

[Total : 25 marks]

________________________________________

This question paper consists of 4 questions on 5 printed pages.

You might also like

- Customer Service Module Lesson PlanDocument10 pagesCustomer Service Module Lesson PlanDavinia Botía Corral100% (3)

- Online Assessment April 2020: This Question Paper Consists of 5 Questions On 6 Printed PagesDocument6 pagesOnline Assessment April 2020: This Question Paper Consists of 5 Questions On 6 Printed PagesZhong Kiat TehNo ratings yet

- EE202QDocument7 pagesEE202QBelon Kaler Biyru IINo ratings yet

- 0910sem2 Ee4218Document7 pages0910sem2 Ee4218Atlee Young100% (1)

- DLD Ques2Document2 pagesDLD Ques2mahbub mitulNo ratings yet

- Gujarat Technological UniversityDocument4 pagesGujarat Technological UniversityParamveersinh DabhiNo ratings yet

- Southern University CollegeDocument4 pagesSouthern University CollegeZhong Kiat TehNo ratings yet

- EME4433 1217 Assignment QPDocument4 pagesEME4433 1217 Assignment QPAtif SyedNo ratings yet

- UFMFF8-30-1 Exam Paper 2016-2017Document8 pagesUFMFF8-30-1 Exam Paper 2016-2017Irfan MemonNo ratings yet

- DLD Ques5Document2 pagesDLD Ques5mahbub mitulNo ratings yet

- Apr - May 2023Document3 pagesApr - May 2023Pandyselvi BalasubramanianNo ratings yet

- Sample - Final Exam - DLDDocument5 pagesSample - Final Exam - DLDadlinarashid03No ratings yet

- 19EC303 DPSD Learners Copy 11 03 24Document56 pages19EC303 DPSD Learners Copy 11 03 24Marshmellow FFNo ratings yet

- Elec103p Exam 2015Document8 pagesElec103p Exam 2015cweqingNo ratings yet

- Bals3033 Logic System DesignDocument5 pagesBals3033 Logic System DesignZhong Kiat TehNo ratings yet

- Ect203 Scheme 2021Document9 pagesEct203 Scheme 2021ShakiraNo ratings yet

- Solution PDFDocument5 pagesSolution PDFCedric SunNo ratings yet

- APR2013P21Document63 pagesAPR2013P21qsashutoshNo ratings yet

- ELEC103P Exam 2018Document7 pagesELEC103P Exam 2018cweqingNo ratings yet

- Switching Theory and Logic DesignDocument10 pagesSwitching Theory and Logic DesignRajkumarBattuNo ratings yet

- Indian Institute of Technology (IIT) - BHU: EO-301, D C SDocument7 pagesIndian Institute of Technology (IIT) - BHU: EO-301, D C SAyush Gupta 4-Year B.Tech. Electrical EngineeringNo ratings yet

- CS3CO29-EC-EI3CO07-IT3CO09-OE00005 Digital ElectronicsDocument3 pagesCS3CO29-EC-EI3CO07-IT3CO09-OE00005 Digital Electronicschouhanraman822No ratings yet

- CSS 22531 EgDocument4 pagesCSS 22531 Egrushikarande0024No ratings yet

- Digital Electronic Circuits (ELE-208) RCSDocument2 pagesDigital Electronic Circuits (ELE-208) RCSSudhakar JoshiNo ratings yet

- DE - KOE 039 - Question BankDocument6 pagesDE - KOE 039 - Question Bankyash vatsNo ratings yet

- Ect203 Scheme 2020Document8 pagesEct203 Scheme 2020ShakiraNo ratings yet

- Semester 1 Examinations 2018/2019: Programme (S)Document6 pagesSemester 1 Examinations 2018/2019: Programme (S)fuckoffmanNo ratings yet

- Acseh0304 (DLD) 2Document5 pagesAcseh0304 (DLD) 2yt608118No ratings yet

- CT Dec 2019 v2Document6 pagesCT Dec 2019 v2muthukumaran TanujNo ratings yet

- BDA 30703 Sem 1 1213 PDFDocument7 pagesBDA 30703 Sem 1 1213 PDFJevine LaiNo ratings yet

- Digital Control Systems May 2007 Question PaperDocument8 pagesDigital Control Systems May 2007 Question Paperelimelek100% (3)

- EG2061 Electronics and ControlDocument9 pagesEG2061 Electronics and ControlTudor Octavian RusuNo ratings yet

- Second Semester Examinations 2016/2017: Answer FOUR QuestionsDocument6 pagesSecond Semester Examinations 2016/2017: Answer FOUR Questionshussein hammoudNo ratings yet

- EE234 Final Exam Fall 2023-11 - AnnotatedDocument8 pagesEE234 Final Exam Fall 2023-11 - Annotatedpizza8019No ratings yet

- DLD - Question - Final 2022Document2 pagesDLD - Question - Final 2022Md Israfil HossainNo ratings yet

- r05220403 Switching Theory and Logic DesignDocument8 pagesr05220403 Switching Theory and Logic DesignSRINIVASA RAO GANTANo ratings yet

- Sco 211 Automata TheoryDocument4 pagesSco 211 Automata TheoryCaleb kipkorirNo ratings yet

- Eee 3131 Final Exam 2022-1Document6 pagesEee 3131 Final Exam 2022-1Billy MulengaNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- See Adld 2020Document2 pagesSee Adld 20201ms21ec132No ratings yet

- En123 - SM2 2022 Department of Electrical & Communications Engineering DepartmentDocument6 pagesEn123 - SM2 2022 Department of Electrical & Communications Engineering DepartmentDavid Jnr PeraNo ratings yet

- End CS 205 - 2017Document4 pagesEnd CS 205 - 2017Chathuranga RuwanpathiranaNo ratings yet

- Question Paper Winter 2019Document3 pagesQuestion Paper Winter 2019AartiNo ratings yet

- Dlda 2Document2 pagesDlda 2Manoj NaikNo ratings yet

- L-3/T - 2/EEE Date: 28/0312022: IS) +D (I, 3,6,7)Document19 pagesL-3/T - 2/EEE Date: 28/0312022: IS) +D (I, 3,6,7)Sanjid ElahiNo ratings yet

- DLD Ques1Document2 pagesDLD Ques1mahbub mitulNo ratings yet

- STLD Regular Jntu Question Papers 2008Document9 pagesSTLD Regular Jntu Question Papers 2008anjaneyulud100% (1)

- B38DB ClassExs2sDocument33 pagesB38DB ClassExs2sNabil IshamNo ratings yet

- STLD 2009 RegularDocument4 pagesSTLD 2009 RegularrangerNo ratings yet

- United International University (UIU) : Dept. of Computer Science& Engineering (CSE)Document2 pagesUnited International University (UIU) : Dept. of Computer Science& Engineering (CSE)mahbub mitulNo ratings yet

- CSS 22531-2023-Summer-Question-Paper EGDocument4 pagesCSS 22531-2023-Summer-Question-Paper EGrushikarande0024No ratings yet

- Csi Zg518 Ec-3r First Sem 2023-2024Document8 pagesCsi Zg518 Ec-3r First Sem 2023-2024vewij82511No ratings yet

- Contest WebDocument24 pagesContest WebliwfsvleexpxwhnsnvNo ratings yet

- Mca 1 Sem Computer Organization and Architecture Kca105 2022Document1 pageMca 1 Sem Computer Organization and Architecture Kca105 2022kimog66911No ratings yet

- Birla Institute of Technology and Science, Pilani I SEMESTER 2004-05Document6 pagesBirla Institute of Technology and Science, Pilani I SEMESTER 2004-05navaneeth_kumarNo ratings yet

- Ecs-301 Digital Logic Design 2010-11Document4 pagesEcs-301 Digital Logic Design 2010-11Satyedra MauryaNo ratings yet

- Summer2022 AnnotatedDocument4 pagesSummer2022 AnnotatedSarojkumar BhosleNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- GARCH Models: Structure, Statistical Inference and Financial ApplicationsFrom EverandGARCH Models: Structure, Statistical Inference and Financial ApplicationsRating: 5 out of 5 stars5/5 (1)

- 02 - Chap 2 - AC Power Analysis - 2021CDocument68 pages02 - Chap 2 - AC Power Analysis - 2021CZhong Kiat TehNo ratings yet

- Three-Phase CircuitsDocument69 pagesThree-Phase CircuitsZhong Kiat TehNo ratings yet

- Frequency ResponseDocument97 pagesFrequency ResponseZhong Kiat TehNo ratings yet

- IRJET V5I3579 With Cover Page v2Document6 pagesIRJET V5I3579 With Cover Page v2Zhong Kiat TehNo ratings yet

- Home - Management With Cover Page v2Document10 pagesHome - Management With Cover Page v2Zhong Kiat TehNo ratings yet

- Designand Implementationofan Internetof Things Based Smart Energy MeteringDocument5 pagesDesignand Implementationofan Internetof Things Based Smart Energy MeteringZhong Kiat TehNo ratings yet

- Southern: Final Examination Semester I/Year 2019Document8 pagesSouthern: Final Examination Semester I/Year 2019Zhong Kiat TehNo ratings yet

- Online Assessment April 2020: This Question Paper Consists of 5 Questions On 6 Printed PagesDocument6 pagesOnline Assessment April 2020: This Question Paper Consists of 5 Questions On 6 Printed PagesZhong Kiat TehNo ratings yet

- Southern University CollegeDocument4 pagesSouthern University CollegeZhong Kiat TehNo ratings yet

- Chapter 6. Infiltration and VentilationDocument1 pageChapter 6. Infiltration and VentilationKarthikeyan SankarrajanNo ratings yet

- Part List 2630.180 - 2640.180Document20 pagesPart List 2630.180 - 2640.180Otoniel Cardenas100% (1)

- Training Memorandum of Agreement/Waiver: Polytechnic University of The Philippines Quezon City BranchDocument3 pagesTraining Memorandum of Agreement/Waiver: Polytechnic University of The Philippines Quezon City BranchAnton ArponNo ratings yet

- Seminar: Faizan Khan, Tobias Tritschler, Susan R Kahn, Marc A RodgerDocument14 pagesSeminar: Faizan Khan, Tobias Tritschler, Susan R Kahn, Marc A RodgerJuan Camilo Morales TabordaNo ratings yet

- RDF 027 SSBT Activity Plan Day 3 (Collision Between Paula C and Darya Gayatri) Rev 2.0Document9 pagesRDF 027 SSBT Activity Plan Day 3 (Collision Between Paula C and Darya Gayatri) Rev 2.0Kris TinaNo ratings yet

- GBP Statement: Account SummaryDocument16 pagesGBP Statement: Account SummaryKris TheVillainNo ratings yet

- Robot Welding in ShipbuildingDocument5 pagesRobot Welding in Shipbuildingvictor navarro chiletNo ratings yet

- Survey of Road DataDocument23 pagesSurvey of Road DataMuddasar AhmedNo ratings yet

- Lab Assignment 041035Document10 pagesLab Assignment 041035123fakehaNo ratings yet

- Jawaban Suzette WashingtonDocument1 pageJawaban Suzette Washingtonakmal muzamarNo ratings yet

- Digital Prescription and Disease Prediction Using Machine LearningDocument8 pagesDigital Prescription and Disease Prediction Using Machine LearningInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Honor H30-U10 V100R001C432B109 Upgrade GuidelineDocument15 pagesHonor H30-U10 V100R001C432B109 Upgrade GuidelineFahad HussainNo ratings yet

- ExerciseDocument9 pagesExerciseChi NguyễnNo ratings yet

- Spatio-Temporal Assessment of Urban Heat Island Effects in Kuala Lumpur Metropolitan City Using Landsat ImagesDocument9 pagesSpatio-Temporal Assessment of Urban Heat Island Effects in Kuala Lumpur Metropolitan City Using Landsat ImagesAshraf RamadanNo ratings yet

- Eusebio Vs EusebioDocument2 pagesEusebio Vs EusebioNC BergoniaNo ratings yet

- My CV PDFDocument2 pagesMy CV PDFAli ArslanNo ratings yet

- The Adoption of The Principles of Equity Jurisprudence Into The ADocument12 pagesThe Adoption of The Principles of Equity Jurisprudence Into The AAjinkya PatilNo ratings yet

- T TestDocument12 pagesT TestNantiwa NaulsreeNo ratings yet

- VD - Part 03 - Body DesignDocument49 pagesVD - Part 03 - Body DesignEmre DemiralpNo ratings yet

- Overview:: Factors Affecting Demand of Cadbury Products in IndiaDocument7 pagesOverview:: Factors Affecting Demand of Cadbury Products in IndiaNajish FarhanNo ratings yet

- CUENCAS Allen - Classification - 2015Document52 pagesCUENCAS Allen - Classification - 2015Camila AldereteNo ratings yet

- Rights in Land and Pattadar Pass Books Rules 1989Document42 pagesRights in Land and Pattadar Pass Books Rules 1989raju634No ratings yet

- RW E-Jet User Manual V20-2-4 RottweilDocument107 pagesRW E-Jet User Manual V20-2-4 RottweilPaulo MagalhaesNo ratings yet

- AGPU Everything-About-PVC enDocument16 pagesAGPU Everything-About-PVC enPierluigi GhioneNo ratings yet

- THE IKEA APPROACH - ViralDocument2 pagesTHE IKEA APPROACH - ViralfredrickyadavNo ratings yet

- EPR Sample PreparationDocument4 pagesEPR Sample PreparationPaulNo ratings yet

- Bolivia - Bilateral Relations: GeneralDocument11 pagesBolivia - Bilateral Relations: Generalbansalanuj24No ratings yet

- Universal Precautions in Infection PreventionDocument18 pagesUniversal Precautions in Infection PreventionadiNo ratings yet

- Fiber Glass Reinforced HDDDocument8 pagesFiber Glass Reinforced HDDGilvan SilvaNo ratings yet