Professional Documents

Culture Documents

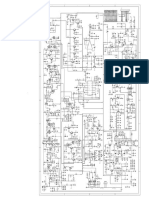

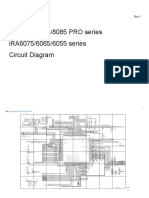

2015 Macbook Air A1466 Charging Circuit

2015 Macbook Air A1466 Charging Circuit

Uploaded by

vinicio andrangoOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

2015 Macbook Air A1466 Charging Circuit

2015 Macbook Air A1466 Charging Circuit

Uploaded by

vinicio andrangoCopyright:

Available Formats

8 7 6 5 4 3 2 1

Reverse-Current Protection

Need to stuff R7192 if either PP5V5_DCIN:YES or PP5V5_VDDP are used!

PP5V5_DCIN:YES

5.5v "G3Hot" Supply

NO STUFF

R7190

R7192

MIN_NECK_WIDTH=0.2 mm For Erp Lot6 spec

MIN_LINE_WIDTH=0.5 mm 0

0 1 2 CHGR_DCIN 50

50 PPCHGR_DCIN_D_R 1 2 CHGR_DCIN_D P5V1_BOOST

MIN_NECK_WIDTH=0.2 mm DIDT=TRUE MF-LF 5% 402

Inrush Limiter MIN_LINE_WIDTH=0.5 mm MF-LF 5% 402 1/16W

1/16W NO STUFF PP5V5_VDDP

NO STUFF1

3

C7190 C7194

1 R7191

1

NCNCNCNC 4.7UF VIN BOOST 0.22UF

CRITICAL

1

0

2 PP5V1_CHGR_VDDP 50

R7185 10%

NO STUFF

10%

NO STUFF

10

FROM ADAPTER 1%470K

25V

U7190 10V

L7195

5

X5R-CERM

2 CERM

2 MF-LF 5% 402

1/16W

0603 LT3470A 402 10UH-20%-0.85A-0.46OHM

1/20W

DFN

64 62 49 PPDCIN_G3H MF PPDCIN_G3H_INRUSH

1 2

2

201 CRITICAL MIN_LINE_WIDTH=0.6 mm

8

SHDN* SW 4 P5V1_SW PP5V5_CHGR_VDDP

NO STUFF NO STUFF

D C7185 1

Q7180

MIN_NECK_WIDTH=0.4 mm

BIAS 2

MIN_LINE_WIDTH=0.5 mm

2520 CRITICAL CRITICAL

MIN_NECK_WIDTH=0.25 mm

S

VOLTAGE=18.5V MIN_NECK_WIDTH=0.25 mm MIN_LINE_WIDTH=0.5 mm

1 1

0.1UF R7180 C7184 CRITICAL SWITCH_NODE=TRUE

1 1

VOLTAGE=5.5V

10% IRF9395TRPBF 4.7UF

7

NC DIDT=TRUE C7198 C7199

100K NO STUFF <Ra>

25V DIRECTFET-MC 10% 10UF 10UF

X5R

2 5%

25V

FB 1

NO STUFF R7195

1

20% 20%

1/20W 2

402 X5R-CERM THRM 1 C7195 10V 10V

G

MF 681K 2 2 Vout = 5.50V

201

0603 GND PAD 1%

X5R X5R

200MA MAX OUTPUT

2 22PF 603 603

(Switcher limit)

9

1/20W

CHGR_AGATE_DIV 5%

6

MF

50V

CHGR_SGATE_DIV 2 201

C0G 2

MIN_LINE_WIDTH=0.25 mm

0201

MIN_NECK_WIDTH=0.2 mm

1

R7186 1 P5V1_FB

332K R7181

1% 62K <Rb>

1/20W 5% NO STUFF 1

MF 1/20W

R7196

CRITICAL 201 MF

PPDCIN_G3H_ISOL 2

64 62 49 42 201 200K

2

D7105 MIN_LINE_WIDTH=0.25 mm (CHGR_AGATE)

1%

1/20W

BAT30CWFILM MIN_NECK_WIDTH=0.2 mm MF

SOT-323 PP5V5_DCIN:NO (CHGR_SGATE) Vout = 1.25V * (1 + Ra / Rb) 201

2

MIN_LINE_WIDTH=0.25 mm

1

R7105 MIN_NECK_WIDTH=0.2 mm

20 R7121

3 50 PPCHGR_DCIN_D_R 1 2 (CHGR_DCIN)

MIN_LINE_WIDTH=0.5 mm MIN_LINE_WIDTH=0.5 mm 10

MIN_NECK_WIDTH=0.2 mm 5% MIN_NECK_WIDTH=0.2 mm 1 2

2

VOLTAGE=18.5V 1/10W MIN_LINE_WIDTH=0.2 mm CRITICAL

MF-LF 5% 2

603

1

MIN_NECK_WIDTH=0.2 mm

1/20W 73 CHGR_CSI_R_P 4 R7120

ACIN pin threshold is 3.2V, +/- 50mV C7120 MF MIN_LINE_WIDTH=0.2 mm

0.020

201 MIN_NECK_WIDTH=0.2 mm

0.047UF 0.5%

10% 1W

DIVIDER SETS ACIN THRESHOLD AT 13.55V 16V MF-LF

2 73 CHGR_CSI_R_N

30mA max load

X7R-CERM R7122 0612

0402

10 3 1

1 2

PP5V1_CHGR_VDD R7101 PPDCIN_G3H_CHGR

MIN_LINE_WIDTH=0.2 mm 4.7 5% MIN_LINE_WIDTH=0.6 mm

MIN_NECK_WIDTH=0.1 mm

1 2 50 PP5V1_CHGR_VDDP 1/20W MIN_NECK_WIDTH=0.15 mm CRITICAL CRITICAL BYPASS=Q7130:1.5mm

VOLTAGE=5.1V MIN_LINE_WIDTH=0.2 mm MF VOLTAGE=18.5V

1 1 1 1 1

5% MIN_NECK_WIDTH=0.2 mm 201

C7130 C7131 C7135 C7136 C7137

1/16W VOLTAGE=5.1V

MF-LF 33UF-0.06OHM 33UF-0.06OHM 1UF 1UF 0.001UF

1 1 1 10% 10% 10%

59 49 46 40 38 37 36 35 30 17 PP3V42_G3H 402 C7101 C7122 C7121 20% 20%

25V 25V 50V

65 64 62 61 25V 2 25V 2 2 2 2

1UF 0.1UF 0.1UF POLY-TANT POLY-TANT

X5R X5R X7R-CERM

C

1

R7110

130K

1%

NO STUFF

1

10%

10V

X5R

402

2

10%

25V

X5R

402

2 2

10%

25V

X5R

402

CASE-D3L CASE-D3L 603-1 603-1 0402

C

1/20W

R7102

19

20

MF 100K

201 5%

2

1/20W

MF

VDD VDDP

201

R7100 2 12 VHST CRITICAL DCIN 2 50 CHGR_DCIN

0 Max Current = 8A

64 46 38 37 SMC_RESET_L 1 2 CHGR_RST_L 13 SMB_RST_N

IN 26

SGATE CHGR_SGATE

SMBUS_SMC_5_G3_SCL 11 SCL PLACE_NEAR=U7100.25:2mm

5%

1/20W

48 40 37

73 64 IN U7100 AGATE 1 CHGR_AGATE 1

C7125 2 3 4 9

MF 48 40 37 SMBUS_SMC_5_G3_SDA 10 SDA TQFN TO SYSTEM

BI 28 73 0.22UF

CSIP f = 400 kHz

ISL6259

0201 73 64 CHGR_CSI_P CRITICAL

59 CHGR_VFRQ 4 VFRQ 10%

IN

Float CELL for 1S

CHGR_CELL 6 CELL

CSIN 27 73 CHGR_CSI_N 2

10V

CERM

Q7130 CRITICAL CRITICAL

402

NTMFD4902NF

3

BOOT 25 CHGR_BOOT MIN_NECK_WIDTH=0.2 mm L7130 F7140

CHGR_ACIN ACIN 24

MIN_LINE_WIDTH=0.5 mm DIDT=TRUE

1 DFN 4.7UH-17A

UGATE CHGR_UGATE MIN_NECK_WIDTH=0.2 mm 8AMP-24V

MIN_LINE_WIDTH=0.5 mm DIDT=TRUE GATE_NODE=TRUE

5 23 1 2 1 2

1

CHGR_ICOMP ICOMP PHASE CHGR_PHASE

10 PPBUS_G3H 27 41 42 49 56 62 64

R7113 MIN_LINE_WIDTH=0.2 mm MIN_NECK_WIDTH=0.2 mm

CHGR_VCOMP 7 VCOMP MIN_NECK_WIDTH=0.2 mm

PIMC104T4R7MN-SM

100 MIN_LINE_WIDTH=0.2 mm MIN_NECK_WIDTH=0.2 mm LGATE 21 CHGR_LGATE MIN_NECK_WIDTH=0.2 mm SWITCH_NODE=TRUE MIN_LINE_WIDTH=0.6 mm 1206

5% CHGR_VNEG MIN_LINE_WIDTH=0.2 mm

8 VNEG MIN_LINE_WIDTH=0.5 mm DIDT=TRUE DIDT=TRUE VOLTAGE=8.6V

1/20W MIN_NECK_WIDTH=0.2 mm GATE_NODE=TRUE

1 18 16

MF

R7115 73 CHGR_CSO_P CSOP BGATE CHGR_BGATE

8

201

2

255K 73 CHGR_CSO_N 17 CSON 20V/V AMON 9 CHGR_AMON 41

OUT

1%

THRM_PAD

1/20W 36V/V BMON 15 CHGR_BMON 41

OUT PPVBAT_G3H_CHGR_REG

MF

1 1 14

C7150 (OD) ACOK SMC_BC_ACOK

R7111 2

201 OUT 37 38 61 65 MIN_LINE_WIDTH=0.6 mm

(AGND)

PGND

0.47UF

5 6 7 MIN_NECK_WIDTH=0.25 MM BYPASS=L7130:Q7130:1.5mm

46.4K 10%

VOLTAGE=8.6V

1 1 1 1

1% CHGR_VCOMP_R C7145

1/20W 2

10V C7140 C7141 C7143

X5R

62UF-0.023OHM 62UF-0.023OHM 62UF-0.023OHM 1000PF

MF

29

22

0402

20% 20% 20% 10%

201

2 1 16V

C7115 11V 2 11V 2 11V 2 2 X7R-1

TANT-POLY TANT-POLY TANT-POLY

470PF CASE-B2S CASE-B2S CASE-B2S 0201

10%

16V

2

R7142 1

X5R-X7R-CERM

0201

1K

B 5%

1/20W

MF

1

C7102

1UF

CRITICAL

B

R7116 1

10%

201

2 10V

XW7100

2

X5R R7150 Q7155

10K 402

SM

0.01

CHGR_ICOMP_R 1% SI7137DP

1/20W 1 2 (GND) 0.5%

SO-8

MF 1W

MF

TO/FROM BATTERY

201 PLACE_NEAR=U7100.22:1mm

2 0612-4

S

1 2 PPVBAT_G3H_CHGR_R PPVBAT_G3H_CONN 48 64

3

CHGR_VNEG_R

D

MIN_LINE_WIDTH=0.6 mm MIN_LINE_WIDTH=0.6 mm

3 4 MIN_NECK_WIDTH=0.25 MM MIN_NECK_WIDTH=0.15 mm

5

VOLTAGE=8.6V VOLTAGE=8.6V

R7151 2.2

1

1

C7116 (CHGR_CSO_P) 1 2 73 43 CHGR_CSO_R_P

MIN_LINE_WIDTH=0.2 mm 201 5% 1/20W MF

G

470PF MIN_NECK_WIDTH=0.1 mm

10%

(CHGR_CSO_N) R7152 0 1 2 73 43 CHGR_CSO_R_N

16V

5% 1/20W MF 0201

4

2 MIN_LINE_WIDTH=0.2 mm

X5R-X7R-CERM

MIN_NECK_WIDTH=0.1 mm

0201

(PPVBAT_G3H_CHGR_R) (PPVBAT_G3H_CHGR_R)

(CHGR_BGATE)

MIN_LINE_WIDTH=0.25 mm

MIN_NECK_WIDTH=0.2 mm

1

1

C7142 C7111 1 1

C7100 C7105 1

C7126

0.1UF 0.01UF 1UF 0.22UF 1000PF * R7151 HAS 2.2OHM TO COMPENSATE UNBALANCED VOLTAGE

10% 10% 10% 10% 10%

6.3V 10V 10V 50V 16V DUE TO DIFFERENT CURRENT ON _P AND _N. (FROM INTERSIL)

2

CERM-X5R X5R-CERM

2 2

X5R X5R-CERM

2

X7R-1

2

1 1 1 1

0201 0201 402-1 0603-1 0201

C7117 C7114 C7113 C7112

GND_CHGR_AGND 10UF 1UF 0.1UF 0.01UF

10% 10% 10% 10%

MIN_LINE_WIDTH=0.2 mm

25V 25V 25V 25V

MIN_NECK_WIDTH=0.2 mm 2 2 2 2

X5R X5R X5R X7R

VOLTAGE=0V

805 603-1 402 402

A SYNC_MASTER=J43_MLB SYNC_DATE=09/14/2012 A

PAGE TITLE

PBus Supply & Battery Charger

DRAWING NUMBER SIZE

Apple Inc. <SCH_NUM> D

REVISION

R

<E4LABEL>

NOTICE OF PROPRIETARY PROPERTY: BRANCH

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

<BRANCH>

THE POSESSOR AGREES TO THE FOLLOWING: PAGE

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

71 OF 121

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART SHEET

IV ALL RIGHTS RESERVED 50 OF 76

8 7 6 5 4 3 2 . 1

You might also like

- 2000 Terex T340 Elec & Hyd SchematicDocument7 pages2000 Terex T340 Elec & Hyd SchematicRussMahn100% (1)

- Samsung Confidential Led TV - Isl24835Document4 pagesSamsung Confidential Led TV - Isl24835Mark Orly Iñosa60% (5)

- LSPWM6R1Document1 pageLSPWM6R1luispache100% (1)

- 1998 Terex T340 Electric Schematic LowerDocument3 pages1998 Terex T340 Electric Schematic LowerRussMahn75% (4)

- TH336C, TH337C, TH406C, TH407C, TH414C, TH514C, TH417C Electrical Schematic 31200832 TH336C, TH337C, TH406C, TH407C, TH414C, TH514C, TH417CDocument15 pagesTH336C, TH337C, TH406C, TH407C, TH414C, TH514C, TH417C Electrical Schematic 31200832 TH336C, TH337C, TH406C, TH407C, TH414C, TH514C, TH417CEduardo67% (3)

- Pigstep: Presto e OstileDocument5 pagesPigstep: Presto e OstileJonNo ratings yet

- 2022 Aau Junior Olympic Games TrackscheduleDocument7 pages2022 Aau Junior Olympic Games TrackscheduleWilliam GrundyNo ratings yet

- Caso de Ángel PérezDocument8 pagesCaso de Ángel PérezMetro Puerto RicoNo ratings yet

- Blaw SoftDocument596 pagesBlaw Softjonathan tanNo ratings yet

- TPD - MS638.PB735 A16047 Schematic DiagramDocument11 pagesTPD - MS638.PB735 A16047 Schematic DiagramGeovanny SanjuanNo ratings yet

- TPD - MS338.PB792 Schematic DiagramDocument11 pagesTPD - MS338.PB792 Schematic DiagramPedro GoisNo ratings yet

- T Display S3Document1 pageT Display S3Sebastiao RochaNo ratings yet

- Fileshare - Ro - PLATINIUM RML-20 OTXT (PTLM 04-1 (20AL) ) (WWW - Pieseelectronice.go - Ro)Document1 pageFileshare - Ro - PLATINIUM RML-20 OTXT (PTLM 04-1 (20AL) ) (WWW - Pieseelectronice.go - Ro)ERYNo ratings yet

- TP MT5507 PC821+Schematics+DiagramDocument12 pagesTP MT5507 PC821+Schematics+DiagramHumberto AguilarNo ratings yet

- Pdvol (PR13) 2 3kva Prime 400V.25.04.2018Document1 pagePdvol (PR13) 2 3kva Prime 400V.25.04.2018maurilioctbaNo ratings yet

- TPD MS338 PC799Document14 pagesTPD MS338 PC799José SoeiroNo ratings yet

- Schematic Anytone at 5555 V6 7 ENGDocument4 pagesSchematic Anytone at 5555 V6 7 ENGTimmyNo ratings yet

- Mte MBL-9000Document1 pageMte MBL-9000Francisco Sanabria Najera100% (7)

- SW ElectronicschematicsDocument3 pagesSW ElectronicschematicsHenrik PeterssonNo ratings yet

- Coo 4Document1 pageCoo 4Jok PrasNo ratings yet

- Kenr5406 03 00 PubDocument2 pagesKenr5406 03 00 PubAhmed MoustafaNo ratings yet

- Rencana HMI Monitoring BusiDocument3 pagesRencana HMI Monitoring BusiEko BeryonoNo ratings yet

- SSCM First ModelDocument1 pageSSCM First ModelPrince ShaikNo ratings yet

- Electrical LegendDocument1 pageElectrical LegendPearl Jane TABSINGNo ratings yet

- TPD - ms338.PC798 SchematicsDocument11 pagesTPD - ms338.PC798 SchematicsMaikol DominguezNo ratings yet

- PRLSBP (4) 5-6-7,5kVA 26 10 2022Document1 pagePRLSBP (4) 5-6-7,5kVA 26 10 2022Darcio TolottiNo ratings yet

- Slk07 04 Fe Igoms Pgf Lay 001 Project Location 12-06-2024Document1 pageSlk07 04 Fe Igoms Pgf Lay 001 Project Location 12-06-2024Agung MaulanaNo ratings yet

- 18 606000 1100001344 Asb Civ SHD 115075 - 01Document1 page18 606000 1100001344 Asb Civ SHD 115075 - 01mahmudulalam konokNo ratings yet

- Street 25M Street 25M: 02 GF - F.F.L +1.90 1Document1 pageStreet 25M Street 25M: 02 GF - F.F.L +1.90 1Khaled AshrafNo ratings yet

- MARGHERA Preliminary Stowage Plan MV Beautrident - Rev.11.03.2022Document1 pageMARGHERA Preliminary Stowage Plan MV Beautrident - Rev.11.03.2022Oleksandr ShcherbynaNo ratings yet

- Mpd-Ug0: 04A-Mobilization and ConstructionDocument1 pageMpd-Ug0: 04A-Mobilization and ConstructioneopokandilNo ratings yet

- LSPWM (5) 29 03 06Document1 pageLSPWM (5) 29 03 06Ricardo EmilioNo ratings yet

- 9 - 35 - 204 - Ei000110443890 - Ylh - SLDDocument1 page9 - 35 - 204 - Ei000110443890 - Ylh - SLDnewattelectricNo ratings yet

- SSEM 010Document1 pageSSEM 010Prince ShaikNo ratings yet

- Corrosion Loops Example 4 - Separator Template1Document1 pageCorrosion Loops Example 4 - Separator Template1Christian JoseNo ratings yet

- Schematic Diagram NV-5001Document1 pageSchematic Diagram NV-5001Marco Kersul100% (3)

- To Control Unit OCS, See Circuit Diagram 2081507Document1 pageTo Control Unit OCS, See Circuit Diagram 2081507andrestkaNo ratings yet

- Pir2802 Pir2802: Pic2002 Pic2102 Pic2002 Pic2102Document2 pagesPir2802 Pir2802: Pic2002 Pic2102 Pic2002 Pic2102Marcel IELCEANNo ratings yet

- Esp32-Poe Rev C ColorDocument1 pageEsp32-Poe Rev C ColorBhupendra SutharNo ratings yet

- n.guit.: аранжировка для гитары - Владимир Гапонцев Standard tuningDocument7 pagesn.guit.: аранжировка для гитары - Владимир Гапонцев Standard tuningÉducation Musicale et chant Choral GARCIA MusiqueNo ratings yet

- 18 606000 1100001344 Asb Civ SHD 115140 - 03Document2 pages18 606000 1100001344 Asb Civ SHD 115140 - 03Mahmudul Alam kanakNo ratings yet

- GT 22Document12 pagesGT 22عبدوNo ratings yet

- Instituto Federal São PauloDocument1 pageInstituto Federal São PauloSide YNo ratings yet

- QP Corridor Ommision LayoutDocument1 pageQP Corridor Ommision LayoutMildredNo ratings yet

- Sunnyside Solo GuitarDocument2 pagesSunnyside Solo GuitarAlexander KorkkaNo ratings yet

- KITCHEN CUSTOM EQUIPMENTS - HWAWEI - SOLUTION60-ModelDocument1 pageKITCHEN CUSTOM EQUIPMENTS - HWAWEI - SOLUTION60-Modelmainulislam8882No ratings yet

- Division - PDF - Highlighted - 2023-10-03T162911.091Document1 pageDivision - PDF - Highlighted - 2023-10-03T162911.091heycapie.extNo ratings yet

- 鋼琴ver1Document3 pages鋼琴ver1chiochiiooNo ratings yet

- APC Back-Ups 400VADocument4 pagesAPC Back-Ups 400VALuis FariaNo ratings yet

- SchematDocument1 pageSchematnesvegamespNo ratings yet

- President Lincoln II Version 3 SchematicDocument13 pagesPresident Lincoln II Version 3 Schematicalf100% (1)

- KC868 A8 PCBV1.4Document1 pageKC868 A8 PCBV1.4Marek Duží100% (1)

- Oht 76Document5 pagesOht 76suraj sarkarNo ratings yet

- HDC-BBS-PH1-ZZ-DR-V-0100-DNL - Access Control Installation Door DetailsDocument1 pageHDC-BBS-PH1-ZZ-DR-V-0100-DNL - Access Control Installation Door Detailslucaz roseNo ratings yet

- Fig 2. 332/J2932 Issue 3: 4 Stabilizers OptionDocument1 pageFig 2. 332/J2932 Issue 3: 4 Stabilizers OptionВладиславГолышевNo ratings yet

- Prelude No. 21 BWV 866 in B MajorDocument3 pagesPrelude No. 21 BWV 866 in B MajorĐại Lâm NguyễnNo ratings yet

- Road From Palugaswewa To HabaranaDocument2 pagesRoad From Palugaswewa To HabaranaRenga Ramanujan CNo ratings yet

- QP Corridor - Works To Be Omitted-Location 1&2Document1 pageQP Corridor - Works To Be Omitted-Location 1&2MildredNo ratings yet

- 005 Minibrute 05 MetalizerDocument1 page005 Minibrute 05 MetalizerCristobal Nicolás100% (1)

- Ira6000 8000 Series-CdDocument427 pagesIra6000 8000 Series-Cdluongnam100% (1)