Professional Documents

Culture Documents

74LS48

74LS48

Uploaded by

Swat ZebraCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

74LS48

74LS48

Uploaded by

Swat ZebraCopyright:

Available Formats

SN54/74LS48

BCD TO 7-SEGMENT

DECODER

The SN54 / 74LS48 is a BCD to 7-Segment Decoder consisting of NAND

gates, input buffers and seven AND-OR-INVERT gates. Seven NAND gates

and one driver are connected in pairs to make BCD data and its complement BCD TO 7-SEGMENT

available to the seven decoding AND-OR-INVERT gates. The remaining DECODER

NAND gate and three input buffers provide lamp test, blanking input/ripple-

blanking input for the LS48. LOW POWER SCHOTTKY

The circuit accepts 4-bit binary-coded-decimal (BCD) and, depending on

the state of the auxiliary inputs, decodes this data to drive other components.

The relative positive logic output levels, as well as conditions required at the

auxiliary inputs, are shown in the truth tables.

The LS48 circuit incorporates automatic leading and / or trailing edge

J SUFFIX

zero-blanking control (RBI and RBO). Lamp Test (LT) may be activated any

CERAMIC

time when the BI / RBO node is HIGH. Both devices contain an overriding CASE 620-09

blanking input (BI) which can be used to control the lamp intensity by varying 16

the frequency and duty cycle of the BI input signal or to inhibit the outputs. 1

• Lamp Intensity Modulation Capability (BI/RBO)

• Internal Pull-Ups Eliminate Need for External Resistors

• Input Clamp Diodes Eliminate High-Speed Termination Effects

N SUFFIX

PLASTIC

CASE 648-08

CONNECTION DIAGRAM DIP (TOP VIEW) 16

VCC f g a b c d e 1

16 15 14 13 12 11 10 9

D SUFFIX

SOIC

16

1 CASE 751B-03

1 2 3 4 5 6 7 8 ORDERING INFORMATION

B C LT BI / RBO RBI D A GND SN54LSXXJ Ceramic

SN74LSXXN Plastic

LOGIC DIAGRAM SN74LSXXD SOIC

A LOGIC SYMBOL

b 7 1 2 6 3 5

B

INPUT

A B C D LT RBI

C c

D SN54 / 74LS48

OUTPUT BI/

d a b c d e f g RBO

BLANKING INPUT OR

RIPPLE-BLANKING

OUTPUT e 13 12 11 10 9 15 14 4

VCC = PIN 16

GND = PIN 8

f

RIPPLE-BLANKING

INPUT

LAMP-TEST

INPUT g

FAST AND LS TTL DATA

5-59

SN54/74LS48

PIN NAMES LOADING (Note a)

HIGH LOW

A, B, C, D BCD Inputs 0.5 U.L. 0.25 U.L.

RBI Ripple-Blanking (Active Low) Input 0.5 U.L. 0.25 U.L.

LT Lamp-Test (Active Low) Input 0.5 U.L. 0.25 U.L.

BI / RBO Blanking Input or Ripple- 0.5 U.L. 0.75 U.L.

Blanking Output (Active Low) 1.2 U.L. 2(1) U.L.

BI Blanking (Active Low) Input 0.5 U.L. 0.25 U.L.

Open-Collector 3.75 (1.25) U.L. (48)

NOTES:

a) Unit Load (U.L.) = 40 µA HIGH / 1.6 mA LOW

b) Outut current measured at VOUT = 0.5 V

Output LOW drive factor is SN54LS / 74LS48: 1.25 U.L. for Military (54), 3.75 U.L. for Commercial (74).

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

NUMERICAL DESIGNATIONS — RESULTANT DISPLAYS

TRUTH TABLE

SN54 / 74LS48

INPUTS OUTPUTS

DECIMAL

OR LT RBI D C B A BI / RBO a b c d e f g NOTE

FUNCTION

0 H H L L L L H H H H H H H L 1

1 H X L L L H H L H H L L L L 1

2 H X L L H L H H H L H H L H NOTES:

3 H X L L H H H H H H H L L H (1) BI/RBO is wired-AND logic serving as blanking input (BI) and/or

4 H X L H L L H L H H L L H H ripple-blanking output (RBO). The blanking out (BI) must be open

or held at a HIGH level when output functions 0 through 15 are

5 H X L H L H H H L H H L H H

desired, and ripple-blanking input (RBI) must be open or at a HIGH

6 H X L H H L H L L H H H H H

level if blanking of a decimal 0 is not desired. X=input may be HIGH

7 H X L H H H H H H H L L L L or LOW.

8 H X H L L L H H H H H H H H (2) When a LOW level is applied to the blanking input (forced condition)

9 H X H L L H H H H H L L H H

all segment outputs go to a LOW level, regardless of the state of any

other input condition.

10 H X H L H L H L L L H H L H

(3) When ripple-blanking input (RBI) and inputs A, B, C, and D are at

11 H X H L H H H L L H H L L H LOW level, with the lamp test input at HIGH level, all segment

12 H X H H L L H L H L L L H H outputs go to a HIGH level and the ripple-blanking output (RBO)

13 H X H H L H H H L L H L H H goes to a LOW level (response condition).

(4) When the blanking input/ripple-blanking output (BI/RBO) is open or

14 H X H H H L H L L L H H H H

held at a HIGH level, and a LOW level is applied to lamp-test input,

15 H X H H H H H L L L L L L L all segment outputs go to a LOW level.

BI X X X X X X L L L L L L L L 2

RBI H L L L L L L L L L L L L L 3

LT L X X X X X H H H H H H H H 4

FAST AND LS TTL DATA

5-60

SN54/74LS48

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

VCC Supply Voltage 54 4.5 5.0 5.5 V

74 4.75 5.0 5.25

TA Operating Ambient Temperature Range 54 – 55 25 125 °C

74 0 25 70

IOH Output Current — High a to g 54, 74 – 100 µA

IOH Output Current — High BI / RBO 54, 74 – 50 µA

IOL Output Current — Low a to g 54 2.0 mA

74 6.0

IOL Output Current — Low BI / RBO 54 1.6 mA

BI / RBO 74 3.2

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Limits

Symbol Parameter Min Typ Max Unit Test Conditions

Guaranteed Input HIGH Voltage for

VIH Input HIGH Voltage 2.0 V

All Inputs

54 0.7 Guaranteed Input LOW Voltage for

VIL Input LOW Voltage V

74 0.8 All Inputs

VIK Input Clamp Diode Voltage – 1.5 V VCC = MIN, IIN = – 18 mA

VCC = MIN, IOH = – 50 µA,

VOH Output HIGH Voltage 2.4 4.2 µA

VIN = VIH or U.L. per Truth Table

VCC = MIN, VO = 0.85 V

IO Output Current a to g – 1.3 – 2.0 mA

Input Conditioner as for VOH

54, 74 0.4 V IOL = 2.0 mA VCC = MIN, VIH = 2.0 V

VOL Output LOW Voltage a to g

74 0.5 V IOL = 6.0 mA VIL = VIL MAX

Output LOW Voltage 54, 74 0.4 V IOL = 1.6 mA VCC = MAX, VIH = 2.0 V

VOL

BI / RBO 74 0.5 V IOL = 3.2 mA VIL = VIL MAX

Input HIGH Current 20 µA VCC = MAX, VIN = 2.7 V

IIH

(Except BI / RBO) 0.1 mA VCC = MAX, VIN = 7.0 V

Input LOW Current

IIL – 0.4 mA VCC = MAX, VIN = 0.4 V

(Except BI / RBO)

IIL Input LOW Current BI/ RBO – 1.2 mA VCC = MAX, VIN = 0.4 V

ICC Power Supply Current 25 38 mA VCC = MAX

IOS Short Circuit Current BI/ RBO (Note 1) – 0.3 –2.0 mA VCC = MAX

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

AC CHARACTERISTICS (VCC = 5.0 V, TA = 25°C)

Limits

Symbol Parameter Min Typ Max Unit Test Conditions

Propagation Delay Time, HIGH-to-LOW

tPHL 100 ns

Level Output from A Input

CL = 15 pF, RL = 4.0 kΩ

Propagation Delay Time, LOW-to-HIGH

tPLH 100 ns

Level Output from A Input

Propagation Delay Time, HIGH-to-LOW

tPHL 100 ns

Level Output from RBI Input

CL = 15 pF, RL = 6.0 kΩ

Propagation Delay Time, LOW-to-HIGH

tPLH 100 ns

Level Output from RBI Input

FAST AND LS TTL DATA

5-61

You might also like

- 01 Service Manual SV600 V4.0 enDocument384 pages01 Service Manual SV600 V4.0 enLuis Felipe Romero100% (3)

- Chapter 11 Part 4 Multistage Amplifier - Sem1 1617Document9 pagesChapter 11 Part 4 Multistage Amplifier - Sem1 1617Yue Kai100% (1)

- Hoja Caracteristicas 7476Document5 pagesHoja Caracteristicas 7476GroplyNo ratings yet

- Amkasyn Device Description Servo Drives KE/KW Compact Power Supplies KE, KES, KEN Compact Inverters KW, KWDDocument212 pagesAmkasyn Device Description Servo Drives KE/KW Compact Power Supplies KE, KES, KEN Compact Inverters KW, KWDMr.K chNo ratings yet

- The DV Rebel's Guide - An All-Digital Approach To Making Killer Action Movies On The Cheap, by Stu Maschwitz (ISBN 0321413644)Document200 pagesThe DV Rebel's Guide - An All-Digital Approach To Making Killer Action Movies On The Cheap, by Stu Maschwitz (ISBN 0321413644)Andrei Vartaci100% (2)

- Etisalat UAE - Prepaid Mobile Data PlansDocument8 pagesEtisalat UAE - Prepaid Mobile Data PlansMcDaryl MateoNo ratings yet

- PCM ProjectDocument7 pagesPCM Projectsuresh NamgiriNo ratings yet

- Transformada ZDocument17 pagesTransformada Znikika1No ratings yet

- DSP Lab Sheet 2 PDFDocument50 pagesDSP Lab Sheet 2 PDFSreekrishna DasNo ratings yet

- Nyquist Stability CriterionDocument4 pagesNyquist Stability CriterionRajeev KumarNo ratings yet

- Datasheet 74hc45Document10 pagesDatasheet 74hc45aleallenderNo ratings yet

- Jacome Sebastian 10Document7 pagesJacome Sebastian 10Yandri DavidNo ratings yet

- Cs Imp QuestDocument3 pagesCs Imp QuestLordwin MichealNo ratings yet

- Application FFT-LVDTDocument6 pagesApplication FFT-LVDTnapoleon_velasc3617No ratings yet

- Lab1 VHDLDocument9 pagesLab1 VHDLGautam GowdaNo ratings yet

- SVD ComputationDocument13 pagesSVD ComputationEnas DhuhriNo ratings yet

- Modul 1 Lab KendaliDocument31 pagesModul 1 Lab KendaliSyukran0% (1)

- Contador BCD UP - DOWN Con GAL 22V10Document1 pageContador BCD UP - DOWN Con GAL 22V10api-27527336100% (1)

- CH 6 Flip Flops - GATE - CourseDocument65 pagesCH 6 Flip Flops - GATE - CourseDikesh ShresthaNo ratings yet

- Lab 11 DAC and ADC Full PackageDocument5 pagesLab 11 DAC and ADC Full PackageLoveWorldCanadaNo ratings yet

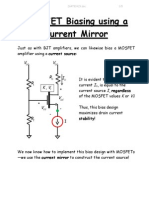

- MOSFET Biasing Using A Current MirrorDocument5 pagesMOSFET Biasing Using A Current MirrorshastryNo ratings yet

- EE680Lab Experiment6-7Document21 pagesEE680Lab Experiment6-7Amro AbusailNo ratings yet

- Network SynthesisDocument17 pagesNetwork SynthesisStarhero HemuNo ratings yet

- Lecture 5 - Biopotential MeasurementsDocument59 pagesLecture 5 - Biopotential Measurementsapi-27535945100% (2)

- Chebyshev2 IIR Filter DesignDocument4 pagesChebyshev2 IIR Filter DesignDramane BonkoungouNo ratings yet

- Lab 4Document18 pagesLab 4MD AZIZUL HOQUE / UPMNo ratings yet

- Ee 391 Circuit Theory New Lab ManualDocument39 pagesEe 391 Circuit Theory New Lab ManualKarthik PariharNo ratings yet

- FM Balanced Slope DetectorDocument5 pagesFM Balanced Slope DetectorPujjalPandeyNo ratings yet

- Laplace Transform ExamplesDocument19 pagesLaplace Transform Exampleshamza abdo mohamoudNo ratings yet

- Flip FlopsDocument21 pagesFlip Flopsmangla bhullar100% (1)

- CT Assignment IDocument4 pagesCT Assignment ImosesalvinNo ratings yet

- Solution 2Document5 pagesSolution 2Paulina MarquezNo ratings yet

- 3.1 Analog MultipliersDocument17 pages3.1 Analog MultipliersMarykutty CyriacNo ratings yet

- Assignment 1Document8 pagesAssignment 1phyrdowsNo ratings yet

- Programmable Read Only Memory Prom: Plds SDocument6 pagesProgrammable Read Only Memory Prom: Plds SShravan Kumar NamdeoNo ratings yet

- Nand GateDocument5 pagesNand GateNeeraj SharmaNo ratings yet

- Alexan Product ListDocument21 pagesAlexan Product ListEdler CasamaNo ratings yet

- EE 174 Fall 2019: Operational AmplifiersDocument36 pagesEE 174 Fall 2019: Operational AmplifiersKavyashreeMNo ratings yet

- Nguyen Le Quang 1852696 Homework #3: K Gs SsDocument8 pagesNguyen Le Quang 1852696 Homework #3: K Gs SsKiet PhamNo ratings yet

- S-Edit Examples GuideDocument41 pagesS-Edit Examples GuideAyan GhoshNo ratings yet

- 6-A Prediction ProblemDocument31 pages6-A Prediction ProblemPrabhjot KhuranaNo ratings yet

- EXPERIMENT 2 Lab2Document28 pagesEXPERIMENT 2 Lab2Aisamuddin SubaniNo ratings yet

- Jacobi MethodDocument2 pagesJacobi MethodJuancho SotilloNo ratings yet

- Experiment-10 (Adder & Subtractor)Document7 pagesExperiment-10 (Adder & Subtractor)M BalajiNo ratings yet

- Small Signal Model MOSFETDocument8 pagesSmall Signal Model MOSFETRAHUL100% (1)

- Amplitude Shift Keying Modulator DemodulatorDocument10 pagesAmplitude Shift Keying Modulator DemodulatorSandi M MNo ratings yet

- Representation of Power Systems: 1.1 One Line DiagramDocument17 pagesRepresentation of Power Systems: 1.1 One Line DiagramDr. Gollapalli Naresh100% (1)

- ALU 74181 SpecificationDocument1 pageALU 74181 SpecificationDražen BorčićNo ratings yet

- Circuit1 OscilloscopeDocument3 pagesCircuit1 Oscilloscopeapi-3801726100% (1)

- 74LS47Document3 pages74LS47jaja558No ratings yet

- 74 Ls 47Document3 pages74 Ls 47Joelo D' CartonNo ratings yet

- 74LS174Document3 pages74LS174jaja558No ratings yet

- 74LS151Document3 pages74LS151Kang RoyNo ratings yet

- 4-Bit Binary Full Adder With Fast Carry SN54/74LS283: Low Power SchottkyDocument5 pages4-Bit Binary Full Adder With Fast Carry SN54/74LS283: Low Power SchottkyJessica RojasNo ratings yet

- MC14499 DatasheetDocument8 pagesMC14499 DatasheetTedyS1959No ratings yet

- Semiconductor Technical Data: Ordering InformationDocument9 pagesSemiconductor Technical Data: Ordering Informationdaniel ortegaNo ratings yet

- 4-Bit Binary Full Adder With Fast Carry SN54/74LS283: Low Power SchottkyDocument4 pages4-Bit Binary Full Adder With Fast Carry SN54/74LS283: Low Power SchottkyLoth Matheus Barba MazaNo ratings yet

- 74LS190Document8 pages74LS190jaja558No ratings yet

- 74LS155Document4 pages74LS155jaja558No ratings yet

- SN74LS193Document11 pagesSN74LS193HeartBraveNo ratings yet

- Datasheet 74192Document7 pagesDatasheet 74192phongbui135100% (3)

- 74LS164Document4 pages74LS164jaja558No ratings yet

- Adc32rfxxevm-Sch DDocument10 pagesAdc32rfxxevm-Sch Daprince6311No ratings yet

- 74LS190Document10 pages74LS190nukachNo ratings yet

- N700-Programing 1 ManualDocument317 pagesN700-Programing 1 ManualAndre CostaNo ratings yet

- Normal Approximation of The Poisson DistributionDocument1 pageNormal Approximation of The Poisson DistributionChooi Jia YueNo ratings yet

- Eki 7706e 2fi Ae PDFDocument2 pagesEki 7706e 2fi Ae PDFMario PatarroyoNo ratings yet

- Prog Lang Notes2019Document184 pagesProg Lang Notes2019Fabrizzio GonzalesNo ratings yet

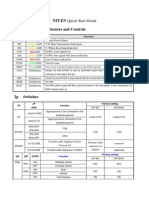

- NIT-EN Quick Start Guide Front Panel Indicators and ControlsDocument2 pagesNIT-EN Quick Start Guide Front Panel Indicators and Controlsonglaido1987No ratings yet

- Mon-53 p4 Milestone1Document15 pagesMon-53 p4 Milestone1api-529470340No ratings yet

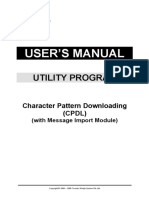

- CPDL User ManualDocument21 pagesCPDL User ManualJOHANA BEDOYANo ratings yet

- Assignment 2 FingerprintDocument2 pagesAssignment 2 FingerprintElaiza Bave MoqueteNo ratings yet

- Carto TestDocument8 pagesCarto TestnazryNo ratings yet

- Medal Log 20210813Document45 pagesMedal Log 20210813Adam ANo ratings yet

- Manual en v5Document74 pagesManual en v5One centerNo ratings yet

- Cast Bolted Brackets: W Series: Nominal Connector DimensionsDocument2 pagesCast Bolted Brackets: W Series: Nominal Connector Dimensionsaams_sNo ratings yet

- 2.operating SystemDocument7 pages2.operating Systemrc5184751No ratings yet

- Lab 3 OSDocument6 pagesLab 3 OSPrateek JaiswalNo ratings yet

- Lexical AnalysisDocument38 pagesLexical Analysissaeed khanNo ratings yet

- Iot Based Intelligent TrolleyDocument10 pagesIot Based Intelligent TrolleyHithesh GowdaNo ratings yet

- IJRICSE-1 Vol 1 Issue Palm Stamp Identification Using Daubechies 4 and Coiflet Transforms PDFDocument4 pagesIJRICSE-1 Vol 1 Issue Palm Stamp Identification Using Daubechies 4 and Coiflet Transforms PDFIJRICSENo ratings yet

- Table-Of-Specification Grade 7Document2 pagesTable-Of-Specification Grade 7KenNo ratings yet

- Oracle SQL Excercise 5 - Formatting OutputDocument2 pagesOracle SQL Excercise 5 - Formatting Outputaditya infaNo ratings yet

- Panasonic RQ-X11 Service Manual - View Online or Download Repair Manual PDFDocument3 pagesPanasonic RQ-X11 Service Manual - View Online or Download Repair Manual PDFAnn Varney FlowersNo ratings yet

- Floating-Point Numbers and Operations RepresentationDocument8 pagesFloating-Point Numbers and Operations RepresentationSurya NarasimanNo ratings yet

- Macbook Water Damage in Cold - Google Search PDFDocument1 pageMacbook Water Damage in Cold - Google Search PDFhahaNo ratings yet

- Engineering Applications of Artificial Intelligence: A Bibliometric Analysis of 30 Years (1988-2018)Document33 pagesEngineering Applications of Artificial Intelligence: A Bibliometric Analysis of 30 Years (1988-2018)Adi lukmanNo ratings yet

- Windows 7 Data RecoveryDocument8 pagesWindows 7 Data RecoveryAsai NeonNo ratings yet

- Paper BoatDocument2 pagesPaper BoatAnkit SinhaNo ratings yet

- School Computer Education Made EasyDocument4 pagesSchool Computer Education Made EasysbNo ratings yet