Professional Documents

Culture Documents

IT8586E

IT8586E

Uploaded by

Jivko IvanovOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

IT8586E

IT8586E

Uploaded by

Jivko IvanovCopyright:

Available Formats

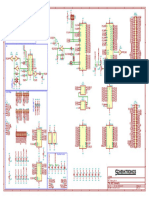

5 4 3 2 1

+3VL

1 RE1 2 PECI

Vcc 3.3V +/- 5%

<5> H_PECI

43_0402_5% RE3 100K +/- 1%

2

@

1 RE3 Board ID RE7 VAD_BID min V AD_BID typ VAD_BID max Phase

+3VL

CE1

47P_0402_50V8-J All capacitors close to EC 100K_0402_1%

0 0K +/- 5% 0 V 0 V 0 V Pre-SDV

1

2

+3VL CE4 CE5 CE8 CE6 CE9 CE10 Board_ID

1 8.2K +/- 5% 0.216 V 0.250 V 0.289 V SDV

Intel recommend 2 18K +/- 5% 0.436 V 0.503 V 0.538 V FVT

2

0.1U_0402_25V6-K

0.1U_0402_25V6-K

0.1U_0402_25V6-K

0.1U_0402_25V6-K

0.1U_0402_25V6-K

0.1U_0402_25V6-K

1 1 1 1

@

1

@

1 RE7

4.7K_0402_1%

3 33K +/- 5% 0.712 V 0.819 V 0.875 V SIT

Close to EC +3VS +3VL_AVCC

4 4.7K +/- 5% 0.141 V 0.148 V 0.155 V SVT

D D

CE7

1

1 2 2 2 2 2 2 2

+VCOREVCC

5 24K +/- 5% 0.612 V 0.638 V 0.664 V

0.1U_0402_25V6-K

+3VL

114

121

127

12

11

26

50

92

74

RE4 minimum trace width 12 mil

3

1 2 WRST# UE1

1

VSTBY1

VSTBY2

VSTBY3

VSTBY4

VSTBY5

VCC

AVCC

VBAT

VSTBY(PLL)

VCORE

100K_0402_5%

CE11

1.05VS_PGOOD_R 1 2 1.05VS_PGOOD 1.05VS_PGOOD <10,14,70>

1U_0402_10V6-K RE40 0_0402_5%

2

KBRST# 4 24 LOGO_LED# +3VL +3VL_AVCC

<12> KBRST# KBRST#/GPB6 PWM0/GPA0 LOGO_LED# <38,54>

SERIRQ 5 25 AOU_IFG#

<12,56> SERIRQ SERIRQ/GPM6 PWM1/GPA1 AOU_IFG# <41>

LPC_FRAME# 6 28 VM_PWRON LE1

+3VALW <56,9> LPC_FRAME# LFRAME#/GPM5 PWM2/GPA2 VM_PWRON <61,78>

LPC_AD3 7 29 1.05VS_PGOOD_R 1 2 +3VL_AVCC

<56,9> LPC_AD3 8 LAD3/GPM3 PWM3/GPA3 30

<56,9> LPC_AD2

LPC_AD2

LAD2/GPM2 PWM PWM4/GPA4

GS_SELFTEST

GS_SELFTEST <56>

LPC_AD1 9 31 EC_FAN_PWM BLM18PG121SN1D_2P

<56,9> LPC_AD1 LAD1/GPM1 PWM5/GPA5 EC_FAN_PWM <50>

RE15 1 2 100K_0402_5% HDD_DETECT# LPC_AD0 10 32 BEEP# 1 1

<56,9> LPC_AD0 13 LAD0/GPM0 PWM6/SSCK/GPA6 34 BEEP# <36>

<8> CLK_PCI_EC

CLK_PCI_EC

LPCCLK/GPM4 LPC PWM7/RIG1#/GPA7

VCCST_PG_EC

VCCST_PG_EC <14>

+3VALW WRST# 14 120 CE2 CE3

HDD_DETECT# 15 WRST# TMRI0/GPC4 124 SUSP# 0.1U_0402_25V6-K 1000P_0402_50V7-K

<37> HDD_DETECT# ECSMI#/GPD4 TMRI1/GPC6 SUSP# <43,61,69,70,71,76> 2 2

RPE1 EC_RX 16

<52> EC_RX PWUREQ#/BBO/SMCLK2ALT/GPC7

1 8 MSATA_DETECT# EC_TX 17 66 GPU_VR_HOT# GPU_VR_HOT# <21,76> LE2

2 7 <52> EC_TX 22 LPCPD#/GPE6 ADC0/GPI0 67 1 2

AOU_IFG# PLTRST#_FAR GS_VOUTY GS_VOUTY <56> EC_AGND

<10,52,56> PLTRST#_FAR LPCRST#/GPD2 ADC1/GPI1

3 6 KB_FN EC_SCI# 23 68 BATT_TEMP BATT_TEMP <66,67>

4 5 <7> EC_SCI# 126 ECSCI#/GPD3 ADC2/GPI2 69

EC_WLAN_WAKE#

<21> VGA_AC_DC#

VGA_AC_DC#

GA20/GPB5 ADC ADC3/GPI3

Board_ID BLM18PG121SN1D_2P

70

10K_0804_8P4R_5% IT8586E/AX ADC4/GPI4

ADC5/DCD1#/GPI5

71

72

FAN_ID

ADP_I

GS_VOUTX

FAN_ID <50>

ADP_I <67>

GS_VOUTX <56>

1

RPE2

8 KSO1

<51> KSI[0..7]

KSI[0..7] KSI0 58

KSI0/STB#

LQFP-128L ADC6/DSR1#/GPI6

ADC7/CTS1#/GPI7

73 ADP_ID ADP_ID <65> +5VALW

2 7 KSO2 KSI1 59 78 SUSWARN# SUSWARN# <10>

3 6 FAN_ID KSO[0..17] KSI2 60 KSI1/AFD# DAC2/TACH0B/GPJ2 79 MAINPWON_EC USB_ON# RE2 1 2 10K_0402_5%

<51> KSO[0..17] KSI2/INIT# DAC3/TACH1B/GPJ3 MAINPWON_EC <65,66,68>

4 5 LAN_WAKE# KSI3 61 DAC 80 H_PROCHOT_EC

KSI4 62 KSI3/SLIN# DAC4/DCD0#/GPJ4 81 ENBKL

C ENBKL <11> C

10K_0804_8P4R_5% KSI5 63 KSI4 DAC5/RIG0#/GPJ5

+3VS KSI6 64 KSI5 85 AOU_EN +5VS

KSI6 PS2CLK0/TMB0/CEC/GPF0 AOU_EN <41>

RPE3 KSI7 65 86 PBTN_OUT#

1 8 36 KSI7 PS2DAT0/TMB1/GPF1 87 PBTN_OUT# <10> 1 2

LPC_FRAME# KSO0 PCH_SLP_SUS# PCH_SLP_SUS# <10> CP_CLK RE5 4.7K_0402_5%

+3VL KSO0/PD0 GPF2

2 7 EC_FAN_SPEED KSO1 37

KSO1/PD1 Int. K/B PS2 GPF3

88 SUSACK#

SUSACK# <10>

CP_DATA RE6 1 2 4.7K_0402_5%

3 6 KSO2 38 89 CP_CLK

4 5 39 KSO2/PD2 Matrix PS2CLK2/GPF4 90

CP_CLK <49>

LID_SW# KSO3 CP_DATA

KSO3/PD3 PS2DAT2/GPF5 CP_DATA <49>

KSO4 40 +3VS

41 KSO4/PD4 96

10K_0804_8P4R_5% KSO5

KSO5/PD5 EXTERNAL SERIAL FLASH GPH3/ID3

EC_DPWROK

EC_DPWROK <10>

KSO6 42 97 PCH_PWR_EN# EC_FAN_PWM RE8 1 @ 2 10K_0402_5%

43 KSO6/PD6 GPH4/ID4 98 PCH_PWR_EN# <61>

KSO7 ACOFF

KSO7/PD7 GPH5/ID5 ACOFF <67>

RPE4 KSO8 44 99 PCH_PWROK GPU_VR_HOT# RE9 1 2 10K_0402_5%

KSO8/ACK# GPH6/ID6 PCH_PWROK <10>

1 8 SUSP# KSO9 45

2 7 KSO10 46 KSO9/BUSY 101 FSCE#

KSO10/PE NC1 FSCE# <9>

3 6 KSO11 51

KSO11/ERR# NC2

102 SPI_FMOSI#

SPI_FMOSI# <9> Un-stuff if not necessary.

4 5 SYSON KSO12 52 SPI Flash ROM 103 SPI_FMISO

KSO12/SLCT NC3 SPI_FMISO <9>

KSO13 53 105 SPI_FSCK

KSO13 NC4 SPI_FSCK <9>

100K_0804_8P4R_5% KSO14 54

KSO15 55 KSO14

@ KSO16 56 KSO15 108 ACIN

CE14 2 1 57 KSO16/SMOSI/GPC3 AC_IN# 109

0.1U_0402_25V6-K KSO17

KSO17/SMISO/GPC5 UART LID_SW#

LID_SW# LID_SW# <34,51>

For EMC

ON/OFF# 110 82 PCH_SYSPWROK

<34,50> ON/OFF# PWRSW# EGAD/GPE1 PCH_SYSPWROK <10>

111

XLP_OUT SM Bus EGCS#/GPE2

83 EC_ON EC_ON <68>

EC_SMB_CK1 115 84 AOU_CTL1

+3VL <66,67> EC_SMB_CK1 SMCLK1/GPC1 EGCLK/GPE3 AOU_CTL1 <41>

EC_SMB_DA1 116

<66,67> EC_SMB_DA1 SMDAT1/GPC2

RPE5 PECI 117 GPIO 77 PM_SLP_S5#

SMCLK2/PECI/GPF6 GPJ1 PM_SLP_S5# <10>

1 8 EC_SMB_CK1 ADAPTER_ID_ON# 118 100 EC_MUTE#

+3VS <65> ADAPTER_ID_ON# SMDAT2/PECIRQT#/GPF7 SSCE0#/GPG2 EC_MUTE# <35>

2 7 EC_SMB_DA1 EC_SMB_CK3 94 106 EC_GS_ON#

3 6 <21,34,55,9> EC_SMB_CK3 95 CRX1/SIN1/SMCLK3/GPH1/ID1 SSCE1#/GPG0 104 EC_GS_ON# <56>

EC_SMB_DA3 ME_FLASH

<21,34,55,9> EC_SMB_DA3 CTX1/SOUT1/GPH2/SMDAT3/ID2 DSR0#/GPG6 ME_FLASH <7>

4 5 EC_SMB_CK3 107 SYSON

DTR1#/SBUSY/GPG1/ID7 SYSON <61,69>

119 BKOFF#

+3VS CRX0/GPC0 123 BKOFF# <38>

2.2K_0804_8P4R_5% AOAC_ON#

CTX0/TMA0/GPB2 AOAC_ON# <52>

+3VL 112 18 PM_SLP_S3# PM_SLP_S3# <10>

RE27 1 2 2.2K_0402_5% EC_SMB_DA3 LAN_WAKE# 125 VSTBY0 RI1#/GPD0 21 PM_SLP_S4#

<47> LAN_WAKE# GPE4 RI2#/GPD1 PM_SLP_S4# <10>

B WAKE UP TACH2/GPJ0

76 PM_SLP_A# PM_SLP_A# <10> B

48 AOU_CTL3

TACH1A/TMA1/GPD7 47 AOU_CTL3 <41> +3VL

EC_FAN_SPEED EC_FAN_SPEED <50>

USB_ON# 33 TACH0A/GPD6 19 EC_WLAN_WAKE# MIRROR@

<34,40> USB_ON# GINT/CTS0#/GPD5 L80HLAT/BAO/GPE0 EC_WLAN_WAKE# <52>

MSATA_DETECT# 35 GPIO 20 KB_FN

<52> MSATA_DETECT# RTS1#/GPE5 L80LLAT/GPE7 KB_FN <51>

EC_RSMRST# 93 EC_ON RE39 1 2 10K_0402_5%

<10> EC_RSMRST# CLKRUN#/GPH0/ID0

EC_WAKE# 2

Please don't place any PU Resistor on GPG[7:2] +3VL

<12> EC_WAKE# 128 CK32KE/GPJ7 (Reserve hardware strapping)

<10> AC_PRESENT

AC_PRESENT

CK32K/GPJ6 Clock

MIRROR@

EC_MUTE# RE31 1 2 10K_0402_5%

RE32 1 @ 2 10K_0402_5%

AVSS

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

1. Version CX : Don't Support Mirror Code

IT8586E-AX_LQFP128_14X14 IT8586E/FX LQFP Version DX/EX/FX : Support Mirror Code

1

27

49

91

113

122

75

SA00005W940

2. For Mirror Code

EC_AGND

"H" --> Enable

"L" --> Disable (Default)

*

AC IN, need to confirm the pin is High or Low active while pulg ACIN

+3VL

For factory EC flash

ACIN RE33 1 2 10K_0402_5%

1 EC_SMB_CK1 RE34 1 2 0_0402_5%

ACPRN <67>

IT1 @1 EC_SMB_DA1

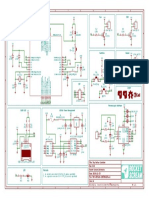

PROCHOT# IT2 @1 DEV1 @ 2 1 RB751V-40_SOD323-2

For ESD (EC asserts PROCHOT# signal by driving high, IT3

IT4

@1

@1

A A

EMC_NS@ the level shifter must invert it and drive the processor side PROCHOT# low.) IT5 @ CE12 1 2 100P_0402_50V8-J

CE13 1 2 220P_0402_50V7-K PLTRST#_FAR

1 KSI7

For EMI IT6 @1 KSI6

EMC_NS@ RE38 EMC_NS@ VR_HOT# IT7 @1 WRST#

CE15 1 2 10P_0402_50V8-J 1 2 CLK_PCI_EC <5,67,73> VR_HOT# IT8 @

D

1

1

10_0402_5% H_PROCHOT_EC 2 CE17

CE16 2 1 100P_0402_50V8-J BATT_TEMP G Title

QE1 S 47P_0402_50V8-J

Security Classification LC Future Center Secret Data

3

2N7002WT1G_1N_SC-70-3 2

BATT_TEMP EC ADC pin Issued Date 2013/09/07 Deciphered Date 2014/09/07 XXXX

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D Size Document Number Rev

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

C

AITE1_NM-A221 1.0

Date: Thursday, November 06, 2014 Sheet 62 of 81

5 4 3 2 1

You might also like

- C.6 Raymond Yiu - LullabyDocument4 pagesC.6 Raymond Yiu - Lullaby김영은100% (5)

- FP14000 AmpDocument1 pageFP14000 AmpAgin Tersakiti67% (6)

- Qdoc - Tips Visionplus Interview QuestionsDocument3 pagesQdoc - Tips Visionplus Interview QuestionsHari Prasad SL Reddy100% (1)

- Fp14000 Amp ADocument1 pageFp14000 Amp Acoolruler4056% (9)

- MINI (KV30 - 0) c.12V.BIVOLT - MINI.IV.28.01.2021Document1 pageMINI (KV30 - 0) c.12V.BIVOLT - MINI.IV.28.01.2021wesnen lara100% (1)

- TP - ms18VG - pb77 A13486 Schematic DiagramDocument7 pagesTP - ms18VG - pb77 A13486 Schematic DiagramJulian Andres RozoNo ratings yet

- SchematicDocument41 pagesSchematicCarlos Ventura100% (1)

- 16PinBox HW2Document1 page16PinBox HW2Ney AndradeNo ratings yet

- Datasheet IT8987E PDFDocument1 pageDatasheet IT8987E PDFAnalia Madeled Tovar JimenezNo ratings yet

- Datasheet IT8987E PDFDocument1 pageDatasheet IT8987E PDFAnalia Madeled Tovar JimenezNo ratings yet

- Datasheet IT8987E PDFDocument1 pageDatasheet IT8987E PDFd4l170100% (1)

- F10 Taps in Auto Transformers PaperDocument55 pagesF10 Taps in Auto Transformers Paperverma210No ratings yet

- S-0701-PE Chief Engineer's ReportDocument2 pagesS-0701-PE Chief Engineer's ReportThiet PhamNo ratings yet

- Airbus vs. Boeing NotesDocument4 pagesAirbus vs. Boeing NotesEsteban AguirreNo ratings yet

- It8586e PDFDocument1 pageIt8586e PDFFacundo TorresNo ratings yet

- Lenovo Ideapad 300-15ISK NM-A481Document1 pageLenovo Ideapad 300-15ISK NM-A481Moriel EverNo ratings yet

- Схема Ресанта Sh Тгр Тпи TopDocument1 pageСхема Ресанта Sh Тгр Тпи TopИльнур ТагировNo ratings yet

- DIGIT - Schematic - PSU SectionDocument1 pageDIGIT - Schematic - PSU Sectionvs055707No ratings yet

- Power Input: IN GND BS Comp EN SS SWDocument10 pagesPower Input: IN GND BS Comp EN SS SWjesurajanNo ratings yet

- MAX8774Document1 pageMAX8774Tim O BrienNo ratings yet

- ZX7 400ivDocument1 pageZX7 400ivRobert CaseNo ratings yet

- Samyung Enc Co.,Ltd.: Front InterfaceDocument1 pageSamyung Enc Co.,Ltd.: Front InterfacejasonelectronicsphilNo ratings yet

- iAMT EC Strapping Need To Check: For IT8541 PowerDocument1 pageiAMT EC Strapping Need To Check: For IT8541 PowerkasimkaNo ratings yet

- Dccon Ir 5065Document34 pagesDccon Ir 5065Phet CopywayNo ratings yet

- Nes 001Document1 pageNes 001luis albertoNo ratings yet

- KTC Mp44010+hr100a+ap3041 (K-Pl-Lo1)Document1 pageKTC Mp44010+hr100a+ap3041 (K-Pl-Lo1)AlejandroBarottiNo ratings yet

- AOC LE32W164 Diagrama Power Board - K-75L2 - K-75L1 - OB2273Document33 pagesAOC LE32W164 Diagrama Power Board - K-75L2 - K-75L1 - OB2273Angel ArebaloNo ratings yet

- Aoc Le32w254dDocument4 pagesAoc Le32w254dVenícius SetubalNo ratings yet

- A2 - KV灯丝控制板1-40-003S REV J SHDocument1 pageA2 - KV灯丝控制板1-40-003S REV J SH易行胜No ratings yet

- 2400 DPA-SchematicsDocument2 pages2400 DPA-SchematicsRicardoNo ratings yet

- PIC16F87X STK v3Document1 pagePIC16F87X STK v3roures76100% (1)

- Input XLR: HF Level (On Backplate)Document2 pagesInput XLR: HF Level (On Backplate)JorgeNo ratings yet

- SRG 1150dnallDocument25 pagesSRG 1150dnallСергей ЧерёмухинNo ratings yet

- fsp488-4f01 Power Supply SCHDocument1 pagefsp488-4f01 Power Supply SCHCarlos Junior PereiraNo ratings yet

- Vestel: Tuner Supply OpsionDocument20 pagesVestel: Tuner Supply OpsionQmichchou JaouadNo ratings yet

- Msi Ms-N7y1 r0.1 SchematicsDocument12 pagesMsi Ms-N7y1 r0.1 SchematicsEnzoNo ratings yet

- 17mb35 2 SemaDocument12 pages17mb35 2 SemaHasan AKNo ratings yet

- Homage Ups SchematicDocument5 pagesHomage Ups Schematicsaif ul noor0% (1)

- VK3HN OLED SchematicDocument1 pageVK3HN OLED Schematicluistorcatt72No ratings yet

- 8885Document1 page8885Oleg SelavinNo ratings yet

- R5F10MMED: Magnetic Sensor (SMD)Document1 pageR5F10MMED: Magnetic Sensor (SMD)yash kumarNo ratings yet

- Hisense FA y LED DriveDocument2 pagesHisense FA y LED Driveatomo33No ratings yet

- FA + Mainboard MSD3463-T5C1 Solo FuenteDocument2 pagesFA + Mainboard MSD3463-T5C1 Solo FuenteFrancisco Antonio100% (1)

- 2050 Control Head Schematics and OverlaysDocument1 page2050 Control Head Schematics and OverlaysDawit LetaNo ratings yet

- Res RP Wdo WP WDI VDDDocument2 pagesRes RP Wdo WP WDI VDDspamail73887No ratings yet

- W5500 SchematicDocument1 pageW5500 SchematicJan Kubala100% (1)

- Max300x - 400X - 700X (SMD)Document1 pageMax300x - 400X - 700X (SMD)Eduardo FingerNo ratings yet

- GD - Out: Nc/Hs Nc/Hs Nc/Hs Nc/HsDocument1 pageGD - Out: Nc/Hs Nc/Hs Nc/Hs Nc/HspedroNo ratings yet

- MT1389 DatasheetDocument1 pageMT1389 Datasheetmckayb138No ratings yet

- Datasheet It8987e PDF FreeDocument1 pageDatasheet It8987e PDF Freemauri kñazovicNo ratings yet

- Datasheet It8987e PDF FreeDocument1 pageDatasheet It8987e PDF Freejhonnattan moreno casilimasNo ratings yet

- Telefunken+Tf Led50s10t2+k PL L01+psuDocument1 pageTelefunken+Tf Led50s10t2+k PL L01+psuRafael DiazNo ratings yet

- 1 4902566775947788782Document1 page1 4902566775947788782Sebastian OrregoNo ratings yet

- K PL L01 PDFDocument1 pageK PL L01 PDFEr Ni100% (1)

- Telefunken TF-LED50S10T2 K-PL-L01 PSUDocument1 pageTelefunken TF-LED50S10T2 K-PL-L01 PSUAndres Alegria0% (1)

- Telefunken - K PL l01 PDFDocument1 pageTelefunken - K PL l01 PDFalextuningNo ratings yet

- K PL L01Document1 pageK PL L01Er NiNo ratings yet

- Sansuitv50 PDFDocument1 pageSansuitv50 PDFalextuningNo ratings yet

- Tiny Reflow ControllerDocument1 pageTiny Reflow Controller31482100% (1)

- SHD Cscec 18 F01 ST SC 01 Ex 05 0007 0000 01 PDFDocument1 pageSHD Cscec 18 F01 ST SC 01 Ex 05 0007 0000 01 PDFMohamed SherifNo ratings yet

- Instant Assessments for Data Tracking, Grade 1: MathFrom EverandInstant Assessments for Data Tracking, Grade 1: MathRating: 4 out of 5 stars4/5 (1)

- Instant Assessments for Data Tracking, Grade 4: MathFrom EverandInstant Assessments for Data Tracking, Grade 4: MathRating: 5 out of 5 stars5/5 (2)

- CajaDocument61 pagesCajaAlcides Huacho OsorioNo ratings yet

- Liebherr LN 252-1 Zinco AltoDocument6 pagesLiebherr LN 252-1 Zinco AltowiroNo ratings yet

- Keep The Heat AnswersDocument6 pagesKeep The Heat AnswersCarl WeinfieldNo ratings yet

- G484 Jan 11Document12 pagesG484 Jan 11samy9387No ratings yet

- HS Weld Spotter - UNI-4550 - ManualDocument1 pageHS Weld Spotter - UNI-4550 - Manualdmh.agent.0077No ratings yet

- Microchannel Heat Exchanger: Prepared byDocument18 pagesMicrochannel Heat Exchanger: Prepared byPritam GoleNo ratings yet

- PMAY G - Model 9Document12 pagesPMAY G - Model 9DanielNo ratings yet

- WSAWLD002Document29 pagesWSAWLD002Nc BeanNo ratings yet

- High Tech Tool CatalogDocument40 pagesHigh Tech Tool CatalogMadirley PimentaNo ratings yet

- Specification For Pressure TransmitterDocument1 pageSpecification For Pressure TransmitterHarish GundaNo ratings yet

- VL250K7 SDDocument6 pagesVL250K7 SDAlexey KolmakovNo ratings yet

- Kuri CONQUERORDocument16 pagesKuri CONQUERORJosh WhiteNo ratings yet

- Intel ChipsetDocument34 pagesIntel Chipsetthsilva85No ratings yet

- Sustainable Architecture and Building Design (SABD) PDFDocument19 pagesSustainable Architecture and Building Design (SABD) PDFShivachandran Sivanesan67% (3)

- SteelDocument20 pagesSteelShashank SaxenaNo ratings yet

- Transcript ID#:6429902) : Page - 1Document5 pagesTranscript ID#:6429902) : Page - 1austinfru7No ratings yet

- Wd-Ra-Pp-Tb100: Drawing Package Revision Level: B GM - Epartsdb - 201806 Last Part Selected WithDocument18 pagesWd-Ra-Pp-Tb100: Drawing Package Revision Level: B GM - Epartsdb - 201806 Last Part Selected WithHilario CruzNo ratings yet

- Price List For Treadmills-Kstar 2021Document50 pagesPrice List For Treadmills-Kstar 2021iReborn YogyakartaNo ratings yet

- Handling of Turbine During EmergencyDocument17 pagesHandling of Turbine During EmergencyManohar Tatwawadi100% (1)

- Clutch - Bleeding Ducati 749Document2 pagesClutch - Bleeding Ducati 749cccoccococNo ratings yet

- CRM Service Contracts Conversions - Usage of Contracts Public ApisDocument16 pagesCRM Service Contracts Conversions - Usage of Contracts Public ApisSridhar YerramNo ratings yet

- ATON1Document42 pagesATON1Firdauz Rahmat100% (1)

- Enterprise Mobility 8-5 Deployment GuideDocument560 pagesEnterprise Mobility 8-5 Deployment GuideAbhay BhardwajNo ratings yet

- BoilerDocument17 pagesBoilerʞǝǝs Uǝ ƎpıɥNo ratings yet

- Primavera P6 EPPM Administrator TrainingDocument3 pagesPrimavera P6 EPPM Administrator TrainingfsüleymanoğluNo ratings yet

- Catálogo Tecno Plastic - Material IS PDFDocument98 pagesCatálogo Tecno Plastic - Material IS PDFsalpica0174770% (1)