Professional Documents

Culture Documents

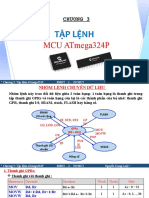

(4pages) - AVR INSTRUCTION SET

(4pages) - AVR INSTRUCTION SET

Uploaded by

Nguyễn Thành Trung0 ratings0% found this document useful (0 votes)

15 views4 pagesOriginal Title

(4pages)_AVR INSTRUCTION SET

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

15 views4 pages(4pages) - AVR INSTRUCTION SET

(4pages) - AVR INSTRUCTION SET

Uploaded by

Nguyễn Thành TrungCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 4

CÁC THANH GHI SFRs

& ĐỊA CHỈ IORs CƠ BẢN

Địa chỉ Tên Địa chỉ Tên Địa chỉ Tên

Bộ nhớ I/O Thanh ghi Bộ nhớ I/O Thanh ghi Bộ nhớ I/O Thanh ghi

0x20 0x00 PINA 0x54 0x34 MCUSR 0x83 Reserved

0x21 0x01 DDRA 0x55 0x35 MCUCR 0x84 TCNT1L và

0x22 0x02 PORTA 0x56 Reserved 0x85 TCNT1H

0x23 0x03 PINB 0x57 0x37 SPMCSR 0x86 ICR1L và

0x24 0x04 DDRB 0x58 0x87 ICR1H

0x25 0x05 PORTB … Reserved 0x88 OCR1AL và

0x26 0x06 PINC 0x5A 0x89 OCR1AH

0x27 0x07 DDRC 0x5B 0x3B RAMPZ 0x8A OCR1BL và

0x28 0x08 PORTC 0x5C Reserved 0x8B OCR1BH

0x29 0x09 PIND 0x5D 0x3D SPL và 0x8C

0x2A 0x0A DDRD 0x5E 0x3E SPH … Reserved

0x2B 0x0B PORTD 0x5F 0x3F SREG 0xAF

0x2C 0x60 WDTCSR 0xB0 TCCR2A

… Reserved 0x61 CLKPR 0xB1 TCCR2B

0x34 0x62 Reserved 0xB2 TCNT2

0x35 0x15 TIFR0 0x63 Reserved 0xB3 OCR2A

0x36 0x16 TIFR1 0x64 PRR0 0xB4 OCR2B

0x37 0x17 TIFR2 0x65 Reserved 0xB5 Reserved

0x38 0x66 OSCCAL 0xB6 ASSR

.. Reserved 0x67 Reserved 0xB7 Reserved

0x3A 0x68 PCICR 0xB8 TWBR

0x3B 0x1B PCIFR 0x69 EICRA 0xB9 TWSR

0x3C 0x1C EIFR 0x6A Reserved 0xBA TWAR

0x3D 0x1D EIMSK 0x6B PCMSK0 0xBB TWDR

0x3E 0x1E GPIOR0 0x6C PCMSK1 0xBC TWCR

0x3F 0x1F EECR 0x6D PCMSK2 0xBD TWAMR

0x40 0x20 EEDR 0x6E TIMSK0 0xBE Reserved

0x41 0x21 EEARL và 0x6F TIMSK1 0xBF Reserved

0x42 0x22 EEARH 0x70 TIMSK2 0xC0 UCSR0A

0x43 0x23 GTCCR 0x71 Reserved 0xC1 UCSR0B

0x44 0x24 TCCR0A 0x72 Reserved 0xC2 UCSR0C

0x45 0x25 TCCR0B 0x73 PCMSK3 0xC3 Reserved

0x46 0x26 TCNT0 0x74 0xC4 UBRR0L và

0x47 0x27 OCR0A … Reserved 0xC5 UBRR0H

0x48 0x28 OCR0B 0x77 0xC6 UDR0

0x49 Reserved 0x78 ADCL và 0xC7 Reserved

0x4A 0x2A GPIOR1 0x79 ADCH 0xC8 UCSR1A

0x4B 0x2B GPIOR2 0x7A ADCSRA 0xC9 UCSR1B

0x4C 0X2C SPCR0 0x7B ADCSRB 0xCA UCSR1C

0x4D 0x2D SPSR0 0x7C ADMUX 0xCB Reserved

0x4E 0x2E SPDR0 0x7D Reserved 0xCC UBRR1L và

0x4F 0x2F Reserved 0x7E DIDR0 0xCD UBRR1H

0x50 0x30 ACSR 0x7F DIDR1 0xCE UDR1

0x51 0x31 OCDR 0x80 TCCR1A 0xCF

0x52 0x32 Reserved 0x81 TCCR1B … Reserved

0x53 0x33 SMCR 0x82 TCCR1C 0xFF

CÁC KÝ HIỆU ĐƯỢC SỬ DỤNG TRONG TẬP LỆNH

Thanh ghi trạng thái SREG và các bit trong thanh ghi

SREG: thanh ghi trạng thái

C: Cờ Carry

Z: Cờ Zero

N: Cờ âm

V: Cờ tràn bù 2

S: Cờ dấu = N ⊕ V

H: Cờ nhớ phân nữa

T: bit sao chép sử dụng trong các lệnh BLD và BST

I: Cờ cho phép/không cho phép ngắt toàn cục

Các thanh ghi và toán hạng trong lệnh

Rd: thanh ghi đích trong tập thanh ghi

Rr: thanh ghi nguồn

R: kết quả sau khi thực thi lệnh

K: hằng số dữ liệu

k: hằng số địa chỉ

b: bit trong tập GPRs hoặc I/O REGs (3-bit)

s: Bit trong SREG (3-bit)

X,Y,Z: T.ghi địa chỉ gián tiếp X=R27:R26,Y=R29:R28,Z=R31:R30

P: địa chỉ các I/O REGs cơ bản.

q: độ dời hoặc địa chỉ trực tiếp (6-bit)

INSTRUCTION SET SUMMARY

Mnemonics Operands Description Operation Flags #Clocks

ARITHMETIC AND LOGIC INSTRUCTIONS

ADD Rd, Rr {d,r: 031} Add two Registers Rd Rd + Rr H,S,V,N,Z,C 1

ADC Rd, Rr {d,r: 031} Add with Carry two Registers Rd Rd + Rr + C H,S,V,N,Z,C 1

ADIW Rdl,K {dl: 24,26,28,30- K:063} Add Immediate to Word Rdh:Rdl Rdh:Rdl + K S,V,N,Z,C 2

SUB Rd, Rr {d,r: 031} Subtract two Registers Rd Rd - Rr H,S,V,N,Z,C 1

SUBI Rd, K {d: 1631, K:0255} Subtract Imemediate from Register Rd Rd - K H,S,V,N,Z,C 1

SBC Rd, Rr {d,r: 031} Subtract with Carry two Registers Rd Rd - Rr - C H,S,V,N,Z,C 1

SBCI Rd, K {d,r: 1631, K:0255} Subtract Imemediate with Carry from Reg. Rd Rd - K - C H,S,V,N,Z,C 1

SBIW Rdl,K {dl: 24,26,28,30- K:063} Subtract Immediate from Word Rdh:Rdl Rdh:Rdl - K S,V,N,Z,C 2

AND Rd, Rr {d,r: 031} Logical AND Registers Rd Rd Rr S,V=0,N,Z 1

ANDI Rd, K {d: 1631, K:0255} Logical AND Register and Constant Rd Rd K S,V=0,N,Z 1

OR Rd, Rr {d,r: 031} Logical OR Registers Rd Rd v Rr S,V=0,N,Z 1

ORI Rd, K {d: 1631, K:0255} Logical OR Register and Constant Rd Rd v K S,V=0,N,Z 1

EOR Rd, Rr {d,r: 031} Exclusive OR Registers Rd Rd Rr S,V=0,N,Z 1

COM Rd {d: 031} One’s Complement Rd 0xFF Rd S,V=0,N,Z,C=1 1

NEG Rd {d: 031} Two’s Complement Rd 0x00 Rd H,S,V,N,Z,C 1

SBR Rd,K {d: 1631, K:0255} Set Bit(s) in Register Rd Rd v K S,V=0,N,Z 1

CBR Rd,K {d: 1631, K:0255} Clear Bit(s) in Register Rd Rd (0xFF - K) S,V=0,N,Z 1

INC Rd {d: 031} Increment Rd Rd + 1 S,V,N,Z 1

DEC Rd {d: 031} Decrement Rd Rd 1 S,V,N,Z 1

TST Rd {d: 031} Test for Zero or Minus Rd Rd Rd S,V=0,N,Z 1

CLR Rd {d: 031} Clear Register Rd Rd Rd S=0,V=0,N=0,Z=1 1

SER Rd {d: 031} Set Register Rd 0xFF None 1

MUL Rd, Rr {d,r: 031} Multiply Unsigned R1:R0 Rd x Rr Z,C 2

MULS Rd, Rr {d,r: 1631} Multiply Signed R1:R0 Rd x Rr Z,C 2

MULSU Rd, Rr {d,r: 1631} Multiply Signed with Unsigned R1:R0 Rd x Rr Z,C 2

FMUL Rd, Rr {d,r: 1623} Fractional Multiply Unsigned R1:R0 (Rd x Rr) << 1 Z,C 2

FMULS Rd, Rr {d,r: 1623} Fractional Multiply Signed R1:R0 (Rd x Rr) << 1 Z,C 2

FMULSU Rd, Rr {d,r: 1623} Fractional Multiply Signed with Unsigned R1:R0 (Rd x Rr) << 1 Z,C 2

BRANCH INSTRUCTIONS

RJMP k {k:-20482047} Relative Jump PC PC + k + 1 None 2

IJMP Indirect Jump to (Z), Z: 03FFFH PC Z None 2

JMP k {k:03FFFH} Direct Jump PC k None 3

RCALL k {k: -20482047} Relative Subroutine Call PC PC + k + 1 None 3

ICALL Indirect Call to (Z) ,Z: 03FFFH PC Z None 3

CALL k {k:03FFFH} Direct Subroutine Call PC k None 4

RET Subroutine Return PC STACK None 4

RETI Interrupt Return PC STACK I 4

CPSE Rd,Rr {d,r: 031} Compare, Skip if Equal if (Rd = Rr) PC PC + 2 or 3 None 1/2/3

CP Rd,Rr {d,r: 031} Compare Rd Rr H,S,V,N,Z,C 1

CPC Rd,Rr {d,r: 031} Compare with Carry Rd Rr C H,S,V,N,Z,C 1

CPI Rd,K {d: 1631, K:0255} Compare Register with Immediate Rd K H,S,V,N,Z,C 1

SBRC Rr, b {r: 031, b:07} Skip if Bit in Register is Cleared if (Rr(b)=0) PC PC + 2 or 3 None 1/2/3

SBRS Rr, b b {r: 031, b:07} Skip if Bit in Register is Set if (Rr(b)=1) PC PC + 2 or 3 None 1/2/3

SBIC P, b {P: 031, b:07} Skip if Bit in I/O Register is Cleared if (P(b)=0) PC PC + 2 or 3 None 1/2/3

SBIS P, b {P: 031, b:07} Skip if Bit in I/O Register is Set if (P(b)=1) PC PC + 2 or 3 None 1/2/3

BRBS s, k {s: 07, k:-6463} Branch if Status Flag Set if (SREG(s) = 1) then PCPC+k + 1 None 1/2

BRBC s, k {s: 07, k:-6463} Branch if Status Flag Cleared if (SREG(s) = 0) then PCPC+k + 1 None 1/2

BREQ = k { k:-6463} Branch if Equal if (Z = 1) then PC PC + k + 1 None 1/2

BRNE k { k:-6463} Branch if Not Equal if (Z = 0) then PC PC + k + 1 None 1/2 KẾT

BRCS k { k:-6463} Branch if Carry Set if (C = 1) then PC PC + k + 1 None 1/2 THÚC

BRCC k { k:-6463} Branch if Carry Cleared if (C = 0) then PC PC + k + 1 None 1/2 DÙNG 1

BRSH k { k:-6463} Branch if Same or Higher -Unsigned if (C = 0) then PC PC + k + 1 None 1/2

CHU KỲ,

BRLO k { k:-6463} Branch if Lower -Unsigned if (C = 1) then PC PC + k + 1 None 1/2

LẶP TIẾP

DÙNG 2

BRMI k { k:-6463} Branch if Minus if (N = 1) then PC PC + k + 1 None 1/2

CHU KỲ

BRPL k { k:-6463} Branch if Plus if (N = 0) then PC PC + k + 1 None 1/2

BRGE > k { k:-6463} Branch if Greater or Equal- Signed if (N V= 0) then PC PC + k + 1 None 1/2

BRLT < k { k:-6463} Branch if Less Than Zero- Signed if (N V= 1) then PC PC + k + 1 None 1/2

BRHS k { k:-6463} Branch if Half Carry Flag Set if (H = 1) then PC PC + k + 1 None 1/2

BRHC k { k:-6463} Branch if Half Carry Flag Cleared if (H = 0) then PC PC + k + 1 None 1/2

BRTS k { k:-6463} Branch if T Flag Set if (T = 1) then PC PC + k + 1 None 1/2

BRTC k { k:-6463} Branch if T Flag Cleared if (T = 0) then PC PC + k + 1 None 1/2

BRVS k { k:-6463} Branch if Overflow Flag is Set if (V = 1) then PC PC + k + 1 None 1/2

BRVC k { k:-6463} Branch if Overflow Flag is Cleared if (V = 0) then PC PC + k + 1 None 1/2

BRIE k { k:-6463} Branch if Interrupt Enabled if ( I = 1) then PC PC + k + 1 None 1/2

BRID k { k:-6463} Branch if Interrupt Disabled if ( I = 0) then PC PC + k + 1 None 1/2

BIT AND BIT-TEST INSTRUCTIONS

SBI P,b {P: 031, b:07} Set Bit in I/O Register I/O(P,b) 1 None 2

CBI P,b {P: 031, b:07} Clear Bit in I/O Register I/O(P,b) 0 None 2

LSL Rd {d: 031} Logical Shift Left Rd(n+1) Rd(n), Rd(0) 0 Z,C,N,V 1

LSR Rd {d: 031} Logical Shift Right Rd(n) Rd(n+1), Rd(7) 0 Z,C,N,V 1

ROL Rd {d: 031} Rotate Left Through Carry Rd(0)C,Rd(n+1) Rd(n),CRd(7) Z,C,N,V 1

ROR Rd {d: 031} Rotate Right Through Carry Rd(7)C,Rd(n) Rd(n+1),CRd(0) Z,C,N,V 1

ASR Rd {d: 031} Arithmetic Shift Right Rd(n) Rd(n+1), n=0..6 Z,C,N,V 1

SWAP Rd {d: 031} Swap Nibbles Rd(3..0)Rd(7..4),Rd(7..4)Rd(3..0) None 1

BSET s {s: 07} Flag Set SREG(s) 1 SREG(s) 1

BCLR s {s: 07} Flag Clear SREG(s) 0 SREG(s) 1

BST Rr, b {r: 031, b:07} Bit Store from Register to T T Rr(b) T 1

BLD Rd, b {d: 031, b:07} Bit load from T to Register Rd(b) T None 1

SEC Set Carry C1 C 1

CLC Clear Carry C0 C 1

SEN Set Negative Flag N1 N 1

CLN Clear Negative Flag N0 N 1

SEZ Set Zero Flag Z1 Z 1

CLZ Clear Zero Flag Z0 Z 1

SEI Global Interrupt Enable I1 I 1

CLI Global Interrupt Disable I 0 I 1

SES Set Signed Test Flag S1 S 1

CLS Clear Signed Test Flag S0 S 1

SEV Set Twos Complement Overflow. V1 V 1

CLV Clear Twos Complement Overflow V0 V 1

SET Set T in SREG T1 T 1

CLT Clear T in SREG T0 T 1

SEH Set Half Carry Flag in SREG H1 H 1

CLH Clear Half Carry Flag in SREG H0 H 1

DATA TRANSFER INSTRUCTIONS

MOV Rd, Rr {d,r:031} Move Between Registers Rd Rr None 1

MOVW Rd, Rr {d,r(0,2,4,..28,30)} Copy Register Word Rd+1:Rd Rr+1:Rr None 1

LDI Rd, K {d:1631, K:0255} Load Immediate Rd K None 1

LD Rd, X {d:031, XR27:R26} Load Indirect Rd (X) None 2

LD Rd, X+ {d:031} Load Indirect and Post-Inc. Rd (X), X X + 1 None 2

LD Rd, - X {d:031} Load Indirect and Pre-Dec. X X - 1, Rd (X) None 2

LD Rd, Y {d:031, YR29:R28} Load Indirect Rd (Y) None 2

LD Rd, Y+ { d:031} Load Indirect and Post-Inc. Rd (Y), Y Y + 1 None 2

LD Rd, - Y { d:031} Load Indirect and Pre-Dec. Y Y - 1, Rd (Y) None 2

LDD Rd,Y+q {d:031, q:063} Load Indirect with Displacement Rd (Y + q) None 2

LD Rd, Z {d:031, ZR31:R30} Load Indirect Rd (Z) None 2

LD Rd, Z+ { d:031} Load Indirect and Post-Inc. Rd (Z), Z Z+1 None 2

LD Rd, -Z { d:031} Load Indirect and Pre-Dec. Z Z - 1, Rd (Z) None 2

LDD Rd, Z+q {d:031, q:063} Load Indirect with Displacement Rd (Z + q) None 2

LDS Rd, k {d:031, k:08FFH} Load Direct from SRAM Rd (k) None 2

ST X, Rr {r:031} Store Indirect (X) Rr None 2

ST X+, Rr {r:031} Store Indirect and Post-Inc. (X) Rr, X X + 1 None 2

ST - X, Rr {r:031} Store Indirect and Pre-Dec. X X - 1, (X) Rr None 2

ST Y, Rr {r:031} Store Indirect (Y) Rr None 2

ST Y+, Rr {r:031} Store Indirect and Post-Inc. (Y) Rr, Y Y + 1 None 2

ST - Y, Rr {r:031} Store Indirect and Pre-Dec. Y Y - 1, (Y) Rr None 2

STD Y+q,Rr {r:031,q:063} Store Indirect with Displacement (Y + q) Rr None 2

ST Z, Rr {r:031} Store Indirect (Z) Rr None 2

ST Z+, Rr {r:031} Store Indirect and Post-Inc. (Z) Rr, Z Z + 1 None 2

ST -Z, Rr {r:031} Store Indirect and Pre-Dec. Z Z - 1, (Z) Rr None 2

STD Z+q,Rr {r:031,q:063} Store Indirect with Displacement (Z + q) Rr None 2

STS k, Rr {r:031, k:08FFH} Store Direct to SRAM (k) Rr None 2

LPM Load Program Memory R0 (Z) None 3

LPM Rd, Z Load Program Memory Rd (Z) None 3

LPM Rd, Z+ Load Program Memory and Post-Inc Rd (Z), Z Z+1 None 3

SPM Store Program Memory (Z) R1:R0 None 3

IN Rd, P {d:031,P:063} In Port Rd P None 1

OUT P, Rr {r:031,P:063} Out Port P Rr None 1

PUSH Rr {r:031} Push Register on Stack STACK Rr None 2

POP Rd {d:031} Pop Register from Stack Rd STACK None 2

MCU CONTROL INSTRUCTIONS

NOP No Operation None 1

SLEEP Sleep (see specific descr. for Sleep function) None 1

WDR Watchdog Reset (see specific descr. for WDR/timer) None 1

BREAK Break For On-chip Debug Only None 1

You might also like

- Báo cáo thực hành điện tử sốDocument31 pagesBáo cáo thực hành điện tử sốkhanhhungno10% (1)

- De-Thi HTDKN HK2 1617Document1 pageDe-Thi HTDKN HK2 1617Phùng Tiến ĐạtNo ratings yet

- Các Thanh Ghi Sfrs & Địa Chỉ Iors Cơ BảnDocument4 pagesCác Thanh Ghi Sfrs & Địa Chỉ Iors Cơ BảnLộc Huỳnh TấnNo ratings yet

- (TomTat) TapLenhAVRDocument6 pages(TomTat) TapLenhAVRBảo NguyễnNo ratings yet

- Tom Tat Tap Lenh AvrDocument6 pagesTom Tat Tap Lenh Avran Nguyễn ThànhNo ratings yet

- Toan Tu Trong AsmDocument6 pagesToan Tu Trong AsmNgô Trung HiếuNo ratings yet

- Lab2 FullDocument26 pagesLab2 Fulldatokno62No ratings yet

- PRELAB5Document77 pagesPRELAB5Tuấn Nguyễn AnhNo ratings yet

- L11 3 Lab 3Document28 pagesL11 3 Lab 3Hào LữNo ratings yet

- Tập lệnh AVR (Hong) (Phần 2)Document33 pagesTập lệnh AVR (Hong) (Phần 2)NAM VŨ PHƯƠNGNo ratings yet

- Ôn Thi TN VXLDocument94 pagesÔn Thi TN VXLkhanguyenthanh27No ratings yet

- Bài tập rèn luyện 3Document7 pagesBài tập rèn luyện 3khoa.nguyen211No ratings yet

- Lab3 1Document24 pagesLab3 1anhngoc.cgt.2012No ratings yet

- Prelab Thinghiembai3 Nhom02 Lopl03 TNVXLDocument25 pagesPrelab Thinghiembai3 Nhom02 Lopl03 TNVXLTài Nguyễn TấnNo ratings yet

- Pre TimerDocument9 pagesPre Timerbuithikiemlien12c2No ratings yet

- Báo Cáo Lab3Document25 pagesBáo Cáo Lab3Bảo NguyễnNo ratings yet

- Lab2 CBDocument38 pagesLab2 CBGdhsjdh HddfffNo ratings yet

- Slide CH3 TapLenhAVR ATmega324PDocument48 pagesSlide CH3 TapLenhAVR ATmega324PQuanNo ratings yet

- L05 Nhom3Document23 pagesL05 Nhom3Duy VoNo ratings yet

- BÁO CÁO THÍ NGHIỆM VI XỬ LÝ BUỔI 2Document14 pagesBÁO CÁO THÍ NGHIỆM VI XỬ LÝ BUỔI 2Tuấn Nguyễn AnhNo ratings yet

- BTVXL Chuong7Document14 pagesBTVXL Chuong7Trịnh Quốc ThànhNo ratings yet

- L10 3 Pre Lab 3Document22 pagesL10 3 Pre Lab 3Hào LữNo ratings yet

- KỸ THUẬT SỐ quoc vietDocument18 pagesKỸ THUẬT SỐ quoc vietVIETNo ratings yet

- tài liệu vi xử líDocument6 pagestài liệu vi xử líDat NguyenNo ratings yet

- 07 - Dinhthoi - 8253 - TimeDocument53 pages07 - Dinhthoi - 8253 - TimeTuấn LươngNo ratings yet

- BTVXL Chuong3Document12 pagesBTVXL Chuong3Trịnh Quốc ThànhNo ratings yet

- L07 8 Pre Lab 3Document21 pagesL07 8 Pre Lab 3haideeptryvnNo ratings yet

- BTC10 VR1Document23 pagesBTC10 VR1datokno62No ratings yet

- PRELAB2Document18 pagesPRELAB2Gdhsjdh HddfffNo ratings yet

- Prelab LAB2 1Document11 pagesPrelab LAB2 1Phạm Bảo MinhNo ratings yet

- PDFSlideC3full TapLenhAVR ATmega324PDocument62 pagesPDFSlideC3full TapLenhAVR ATmega324PLộc Huỳnh TấnNo ratings yet

- BTVXL Chuong10 Nhom1 AN01Document26 pagesBTVXL Chuong10 Nhom1 AN01Trịnh Quốc ThànhNo ratings yet

- Đáp án Bài tập VXL trên lớp (12.04.2023)Document5 pagesĐáp án Bài tập VXL trên lớp (12.04.2023)Trinh Nguyễn NhưNo ratings yet

- Hướng dẫn kết nối với bộ AT-DIO8 - RS485Document3 pagesHướng dẫn kết nối với bộ AT-DIO8 - RS485Ooal GonNo ratings yet

- Hien Thi Ra LCDDocument6 pagesHien Thi Ra LCDbaodang080420004No ratings yet

- L08 Nhóm01Document27 pagesL08 Nhóm01quynh.dinhtin847451No ratings yet

- CHUONG 3 - TAP LENH AVR ATMEGA324P - P1-TrangDocument12 pagesCHUONG 3 - TAP LENH AVR ATMEGA324P - P1-TrangPhan Thành LợiNo ratings yet

- Báo Cáo Lab3Document8 pagesBáo Cáo Lab3Tuấn Nguyễn AnhNo ratings yet

- Chuong 3Document26 pagesChuong 3nguyên trầnNo ratings yet

- Bai 1 - He Thong Dieu Khien Led Đơn, Led 7 Đo NDocument38 pagesBai 1 - He Thong Dieu Khien Led Đơn, Led 7 Đo Nkhánh trần minhNo ratings yet

- ôn tập ktraDocument26 pagesôn tập ktraNhật NamNo ratings yet

- Báo Cáo LAB4 - N8 - L04Document52 pagesBáo Cáo LAB4 - N8 - L04Tài PhanNo ratings yet

- LAB3Document38 pagesLAB3THÀNH NGUYỄN MINHNo ratings yet

- Báo Cáo Thưch Hành Nhóm 1 TDH1 K61Document20 pagesBáo Cáo Thưch Hành Nhóm 1 TDH1 K61vhmanh0357No ratings yet

- L11 6 Lab 3Document34 pagesL11 6 Lab 3Nhật ĐoànNo ratings yet

- TN2# - L05 - Nhóm 2Document39 pagesTN2# - L05 - Nhóm 2Duy VoNo ratings yet

- Báo Cáo AdcDocument14 pagesBáo Cáo AdcHoàng Nam NguyễnNo ratings yet

- Bai Tap TKHTNDocument4 pagesBai Tap TKHTNNhật Đăng Nguyễn ĐìnhNo ratings yet

- Taplenh8051 Va RAMDocument10 pagesTaplenh8051 Va RAMDoan Quoc DuongNo ratings yet

- Giai Bai Tap Chuong 3 - Bai 13-15Document4 pagesGiai Bai Tap Chuong 3 - Bai 13-15Minh NguyễnNo ratings yet

- The Atmega324 Microcontroller: Hardware SummaryDocument41 pagesThe Atmega324 Microcontroller: Hardware SummaryLộc Huỳnh TấnNo ratings yet

- TN#3 NhómL20 T 02Document46 pagesTN#3 NhómL20 T 02Duy VoNo ratings yet

- LAB4Document48 pagesLAB4Duy Vo100% (1)

- VXL KTGK HK231 DE1 DA FinalDocument4 pagesVXL KTGK HK231 DE1 DA Finalcaohieu882001No ratings yet

- De 30Document14 pagesDe 30Phuong NguyenNo ratings yet

- Báo Cáo TNXVL LAB4Document24 pagesBáo Cáo TNXVL LAB4Trịnh Quốc ThànhNo ratings yet

- HongChauNgocTuan Chuong3Document7 pagesHongChauNgocTuan Chuong3Ngoc TuanNo ratings yet

- Slide 7,8,9Document1 pageSlide 7,8,9Nguyễn Thành TrungNo ratings yet

- Lập trình AVR assembly 2 (Update17.03.2023)Document20 pagesLập trình AVR assembly 2 (Update17.03.2023)Nguyễn Thành TrungNo ratings yet

- Lập trình AVR assembly (Hồng) (phần 1)Document14 pagesLập trình AVR assembly (Hồng) (phần 1)Nguyễn Thành TrungNo ratings yet

- KIẾN TRÚC AVR (Hong)Document40 pagesKIẾN TRÚC AVR (Hong)Nguyễn Thành TrungNo ratings yet

- Cổng nối tiếp (phần 1)Document37 pagesCổng nối tiếp (phần 1)Nguyễn Thành TrungNo ratings yet