Professional Documents

Culture Documents

TC554161FTL 70

TC554161FTL 70

Uploaded by

Técnico 04 LógicaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

TC554161FTL 70

TC554161FTL 70

Uploaded by

Técnico 04 LógicaCopyright:

Available Formats

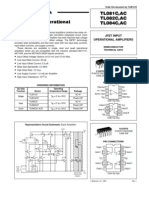

TOSHIBA

1l:554161F1nL/~-70/85/10

SILICON GATE CMOS PRELIMINARY

262,144 WORD x 16 BIT STATIC RAM

Description

The TC554161 FTUTRL is a 4,194,304 bit CMOS static random access memory organized as 262,144 words by 16 bits and

operated from a single 5V power supply. Advanced circuit techniques provide both high speed and low power features with an

operating current of 1OmNMHz (typ.) and a minimum cycle time of lOns. When CE is a logical high, the device is placed in a low

power standby mode in which the standby current is 1O~ (max.). The TC554161 FTUTRL has two control inputs. A chip enable

input (CE) allows for device selection and data retention control, while an output enable input (OE) provides fast memory access.

Byte access is supported by upper and lower byte controls. The TC554161 FTUTRL is suitable for use in microprocessor systems

where high speed, low power, and battery backup are required. The TC554161 FTUTRL is offered in a 54-pin thin small outline

plastic package (forward type, reverse type).

Features Pin Connection (Top View)

• Low power dissipation: 55mW/MHz (typ.)

NC A4 NC

• Standby current: 100~(max.) A3 AS A3

• Single 5V power supply A2 A6 A2

• Access time (max.) Al A7 Al

AO NC AO

TC554161 FTL/TRL 11016 1/01 11016

11015 1102 11015

·70 ·85 ·10 Vee Vee Vee

GNO GNO GNO

Access Time 70ns 85ns 100ns 1/014 1/03 1/014

CE Access Time 70ns 85ns 100ns 1/013 1/04 1/013

US LS US

OE Access Time 35ns 45ns 50ns CE OE CE

NC NC NC

• Power down feature: CE RJW NC R/W

• Data retention supply voltage: 2.0 - 5.5V 1/012 1/05 1/012

• Inputs and outputs TTL compatible 1/011 1/06 1/011

GNO GNO GNO

• Package TC554161 FTL : TSOP54-P-400 Vee Vee Vee

TC554161TRL : TSOP54-P-400A 11010 1/07 11010

1/09 1/08 1109

Pin Names NC AS NC

A17 A9 A17

AO -A17 Address Inputs A16 A10 A16

1/01 - 1/016 Data Input/Output A15 All A15

A14 A12 A14

CE Chip Enable Input A13 NC A13

RIW ReadIWrite Control Input

OE Output Enable Input

LB,UB Data Byte Control Input

Voo Power (+5V)

GND Ground

NC No Connection

TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC. A-141

TC554161 FTLfTR L-70/8511 0 Static RAM

Block Diagram

I>:

+-0 Voo

~~

1>:0

MEMORY

CELL ARRAY

1,024x256x 16

+-0 GND

(4,194,304)

1101

1/02

1/03

1104

1/05

1106

1/08

1/07

1/09

11010

;~~f:::::::~~IZ~

1/011

1/012

1/013

1/014

11015

11016

RNV_~~I

at

~~J±8!§f~~----------------~

rn~~~~~-----------------------J

a o - - - I . - - - < f > - - - CE

Operating Mode

~

MODE

CE OE R/W [8

L

UB

L

1/01 -1/08

Output

1/09 -1/016

Output

POWER

1000

Read L L H H L High Impedance Output 1000

L H Output High Impedance 1000

L L Input Input 1000

Write L * L H L High Impedance Input 1000

L H Input High Impedance 1000

L H H * *

Output Deselect High Impedance High Impedance 1000

L * * H H

Standby H * * * * High Impedance High Impedance loos

* H orL

Maximum Ratings

SYMBOL ITEM RATING UNIT

Voo Power Supply Voltage -0.3 -7.0 V

VIN Input Voltage -0.3* - 7.0 V

Vila Input and Output Voltage -0.5* - Voo + 0.5 V

Po Power Dissipation 0.6 W

TSOLOER Soldering Temperature • Time 260· 10 °C· sec

T STRG Storage Temperature -55 - 150 °C

TOPR Operating Temperature 0-70 °C

* -3.0V with a pulse width of 30ns

A-142 TO$HIBA AMERICA ELECTRONIC COMPONENTS. INC. PRELIMINARY

Static RAM TC554161 FTLlTRL-70/85/1 0

DC Recommended Operating Conditions

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

Voo Power Supply Voltage 4.5 5.0 5.5

V IH Input High Voltage 2.2 - Voo + 0.3

V

V il Input Low Voltage -0.3* - 0.8

V OH Data Retention Supply Voltage 2.0 - 5.5

, -3.0V with a pulse width of 30ns

DC Characteristics (Ta = 0 - 70°C, Voo = 5V±10%)

SYMBOL PARAMETE14 TEST CONDITION MIN. TYP. MAX. UNIT

III Input Leakage Current VIN =0 - Voo - - ±1.0 IlA

CE = V IH or RIW = V il or OE = V IH

ILO Output Leakage Current - - ±1.0 IlA

V OUT = 0 - Voo

10H Output High Current V OH = 2.4V -1.0 - - rnA

10l Output Low Current Val = O.4V 2.1 - - rnA

CE = V ll , lOUT = OrnA Min. - - 100

10001 Other Inputs =VIHN ll teyel e

11ls - 15 -

Operating Current rnA

CE = 0.2V, lOUT = OrnA Min. - - 90

10002 teyel e

Other Inputs = VIHN ll 11ls - 10 -

100S1 CE = V IH , Other Inputs = VIHN ll - - 3 rnA

Standby Current CE =Voo - 0.2V

100S2 - - 100 IlA

Voo = 2.0V - 5.5V

Capacitance* (Ta =25°C, f =1.0MHz)

SYMBOL PARAMETER TEST CONDITION MAX. UNIT

C IN Input Capacitance VIN = GND 10

pF

COUT Output Capacitance V OUT = GND 10

'This parameter is periodically sampled and is not 100% tested.

PRELIMINARY TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC. A-143

TC554161 FTUTRL-70/85/1 0 Static RAM

AC Characteristics (Ta =0 - 70°C, Voo =5V±10O/o)

Read Cycle

TC554161FTlfTRL

SYMBOL PARAMETER -70 -85 -10 UNIT

MIN. MAX. MIN. MAX. MIN. MAX.

tRc Read Cycle Time 70 - 85 - 100 -

tAcc Address Access Time - 70 - 85 - 100

tco CE Access Time - 70 - 85 - 100

tOE OE Access Time - 35 - 45 - 50

tBA UB, LB Access Time - 35 - 45 - 50

tOH Output Data Hold Time from Address Change 10 - 10 - 10 -

ns

tCOE Output Enable Time from CE 10 - 10 - 10 -

tOEE Output Enable Time from OE 5 - 5 - 5 -

tBE Output Enable Time from UB, LB 5 - 5 - 5 -

too Output Disable Time from CE - 25 - 30 - 35

tooo Output Disable Time from OE - 25 - 30 - 35

tBO Output Disable Time from UB, LB - 25 - 30 - 35

Write Cycle

TC554161 FTlfTRL

SYMBOL PARAMETER -70 -85 -10 UNIT

MIN. MAX. MIN. MAX. MIN. MAX.

twc Write Cycle Time 70 - 85 - 100 -

twp Write Pulse Width 50 - 55 - 60 -

tew Chip Enable to End of Write 60 - 70 - 80 -

tBW UB, LB Enable to End of Write 50 - 55 - 60 -

tAS Address Setup Time 0 - 0 - 0 -

ns

tWR Write Recovery Time 0 - 0 - 0 -

tos Data Setup Time 30 - 35 - 40 -

tOH Data Hold Time 0 - 0 - 0 -

tOEW Output Enable Time from RIW 5 - 5 - 5 -

to ow Output Disable Time from RIW - 25 - 30 - 35

AC Test Conditions

Input Pulse Levels 2.4V/0.6V

Input Pulse Rise and Fall Time 5ns

Input Timing Measurement Reference Levels 1.5V

Output Timing Measurement Reference Levels 1.5V

Output Load 1 TTL Gate and C L = 100pF

A-144 TDSHIBA AMERICA ELECTRONIC COMPDNENTS,INC. PRELIMINARY

Static RAM TC554161 FTLlTRL-70/85/10

Timing Waveforms

Read Cycle (1)

ADDRESSES

UB,LB

Dout --------------+-----------~ Output Data Valid

UNKNOWN

Write Cycle 1 (4) (RIW Controlled Write)

ADDRESSES

RIVV

tBW

UB,LB

High Impedance

Dout

Din (5) (5)

PRELIMINARY TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC. A-145

TC554161 FTUTRL-70/85/1 0 Static RAM

Write Cycle 2 (4) (CE Controlled Write)

ADDRESSES

R/W

UB,LB

High Impedance

Dout------------------------~

Din (5) (5)

Write Cycle 3 (4) (UB, LB Controlled Write)

ADDRESSES

UB,LB

Dout------------------------~

Din (5) (5)

A-146 TOSHIBA AMERICA ELECTRONIC CDMPONENTS, INC. PRELIMI~~RY.

Static RAM TC554161 FTLlTRL-70/85/1 0

Notes:

1. RNV is high for read cycles.

2. If the CE low transition occurs coincident with or after the RIW low transition, outputs remain in

a high impedance state.

3. If the CE high transition occurs coincident with or prior to the RIW high transition, outputs remain

in a high impedance state.

4. If OE is high during a write cycle, the outputs are in a high impedance state during this period.

5. The 1/0 may be in the output state during this time; therefore input signals of opposite phase must not be applied.

PRELIMINARY TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC. A-147

TC554161 FTUTRL-70/85/1 0 Static RAM

Data Retention Characteristics (Ta = 0 - 70°C)

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V OH Data Retention Supply Voltage 2.0 - 5.5 V

IOOS2 Standby Current

IV OH = 3.0V - - 50

~

IV OH =5.5V - - 100

tCOR Chip Deselect to Data Retention Mode 0 - - ns

tR Recovery Time 5 - - ms

CE Controlled Data Retention Mode

Voo DATA RETENTION MODE

4.SV

Voo-O.2V

GND

Note:

1. If the V1H of CE is 2.2V in operation, during the period that the Voo voltage is going down from 4.5V to 2.4V, IOOS1

current flows.

A-148 TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC. PRELIMINARY

You might also like

- CH 5 Test BankDocument75 pagesCH 5 Test BankJB50% (2)

- TC554161FTL 70LDocument8 pagesTC554161FTL 70LTécnico 04 LógicaNo ratings yet

- TC551001BPL 70L ToshibaDocument8 pagesTC551001BPL 70L ToshibaKalees WaranNo ratings yet

- FlashMemory-DataSheets Atmel Elenota - PLDocument13 pagesFlashMemory-DataSheets Atmel Elenota - PLriegerautoNo ratings yet

- TC58NVG0S3ETA00Document65 pagesTC58NVG0S3ETA00Freddy AmayaNo ratings yet

- IS61LV2568L: 256K X 8 High-Speed Cmos Static RamDocument14 pagesIS61LV2568L: 256K X 8 High-Speed Cmos Static RamTan Hung LuuNo ratings yet

- 3A Ultra Low Dropout Linear Regulator: General DescriptionDocument12 pages3A Ultra Low Dropout Linear Regulator: General DescriptionLoengrin MontillaNo ratings yet

- EL5166, EL5167: FeaturesDocument16 pagesEL5166, EL5167: FeaturesЕвгений ИвановNo ratings yet

- TC58NVG3S0FTA00Document73 pagesTC58NVG3S0FTA00varimasrNo ratings yet

- EOL Product: HM5216165 SeriesDocument52 pagesEOL Product: HM5216165 SeriesfurqanhamidNo ratings yet

- Description: 2 GBIT (256M × 8 Bit) Cmos Nand E PromDocument65 pagesDescription: 2 GBIT (256M × 8 Bit) Cmos Nand E PromLuis SantosNo ratings yet

- Description: 1G BIT (128M 8 Bit) Cmos Nand E PromDocument52 pagesDescription: 1G BIT (128M 8 Bit) Cmos Nand E PromLuis SantosNo ratings yet

- TC58NVG2S3ETA00Document70 pagesTC58NVG2S3ETA00Freddy AmayaNo ratings yet

- Hy628100alg 70Document9 pagesHy628100alg 70Claudiney BricksNo ratings yet

- Toshiba 8GB NAND TC58NVG3S0FTAI0 PDFDocument73 pagesToshiba 8GB NAND TC58NVG3S0FTAI0 PDFMilan MilenovicNo ratings yet

- Description: 2 GBIT (256M × 8 Bit) Cmos Nand E PromDocument65 pagesDescription: 2 GBIT (256M × 8 Bit) Cmos Nand E Promsuan kwang Tan100% (1)

- TCL Chassis M113 SINGER SCT-29128 - Service - ManualDocument90 pagesTCL Chassis M113 SINGER SCT-29128 - Service - ManualAjith Priyalal75% (4)

- TCL M113 Tmpa8809 MC4406 SMDocument90 pagesTCL M113 Tmpa8809 MC4406 SMYanto LufiNo ratings yet

- HY628400 HynixSemiconductorDocument9 pagesHY628400 HynixSemiconductorHamidNo ratings yet

- TC58NVG1S3BFT00 - TC58NVG1S8BFT00Document37 pagesTC58NVG1S3BFT00 - TC58NVG1S8BFT00Freddy AmayaNo ratings yet

- Cy7c1019cv33 12zcDocument8 pagesCy7c1019cv33 12zcTuhin KarakNo ratings yet

- Single-Channel: 6N138, 6N139 Dual-Channel: HCPL-2730, HCPL-2731 Low Input Current High Gain Split Darlington OptocouplersDocument15 pagesSingle-Channel: 6N138, 6N139 Dual-Channel: HCPL-2730, HCPL-2731 Low Input Current High Gain Split Darlington Optocouplersdevrim.kosalNo ratings yet

- Features General Description: High Input Voltage, Low Quiescent Current, 150ma LDO RegulatorDocument20 pagesFeatures General Description: High Input Voltage, Low Quiescent Current, 150ma LDO RegulatorRoxanaDelcampoNo ratings yet

- Microcomputers, Inc.: RN ( FfirnwDocument4 pagesMicrocomputers, Inc.: RN ( FfirnwPrzemysław WójcikNo ratings yet

- Toshiba-Tc58bvg0s3hta00 C113406Document44 pagesToshiba-Tc58bvg0s3hta00 C113406ivan lopezNo ratings yet

- Description: 2 Gbit (256M × 8 Bit) Cmos Nand E PromDocument53 pagesDescription: 2 Gbit (256M × 8 Bit) Cmos Nand E PromMiguel CastilloNo ratings yet

- Rotel RSP-1066 Service ManuelDocument20 pagesRotel RSP-1066 Service ManuelpiotreNo ratings yet

- TL 084 CNDocument8 pagesTL 084 CNNiranjan kumarNo ratings yet

- TC58NVG2S0FTA00 ToshibaDocument71 pagesTC58NVG2S0FTA00 ToshibaMang Asep BuhoyNo ratings yet

- 2.5-V Integrated Reference Circuit: FeaturesDocument24 pages2.5-V Integrated Reference Circuit: FeaturesAnderson BorgesNo ratings yet

- HCPL 061aDocument19 pagesHCPL 061aMaria TzagarakiNo ratings yet

- Celestion 2-Way 10 Inch MonitorDocument12 pagesCelestion 2-Way 10 Inch MonitorAnthony CuervoNo ratings yet

- Description: 1G BIT (128M 8 Bit) Cmos Nand E PromDocument52 pagesDescription: 1G BIT (128M 8 Bit) Cmos Nand E PromLademir FerreiraNo ratings yet

- Jameco Part Number 871463: Distributed byDocument13 pagesJameco Part Number 871463: Distributed byBrahimiNo ratings yet

- 7SJ64 13.8kV Busbar ProtectionDocument2 pages7SJ64 13.8kV Busbar ProtectionBalajiNo ratings yet

- IS41LV16100B: 1M X 16 (16-Mbit) Dynamic Ram With Edo Page ModeDocument23 pagesIS41LV16100B: 1M X 16 (16-Mbit) Dynamic Ram With Edo Page ModeIldevan JoséNo ratings yet

- HY62V8100B (Rev13) PDFDocument12 pagesHY62V8100B (Rev13) PDFsmhzzNo ratings yet

- El 7104Document7 pagesEl 7104Oscar FernandezNo ratings yet

- 29lv400 Flash EepromDocument24 pages29lv400 Flash Eepromdeimos1No ratings yet

- 128K X 8 Low Power Cmos Static Ram: Description FeaturesDocument11 pages128K X 8 Low Power Cmos Static Ram: Description Featuresvanhuong87No ratings yet

- Description: 1 GBIT (128M × 8 Bits) Cmos Nand EepromDocument34 pagesDescription: 1 GBIT (128M × 8 Bits) Cmos Nand Eeprommiloud1911No ratings yet

- As7c256a 10TCNTR PDFDocument51 pagesAs7c256a 10TCNTR PDFjan ZielinskiNo ratings yet

- OPI1264Document4 pagesOPI12648403c36589584aNo ratings yet

- 16K (2Kx8) Parallel Eeproms AT28C16: FeaturesDocument12 pages16K (2Kx8) Parallel Eeproms AT28C16: FeaturesWilmer OscoNo ratings yet

- Toshiba Confidential Tc58Nvg5D2Fta00: DescriptionDocument65 pagesToshiba Confidential Tc58Nvg5D2Fta00: DescriptionNoel Alejandro Cordova RangelNo ratings yet

- 256K X 4 Static RAM: PreliminaryDocument10 pages256K X 4 Static RAM: PreliminaryedgarlibanioNo ratings yet

- CA3450Document8 pagesCA3450MUHAMMAD SISWANTORONo ratings yet

- Yaskawa GPD 503 Manual PDFDocument160 pagesYaskawa GPD 503 Manual PDFArturo Sánchez100% (2)

- Features: High Performance Pin DriverDocument11 pagesFeatures: High Performance Pin DriverЕвгений ИвановNo ratings yet

- Industrial Inverter Inverter For Air Conditioner IGBT/Power MOSFET Gate Drive IH (Induction Heating)Document9 pagesIndustrial Inverter Inverter For Air Conditioner IGBT/Power MOSFET Gate Drive IH (Induction Heating)El Riz El SammyNo ratings yet

- R1LV1616H-I Series: Wide Temperature Range Version 16 M SRAM (1-Mword × 16-Bit / 2-Mword × 8-Bit)Document21 pagesR1LV1616H-I Series: Wide Temperature Range Version 16 M SRAM (1-Mword × 16-Bit / 2-Mword × 8-Bit)samsularief03No ratings yet

- Pulse-Width-Modulation Control Circuits Az7500EDocument13 pagesPulse-Width-Modulation Control Circuits Az7500EMy shop Cool100% (1)

- HCPL0452, HCPL0453, HCPL0500, HCPL0501, HCPL0530, HCPL0531, HCPL0534 High Speed Transistor OptocouplersDocument9 pagesHCPL0452, HCPL0453, HCPL0500, HCPL0501, HCPL0530, HCPL0531, HCPL0534 High Speed Transistor OptocouplerskarimNo ratings yet

- Eeprom At28c64Document14 pagesEeprom At28c64Manuel FonsecaNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsRating: 5 out of 5 stars5/5 (1)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- 110 Integrated Circuit Projects for the Home ConstructorFrom Everand110 Integrated Circuit Projects for the Home ConstructorRating: 4.5 out of 5 stars4.5/5 (2)

- Project MarketingDocument88 pagesProject MarketingAnkita DhimanNo ratings yet

- Notes On Jean Piaget DeweyDocument2 pagesNotes On Jean Piaget DeweyfadzillahNo ratings yet

- Reading of Electrical Drawings-1 (Power Circuit) : Chapter-13Document23 pagesReading of Electrical Drawings-1 (Power Circuit) : Chapter-13GAGANNo ratings yet

- Fxrate 06 06 2023Document2 pagesFxrate 06 06 2023ShohanNo ratings yet

- Indonesian Sign Language Visualization Model (BISINDO) Website-Based Oral Health On Tooth Brushing Behavior in Deaf ChildrenDocument6 pagesIndonesian Sign Language Visualization Model (BISINDO) Website-Based Oral Health On Tooth Brushing Behavior in Deaf ChildrenInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Online Shop Dengan Norma Subjektif Sebagai Variabel ModerasiDocument13 pagesOnline Shop Dengan Norma Subjektif Sebagai Variabel ModerasiNicky BrenzNo ratings yet

- Arts Lessonplantemplatevisualarts2019Document18 pagesArts Lessonplantemplatevisualarts2019api-451772183No ratings yet

- Lesson 11 Creating A Positive School CultureDocument4 pagesLesson 11 Creating A Positive School CultureLIM CHUNG SZE KPM-GuruNo ratings yet

- Std12 IndCulture TMDocument201 pagesStd12 IndCulture TMTholkappiyan GanesanNo ratings yet

- Competiveness of Sri Lankan Apparel IndustryDocument9 pagesCompetiveness of Sri Lankan Apparel IndustryDanuNo ratings yet

- Testbank ch01Document14 pagesTestbank ch01HườngNo ratings yet

- Make Wire Transfers Through Online Banking From AnywhereDocument2 pagesMake Wire Transfers Through Online Banking From AnywhereDani PermanaNo ratings yet

- Statement of Principle Self-Care Including Self-Medication - The Professional Role of The PharmacistDocument5 pagesStatement of Principle Self-Care Including Self-Medication - The Professional Role of The PharmacistAprilia R. Permatasari0% (1)

- Peb6c5kubDocument6 pagesPeb6c5kubNandar Min HtetNo ratings yet

- SOAL MID TERM ENGLISH 13 Tyad 1Document6 pagesSOAL MID TERM ENGLISH 13 Tyad 1ani julitaNo ratings yet

- Distribution Channel of AMULDocument13 pagesDistribution Channel of AMULMeet JivaniNo ratings yet

- TCS AIP Take Home AssignmentDocument16 pagesTCS AIP Take Home AssignmentShruthiSAthreyaNo ratings yet

- Arizona's Top Kitchen & Bath Remodeling ContractorDocument8 pagesArizona's Top Kitchen & Bath Remodeling ContractorPremier Kitchen and BathNo ratings yet

- Accounting All ChaptersDocument155 pagesAccounting All ChaptersHasnain Ahmad KhanNo ratings yet

- Story As World MakingDocument9 pagesStory As World MakingAugusto ChocobarNo ratings yet

- Machiavellian Reflections (Part 1) : PreambleDocument9 pagesMachiavellian Reflections (Part 1) : PreambleMuhammet Fatih Cantepe100% (1)

- Fizika RadiologijaDocument9 pagesFizika RadiologijaBorislav TapavičkiNo ratings yet

- Pipe Pressure Drope ASEREHDocument3 pagesPipe Pressure Drope ASEREHSenghou MeasNo ratings yet

- Marked Fake Deck Tricks3Document7 pagesMarked Fake Deck Tricks3Tito Banerjee100% (1)

- Activation of Bacterial Spores. A Review': I G RminaDocument7 pagesActivation of Bacterial Spores. A Review': I G RminaJunegreg CualNo ratings yet

- Marketing Channels and Supply Chain ManagementDocument28 pagesMarketing Channels and Supply Chain ManagementGangadhar MamadapurNo ratings yet

- Subcontracting ProcedureDocument36 pagesSubcontracting Procedureswaroopreddyp100% (3)

- A 201Document1 pageA 201AnuranjanNo ratings yet