Professional Documents

Culture Documents

Electronics Prac Manual-2022

Electronics Prac Manual-2022

Uploaded by

Simphiwe MkholwaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Electronics Prac Manual-2022

Electronics Prac Manual-2022

Uploaded by

Simphiwe MkholwaCopyright:

Available Formats

Laboratory Practical Manual

FACULTY : ENGINEERING

DEPARTMENT : ELECTRICAL

QUALIFICATION : NATIONAL DIPLOMA

SUBJECT : ELECTRONICS III

SUBJECT CODE : 080824803

UNIVERSITY CODE : ELET331, ELET138, ECTR202 & ELTR202

Date Revised : January 2022

Revised by : A. Lonappan

NB. 1. This manual must be consulted together with your course guide for detailed

department and institution rules and regulations.

2. All the rules of the laboratory must be adhered to at all times. (Consult the

Control Technician – Laboratories, if in doubt.)

Lecturer : Anil Lonappan

Technician :

Office : A97

Telephone : 031 907 7124

Fax : 031 907 7249

E-mail : lonappan@mut.ac.za

Consultation times : To be discussed with students at beginning of each semester.

SUBJECT LECTURER CONSULTATION TIMES

A. Lonappan Mon: Tue:

Wed: Thurs:

Fri:

Head of Department : Mr. R. C. Foya

Telephone : 031907 7224

Fax No. : 031907 7249

Departmental Secretary : Ms. C. Mthembu

Telephone : 031907 7249

Lectures : Four (4) periods per week

Practical work : Four (4) periods per week

Tutorials : Incorporated into lectures

Lecture venue : Students to be advised at beginning of each semester

Practical work venue : M & C Laboratory

Duration of Course : Sixteen (16) weeks

Electronics III A.Lonappan 2 Jan 2022

LABORATORY SAFETY RULES

1. Conduct yourself in a responsible manner at all times in the laboratory.

2. Follow all written and verbal instructions carefully. If you do not understand a

direction or part of a procedure, ask the Lecturer, Technician or Demonstrator.

3. No student may work in the laboratory without the presence of the Lecturer,

Technician or Demonstrator.

4. When first entering a laboratory, do not touch any equipment until you are instructed

to do so.

5. Perform only those experiments/practicals authorized by your Lecturer. Carefully

follow all instructions, both written and oral.

6. Eating, drinking or chewing gum is strictly prohibited in the laboratory

7. Be prepared for your work in the laboratory. Read all procedures thoroughly before

entering the laboratory. Never fool around in the laboratory. Horseplay, practical jokes, and

pranks are dangerous and prohibited.

8. Observe good housekeeping practices. Work areas should be kept clean and tidy at all

times.

9. Be alert and proceed with caution at all times in the laboratory. Notify the staff

immediately of any unsafe conditions you observe.

10. Labels and equipment instructions must be read carefully before use. Set up and use

the equipment as directed by your Lecturer, Technician or Demonstrator.

11. Know the locations and operating procedures of all safety equipment including: first

aid kit(s), and fire extinguisher. Know where the fire alarm and the exits are located.

12. Dress properly during a laboratory activity. Long hair, dangling jewelry, and loose or

baggy clothing are a hazard in the laboratory. Long hair must be tied back, and dangling

jewelry and baggy clothing must be secured. Shoes must completely cover the foot. No

sandals/open shoes allowed in the laboratory.

13. Report any accident (spill, breakage, etc.) or injury (cut, burn, etc.) to the

Lecturer/Technician immediately, no matter how trivial it seems. Do not panic.

14. If you or your lab partner is hurt, immediately (and loudly) yell out the

Lecturer/Technician's name to get his/her attention. Do not panic!

15. All students should be in possesion of Engineering Safety Commitment Brochure

and should familirise with it.

Electronics III A.Lonappan 3 Jan 2022

LABORATORY SESSION RULES

1. All students should present and work in the respective laboratory session informed at

the beginning of the class.

2. All students should prepare for the experimental work before coming to the laboratory

session.

3. Attendance of the students will be taken during each laboratory session by means of

attendance register.

4. Students are not allowed to enter the laboratory after more than 20 minutes of the start

of the respective laboratory session.

5. Students should submit their practical report exactly one week after attending a

session. No further grace period will not be allocated or entertained in this regard.

6. Submission of practical report will be reconciled with the attendance register for

respective session.

7. If a student has not attended a laboratory session they cannot submit a report.

8. Any other matter with regards to the laboratory session should be brought to the

attention of the lecturer

Electronics III A.Lonappan 4 Jan 2022

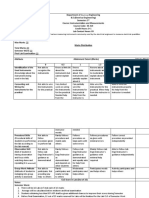

PRACTICAL WORK ASSESSMENT RUBRIC

CRITERIA / EXCELLENT (4) GOOD (3) FAIR (2) POOR (1)

LEVEL

Familiarisation of Student correctly Student correctly answered Student correctly Between 0% and 50 %

theory and answered 90% of the 75% of the questions asked answered 50 % of the

method questions asked questions asked

CRITERIA / EXCELLENT (4) GOOD (3) FAIR (2) POOR (1)

LEVEL

Identification & Student was able to a) Student was able to Struggled to Failed in both aspects

Setting up of identify the required identify the apparatus but identify the

Apparatus apparatus and need minor help in the required apparatus

managed to set the setting up of apparatus and needed help for

apparatus in the b) Struggled to identify setting the

proper way for the but managed to set up the apparatus

required apparatus himself/herself

measurements

CRITERIA / EXCELLENT (4) GOOD (3) FAIR (2) POOR (1)

LEVEL

Method / Student himself Student needed some kind Student managed to a) Student got help from the

Procedure managed to take the of help to get the accurate take the readings tutor, then also the readings are

readings which is and consistent reading himself which are inaccurate/inconsistent

accurate and inaccurate b) Managed to take the

consistent /inconsistent to some readings himself which is

extend inaccurate/ inconsistent.

CRITERIA / EXCELLENT (4) GOOD (3) FAIR (2) POOR (1)

LEVEL

Calculation All the physical Student needed some kind Converted the Failed in the conversion and

quantities are of help in the conversion of quantities to SI calculation.

converted to SI system quantities or calculation, but system but the

of units and did the managed to do it calculation is wrong

calculation

CRITERIA / EXCELLENT (4) GOOD (3) FAIR (2) POOR (1)

LEVEL

Graph Identified the Student needed some kind Student needed some a) Student needed some help in

independent and of help in one of these kind of help in two of three or more of these (

dependent variable, (identifying the dependent these( identifying the identifying the dependent &

got a title for the & independent variable, dependent & independent variable, title of

graph, marked the title of the graph, making independent variable, the graph, making the axes of

axes properly and did the axes of the graph or title of the graph, the graph or calculation (If any)

the calculation from calculation (If any) making the axes of the b) Failed

the graph correctly (If graph or calculation

any) (If any)

CRITERIA / EXCELLENT (4) GOOD (3) FAIR (2) POOR (1)

LEVEL

Presentation of Accurate results Results are not so accurate Results are not at all a) No accuracy in value and

results presented with but the units are accurate accurate but the units units are wrong is wrong

relevant units are fine b) Results are accurate but unit

wrong

Electronics III A.Lonappan 5 Jan 2022

Practical 1 - DESIGN OF A LOW PASS FILTER

Objective of the practical

Aim:

To design and test a low pass filter using op-amp

Apparatus required:

1) Op-Amp (μA - 741)- 2 No’s

2) DC Power Supply ( 1 2 - 0 - 12) V

3) CRO (0-20MHz range)

4) Signal Generator (0 to 1MHz range)

5) Bread board

6) Resistors and capacitors

Circuit diagram

The filter has a constant gain from 0Hz to a high cut-off frequency fH. At fH the gain is down

by 3dB; after f>fH the gain decreses with an increase in input frequency at a rate of -20dB per

decade. The frequencies between 0Hz and fH are known as pass band freqncies, where as the

range of frequncies those beyond fH are called stop band frequencies.

Design Procedure:

1. Select high cut-off frequency fH of the filter. Let fH = 700Hz

2. Select value of C less than 1µF. (As the maximum value of ceramic capacitor availble

is 1µF). Let C=0.01µF

Electronics III A.Lonappan 6 Jan 2022

3. Calculate R from Equation 1.

fH = 1/2πRC - (1)

For fH = 700Hz and C = 0.01µF from Eq. (1) R = 22.7kΩ

Select nearest value of standard resistance availble R = 22kΩ

4. Select R1 and RF such that required pass band gain is obtained

Pass band gain = 1+(RF/R1)

Let R1= RF= 10kΩ for a pass band gain of 2

5. Final values of components

R1 = 10kΩ, RF = 10kΩ, R= 22kΩ, C = 0.01µF, fH=700Hz

Lowpass filter experimental procedure:

1. Vary the input frequency at regular intervals and note down the output response from

the CRO.

2. Calculate the gain in dB.

3. Verify practical and theoretical cutoff frequency

4. Plot the frequency response on semi-log sheet

Frequency response

Electronics III A.Lonappan 7 Jan 2022

Practical 2 - DESIGN OF A HIGH PASS FILTER

Objective of the practical

Aim:

To design and test a high pass filter using op-amp

Apparatus required:

1) Op-Amp (μA - 741)- 2 No’s

2) DC Power Supply ( 1 2 - 0 - 12) V

3) CRO (0-20MHz range)

4) Signal Generator (0 to 1MHz range)

5) Bread board

6) Resistors and capacitors

Circuit diagram

The filter has a constant gain above the low cut-off frequency fL. At fL the gain is down by

3dB the pass band gain; below f<fL the gain decreses in input frequency at a rate of -20dB per

decade. The frequencies above fL are known as pass band freqncies, where as the range of

frequncies from 0Hz to fL are called stop band frequencies..

Design Procedure:

1. Select high cut-off frequency fL of the filter. Let fL = 700Hz

2. Select value of C less than 1µF. (As the maximum value of ceramic capacitor availble

is 1µF). Let C=0.01µF

3. Calculate R from Equation 1.

Electronics III A.Lonappan 8 Jan 2022

fL= 1/2πRC - (1)

For fL = 700Hz and C = 0.01µF from Eq. (1) R = 22.7kΩ

Select nearest value of standard resistance availble R = 22kΩ

4. Select R1 and RF such that required pass band gain is obtained

Pass band gain = 1+(RF/R1)

Let R1= RF= 10kΩ for a pass band gain of 2

5. Final values of components

R1 = 10kΩ, RF = 10kΩ, R= 22kΩ, C = 0.01µF, fL=700Hz

High pass filter experimental procedure:

1. Vary the input frequency at regular intervals and note down the output response from

the CRO.

2. Calculate the gain in dB.

3. Verify practical and theoretical cutoff frequency

4. Plot the frequency response on semi-log sheet

Frequency response

Electronics III A.Lonappan 9 Jan 2022

Practical 3 - DESIGN OF A HIGHER-ORDER FILTER

Objective of the practical

Aim:

To design and test a higher order filter using op-amp

Apparatus required:

1) Op-Amp (μA - 741)- 2 No’s

2) DC Power Supply ( 1 2 - 0 - 12) V

3) CRO (0-20MHz range)

4) Signal Generator (0 to 1MHz range)

5) Bread board

6) Resistors and capacitors

Circuit diagram

For these first-order low-pass and high-pass filters, the gain rolls off at the rate of about

20dB/decade in the stop band. In critical applications (such as digitization, which needs the

flattest response possible in the pass band and most sharply-defined stop band) a higher-order

filter is a necessity. The following diagram shows a second-order low-pass filter (it’s second

order because it contains two low-pass filters). Put it together and measure its gain versus

frequency. Use R2=R3≈3.9 kΩ. Fill the table below and graph your results.

Electronics III A.Lonappan 10 Jan 2022

Tabulation

Gain in dB = 20log(Vout/Vin)

Frequency (Hz) Input amplitude (V) Output amplitude (V) Gain in dB

200

500

1000

2000

5000

10k

20k

50k

100k

Electronics III A.Lonappan 11 Jan 2022

Practical 4 - DESIGN OF A BAND-PASS FILTER

Objective of the practical

Aim:

To design and test a band pass filter using op-amp

Apparatus required:

1) Op-Amp (μA - 741)- 2 No’s

2) DC Power Supply ( 1 2 - 0 - 12) V

3) CRO (0-20MHz range)

4) Signal Generator (0 to 1MHz range)

5) Bread board

6) Resistors and capacitors

Circuit diagram

Band pass filters can be formed by simply "cascading" high-pass and low-pass sections (that

is, put the output of one into the input of the next). Each section resembles the filter in the

previous section (the high-pass versions have their capacitors and resistors interchanged from

their positions in the low pass filter). We can also make a band-pass filter in one section:

The RC combination R4 and C2 is a high-pass filter, which will determine the lower cutoff

frequency. Try R4=1kΩ, and C2 = C3 = 0.01μF, R2=R3≈3.9 kΩ, R1=RF =RL=10 kΩ. Carry out

measurements and fill the following Table and graph your result.

Electronics III A.Lonappan 12 Jan 2022

Tabulation

Table: band pass filter gain in dB =20log(Vout/Vin)

Frequency (Hz) Input amplitude (V) Output amplitude (V) Gain in dB

200

500

1000

2000

5000

10k

20k

50k

100k

Electronics III A.Lonappan 13 Jan 2022

Practical 5 - ACTIVE LOW PASS & HIGH PASS

BUTTERWORTH FILTERS (2nd ORDER)

Objective of the practical

Aim:

To plot the frequency response of Butterworth LPF (Second order) and find the high cut-off

frequency.

Apparatus required

1) Bread Board

2) Function Generator

3) CRO

4) Probes

5) Connecting Wires

6) 741 Op-amp

7) Resistors, Capacitors

Circuit diagram

Filters are classified as follows:

Based on components used in the circuit

Active filters – Use active elements like transistor or op-amp(provides gain) in

addition to passive elements

Electronics III A.Lonappan 14 Jan 2022

Passive filters – Use only passive elements like resistors, capacitors and inductors,

hence no gain here.

Based on frequency range

Low pass filter (LPF) – Allows low frequencies

High pass filter (HPF) – Allows high frequencies

Band pass filter (BPF) – Allows band of frequencies

Band reject filter (BRF) – Rejects band of frequencies

All pass filter – Allows all frequencies but with a phase shift

Active Filter is often a frequency – selective circuit that passes a specified band of

frequencies and blocks or attenuates signals of frequencies outside this band. These Active

Filters are most extensively used in the field of communications and signal processing. They

are employed in one form or another in almost all sophisticated electronic systems such as

Radio, Television, Telephone, Radar, Space Satellites, and BioMedical Equipment. Active

Filters employ transistors or Op – Amps in addition to that of resistors and capacitors. Active

filters have the following advantages over passive filters. (1) Flexible gain and frequency

adjustment. (2) No loading problem (because of high input impedance and low output

impedance) and (3) Active filters are more economical than passive filters. A Second –

Order Low – Pass Butterworth filter uses RC networks for filtering. Note that the op-amp is

used in the non-inverting configuration; hence it does not load down the RC network.

Resistors R1 and RF determine the gain of the filter.

The gain magnitude equation of the Low – Pass filter can be obtained by converting

equation into its equivalent polar form, as follows.

AF

| Vo / Vin | =

4

f

1

fH

where

1

fH = = high cut-off frequency of the filter.

2 R2 R3C 2 C3

The operation of the low – pass filter can be verified from the gain magnitude equation.

1. At very low frequencies, that is f < fH

| Vo/Vin | = AF

2. At f = fH

|Vo/Vin | = AF/√2 = 0.707 AF

3. At f > fH

| Vo/Vin | < AF

Electronics III A.Lonappan 15 Jan 2022

Thus the Low – Pass filter has a constant gain AF from 0 Hz to the almost high cut-

off frequency, fH, it has the gain 0.707AF at exactly fH, and after fH it decreases at a constant

rate with an increase in frequency. The gain decreases 40 dB (= 20 log 102) each time the

frequency is increased by 10. Hence the rate at which the gain rolls off after fH is 40

dB/decade. The frequency f = fH is called the cut-off frequency because the gain of the filter

at this frequency is down by 3 dB (= 20log 0.707) from 0 Hz. Other equivalent terms for cut-

off frequency are -3dB frequency, break frequency, or corner frequency.

Design Procedure

1. Choose a value for the high cut-off frequency, fH (1 kHz)

2. To simplify the design calculations, set R2 = R3= R and C2 = C3 = C. Then choose a

value of C 1µF(0.0047 µF)

3. Calculate the value of R using the equation

1

R

2Cf H

4. Finally, because of the equal resistor (R2 = R3) and capacitor (C2 = C3) values, the

Rf

pass band voltage gain AF = (1+ ) of the second-order low-pass filter has to be

R1

equal to 1.586. That is, Rf = 0.586R1. This gain is necessary to generate Butterworth

response. Hence choose a value of R1 100 kΩ (33 kΩ) and calculate the value of Rf.

Procedure

1. Connect the components/equipment as shown in the circuit diagram.

2. Switch ON the power supply.

3. Connect channel -1 of CRO to input terminals (Vin) and channel -2 to output

terminals (Vo).

4. Set Vin = 1V & fin=10 Hz using function generator.

5. By varying the input frequency in regular intervals, note down the output voltage.

6. Calculate the gain (Vo/Vin) and Gain in dB = 20 log (Vo/Vin) at every frequency.

7. Plot the frequency response curve (taking frequency on X-axis & Gain in dB on

Yaxis) using Semi log Graph.

8. Find out the high cut-off frequency, fH (at Gain= Constant Gain, AF – 3 dB) from the

frequency response plotted.

9. Verify the practical (fH from graph) and the calculated theoretical cut-off frequency

(fH = 1/2πRC ).

Electronics III A.Lonappan 16 Jan 2022

Expected result

Tabulation

Vin = 1 V

Input frequency f (Hz) Output Voltage VO (V) Gain Magnitude Gain in dB

| Vo/Vin | 20log| Vo/Vin |

Calculations

Theoretical cut-off frequency

fH = 1 / (2πRC) = high cut-off frequency of the Low pass filter.

=

Practical cut-off frequency (from Graph)

fH = high cut-off frequency of the Low pass filter = 3dB cut-off frequency

Electronics III A.Lonappan 17 Jan 2022

Practical 6 – DESIGN OF AN INSTRUMENTATION

AMPLIFIER

Objective of the practical

Aim:

To study the operation of an instrumentation amplifier using op-amps.

Apparatus required:

1) Op-Amp (μA - 741)- 3 No’s

2) DC Power Supply ( 1 2 - 0 - 12) V

3) CRO (0-20 MHz range)

4) Bread board

5) Resistors

6) Probes

7) Connecting wires

The instrumentation amplifier is the popular preamplifier for signal conditioning. It offers

high impedance and common mood rejection ratio (CMRR). It composes of three amplifiers.

The gain of the amplifier is determined by the resistor network based on the rules of ideal

operational amplifier.

Circuit diagram

Electronics III A.Lonappan 18 Jan 2022

Design

VO 2R

1 2

V2 V1 R1

Assume R3 = R4 = R2

VO = k (V2 –V1) where k = 1+2R2/R1

Experimental procedure:

1. Connect the components/equipment as shown in the circuit diagram.

2. Switch ON the power supply.

3. Connect channel-1 of CRO at the input terminals and channel-2 at the output terminals.

5. Now apply the input signal.

7. Observe the output of the circuit on the CRO and note down the position, the amplitude

and the time period of V1, V2 & Vo.

8. Plot the output voltages.

Electronics III A.Lonappan 19 Jan 2022

Practical 7 - INTEGRATOR USING OP-AMP

Objective of the practical

Aim:

To study the operation of the Integrator using op-amp and trace the output wave forms for

sine and square wave inputs.

Apparatus required:

1) Op-Amp (μA - 741)- 2 No’s

2) DC Power Supply ( 1 2 - 0 - 12) V

3) CRO (0-20MHz range)

4) Signal Generator (0 to 1MHz range)

5) Bread board

6) Resistors and capacitors

7) Probes

8) Connecting wires

Integrator

A circuit in which the output voltage is the integration of the input voltage is called an

integrator.

In the practical integrator to reduce the error voltage at the output, a resistor RF is connected

across the feedback capacitor CF. Thus, RF limits the low-frequency gain and hence

minimizes the variations in the output voltage.

Electronics III A.Lonappan 20 Jan 2022

The frequency response of the integrator is shown in the figure fb is the frequency at which the

gain is 0 dB and is given by fb = 1/2R1Cf.

In this fig. there is some relative operating frequency, and for frequencies from f to fa the gain

RF/R1 is constant. However, after fa the gain decreases at a rate of 20 dB/decade. In other

words, between fa and fb the circuit of fig. 2.1 acts as an integrator. The gain limiting

frequency fa is given by

fa = 1/2RfCf.

Normally fa<fb. From the above equation, we can calculate Rf by assuming fa & Cf. This is

very important frequency. It tells us where the useful integration range starts. If f in < fa -

circuit acts like a simple inverting amplifier and no integration results, If fin = fa - integration

takes place with only 50% accuracy results,

If fin = 10fa - integration takes place with 99% accuracy results.

In the circuit diagram of Integrator, the values are calculated by assuming fa as 50Hz. Hence

the input frequency is to be taken as 500Hz to get 99% accuracy results.

Integrator has wide applications in

1. Analog computers used for solving differential equations in simulation arrangements.

2. A/D Converters

3. Signal wave shaping

4. Function Generators.

Circuit diagram

Circuit diagram of a Intergrator

Electronics III A.Lonappan 21 Jan 2022

Intergrator experimental procedure:

1. Connect the components/equipment as shown in the circuit diagram.

2. Switch ON the power supply.

3. Apply sine wave at the input terminals of the circuit using function Generator.

4. Connect channel-1 of CRO at the input terminals and channel-2 at the output terminals.

5. Observe the output of the circuit on the CRO which is a cosine wave (90o phase shifted

from the sine wave input) and note down the position, the amplitude and the time period of

Vin & Vo.

6. Now apply the square wave as input signal.

7. Observe the output of the circuit on the CRO which is a triangular wave and note down the

position, the amplitude and the time period of Vin & Vo.

8. Plot the output voltages corresponding to sine and square wave inputs.

Expected waveforms:

Electronics III A.Lonappan 22 Jan 2022

Practical 8 - DIFFERENTIATOR USING OP-AMP

Objective of the practical

Aim:

To study the operation of the differentiator using op-amp and trace the output wave forms for

sine and square wave inputs.

Apparatus required:

1) Op-Amp (μA - 741)- 2 No’s

2) DC Power Supply ( 1 2 - 0 - 12) V

3) CRO (0-20MHz range)

4) Signal Generator (0 to 1MHz range)

5) Bread board

6) Resistors and capacitors

7) Probes

8) Connecting wires

Differentiator:

As the name suggests, the circuit performs the mathematical operation of differentiation,

i.e. the output voltage is the derivative of the input voltage. Vo = - Rf C1 dVin/dt

Both the stability and the high-frequency noise problems can be corrected by the addition of

two components: R1 and Cf, as shown in the circuit diagram. This circuit is a practical

differentiator.

The input signal will be differentiated properly if the time period T of the input signal is

larger than or equal to RfC1. That is, T>= RfC1

Differentiator can be designed by implementing the following steps.

1. Select fa equal to the highest frequency of the input signal to be differentiated. Then,

assuming a value of C1<1 F, calculate the value of Rf

2. Calculate the values of R1and Cf so that R1C1=RfCf.

3. Differentiator has wide applications in 1. Monostable Multivibrator 2. Signal wave

shaping 3. Function Generators.

Electronics III A.Lonappan 23 Jan 2022

Circuit diagram

Circuit diagram of a Differentiator

Differentiator experimental procedure:

1. Connect the components/equipment as shown in the circuit diagram.

2. Switch ON the power supply.

3. Apply sine wave at the input terminals of the circuit using function Generator.

4. Connect channel-1 of CRO at the input terminals and channel-2 at the output terminals.

5. Observe the output of the circuit on the CRO which is a cosine wave (90o phase shifted

from the sine wave input) and note down the position, the amplitude and the time period of

Vin & Vo.

6. Now apply the square wave as input signal.

7. Observe the output of the circuit on the CRO which is a spike wave and note down the

position, the amplitude and the time period of Vin & Vo.

8. Plot the output voltages corresponding to sine and square wave inputs.

Electronics III A.Lonappan 24 Jan 2022

Expected waveforms: Differentiator

Electronics III A.Lonappan 25 Jan 2022

Practical 9 - DESIGN OF A RC.PHASE SHIFT

OSCILLATOR

Objective of the practical

Aim:

To design and test the RC Phase shift Oscillator for the frequency of 1kHz.

Apparatus required:

1) Transistor (BC 107)

2) DC Power Supply ( 1 2 - 0 - 12) V

3) CRO (0-20MHz range)

4) Bread board

5) Resistors and capacitors

Design Procedure

VCC = 12V

IC = 2mA

VRC = 40% VCC = 4.8V

VRE = 10% VCC = 1.2V

VCE = 50% VCC = 6V

To find RC, R1, RE & R2

We have,

VRC = ICRC=4.8V

RC = 2.4kΩ

Choose RC = 2.2kΩ

VRE = IERE=1.2V

RE = 600Ω

Choose RE = 680Ω

hfe = 100 (For BC 107)

IB= IC/ hfe = 20mA

Assume current through R1 = 10IB & through R2 = 9IB

VR1 = VCC-VR2

= 10V

Also,

VR1 =10IBR1=10.1V

R1= 50kΩ

Choose R1= 47kΩ

VR2 = VBE+VRE

= 0.7+1.2

= 1.9V

Also,

Electronics III A.Lonappan 26 Jan 2022

VR2 =9IBR2=1.9V

R2= 10.6kΩ

Choose R1= 12kΩ

To find CC & CE

XCE = 1/2πCE=(1/10)RE = 680/10= 68Ω

For

υ = 20Hz

CE= 117µF

Choose CE = 220µF

XCC =1/2πCC = RC/10=220Ω

For

υ = 20Hz

Choose CC = 47 µF

Design of υ Selective Circuit

Required υ of oscillations f = 1kHz

1

f=

2R C 6

4 RC

R

Take R= 4.7kΩ & C=0.01μF

Circuit diagram of a RC phase shift ocillator

Electronics III A.Lonappan 27 Jan 2022

RC phase shift ocillator experimental procedure:

1. Rig up the circuit as shown in the figure

2. Observe the sinusoidal output voltage

3. Measure the frequency and compare with the theoretical values

Result:

Frequency

Theoretical: 1kHz

Practical: _________

Electronics III A.Lonappan 28 Jan 2022

Practical 10 - DESIGN OF A CRYSTAL OSCILLATOR

Objective of the practical

Aim:

To design and test the performance of BJT - Crystal Oscillator for fO >100kHz

Apparatus required:

1) Crystal 2MHz

2) Transistor (SL100)

3) DC Power Supply ( 1 2 - 0 - 12) V

4) CRO (0-20MHz range)

5) Bread board

6) Resistors and capacitors

Design Procedure

Given VCC = 10V, β = 200, IC = 2mA

To find RE

VRE =VCC/10 = 10/10 = 1V

IERE = 1, IE≈ IC

RE = VRE/IC= 1/2mA= 500Ω

Choose RE =470Ω

To find RC

Applying KVL

VCC – ICRC - VCE- VRE = 0 (VCE = VCC/2)

10 – 2X10-3RC – 5 – 1 = 0

4 - 2X10-3RC = 0

RC = 2kΩ

Choose RC = 2.2kΩ

From the biasing circuit

VB = VBE + VRE

= 0.7 + 1

= 1.7V

To find IB

IB = IC/ β = 2X10-3/200= 0.01mA

Assume 10IB flows through R1

R1 =VCC-VB/10IB = 10-1.7/10X0.01mA= 83kΩ

Choose R1 = 82kΩ

Electronics III A.Lonappan 29 Jan 2022

Assume 9IB flows through R2

R2 =VB/9IB =1.7/9X0.01mA = 18kΩ

Choose R2 = 18kΩ

Assume coupling capacitor CC1 and CC2 as 0.47μF

Circuit diagram of crystal oscillator

Electronics III A.Lonappan 30 Jan 2022

Crystal oscillator experimental procedure:

1. Make the connections as shown in circuit diagram

2. Vary 1kΩ potentiometer so as to get an undistorted sine wave at the output

3. Note down the frequency of the output wave and compare it with the theoretical frequency

of oscillation

Result:

Frequency

Theoretical: 2MHz

Practical: _________

Electronics III A.Lonappan 31 Jan 2022

Practical 11 - DESIGN OF A FET HARTLEY

OSCILLATOR

Objective of the practical

Aim:

To design and test the performance of a Hartley Oscillator for given frequency using FET

Apparatus required:

1) FET (BFW11)

2) DC Power Supply ( 1 2 - 0 - 12) V

3) CRO (0-20MHz range)

4) Bread board

5) Resistors and capacitors

Design Procedure

Biasing Circuit

Electronics III A.Lonappan 32 Jan 2022

VDD = 10V, VDS =VDD/2 =5V

For υ FET, IDSS = 11.5mA

VP = -3V

VGS = -1.7V

ID = IDSS [1-VGS/VP]2

ID = 11.5X10-3[1-1.7/3]2

ID = 2mA

Applying KVL to the outer loop

VDD = ID(RD + RS ) + VDS

RD + RS = VDD-VDS/ID= 2.1kΩ

Let RD = 1kΩ & RS = 1.5kΩ

Use 1k pot in series with 1.5kΩ for RS

VDDR2/(R1+R2) = VGS+VRS

R2/(R1+R2) = (VGS+IDRS)/VDD = [-1.7+(2X10-3)1.5X103]/10 = 0.13

R2 = 0.13R1 + 0.13R2

0.87R2 = 0.13R1

R2/R1=0.13/0.87= 0.149

R1= 1MΩ

R2= 0.149R1

R1= 150kΩ

Choose R2 as 82kΩ

Tank Circuit Design

1

fO = Where L = L1 + L2

2 LC

fO = 100kHz

1

L=

4 f O C

2 2

Let C = 330pF

1

L=

4 X (3.14) X (100 X 10 3 ) 2 X 330 X 10 12

2

L = 7.68mH

L1 = 5mH

L2 = 2.6mH

Electronics III A.Lonappan 33 Jan 2022

Circuit diagram of a Hartley Oscillator

Electronics III A.Lonappan 34 Jan 2022

Hartley Oscillator experimental procedure:

1. Make the connections as shown in circuit diagram

2. Observe the sinusoidal output voltage

3. Measure the frequency and compare with the theoretical values

Result:

Theoretical Frequency : 100kHz

Practical Frequency :

Amplitude of the sine wave :

Electronics III A.Lonappan 35 Jan 2022

Practical 12 - DESIGN OF A COLPITTS OSCILLATOR

Objective of the practical

Aim:

To design and test the performance of a Colpitts Oscillator for given frequency using FET

Apparatus required:

1) FET (BFW11)

2) DC Power Supply ( 1 2 - 0 - 12) V

3) CRO (0-20MHz range)

4) Bread board

5) Resistors and capacitors

Design Procedure

Biasing Circuit

VDD = 10V, VDS =VDD/2 =5V

For υ FET, IDSS = 11.5mA

Electronics III A.Lonappan 36 Jan 2022

VP = -3V

VGS = -1.7V

ID = IDSS [1-VGS/VP]2

ID = 11.5X10-3[1-1.7/3]2

ID = 2mA

Applying KVL to the outer loop

VDD = ID(RD + RS ) + VDS

RD + RS = VDD-VDS/ID= 2.1kΩ

Let RD = 1kΩ & RS = 1.5kΩ

Use 1k pot in series with 1.5kΩ for RS

VDDR2/(R1+R2) = VGS+VRS

R2/(R1+R2) = (VGS+IDRS)/VDD = [-1.7+(2X10-3)1.5X103]/10 = 0.13

R2 = 0.13R1 + 0.13R2

0.87R2 = 0.13R1

R2/R1=0.13/0.87= 0.149

R1= 1MΩ

R2= 0.149R1

R1= 150kΩ

Choose R2 as 82kΩ

Tank Circuit Design

1

fO = Where Ceq = C1C2/(C1+C2)

2 LC eq

fO = 100kHz

1000 X 2200 X 10 24

C=

1000 2200X 10 12

C= 687.5pF

1

L=

4 f O2 C

2

1

L=

4 X (3.14) X (100 X 10 3 ) 2 X 687.5 X 10 12

2

L = 3.6mH

Electronics III A.Lonappan 37 Jan 2022

Circuit diagram of a Colpitts Oscillator

Electronics III A.Lonappan 38 Jan 2022

Colpitts Oscillator experimental procedure:

1. Make the connections as shown in circuit diagram

2. Observe the sinusoidal output voltage

3. Measure the frequency and compare with the theoretical values

Result:

Theoretical Frequency : 100kHz

Practical Frequency :

Amplitude of the sine wave :

Electronics III A.Lonappan 39 Jan 2022

You might also like

- EIM Exploratory's DLL (Lesson 1 - LO1-LO2 Week 1) (1) EportfolioDocument19 pagesEIM Exploratory's DLL (Lesson 1 - LO1-LO2 Week 1) (1) EportfolioAngelo Arriola93% (27)

- RevD - RetCam Envision Spec Sheet - EN - Lo-ResDocument2 pagesRevD - RetCam Envision Spec Sheet - EN - Lo-ResOmar Esneiber Torres CarvajalNo ratings yet

- Caterpillar 740 Electric SchematicDocument7 pagesCaterpillar 740 Electric SchematicAdhont100% (1)

- PW5 Basic Double Busbar Dis 20Document12 pagesPW5 Basic Double Busbar Dis 20Shanthiyaah ArumugamNo ratings yet

- Daily Lesson Log C++ ProgrammingDocument3 pagesDaily Lesson Log C++ ProgrammingRhexel ReyesNo ratings yet

- PW 5Document7 pagesPW 5NandakishhoreNo ratings yet

- CAED Lab Manual Safia TahirDocument71 pagesCAED Lab Manual Safia Tahirzubair tahirNo ratings yet

- Electrical Engineering Department ACADEMIC SESSION: - Dec40073-Database SystemDocument26 pagesElectrical Engineering Department ACADEMIC SESSION: - Dec40073-Database Systemiskandardaniel0063No ratings yet

- Lesson Plan - TLE ElectricityDocument3 pagesLesson Plan - TLE ElectricityStyrich Nyl AbayonNo ratings yet

- Electronic Final 01Document56 pagesElectronic Final 01zubair tahirNo ratings yet

- Camarines Norte College of Arts and Business Bagong Silang 1, Labo, Camarines Norte Name: - DateDocument37 pagesCamarines Norte College of Arts and Business Bagong Silang 1, Labo, Camarines Norte Name: - Datejoy visitacionNo ratings yet

- Lab Sheet PW6 Jun 2017Document12 pagesLab Sheet PW6 Jun 2017Muhd FaizNo ratings yet

- Stu 1st Pages LCSDocument15 pagesStu 1st Pages LCSmunaamahmad222No ratings yet

- EE353SP15 FinalDocument5 pagesEE353SP15 FinalSyedZain1993No ratings yet

- K To 12 Electronics Learning Module Student FileDocument126 pagesK To 12 Electronics Learning Module Student FileCastillo, Warner John F.No ratings yet

- Electrical Engineering Department: Course: Dee30043 Electronic CircuitDocument11 pagesElectrical Engineering Department: Course: Dee30043 Electronic Circuitsaiman suiNo ratings yet

- C++-DLL Week 8Document3 pagesC++-DLL Week 8Rhexel ReyesNo ratings yet

- Lab Sheet PW6 Jun 2017Document13 pagesLab Sheet PW6 Jun 2017Muhd FaizNo ratings yet

- Part E Course Outcomes Assessment Plan: Philippine College of Science and TechnologyDocument4 pagesPart E Course Outcomes Assessment Plan: Philippine College of Science and Technologyrandy poyaoanNo ratings yet

- LB LO 1 Strike An ArcDocument5 pagesLB LO 1 Strike An ArcJoy BuycoNo ratings yet

- KINS - 1100 - M03 - M04 - Course Outline - 202320 PDFDocument5 pagesKINS - 1100 - M03 - M04 - Course Outline - 202320 PDFAttNo ratings yet

- Thermalfluid Lab - MEC 554 / LSRC / SCA Rev. 01-2017: Concentric Tube Heat ExchangerDocument24 pagesThermalfluid Lab - MEC 554 / LSRC / SCA Rev. 01-2017: Concentric Tube Heat ExchangerAhmad SyamilNo ratings yet

- COT 2 Exemplary Dll-Template COT2Document3 pagesCOT 2 Exemplary Dll-Template COT2Joanne Cabangil100% (2)

- Pw6 Busbar With Load Dis 19Document11 pagesPw6 Busbar With Load Dis 19Shanthiyaah ArumugamNo ratings yet

- Emd5m6a1 Lab Report Thermo 2Document21 pagesEmd5m6a1 Lab Report Thermo 2Zulfaris NasirNo ratings yet

- MATLABDocument13 pagesMATLABVraj ShahNo ratings yet

- DLL in Eim 11 Q1Document19 pagesDLL in Eim 11 Q1Emelito Colentum100% (2)

- Refrigerent LaboratoryDocument18 pagesRefrigerent LaboratoryKRG KickFlashNo ratings yet

- BG1801 Course OutlineDocument6 pagesBG1801 Course OutlineGracee GraceeNo ratings yet

- Rubrics Exceeds Expectation (3) Meets ExpectationDocument25 pagesRubrics Exceeds Expectation (3) Meets Expectationsusan williamNo ratings yet

- Syde 352 LDocument5 pagesSyde 352 Lalldaylam3No ratings yet

- DLL ScribdDocument5 pagesDLL ScribdMikutapi LuchingNo ratings yet

- CHE1CHF Labmanual 2023Document129 pagesCHE1CHF Labmanual 2023Alexandra GutrovaNo ratings yet

- Physiology-I Lab Manual 2021Document50 pagesPhysiology-I Lab Manual 2021Shaheer MirzaNo ratings yet

- 04 Laboratory Manual Sbc3043 Semester 1, 2018 2019 A181Document19 pages04 Laboratory Manual Sbc3043 Semester 1, 2018 2019 A181Leena MuniandyNo ratings yet

- Compr 1Document5 pagesCompr 1armie valenciaNo ratings yet

- Detailed Lesson Plan in TLE 10 Electronics I. ObjectivesDocument5 pagesDetailed Lesson Plan in TLE 10 Electronics I. Objectivesalden indemneNo ratings yet

- BIO 230 Syllabus 190 Spring 2024 Angermeier - TaggedDocument9 pagesBIO 230 Syllabus 190 Spring 2024 Angermeier - Taggedkb95387No ratings yet

- Survey Lab ManualDocument37 pagesSurvey Lab ManualKausik ChatterjeeNo ratings yet

- EIM Exploratorys DLL Week 1Document4 pagesEIM Exploratorys DLL Week 1henryNo ratings yet

- Cot 3 Electrical InstallationDocument3 pagesCot 3 Electrical InstallationJoanne CabangilNo ratings yet

- Lesson Plan in TVL Home Economics - COOKERY Grade 11 & 12: August 08, 2018Document3 pagesLesson Plan in TVL Home Economics - COOKERY Grade 11 & 12: August 08, 2018Darlene Daguno CabridoNo ratings yet

- CHE1CHF Labmanual Wreptbk 2024 v3 (MasterCopy) 2024Document133 pagesCHE1CHF Labmanual Wreptbk 2024 v3 (MasterCopy) 2024bhautoosnehaNo ratings yet

- M1 - L1 - 3 - Procedure For Sterilization and Sanitation of Nail Care Tools and EquipmentsDocument2 pagesM1 - L1 - 3 - Procedure For Sterilization and Sanitation of Nail Care Tools and EquipmentsRamz Latsiv Yohgat100% (1)

- Complex Engineering Problem (CEP) Descriptive FormDocument4 pagesComplex Engineering Problem (CEP) Descriptive FormArslan MunawarNo ratings yet

- Forced and Free ConvectionDocument33 pagesForced and Free ConvectionmirahNo ratings yet

- LabManual - PHY2049L.pdf (1) 2Document67 pagesLabManual - PHY2049L.pdf (1) 2juanfelipecadavidherreraNo ratings yet

- Full Report Forced and Natural ConvectionDocument27 pagesFull Report Forced and Natural Convectionfaruq haziqNo ratings yet

- CLO No-4: Demonstrate Use of Various Measuring Instruments Commonly Used by The Electrical Engineers To Measure Electrical QuantitiesDocument2 pagesCLO No-4: Demonstrate Use of Various Measuring Instruments Commonly Used by The Electrical Engineers To Measure Electrical QuantitiesEngr Haseena JabbarNo ratings yet

- 8 - Manual - Surveying LabDocument52 pages8 - Manual - Surveying LabJEAN DE DIEU MUVARANo ratings yet

- B2-1 (T&H 1) PDFDocument40 pagesB2-1 (T&H 1) PDFAhmad SyamilNo ratings yet

- National Institute of Physics: College of Science University of The Philippines Diliman, Quezon City 1101 Metro-ManilaDocument12 pagesNational Institute of Physics: College of Science University of The Philippines Diliman, Quezon City 1101 Metro-ManilaDoom RefugeNo ratings yet

- Thermalfluid Lab - MEC 554 / LSRC / SCA Rev. 01-2017: Flow Characteristic Through The Convergent-Divergent DuctDocument27 pagesThermalfluid Lab - MEC 554 / LSRC / SCA Rev. 01-2017: Flow Characteristic Through The Convergent-Divergent DuctAhmad SyamilNo ratings yet

- Surveying Lab ManualDocument83 pagesSurveying Lab Manualsree204raoNo ratings yet

- 71.1 Syllabus Mid-Year 2016-2017Document2 pages71.1 Syllabus Mid-Year 2016-2017Mary JoyceNo ratings yet

- 2.electronic Devices & CircuitsDocument93 pages2.electronic Devices & CircuitsMuhammad AbdullahNo ratings yet

- Xi - Physics (042) Practical Final Exam 2023-2024-1Document2 pagesXi - Physics (042) Practical Final Exam 2023-2024-1HentaiNo ratings yet

- CG Week3.2 DLPactivityDocument4 pagesCG Week3.2 DLPactivityRachel CanoNo ratings yet

- Course Outline BSED 3ADocument6 pagesCourse Outline BSED 3AborntohavenonameNo ratings yet

- Guidelines and InstructionsDocument5 pagesGuidelines and InstructionsArvin LiangdyNo ratings yet

- Protocall 934 Hazardous Materials Technician: Ten Fingers and Ten ToesFrom EverandProtocall 934 Hazardous Materials Technician: Ten Fingers and Ten ToesNo ratings yet

- Case Study On Inductive Proximity SwitchesDocument4 pagesCase Study On Inductive Proximity SwitchesMANASNo ratings yet

- Inversor MoellerDocument45 pagesInversor MoellerElderNo ratings yet

- Diala AX TdsDocument2 pagesDiala AX TdsAbdalhakeem Al turkyNo ratings yet

- Sma SC Mvps RFQ Configurator Iec v3.41Document66 pagesSma SC Mvps RFQ Configurator Iec v3.41Ion BlanaruNo ratings yet

- Hoja de Vida Actualizadad Ingeniero Electronico Esteban Casanova en Ingles.Document2 pagesHoja de Vida Actualizadad Ingeniero Electronico Esteban Casanova en Ingles.esteban casanovaNo ratings yet

- Siemens Micromaster 420 VFD Setting (Analog Input + Fixed Speed)Document1 pageSiemens Micromaster 420 VFD Setting (Analog Input + Fixed Speed)Rinu RavikumarNo ratings yet

- Cispr14 2 Amd2 (Ed1.0) BDocument14 pagesCispr14 2 Amd2 (Ed1.0) BpabNo ratings yet

- Cpplus SPP Price ListDocument11 pagesCpplus SPP Price ListVinodh MNo ratings yet

- Quiz 3 FinalsDocument11 pagesQuiz 3 FinalsReyven Lumiguen TorresNo ratings yet

- Kripsol Spare PartsDocument122 pagesKripsol Spare PartsnewbornlifeNo ratings yet

- Final Report Transformer Design Section A PDFDocument68 pagesFinal Report Transformer Design Section A PDFThabiso Kyle100% (1)

- PowerCube 1000 User ManualDocument341 pagesPowerCube 1000 User ManualDavid Chokani100% (1)

- Solution Manual For Structured Computer Organization 6 e 6th Edition 0132916525Document33 pagesSolution Manual For Structured Computer Organization 6 e 6th Edition 0132916525oweltyswiller.28sh100% (17)

- Controls Operation and TroubleshootingDocument138 pagesControls Operation and TroubleshootingAnup SurendranNo ratings yet

- Power Electronic TransformerDocument61 pagesPower Electronic TransformerMahidhar Talapaneni100% (2)

- Componentes SHR5500Document20 pagesComponentes SHR5500Miguel Angel Rodriguez CatroNo ratings yet

- LVC Price List 2023Document156 pagesLVC Price List 2023threephase electricNo ratings yet

- The Settings of Foobar Player - ENDocument19 pagesThe Settings of Foobar Player - ENtoto36No ratings yet

- Persamaan IC RT Dan TPS PDFDocument10 pagesPersamaan IC RT Dan TPS PDFedi purwantoNo ratings yet

- Toshiba VTW2887Document105 pagesToshiba VTW2887thomas-stentzelNo ratings yet

- Cybenetics - Evaluation - Report - Galax - OMEGA GLX1000Document12 pagesCybenetics - Evaluation - Report - Galax - OMEGA GLX1000intel boyNo ratings yet

- Eto Coc Written Examination Questions & Answers Part-1: by Minbox - February 11, 2020Document15 pagesEto Coc Written Examination Questions & Answers Part-1: by Minbox - February 11, 2020Gokul RajNo ratings yet

- VelometersDocument6 pagesVelometersRaj SomaiyaNo ratings yet

- Extract From The Online Catalog: Uk 5 N BuDocument8 pagesExtract From The Online Catalog: Uk 5 N BufragercitoNo ratings yet

- iRT PicoBUC Extended Temperature Range Ku-Band 40/50W GaN SSPBDocument2 pagesiRT PicoBUC Extended Temperature Range Ku-Band 40/50W GaN SSPBarzeszutNo ratings yet

- 1.1 M20S Repair GuidanceDocument10 pages1.1 M20S Repair GuidanceOsmin MendozaNo ratings yet

- Et101-2008+a1+a2 Ac A3-2018Document393 pagesEt101-2008+a1+a2 Ac A3-2018Tommy MurphyNo ratings yet

- KV-5500/5000/3000/1000/700 Series: Programmable Controller Special UnitDocument4 pagesKV-5500/5000/3000/1000/700 Series: Programmable Controller Special UnitAlejandro Genetik HernandezNo ratings yet