Professional Documents

Culture Documents

8086 MIC - Unit 1 - Notes

8086 MIC - Unit 1 - Notes

Uploaded by

viraj babarOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

8086 MIC - Unit 1 - Notes

8086 MIC - Unit 1 - Notes

Uploaded by

viraj babarCopyright:

Available Formats

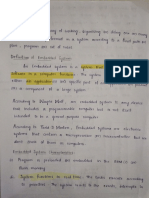

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.

Patil

Chapter 1

8086-16 Bit Microprocessor

1. Introduction

8086 Microprocessor is an enhanced version of 8085 Microprocessor that

was designed by Intel in 1978. It is a 16-bit Microprocessor having 20

address lines and16 data lines that provides up to 1MB storage. It consists

of powerful instruction set, which provides operations like multiplication

and division easily.

It supports two modes of operation, i.e. Maximum mode and Minimum

mode. Maximum mode is suitable for system having multiple processors

and Minimum mode is suitable for system having a single processor.

2. Salient Features of 8086

The most prominent features of a 8086 microprocessor are as follows −

It has an instruction queue, which is capable of storing six instruction

bytes from the memory resulting in faster processing.

It was the first 16-bit processor having 16-bit ALU, 16-bit registers,

internal data bus, and 16-bit external data bus resulting in faster

processing.

It is available in 3 versions based on the frequency of operation −

o 8086 → 5MHz

o 8086-2 → 8MHz

o (c)8086-1 → 10 MHz

It uses two stages of pipelining, i.e. Fetch Stage and Execute Stage,

which improves performance.

Fetch stage can prefetch up to 6 bytes of instructions and stores

them in the queue.

Execute stage executes these instructions.

It has 256 vectored interrupts.

It consists of 29,000 transistors.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

Comparison between 8085 & 8086 Microprocessor

Size − 8085 is 8-bit microprocessor, whereas 8086 is 16-bit

microprocessor.

Address Bus − 8085 has 16-bit address bus while 8086 has 20-bit

address bus.

Memory − 8085 can access up to 64Kb, whereas 8086 can access

up to 1 Mb of memory.

Instruction − 8085 doesn’t have an instruction queue, whereas 8086

has an instruction queue.

Pipelining − 8085 doesn’t support a pipelined architecture while

8086 supports a pipelined architecture.

I/O − 8085 can address 2^8 = 256 I/O's, whereas 8086 can access

2^16 = 65,536 I/O's.

Cost − The cost of 8085 is low whereas that of 8086 is high.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

3. Microprocessor - 8086 Pin Configuration

8086 was the first 16-bit microprocessor available in 40-pin DIP (Dual

Inline Package) chip. Let us now discuss in detail the pin configuration of a

8086 Microprocessor.

8086 Pin Diagram

Here is the pin diagram of 8086 microprocessor −

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

Let us now discuss the signals in detail −

Power supply and frequency signals

It uses 5V DC supply at VCC pin 40, and uses ground at VSS pin 1 and 20

for its operation.

Clock signal

Clock signal is provided through Pin-19. It provides timing to the processor

for operations. Its frequency is different for different versions, i.e. 5MHz,

8MHz and 10MHz.

Address/data bus

AD0-AD15. These are 16 address/data bus. AD0-AD7 carries low order

byte data and AD8AD15 carries higher order byte data. During the first

clock cycle, it carries 16-bit address and after that it carries 16-bit data.

Address/status bus

A16-A19/S3-S6. These are the 4 address/status buses. During the first

clock cycle, it carries 4-bit address and later it carries status signals.

S7/BHE

BHE stands for Bus High Enable. It is available at pin 34 and used to

indicate the transfer of data using data bus D8-D15. This signal is low

during the first clock cycle, thereafter it is active.

Read($\overline{RD}$)

It is available at pin 32 and is used to read signal for Read operation.

Ready

It is available at pin 22. It is an acknowledgement signal from I/O devices

that data is transferred. It is an active high signal. When it is high, it

indicates that the device is ready to transfer data. When it is low, it

indicates wait state.

RESET

It is available at pin 21 and is used to restart the execution. It causes the

processor to immediately terminate its present activity. This signal is active

high for the first 4 clock cycles to RESET the microprocessor.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

INTR

It is available at pin 18. It is an interrupt request signal, which is sampled

during the last clock cycle of each instruction to determine if the processor

considered this as an interrupt or not.

NMI

It stands for non-maskable interrupt and is available at pin 17. It is an edge

triggered input, which causes an interrupt request to the microprocessor.

$\overline{TEST}$

This signal is like wait state and is available at pin 23. When this signal is

high, then the processor has to wait for IDLE state, else the execution

continues.

MN/$\overline{MX}$

It stands for Minimum/Maximum and is available at pin 33. It indicates

what mode the processor is to operate in; when it is high, it works in the

minimum mode and vice-aversa.

INTA

It is an interrupt acknowledgement signal and id available at pin 24. When

the microprocessor receives this signal, it acknowledges the interrupt.

ALE

It stands for address enable latch and is available at pin 25. A positive

pulse is generated each time the processor begins any operation. This

signal indicates the availability of a valid address on the address/data

lines.

DEN

It stands for Data Enable and is available at pin 26. It is used to enable

Transreceiver 8286. The transreceiver is a device used to separate data

from the address/data bus.

DT/R

It stands for Data Transmit/Receive signal and is available at pin 27. It

decides the direction of data flow through the transreceiver. When it is

high, data is transmitted out and vice-a-versa.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

M/IO

This signal is used to distinguish between memory and I/O operations.

When it is high, it indicates I/O operation and when it is low indicates the

memory operation. It is available at pin 28.

WR

It stands for write signal and is available at pin 29. It is used to write the

data into the memory or the output device depending on the status of M/IO

signal.

HLDA

It stands for Hold Acknowledgement signal and is available at pin 30. This

signal acknowledges the HOLD signal.

HOLD

This signal indicates to the processor that external devices are requesting

to access the address/data buses. It is available at pin 31.

QS1 and QS0

These are queue status signals and are available at pin 24 and 25. These

signals provide the status of instruction queue. Their conditions are shown

in the following table −

QS0 QS1 Status

0 0 No operation

0 1 First byte of opcode from the queue

1 0 Empty the queue

1 1 Subsequent byte from the queue

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

S0, S1, S2

These are the status signals that provide the status of operation, which is

used by the Bus Controller 8288 to generate memory & I/O control signals.

These are available at pin 26, 27, and 28. Following is the table showing

their status −

S2 S1 S0 Status

0 0 0 Interrupt acknowledgement

0 0 1 I/O Read

0 1 0 I/O Write

0 1 1 Halt

1 0 0 Opcode fetch

1 0 1 Memory read

1 1 0 Memory write

1 1 1 Passive

LOCK

When this signal is active, it indicates to the other processors not to ask

the CPU to leave the system bus. It is activated using the LOCK prefix on

any instruction and is available at pin 29.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

RQ/GT1 and RQ/GT0

These are the Request/Grant signals used by the other processors

requesting the CPU to release the system bus. When the signal is

received by CPU, then it sends acknowledgment. RQ/GT0 has a higher

priority than RQ/GT1.

4. Internal Architecture of 8086

The following diagram depicts the architecture of a 8086 Microprocessor –

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

8086 Microprocessor is divided into two functional units,

i.e., EU (Execution Unit) and BIU (Bus Interface Unit).

EU (Execution Unit)

Execution unit gives instructions to BIU stating from where to fetch the

data and then decode and execute those instructions. Its function is to

control operations on data using the instruction decoder & ALU. EU has no

direct connection with system buses as shown in the above figure, it

performs operations over data through BIU.

Let us now discuss the functional parts of 8086 microprocessors.

ALU

It handles all arithmetic and logical operations, like +, −, ×, /, OR, AND,

NOT operations.

Flag Register

It is a 16-bit register that behaves like a flip-flop, i.e. it changes its status

according to the result stored in the accumulator. It has 9 flags and they

are divided into 2 groups − Conditional Flags and Control Flags.

Conditional Flags

It represents the result of the last arithmetic or logical instruction executed.

Following is the list of conditional flags −

Carry flag − This flag indicates an overflow condition for arithmetic

operations.

Auxiliary flag − When an operation is performed at ALU, it results in

a carry/barrow from lower nibble (i.e. D0 – D3) to upper nibble (i.e.

D4 – D7), then this flag is set, i.e. carry given by D3 bit to D4 is AF

flag. The processor uses this flag to perform binary to BCD

conversion.

Parity flag − This flag is used to indicate the parity of the result, i.e.

when the lower order 8-bits of the result contains even number of

1’s, then the Parity Flag is set. For odd number of 1’s, the Parity Flag

is reset.

Zero flag − This flag is set to 1 when the result of arithmetic or

logical operation is zero else it is set to 0.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

Sign flag − This flag holds the sign of the result, i.e. when the result

of the operation is negative, then the sign flag is set to 1 else set to

0.

Overflow flag − This flag represents the result when the system

capacity is exceeded.

Control Flags

Control flags controls the operations of the execution unit. Following is the

list of control flags −

Trap flag − It is used for single step control and allows the user to

execute one instruction at a time for debugging. If it is set, then the

program can be run in a single step mode.

Interrupt flag − It is an interrupt enable/disable flag, i.e. used to

allow/prohibit the interruption of a program. It is set to 1 for interrupt

enabled condition and set to 0 for interrupt disabled condition.

Direction flag − It is used in string operation. As the name suggests

when it is set then string bytes are accessed from the higher memory

address to the lower memory address and vice-a-versa.

General purpose register

There are 8 general purpose registers, i.e., AH, AL, BH, BL, CH, CL, DH,

and DL. These registers can be used individually to store 8-bit data and

can be used in pairs to store 16bit data. The valid register pairs are AH

and AL, BH and BL, CH and CL, and DH and DL. It is referred to the AX,

BX, CX, and DX respectively.

AX register − It is also known as accumulator register. It is used to

store operands for arithmetic operations.

BX register − It is used as a base register. It is used to store the

starting base address of the memory area within the data segment.

CX register − It is referred to as counter. It is used in loop instruction

to store the loop counter.

DX register − This register is used to hold I/O port address for I/O

instruction.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

Stack pointer register

It is a 16-bit register, which holds the address from the start of the

segment to the memory location, where a word was most recently stored

on the stack.

BIU (Bus Interface Unit)

BIU takes care of all data and addresses transfers on the buses for the EU

like sending addresses, fetching instructions from the memory, reading

data from the ports and the memory as well as writing data to the ports

and the memory. EU has no direction connection with System Buses so

this is possible with the BIU. EU and BIU are connected with the Internal

Bus.

It has the following functional parts −

Instruction queue − BIU contains the instruction queue. BIU gets

upto 6 bytes of next instructions and stores them in the instruction

queue. When EU executes instructions and is ready for its next

instruction, then it simply reads the instruction from this instruction

queue resulting in increased execution speed.

Fetching the next instruction while the current instruction executes is

called pipelining.

Segment register − BIU has 4 segment buses, i.e. CS, DS, SS&

ES. It holds the addresses of instructions and data in memory, which

are used by the processor to access memory locations. It also

contains 1 pointer register IP, which holds the address of the next

instruction to executed by the EU.

o CS − It stands for Code Segment. It is used for addressing a

memory location in the code segment of the memory, where

the executable program is stored.

o DS − It stands for Data Segment. It consists of data used by

the program and is accessed in the data segment by an offset

address or the content of other register that holds the offset

address.

o SS − It stands for Stack Segment. It handles memory to store

data and addresses during execution.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:

Name:- Mrs.A.S.Patil

o ES − It stands for Extra Segment. ES is additional data

segment, which is used by the string to hold the extra

destination data.

Instruction pointer − It is a 16-bit

bit register used to hold the address

of the next instruction to be executed.

5. 8086-Flag Register

The Flag register is a Special Purpose Register. Depending upon the

value of result after any arithmetic and logical operation the flag bits

become set (1) or reset (0).

The following section explains

explains the Flag Register for 8086 in details.

This register is also called status register. It is a 16 bit register which

contains six status flags and three control flags. So, only nine bits of the

16 bit register are defined and the remaining seven bits are undefined.

Normally this status flag bits indicate the status of the ALU after the

arithmetic or logical operations.

Each bit of the status register is a flip/flop.

The Flag register contains Carry flag, Parity flag, Auxiliary flag Zero flag,

Sign flag ,Trap flag, Interrupt flag, Direction flag and overflow flag as

shown in the diagram.

The CF,PF,AF,ZF,SF,OF are the status flags and the TF,IF and CF are

the control flags.

Figure – Format of flag register

There are total 9 flags in 8086 and the flag register is divided into two

types:

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Bk,Pune

Sub: - Microprocessor (22415) Faculty Name:

Name:- Mrs.A.S.Patil

(a) Status Flags

(b) Control Flags

(a) Status Flags – There are 6 flag registers in 8086 microprocessor

which become set(1) or reset(0) depending upon condition after either 8-

bit or 16-bit

bit operation. These flags are conditional/status flags. 5 of these

flags are same as in case of 8085 microprocessor and their working is

also same as in 8085 microprocessor. The sixth one is the overflow flag.

The 6 status flags are:

1. Sign Flag (S)

2. Zero Flag (Z)

3. Auxiliary Cary Flag (AC)

4. Parity Flag (P)

5. Carry Flag (CY)

6. Overflow Flag (O)

In 8085 microprocessor, flag register consists of 8 bits and only 5 of

them are useful. The 5 flags are:

1. Sign Flag (S) – After any operation if the MSB (B(7)) of the result is

1, it indicates the number is negative and the sign flag becomes set,

i.e. 1. If the MSB is 0, it indicates the number is positive and the sign

flag becomes reset i.e. 0.

from 00H to 7F, sign flag is 0

from 80H to FF, sign flag is 1

1- MSB is 1 (negative)

0- MSB is 0 (positive)

Example:

MVI A 30 (load 30H in register A)

MVI B 40 (load 40H in register B)

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Bk,Pune

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

SUB B (A = A – B)

These set of instructions will set the sign flag to 1 as 30 – 40 is a

negative number.

MVI A 40 (load 40H in register A)

MVI B 30 (load 30H in register B)

SUB B (A = A – B)

These set of instructions will reset the sign flag to 0 as 40 – 30 is a

positive number.

2. Zero Flag (Z) – After any arithmetical or logical operation if the result

is 0 (00)H, the zero flag becomes set i.e. 1, otherwise it becomes

reset i.e. 0.

00H zero flag is 1.

from 01H to FFH zero flag is 0

1- zero result

0- non-zero result

Example:

MVI A 10 (load 10H in register A)

SUB A (A = A – A)

These set of instructions will set the zero flag to 1 as 10H – 10H is

00H

3. Auxiliary Carry Flag (AC) – This flag is used in BCD number

system(0-9). If after any arithmetic or logical operation D(3) generates

any carry and passes on to B(4) this flag becomes set i.e. 1,

otherwise it becomes reset i.e. 0. This is the only flag register which

is not accessible by the programmer

1-carry out from bit 3 on addition or borrow into bit 3 on subtraction

0-otherwise

Example:

MOV A 2B (load 2BH in register A)

MOV B 39 (load 39H in register B)

ADD B (A = A + B)

These set of instructions will set the auxiliary carry flag to 1, as on

adding 2B and 39, addition of lower order nibbles B and 9 will

generate a carry.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

4. Parity Flag (P) – If after any arithmetic or logical operation the result

has even parity, an even number of 1 bits, the parity register

becomes set i.e. 1, otherwise it becomes reset i.e. 0.

1-accumulator has even number of 1 bits

0-accumulator has odd parity

Example:

MVI A 05 (load 05H in register A)

This instruction will set the parity flag to 1 as the BCD code of 05H is

00000101, which contains even number of one’s i.e. 2.

5. Carry Flag (CY) – Carry is generated when performing n bit

operations and the result is more than n bits, then this flag becomes

set i.e. 1, otherwise it becomes reset i.e. 0.

During subtraction (A-B), if A>B it becomes reset and if (A<B) it

becomes set.

Carry flag is also called borrow flag.

1-carry out from MSB bit on addition or borrow into MSB bit on

subtraction

0-no carry out or borrow into MSB bit

Example:

MVI A 30 (load 30H in register A)

MVI B 40 (load 40H in register B)

SUB B (A = A – B)

These set of instructions will set the carry flag to 1 as 30 – 40

generates a carry/borrow.

MVI A 40 (load 40H in register A)

MVI B 30 (load 30H in register B)

SUB B (A = A – B)

These set of instructions will reset the sign flag to 0 as 40 – 30 does

not generate any carry/borrow.

6. Overflow Flag (O) – This flag will be set (1) if the result of a signed

operation is too large to fit in the number of bits available to represent

it, otherwise reset (0). After any operation, if D[6] generates any carry

and passes to D[7] OR if D[6] does not generates carry but D[7]

generates, overflow flag becomes set, i.e., 1. If D[6] and D[7] both

generate carry or both do not generate any carry, then overflow flag

becomes reset, i.e., 0.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

Example: On adding bytes 100 + 50 (result is not in range -128…127),

so overflow flag will set.

MOV AL, 50 (50 is 01010000 which is positive)

MOV BL, 32 (32 is 00110010 which is positive)

ADD AL, BL (82 is 10000010 which is negative)

Overflow flag became set as we added 2 +ve numbers and we got a -ve

number.

(b) Control Flags – The control flags enable or disable certain

operations of the microprocessor. There are 3 control flags in 8086

microprocessor and these are:

1. Directional Flag (D) – This flag is specifically used in string

instructions.

If directional flag is set (1), then access the string data from higher

memory location towards lower memory location.

If directional flag is reset (0), then access the string data from lower

memory location towards higher memory location.

2. Interrupt Flag (I) – This flag is for interrupts.

If interrupt flag is set (1), the microprocessor will recognize interrupt

requests from the peripherals.

If interrupt flag is reset (0), the microprocessor will not recognize any

interrupt requests and will ignore them.

3. Trap Flag (T) – This flag is used for on-chip debugging. Setting trap

flag puts the microprocessor into single step mode for debugging. In

single stepping, the microprocessor executes a instruction and enters

into single step ISR.

If trap flag is set (1), the CPU automatically generates an internal

interrupt after each instruction, allowing a program to be inspected as

it executes instruction by instruction.

If trap flag is reset (0), no function is performed.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

6.8086-Interrupts-Hardware Interrupts

An interrupt to the microprocessor is defined as that which disturbs the

normal execution of a program .

Interrupt Types:

The interrupts are divided into two types.

They are external hardware Interrupts and internal (Software)

Interrupts.

The hardware interrupts are classified as nonmaskable and maskable

interrupts.

The hardware interrupt is caused by any peripheral device by sending a

signal through a specified pin to the microprocessor.

Whereas internal interrupts are initiated by the state of the CPU (e.g.

divide by zero error) or by an instruction.

So, the software interrupt is one which interrupts the normal execution of

a program of the microprocessor.

Hardware interrupts:

The 8086 has two hardware interrupt pins namely NMI and INTR.

In the two, the NMI is a non-maskable interrupt and the INTR interrupt

request is a maskable interrupt which has lower priority .

The third pin associated with the hardware interrupts are the INTA called

interrupt acknowledge.

NMI:

The processor provides a single non-maskable interrupt pin (NMI) which

has higher priority than the maskable interrupt request pin (INTR).

A typical use would be to activate a power failure routine.

The NMI is edge-triggered on a LOW-to-HIGH transition.

The activation of this pin causes a type 2 interrupt.

INTR:

The 8086 provides a single interrupt request input (INTR) which can be

masked internally by software with the resetting of the interrupt enable

FLAG status bit.

The interrupt request signal is level triggered.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

It is internally synchronized during each clock cycle on the high-going

edge of CLK. To be responded to, INTR must be present (HIGH) during

the clock period preceding the end of the current instruction or the end of

a whole move for a block type instruction.

7. 8086-Software Interrupt

An interrupt to the microprocessor is defined as that which disturbs the

normal execution of a program.

Software Interrupt:

8086 can generate 256 interrupt types through the instruction INT n.

Any of the 256 interrupt types can be generated by specifying the

interrupt type after INT instruction. For example INT 33 will cause type 33

interrupt.

I k Bytes of memory from 00000H to 003FF H is set aside to store the

starting address of the Interrupt service sub-routine(ISS) programs in an

8086 based systems.

To store the starting address of the each ISS , four bytes of memory

space is required.

Two bytes are for storing CS value and two bytes for IP value.

The starting address of an ISS stored in 1kB of memory space is called

Interrupt pointer or Interrupt vector.

The 1kB memory space acts as a table and it is called Interrupt Vector

Table (IVT).

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

The 256 interrupt pointers have been numbered from 0 to 255.

The number given to an interrupt pointer denotes the type of the

interrupt. For example Type0,Type1,Type2 etc…

The starting address of the ISS for type0 interrupt is 000000H.For type1

interrupt is 00004H similarly for type2 is 00008H ……

In the IVT the first five pointers are dedicated interrupt pointers. They are

:

TYPE 0 Interrupt corresponds to divide by zero situation

TYPE 1 Interrupt corresponds to Single step execution during the

debugging of a program.

TYPE 2 Interrupts to non-maskable NMI interrupt.

TYPE 3 :Interrupt corresponds to break point interrupt.

TYPE 4 Interrupt corresponds to Overflow interrupt.

The Interrupts from Type 5 to Type 31 are reserved for other advanced

microprocessors, and from 32 to Type 255 are available for hardware and

software interrupts.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

Figure 1.1 Reserved Memory Locations

8. 8086- Memory Organization

The following section explains memory organization for 8086

microprocessor in details.

Memory organization:

The processor provides a 20-bit address to memory which locates

the byte being referenced.

The memory is organized as a linear array of up to 1 million bytes,

addressed as 00000(H) to FFFFF(H).

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

The memory is logically divided into code, data, extra data, and stack

segments of up to 64K bytes each, with each segment falling on 16-byte

boundaries. (See Figure 1.2.)

All memory references are made relative to base addresses contained in

high speed segment registers.

The segment types were chosen based on the addressing needs of

programs.

The segment register to be selected is automatically chosen according to

the rules of the following table.

All information in one segment type share the same logical attributes

(e.g. code or data).

By structuring memory into relocatable areas of similar characteristics

and by automatically selecting segment registers, programs are shorter,

faster, and more structured.

Word (16-bit) operands can be located on even or odd address

boundaries and are thus not constrained to even boundaries as is the

case in many 16-bit computers.

For address and data operands, the least significant byte of the word is

stored in the lower valued address location and the most significant byte

in the next higher address location.

The BIU automatically performs the proper number of memory accesses,

one if the word operand is on an even byte boundary and two if it is on an

odd byte boundary.

Except for the performance penalty, this double access is transparent to

the software.

This performance penalty does not occur for instruction fetches, only

word operands.

Physically, the memory is organized as a high bank (D15±D8) and a low

bank (D7±D0) of 512K 8-bit bytes addressed in parallel by the

processor's address lines A19±A1.

Byte data with even addresses is transferred on the D7±D0 bus lines

while odd addressed byte data (A0 HIGH) is transferred on the D15±D8

bus lines.

The processor provides two enable signals, BHE and A0, to selectively

allow reading from or writing into either an odd byte location, even byte

location, or both.

The instruction stream is fetched from memory as words and is

addressed internally by the processor to the byte level as necessary.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

8086-Reserved Memory Locations

The following section explains Reserved Memory Locations for 8086

microprocessor in brief.

Reserved Memory Locations-8086:

Certain locations in memory are reserved for specific CPU operations.

Locations from address FFFF0H through FFFFFH are reserved for

operations including a jump to the initial program loading routine.

Following RESET, the CPU will always begin execution at location

FFFF0H where the jump must be. Locations 00000H through 003FFH

are reserved for interrupt operations.

Each of the 256 possible interrupt types has its service routine pointed to

by a 4-byte pointer element consisting of a 16-bit segment address and a

16-bit offset address.

The pointer elements are assumed to have been stored at the respective

places in reserved memory prior to occurrence of interrupts.

Addressing Data in Memory

The process through which the processor controls the execution of

instructions is referred as the fetch-decode-execute cycle or

the execution cycle. It consists of three continuous steps −

Fetching the instruction from memory

Decoding or identifying the instruction

Executing the instruction

The processor may access one or more bytes of memory at a time. Let us

consider a hexadecimal number 0725H. This number will require two bytes

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

of memory. The high-order byte or most significant byte is 07 and the low-

order byte is 25.

The processor stores data in reverse-byte sequence, i.e., a low-order byte

is stored in a low memory address and a high-order byte in high memory

address. So, if the processor brings the value 0725H from register to

memory, it will transfer 25 first to the lower memory address and 07 to the

next memory address.

x: memory address

When the processor gets the numeric data from memory to register, it

again reverses the bytes. There are two kinds of memory addresses −

Absolute address - a direct reference of specific location.

Segment address (or offset) - starting address of a memory segment

with the offset value.

9. 8086- Absolute Addresses Calculation:

The following section will give an overview about the Absolute Addresses

Calculation in the 8086 microprocessor.

Absolute Addresses Calculation:

In the 8086/8088 any program consists of at least 3 segments: code

segment that contains the instructions of the program, data

segment that contains the data of the program and the stack segment.

Accessing the different segments of the program requires two address

components offset or Effective Address (AE) and Segment Number or

address.

The sources of these addresses differ from segment to another. To fetch

an instruction (accessing the code segment), the absolute address is

calculated as follow:

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

Absolute Address (code segment) = CS * 16 IP

Where CS is the contents of the Code Segment Register and IP is the

Instruction Pointer contents.

Accessing data segment, depends on the addressing mode of the

instruction. For example, to access data segment for executing the

instruction MOV AX,[BX] the absolute address is calculated as follow:

Absolute Address (data segment) = DS * 16 BX

To execute the instruction PUSH AX , which access the stack segment,

the absolute address is calculated as follow:

Absolute Address (data segment) = SS * 16 SP

Example:

Suppose that the register contents of some of the 8086/8088 registers are

as follows:

DS = 0200H, SS = 0100H, BX = 0300H, SP = 0300H, DI = 0400H, and SI

= 0200H. If the displacement LIST = 0250H, calculate the Effective

Address (EA) and the Absolute Address of the following instructions:

a) MOV AL, [1234H]

b) MOV LIST[DI],AL

c) MOV CH,[BX SI]

d) PUSH SI

Solution:

This instruction is a Direct Addressing Instruction, thus the EA or Offset

is a part of the instruction. The Offset is 1234H and the segment address

is contained in DS. The Absolute Address is 200H * 10H 1234H =

3234H.

b) The addressing mode of this instruction is Register Relative

Addressing. Thus:

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:

Name:- Mrs.A.S.Patil

The EA or Offset of this instruction = DI LIST = 400H 250H = 650H

The Absolute Addressing = 200H * 10H 650H = 2650H

c) The addressing mode of this instruction is Base Plus Index

Addressing. Thus:

The EA or Offset of this instruction = SI BX = 200H 300H = 500H

The Absolute Addressing = 200H * 10H 500H = 2500H

d) The addressing mode of this instruction is Register Addressing which

uses both SS and

nd SP registers for addressing. Thus:

The EA or Offset of this instruction = contents of SI = 200H

The Absolute Addressing = 100H * 10H 300H = 1300H

How 20 bit physical address is generated in 8086?

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Bk,Pune

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

Figure shows the process of generating 20 bit address

8086 has a concept of Memory Segmentation. It is a method where the

whole memory is segmented (divided) into smaller parts called segments.

These segments are

• Code Segment (CS)

• Stack Segment (SS)

• Data Segment (DS)

• Extra Segment (ES)

Each Segment has a corresponding 16-bit Segment Register which holds

the Base Address (starting Address) of the Segment. At any given time,

8086 can address 16-bit x 64KB = 256 KB of memory chunk out of 1MB.

8086 has 20bit address line. So the maximum value of address that can be

addressed by 8086 is 2^20 = 1MB. So 8086 can address the locations

ranging between 00000 H to FFFFF H. This 1MB memory is divided into 16

logical segments, each with a memory of 64KB.

To locate any adress in the memory bank, it needs the Physical address of

that memory location. It cannot get the 20-bit Physical adress using the

8086 Address Line or 16-bit Segment Registers alone.

In order to access memory location, you cannot pass 20-bit address

directly to the processor. You need to tell the 16-bit address with respect to

the segment. This 16-bit address with respect to the part (segment of

64KB) of the memory bank is called the offset.

So, Physical Address = Base Address + Offset.

Suppose the Data Segment holds the Base Aaddress as 1000h and the

data you need is present in the 0020h memory location (Offset) of the Data

Segment. The calculation of the actual address is done as follows.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

1. Left shift the 16-bit address present in the segment register by 4-bits

0001 0000 0000 0000 (0000)

2. Add the 16-bit offset address to this shifted base address

0001 0000 0000 0000 0000

+ 0000 0000 0010 0000

--------------------------------------

0001 0000 0000 0010 0000

So the actual address turns out to be 10020h.

At any point of time we can change the base address of the segment

registers and use the memory locations in those segments using the offset.

Problems on physical address calculation in 8086 Microprocessor

we are going to solve some problems on calculating the physical

address (also known as effective address) of 20 bits using the different

segment registers and their respective offsets.

Q1) The value of Code Segment (CS) Register is 4042H and the value of

different offsets is as follows:

BX: 2025H , IP: 0580H , DI: 4247H

Calculate the effective address of the memory location pointed by the CS

register.

Ans:

The offset of the CS Register is the IP register.

Therefore, the effective address of the memory location pointed by the CS

register is calculated as follows:

Effective address= Base address of CS register X 10H + Address of IP

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

= 4042H X 10H + 0580H

= (40420 + 0580)H

= 41000H

Q2) Calculate the effective address for the following register:

SS: 3860H, SP: 1735H, BP: 4826H

Ans:

Both SP and BP are the offsets for Stack Register (SS). The address

calculated when BP is taken as the offset gives the starting address of the

stack. The address when SP is taken as the offset denotes the memory

location where the top of the stack lies.

Therefore, the effective address for both these cases is:

(SS X 10H) + SP = 3640H X 10H + 1735H

= 36400H + 1735H

= 38135H

(SS X 10H) + BP = 3640H X 10H + 4826H

= 36400H + 4826H

= 41226H

Q3) The value of the DS register is 3032H. And the BX register contains a

16 bit value which is equal to 3032H. 0008H is added to BX.

ADD BX, 0008H

The register AX contains some value which needs to be stored at a location

as follows:

MOV [BX], AX

Calculate the address at which the value of the AX will be stored.

Ans:

After executing the first instruction, the value of BX Register is as follows:

BX = 3040H

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

The BX register is an offset of the Data Segment (DS) register. So, the

location at which the value of the AX register will be stored is calculated as

follows:

(DS X 10H) + BX = 3032H X 10H +3040H

= 30320H + 3040H

= 33360H

10. The feature of pipelining and queue in 8086

architecture

1. The process of fetching the next instruction when the present

instruction is being executed is called as pipelining.

2. Pipelining has become possible due to the use of queue.

3. BIU (Bus Interfacing Unit) fills in the queue until the entire queue is

full.

4. BIU restarts filling in the queue when at least two locations of queue

are vacant.

Advantages of pipelining:

The execution unit always reads the next instruction byte from the

queue in BIU. This is faster than sending out an address to the

memory and waiting for the next instruction byte to come.

In short pipelining eliminates the waiting time of EU and speeds up

the processing. -The 8086 BIU will not initiate a fetch unless and until

there are two empty bytes in its queue. 8086 BIU normally obtains

two instruction bytes per fetch.

The Instruction Queue:

1. The execution unit (EU) is supposed to decode or execute an

instruction.

2. Decoding does not require the use of buses.

3. When EU is busy in decoding and executing an instruction, the BIU

fetches up to six instruction bytes for the next instructions.

4. These bytes are called as the pre-fetched bytes and they are stored

in a first in first out (FIFO) register set, which is called as a queue.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

Significance of Queue:

1. As shown in the above figure, while the EU is busy in decoding the

instruction corresponding to memory location 100F0, the BIU fetches

the next six instruction bytes from locations 100F1 to 100F6

numbered as 1 to 6.

2. These instruction bytes are stored in the 6 byte queue on the first in

first out (FIFO) basis.

3. When EU completes the execution of the existing instruction and

becomes ready for the next instruction, it simply reads the instruction

bytes in the sequence 1, 2…. from the Queue.

4. Thus the Queue will always hold the instruction bytes of the next

instructions to be executed by the EU.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

Sub: - Microprocessor (22415) Faculty Name:- Mrs.A.S.Patil

11. Differentiate between Minimum Mode and Maximum Mode in 8086.

Maximum Mode Minimum Mode

When MN/MX (bar) is low 8086 is in When MN/MX (bar) is high 8086 is in

maximum mode. minimum mode.

In maximum mode 8086 generates In minimum mode 8086 generates INTA

QS1, QS0, S0 (bar), S1 (bar), S2 (bar), ALE, DEN (bar), DT/R (bar), M/IO

(bar), LOCK (bar), RQ (bar), GT1, RQ (bar), HLDA, HOLD and WR (bar), control

(bar)/GT0 control signals. signals.

So clearly there are multiple processes There is only one processor in the system

in the system. minimum mode.

Where in maximum mode interfacing, In minimum mode no interfacing or

master/slave and multiplexing and master/slave signal is required.

several such control signals are

required.

In maximum mode a bus controller is In maximum mode direct RD WR signals can

required to produce control signals. be used. No bus controller required. A simple

This bus controller produces de-multiplexing would do the job of

MEMRDC, MEMWRC, IOWRC, ALE, producing the control signals. The de-

DEN, DT/R control signals. multiplexer produces MEMRD, MEMWR,

IORD, IOWR control signals.

Sou.Venutai Chavan Polytechnic,Vadgaon Bk,Pune-41.

You might also like

- Lab 12Document13 pagesLab 12Brian PaciaNo ratings yet

- Week 1: Practice ProblemsDocument2 pagesWeek 1: Practice Problemsshaz4194No ratings yet

- Number Guessing Game Using Java: Mini Project OnDocument12 pagesNumber Guessing Game Using Java: Mini Project OnDαRֆhaη G᭄ꦿ100% (1)

- Unit - V Procedure and Macro: (12 - Marks)Document18 pagesUnit - V Procedure and Macro: (12 - Marks)50harsh palyekarNo ratings yet

- Sheet (5) : 1. What Do The Following MOV Instructions Accomplish?Document7 pagesSheet (5) : 1. What Do The Following MOV Instructions Accomplish?Ahmed NessemNo ratings yet

- Today's Content: Microprocessor Notes Lecture #1Document15 pagesToday's Content: Microprocessor Notes Lecture #1ayushNo ratings yet

- Unit 1 8086 16 Bit MicroprocessorDocument17 pagesUnit 1 8086 16 Bit MicroprocessorManofwarrior100% (1)

- 2-16 Bit Microprocessor 8086Document20 pages2-16 Bit Microprocessor 8086afzal_a75% (4)

- Winter22 CGRDocument2 pagesWinter22 CGRDerren TuscanoNo ratings yet

- 8086 Program To Count The Number of 1's in A RegisterDocument2 pages8086 Program To Count The Number of 1's in A Registershardul kukarniNo ratings yet

- MIC Project Report2Document11 pagesMIC Project Report2Sk Advertising0% (1)

- Unit 1 - 80386 Architecture and Programmers ModelDocument43 pagesUnit 1 - 80386 Architecture and Programmers ModelpjNo ratings yet

- MicccDocument12 pagesMicccomNo ratings yet

- "Convert BCD Number To Equivalent HEXADECIMAL Number": A Project Report OnDocument11 pages"Convert BCD Number To Equivalent HEXADECIMAL Number": A Project Report OnHàrshãd Sâwañt PātilNo ratings yet

- DSU Microproject ProposalDocument25 pagesDSU Microproject Proposalgirish desaiNo ratings yet

- Block Diagram of 8255 WITH ExplanationDocument8 pagesBlock Diagram of 8255 WITH Explanationsenthilkumar100% (2)

- Chapter 2: 8086 Microprocessor and Its ArchitectureDocument19 pagesChapter 2: 8086 Microprocessor and Its ArchitectureLens NewNo ratings yet

- MIC Solved Questions BankDocument14 pagesMIC Solved Questions BankAdvait kamthekarNo ratings yet

- MIC Chap 2 NotesDocument9 pagesMIC Chap 2 NotesSonali AhireNo ratings yet

- Dsu Microproject (Linked List) Ayush SasaneDocument18 pagesDsu Microproject (Linked List) Ayush SasaneAyush Sasane50% (2)

- Micro Project Report On: Atm Mangement SystemDocument16 pagesMicro Project Report On: Atm Mangement SystemYash SaveNo ratings yet

- Prepare A Report On Different Types of Network and Networking Devices"Document20 pagesPrepare A Report On Different Types of Network and Networking Devices"Omkar mahamuniNo ratings yet

- Microprocessor Programming (22415) Unit 4: Assembly Language Hours: 16 Marks: 20Document60 pagesMicroprocessor Programming (22415) Unit 4: Assembly Language Hours: 16 Marks: 20Shahnawaz KhanNo ratings yet

- Microprocessor MP.Document8 pagesMicroprocessor MP.pritam PawarNo ratings yet

- An Assembly Language Program To Check For Palindrome StringDocument14 pagesAn Assembly Language Program To Check For Palindrome StringrohiniNo ratings yet

- DCC mpGROUP5Document12 pagesDCC mpGROUP5Yash DasouniNo ratings yet

- D.K.T.E. Society's Yashwantrao Chavan Polytechnic, IchalkaranjiDocument12 pagesD.K.T.E. Society's Yashwantrao Chavan Polytechnic, IchalkaranjiRaj RayjadeNo ratings yet

- 1537-39 Java ReportDocument27 pages1537-39 Java ReportNatashaNo ratings yet

- Dte Report 1Document5 pagesDte Report 1Yesh DamaniaNo ratings yet

- Mad Micro ProjectDocument10 pagesMad Micro ProjectThe LooserNo ratings yet

- OOP Micro-Project ReportDocument36 pagesOOP Micro-Project ReportAnurag Pawar100% (1)

- GAD MicroprojectDocument15 pagesGAD MicroprojectJameer InamdarNo ratings yet

- Dma NotesDocument69 pagesDma Notessejal PolNo ratings yet

- Create IPV6 Based Small Computer Network Using A Simulator.: I. Practical SignificanceDocument6 pagesCreate IPV6 Based Small Computer Network Using A Simulator.: I. Practical Significance28-TYCM-1-SANDESH KADAMNo ratings yet

- CGR Assignment 2Document3 pagesCGR Assignment 260 Zaid PeerzadeNo ratings yet

- Write Assembly Language Program To Check String Is Palindrome or NotDocument15 pagesWrite Assembly Language Program To Check String Is Palindrome or NotAyan ShaikhNo ratings yet

- Micro-Project Report ON " ": Design Digital ClockDocument19 pagesMicro-Project Report ON " ": Design Digital ClockAKASH THORATNo ratings yet

- Contents:: Salient Features of 80386 Functional Block Diagram of 80836 Pin Description of 8086Document26 pagesContents:: Salient Features of 80386 Functional Block Diagram of 80836 Pin Description of 8086ajayNo ratings yet

- Implement Priority Queue: Microproject Data Structure Using C'Document23 pagesImplement Priority Queue: Microproject Data Structure Using C'Shreyas Bagate100% (1)

- Calculator Android ProjectDocument1 pageCalculator Android Projectkamlesh100% (1)

- Digital Code Lock SystemDocument17 pagesDigital Code Lock Systemhareeshkesireddy100% (3)

- 8086 Interrupt: Interrupt Vector Table - IVTDocument2 pages8086 Interrupt: Interrupt Vector Table - IVTkaram hayderNo ratings yet

- Communication Load of TCP With Delayed ACK and UDP in Network On ChipDocument5 pagesCommunication Load of TCP With Delayed ACK and UDP in Network On ChipJournal of ComputingNo ratings yet

- Programming Model of 8086Document4 pagesProgramming Model of 8086Prince VegetaNo ratings yet

- 08 Lab Manual - Program To Find Out Factorial of A NumberDocument4 pages08 Lab Manual - Program To Find Out Factorial of A Numberprince-karanNo ratings yet

- Functional Testing - MOD2Document32 pagesFunctional Testing - MOD2Himanshu KumarNo ratings yet

- GAD Micro Project Report GAD Micro Project ReportDocument21 pagesGAD Micro Project Report GAD Micro Project ReportSiddhant AhireNo ratings yet

- 1-32-Bit Microprocessor - Intel 80386Document37 pages1-32-Bit Microprocessor - Intel 80386afzal_a67% (3)

- On The Game of CricketDocument10 pagesOn The Game of CricketAvneesh Agrahari100% (1)

- OOP NotesDocument18 pagesOOP NotesVaishnavi/ven .PNo ratings yet

- DBMS Analysis and Comparison: A Micro Project OnDocument12 pagesDBMS Analysis and Comparison: A Micro Project OnDhiraj Chaudhari CO-137No ratings yet

- DCC Proposal (2) (1) - 1Document5 pagesDCC Proposal (2) (1) - 1Sk AdvertisingNo ratings yet

- QP 22413Document3 pagesQP 22413Vaishali RaneNo ratings yet

- Abhishek Sawant (Flying Bird)Document16 pagesAbhishek Sawant (Flying Bird)abhishek sawantNo ratings yet

- Final Dte ProjectDocument11 pagesFinal Dte ProjectMayur NarsaleNo ratings yet

- Microprocessor NotesDocument140 pagesMicroprocessor NotesSaquibh ShaikhNo ratings yet

- CGR CH 1Document22 pagesCGR CH 1Rupesh Patil100% (2)

- Micro-Project: Title: Sort The Array in Descending Order DescriptionDocument7 pagesMicro-Project: Title: Sort The Array in Descending Order DescriptionSAMMED PATILNo ratings yet

- GAD Practical 24Document2 pagesGAD Practical 24Rohit ParsodeNo ratings yet

- 1-Pass Assembler AlgorithmDocument1 page1-Pass Assembler AlgorithmTejeshwar JNo ratings yet

- H C D W S: Ealth ARE ATA Arehouse YstemDocument15 pagesH C D W S: Ealth ARE ATA Arehouse YstemLucky Programming StudioNo ratings yet

- MIC (22415) UNIT - 1 NotesDocument17 pagesMIC (22415) UNIT - 1 NotesGaurang RaneNo ratings yet

- Microprocessor - 8086 Pin ConfigurationDocument4 pagesMicroprocessor - 8086 Pin ConfigurationShahanasNo ratings yet

- PWP Unit 1Document7 pagesPWP Unit 1viraj babarNo ratings yet

- Micunit 1Document12 pagesMicunit 1viraj babarNo ratings yet

- Format MicDocument3 pagesFormat Micviraj babarNo ratings yet

- Adding 2 CGRDocument5 pagesAdding 2 CGRviraj babarNo ratings yet

- The Holy Book of X86 v2 PDFDocument53 pagesThe Holy Book of X86 v2 PDFMoustafa Al QasrawiNo ratings yet

- Instruction Set Andâ Programming of 8085 - 2024Document140 pagesInstruction Set Andâ Programming of 8085 - 2024manikjain133No ratings yet

- The 8088 & 8086 Microprocessors 4th Ed. by Triebel & Singh NetDocument81 pagesThe 8088 & 8086 Microprocessors 4th Ed. by Triebel & Singh NetHamza Zad Gul67% (6)

- L4-Masm + VS2022Document22 pagesL4-Masm + VS2022Jonah Marwa WilliamNo ratings yet

- Programs QuestionsDocument3 pagesPrograms QuestionsPratham NishadNo ratings yet

- Main Memory: Basic HardwareDocument16 pagesMain Memory: Basic HardwareHarshith BejjamNo ratings yet

- Cf-Ru5102 Uhf Rfid Reader User's Manual v1.2Document36 pagesCf-Ru5102 Uhf Rfid Reader User's Manual v1.2ssssssssssssssaaaaNo ratings yet

- EE6502 Microprocessors and Microcontrollers 16 MARK QA 1Document36 pagesEE6502 Microprocessors and Microcontrollers 16 MARK QA 1umramanNo ratings yet

- Architecture: TMS320C54xDocument14 pagesArchitecture: TMS320C54xKarpagamNo ratings yet

- Computer Architecture and Organization McqsDocument9 pagesComputer Architecture and Organization McqsInsta BroNo ratings yet

- MP-MC R16 - Unit-2Document56 pagesMP-MC R16 - Unit-2Vaishnavi. KoyaNo ratings yet

- 8085 Instruction SetDocument27 pages8085 Instruction Setbostanci100% (1)

- Pseudocode BasicsDocument16 pagesPseudocode BasicsDedie Surya WegaNo ratings yet

- How To Draw Timing DiagramDocument6 pagesHow To Draw Timing DiagramMurughesh MurughesanNo ratings yet

- Syllabus: Microcontrollers 4 Sem Ece/TceDocument60 pagesSyllabus: Microcontrollers 4 Sem Ece/TceRaviNo ratings yet

- 03 Instruction Set Architecture Co 2022Document10 pages03 Instruction Set Architecture Co 2022Win WarNo ratings yet

- Internal Architecture of 8086: Central Processing Unit or and Output Circuitry or I/O andDocument8 pagesInternal Architecture of 8086: Central Processing Unit or and Output Circuitry or I/O andAmandeep Singh KheraNo ratings yet

- Unit - IV PDFDocument16 pagesUnit - IV PDFIt's MeNo ratings yet

- Lec# 8 The Addressing Modes of 8085 MicroprocessorDocument20 pagesLec# 8 The Addressing Modes of 8085 MicroprocessorSalva KhanNo ratings yet

- Assignment 1 PDFDocument2 pagesAssignment 1 PDFAditya MathurNo ratings yet

- Design of A Minimal Processor On An FpgaDocument12 pagesDesign of A Minimal Processor On An FpgaRNo ratings yet

- Central Processing Unit: Cpe 252: Computer Organization 1Document30 pagesCentral Processing Unit: Cpe 252: Computer Organization 1sulekhaisaacNo ratings yet

- Siemens S7 1200 S7 1500 Absolute Addressing EthernetDocument13 pagesSiemens S7 1200 S7 1500 Absolute Addressing EthernetmakotamaquinasNo ratings yet

- Erle Robotics CPP GitbookDocument122 pagesErle Robotics CPP GitbookkolosuxNo ratings yet

- LAB 09 RISC-V Assembly (Part I: Introduction) : EE-222 Microprocessors Systems April 11, 2019Document9 pagesLAB 09 RISC-V Assembly (Part I: Introduction) : EE-222 Microprocessors Systems April 11, 2019Shanawar Ali100% (1)

- Unit 1 Es&iotDocument15 pagesUnit 1 Es&iotChaitanya VarmaNo ratings yet

- Microproessor - Microprocessor and Its Components - : Qisthi Al Hazmi HR., S.T., M.TDocument21 pagesMicroproessor - Microprocessor and Its Components - : Qisthi Al Hazmi HR., S.T., M.TChuenk NeutronNo ratings yet