Professional Documents

Culture Documents

0 ratings0% found this document useful (0 votes)

8 viewsDLD LP

DLD LP

Uploaded by

Rameshchandra K ECEThe document is a lesson plan for a Digital Logic Design subject taught to first year students. It covers 5 units over 40 sessions: 1) Review of numbers and codes, 2) Boolean theorems and minimization techniques, 3) Combinational logic circuits, 4) Synchronous sequential logic, and 5) Registers and counters. Each session lists the topic to be covered, associated textbook references, and remarks.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You might also like

- (Get Now) SOAP For Family Medicine by Daniel Maldonado: Â Š PDF Â Š KINDLE Â ŠDocument12 pages(Get Now) SOAP For Family Medicine by Daniel Maldonado: Â Š PDF Â Š KINDLE Â ŠMauricio Solano DiazNo ratings yet

- Coca Cola Beverages Interview Questions and Answers 9291Document11 pagesCoca Cola Beverages Interview Questions and Answers 9291milkesa destaNo ratings yet

- MasterPlay User GuideDocument29 pagesMasterPlay User GuideArul Patmose ParamanathanNo ratings yet

- Boe310 LectureDocument25 pagesBoe310 LectureRaj Gopal MishraNo ratings yet

- 2.20RO2001 - DE & MicroprocessorsDocument5 pages2.20RO2001 - DE & MicroprocessorsRaj PNo ratings yet

- St. Peter'Scollege of Engineeering and Technology Department of Eee Lesson PlanDocument11 pagesSt. Peter'Scollege of Engineeering and Technology Department of Eee Lesson PlanRaj Bharath Raju100% (1)

- Rajiv Gandhi College of Engineering and TechnologyDocument2 pagesRajiv Gandhi College of Engineering and TechnologyKannan AlagumuthiahNo ratings yet

- Digital Principles and System DesignDocument24 pagesDigital Principles and System Designpranav2131No ratings yet

- Up & Uc - LessonPlanDocument2 pagesUp & Uc - LessonPlanKannan AlagumuthiahNo ratings yet

- STLD (EEE) Teaching MethodologyDocument3 pagesSTLD (EEE) Teaching MethodologyRahil HussainNo ratings yet

- Lesson Plan Electrical Circuits 2Document3 pagesLesson Plan Electrical Circuits 2Sunny RoyalNo ratings yet

- Modified Python Lesson PlanDocument3 pagesModified Python Lesson PlanValavala SrinivasuNo ratings yet

- Department: Cse Subject Code & Subject: Cs6201 Digital Principles and System Design Year/Semester: I/II Name of The Faculty Member: Mr.S.MANIKANDANDocument2 pagesDepartment: Cse Subject Code & Subject: Cs6201 Digital Principles and System Design Year/Semester: I/II Name of The Faculty Member: Mr.S.MANIKANDANManiKandan SubbuNo ratings yet

- DigitalDocument2 pagesDigitalsureshsullanNo ratings yet

- Computer Network Lesson PlanDocument3 pagesComputer Network Lesson PlanJoshua eedaNo ratings yet

- Daa Unit 1 LMSDocument66 pagesDaa Unit 1 LMSBobby ReddyNo ratings yet

- CS3351 Dpco Lesson PlanDocument7 pagesCS3351 Dpco Lesson Planmagy1989No ratings yet

- Fmba Lecture Notes NewDocument21 pagesFmba Lecture Notes NewNaveen DhaaramNo ratings yet

- Digital Logic DesignDocument8 pagesDigital Logic DesignShubham ChoksiNo ratings yet

- Chennai Institute of Technolohy, Chennai - 600 069: Department of Mechanical EngineeringDocument3 pagesChennai Institute of Technolohy, Chennai - 600 069: Department of Mechanical EngineeringKishore RaviNo ratings yet

- Lesson Plan - SECTION ADocument2 pagesLesson Plan - SECTION ALoknadh ChNo ratings yet

- Architecture Question.Document3 pagesArchitecture Question.2021000444.deepakNo ratings yet

- Unit - 2 - Fundamentals of Digital ElectronicsDocument117 pagesUnit - 2 - Fundamentals of Digital ElectronicsKISHAN SHUKLANo ratings yet

- Ldica Session Planner2022-23Document2 pagesLdica Session Planner2022-23vijaykannamallaNo ratings yet

- Ldica Session Planner2022-23 LavanyaDocument2 pagesLdica Session Planner2022-23 LavanyavijaykannamallaNo ratings yet

- HVDC Micro Lesson PlanDocument3 pagesHVDC Micro Lesson PlanMr. R. Jagan EEENo ratings yet

- Flat Lesson PlanDocument2 pagesFlat Lesson PlanNeelamani SamalNo ratings yet

- DICADocument2 pagesDICAak5775No ratings yet

- SS LS 2023-2024Document4 pagesSS LS 2023-2024sudhamaniNo ratings yet

- R2018 Curriculum and SyllabiDocument15 pagesR2018 Curriculum and SyllabiMANIMEGALAI M. ECENo ratings yet

- High Clock Rate CMOS Digital Pipeline MultiplierAcDocument5 pagesHigh Clock Rate CMOS Digital Pipeline MultiplierAcIosif MudraNo ratings yet

- Department of Mechanical EngineeringDocument8 pagesDepartment of Mechanical EngineeringKishore RaviNo ratings yet

- Introduction: Digital Systems & Logic Design: by Taweesak ReungpeerakulDocument19 pagesIntroduction: Digital Systems & Logic Design: by Taweesak ReungpeerakulSoman AunNo ratings yet

- C++ Lesson PlanDocument2 pagesC++ Lesson PlansivaNo ratings yet

- Department of Electronics & Communication HKE's S.L.N College of Engineering Assignment BankDocument2 pagesDepartment of Electronics & Communication HKE's S.L.N College of Engineering Assignment Bankvijayarani.katkamNo ratings yet

- Ec6202 Scad MSM PDFDocument92 pagesEc6202 Scad MSM PDFManjuladevi KannanNo ratings yet

- BEE1023 EE113 Digital Electronics 1 Ver2022Document4 pagesBEE1023 EE113 Digital Electronics 1 Ver2022AYYNo ratings yet

- DLD Micro Lesson PlaN 2 - Section CDocument4 pagesDLD Micro Lesson PlaN 2 - Section CMadhavarao K0% (1)

- Embedded SystemDocument28 pagesEmbedded Systemnanobala15No ratings yet

- DSP Couse FileDocument236 pagesDSP Couse FileSamuel BhukyaNo ratings yet

- $warnandhira: Vlsi SimulationDocument3 pages$warnandhira: Vlsi SimulationRamarao BNo ratings yet

- CAS HandoutDocument2 pagesCAS HandoutMohan KolaNo ratings yet

- DIGITAL Course Plan FinalDocument10 pagesDIGITAL Course Plan FinalponniNo ratings yet

- Cs3351-Lesson PlanDocument5 pagesCs3351-Lesson PlandhivyabharathyNo ratings yet

- Rajalakshmi Engineering College: Thandalam, Chennai - 602 105 Lesson PlanDocument6 pagesRajalakshmi Engineering College: Thandalam, Chennai - 602 105 Lesson PlanJefferson ThompsonNo ratings yet

- De-Lesson PlanDocument4 pagesDe-Lesson PlanEzhil Azhahi.AM Assistant ProfessorNo ratings yet

- Introduction Number Systems and Conversion: This Chapter in The Book IncludesDocument29 pagesIntroduction Number Systems and Conversion: This Chapter in The Book Includes임동훈No ratings yet

- Digital Communication: Department of EceDocument4 pagesDigital Communication: Department of EceJefferson ThompsonNo ratings yet

- R23 Yca2002Document4 pagesR23 Yca2002munnisujliNo ratings yet

- JDocument1 pageJ;(No ratings yet

- 4041Document4 pages4041Manu ENo ratings yet

- Vlsidt Syllabus Detailing - 2k15-CourseDocument2 pagesVlsidt Syllabus Detailing - 2k15-CoursevinodNo ratings yet

- Course Handout: Amity University RajasthanDocument5 pagesCourse Handout: Amity University RajasthanKaran MaanNo ratings yet

- Network Programming: Course No: IS ZC462 Course Code:1627Document4 pagesNetwork Programming: Course No: IS ZC462 Course Code:1627reddythNo ratings yet

- CS3351 LPDocument5 pagesCS3351 LPsyed1188No ratings yet

- CS8602 CD Course PlanDocument7 pagesCS8602 CD Course PlanPrasanna LathaNo ratings yet

- Cs8251 Lesson PlanDocument2 pagesCs8251 Lesson Planshajitha120450% (2)

- PDC Lesson Plan - II-IIDocument2 pagesPDC Lesson Plan - II-IISrinivasu RajuNo ratings yet

- Power ElectronicsDocument107 pagesPower ElectronicsMr. VenkateshNo ratings yet

- STLDDocument2 pagesSTLDPrasanth VarasalaNo ratings yet

- Monte Carlo Frameworks: Building Customisable High-performance C++ ApplicationsFrom EverandMonte Carlo Frameworks: Building Customisable High-performance C++ ApplicationsRating: 1.5 out of 5 stars1.5/5 (2)

- UntitledDocument3 pagesUntitledRameshchandra K ECENo ratings yet

- K Rameshchandra - Sept - 2022 - R&D - ReportDocument4 pagesK Rameshchandra - Sept - 2022 - R&D - ReportRameshchandra K ECENo ratings yet

- A Deep Learning Approach For Efficient Decision Making in Healthcare InformaticsDocument14 pagesA Deep Learning Approach For Efficient Decision Making in Healthcare InformaticsRameshchandra K ECENo ratings yet

- RT22045042019Document1 pageRT22045042019Rameshchandra K ECENo ratings yet

- UntitledDocument156 pagesUntitledRameshchandra K ECENo ratings yet

- Unit 1Document22 pagesUnit 1Rameshchandra K ECENo ratings yet

- EthicalDocument2 pagesEthicalRameshchandra K ECENo ratings yet

- UntitledDocument1 pageUntitledRameshchandra K ECENo ratings yet

- UntitledDocument1 pageUntitledRameshchandra K ECENo ratings yet

- Convert The Following. I. AB Ii. 1234 Iii. 10110011 Iv. (24.315) v. (68BE)Document1 pageConvert The Following. I. AB Ii. 1234 Iii. 10110011 Iv. (24.315) v. (68BE)Rameshchandra K ECENo ratings yet

- DLD Unit-2 NotesDocument36 pagesDLD Unit-2 NotesRameshchandra K ECENo ratings yet

- UntitledDocument1 pageUntitledRameshchandra K ECENo ratings yet

- DLD Unit-4 NotesDocument48 pagesDLD Unit-4 NotesRameshchandra K ECENo ratings yet

- Analog Communication April 2019Document5 pagesAnalog Communication April 2019Rameshchandra K ECENo ratings yet

- DLD Unit-5 NotesDocument16 pagesDLD Unit-5 NotesRameshchandra K ECENo ratings yet

- Course Name Digital Logic Design Year/Semester II B. Tech/I Sem L T P C Regulation Year 2021-2022 3 0 0 3 Digital Logic DesignDocument2 pagesCourse Name Digital Logic Design Year/Semester II B. Tech/I Sem L T P C Regulation Year 2021-2022 3 0 0 3 Digital Logic DesignRameshchandra K ECENo ratings yet

- Area Profiler and NAD - LoginsDocument2 pagesArea Profiler and NAD - LoginsRameshchandra K ECENo ratings yet

- FURUNO FAR-FR2855 Installation Manual RDP115 Basic DiagramsDocument86 pagesFURUNO FAR-FR2855 Installation Manual RDP115 Basic Diagramstoumassis_pNo ratings yet

- Kingspan Jindal Ext. Wall Panel SystemDocument32 pagesKingspan Jindal Ext. Wall Panel Systemabhay kumarNo ratings yet

- Kami 3Document2 pagesKami 3KumarNo ratings yet

- Comparision Between Soyabean Milk and Natural MilkDocument3 pagesComparision Between Soyabean Milk and Natural MilkShivam SinghNo ratings yet

- MQP Keys Mbf106Document18 pagesMQP Keys Mbf106Rajeev DayalNo ratings yet

- Biamp Manual Tesira Hd-1 Oct15-1Document16 pagesBiamp Manual Tesira Hd-1 Oct15-1Rachmat Guntur Dwi PutraNo ratings yet

- Relational Model ConceptsDocument5 pagesRelational Model ConceptsAbhinandan BhatNo ratings yet

- Prof. Alberto Berizzi: Dipartimento Di Energia Ph. 02 2399 3728 Email: Alberto - Berizzi@polimi - ItDocument32 pagesProf. Alberto Berizzi: Dipartimento Di Energia Ph. 02 2399 3728 Email: Alberto - Berizzi@polimi - ItMohammed OsmanNo ratings yet

- Toefl Short Course Sesi 3 ReadingDocument8 pagesToefl Short Course Sesi 3 ReadingNurul Hidayati ListyaningrumNo ratings yet

- Bachelor Thesis Presentation ExampleDocument4 pagesBachelor Thesis Presentation ExampleFiona Phillips100% (2)

- Effects of Kinesio Taping On Hemiplegic Hand in Patients With Upper Limb Post-Stroke SpasticityDocument7 pagesEffects of Kinesio Taping On Hemiplegic Hand in Patients With Upper Limb Post-Stroke Spasticityhgood1001No ratings yet

- Iso 13849-1-2023Document164 pagesIso 13849-1-2023gokhanekinci92No ratings yet

- Kagramian Report 2Document12 pagesKagramian Report 2api-700030358No ratings yet

- WellPlan ReportDocument34 pagesWellPlan ReportElmar CahangirovNo ratings yet

- Chapter 11 Power Point (1) - 5 PDFDocument25 pagesChapter 11 Power Point (1) - 5 PDFMuhammad NaveedNo ratings yet

- Exp 01 Determination of DensityDocument16 pagesExp 01 Determination of DensityParithyiMuraliTharanNo ratings yet

- Tech Gr9 m3 Hydraulic Pneumatic SystemsDocument26 pagesTech Gr9 m3 Hydraulic Pneumatic SystemsEduBoard100% (1)

- Stock April 2020Document5 pagesStock April 2020roby aldiNo ratings yet

- FM ExercisesDocument5 pagesFM ExercisesanililhanNo ratings yet

- FGD Vs CompetitorCustomer - Final - LF14000NN & P559000Document9 pagesFGD Vs CompetitorCustomer - Final - LF14000NN & P559000munhNo ratings yet

- Differential Partitioning of Betacyanins and Betaxanthins Employing Aqueous Two Phase ExtractionDocument8 pagesDifferential Partitioning of Betacyanins and Betaxanthins Employing Aqueous Two Phase ExtractionPaul Jefferson Flores HurtadoNo ratings yet

- How To Use Ladybird Readers PDFDocument18 pagesHow To Use Ladybird Readers PDFJonas SilvaNo ratings yet

- Chapter 22 - Physics - Coordinated Science - IGCSE CambridgeDocument154 pagesChapter 22 - Physics - Coordinated Science - IGCSE CambridgeAlvin DuaneNo ratings yet

- ICD - GujaratDocument1,038 pagesICD - GujaratsunilkumarchaudharyNo ratings yet

- Holbright Hb-8212Document1 pageHolbright Hb-8212Eliana Cristina100% (1)

- Technical Drawing ToolsDocument11 pagesTechnical Drawing Toolsdaphne brown-mundleNo ratings yet

- Guide To Iso 9001 2015 PDFDocument15 pagesGuide To Iso 9001 2015 PDFahmed nawaz100% (2)

DLD LP

DLD LP

Uploaded by

Rameshchandra K ECE0 ratings0% found this document useful (0 votes)

8 views2 pagesThe document is a lesson plan for a Digital Logic Design subject taught to first year students. It covers 5 units over 40 sessions: 1) Review of numbers and codes, 2) Boolean theorems and minimization techniques, 3) Combinational logic circuits, 4) Synchronous sequential logic, and 5) Registers and counters. Each session lists the topic to be covered, associated textbook references, and remarks.

Original Description:

Original Title

DLD_LP

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThe document is a lesson plan for a Digital Logic Design subject taught to first year students. It covers 5 units over 40 sessions: 1) Review of numbers and codes, 2) Boolean theorems and minimization techniques, 3) Combinational logic circuits, 4) Synchronous sequential logic, and 5) Registers and counters. Each session lists the topic to be covered, associated textbook references, and remarks.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

0 ratings0% found this document useful (0 votes)

8 views2 pagesDLD LP

DLD LP

Uploaded by

Rameshchandra K ECEThe document is a lesson plan for a Digital Logic Design subject taught to first year students. It covers 5 units over 40 sessions: 1) Review of numbers and codes, 2) Boolean theorems and minimization techniques, 3) Combinational logic circuits, 4) Synchronous sequential logic, and 5) Registers and counters. Each session lists the topic to be covered, associated textbook references, and remarks.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

You are on page 1of 2

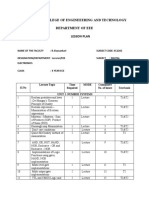

VISHNU INSTITUTE OF TECHNOLOGY

(Autonomous)

Vishnupur, Bhimavaram

DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

LESSON PLAN

Name of the Faculty: K. RAMESH CHANDRA Academic Year: 2022-2023

Designation: Associate Professor Branch: AIML

Department: ECE Year & Semester: I – II

Subject: Digital Logic Design Regulation: R-20

Text Books Required for the Subject

S. No Name of the Text Book Author(s) Name

T1 Switching Theory and Logic design Hill and Peterson

T2 Switching Theory and Logic design A.Anand Kumar

T3 Digital Design Mano

T4 Modern Digital Electronics RP Jain

S.No Hour Topics to be Covered Remarks

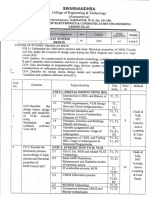

UNIT –I - REVIEW OF NUMBERS & CODES

1 1 Introduction to DLD, Importance, Applications T3

2 1 Representation of numbers of radix T1,T2

3 1 Conversion from one radix to another radix T1,T3

Complements and r’s complement of signed

4 1 T1,T2,T4

numbers, Problems

4-bit codes, BCD, Excess-3 code, 2421, 8421,

5 2 T1,T3

Gray code

6 2 Arithmetic addition and subtraction T1,T2

7 2 problems T1,T2

UNIT – II – BOOLEAN THEOREMS

&MINIMIZATION TECHNIQUES

8 1 Boolean theorems T1,T2

Minimization of logic functions using Boolean

9 2 theorems. Principle of complementation and T1,T2

duality, De-morgans theorems

10 1 Standard SOP and POS forms T1,T3

11 1 Standard POS forms, Problems T1,T3

Basic logic operations-NOT, OR, AND, Universal

12 1 T1,T4

building blocks, EX-OR, EX-NOR-gates

Standard POS forms Problems. NAND-NAND

13 2 T1,T3

Realizations.

14 2 NOR-NOR Realizations. T1,T3

Minimization of switching functions using K-map

15 2 for 3-variables, 4-variables. Minimization of T1,T4

switching functions using K-map for 5 variables.

16 1 Problems T1,T4

17 1 Problems T1,T4

UNIT – III

COMBINATIONAL LOGIC CIRCUITS

Design of half adder and full adder. Half

18 2 subtractor, Full subtractor, applications of full T1

adders,4-bit binary subtractor

19 1 Adder-subtractor circuit, BCD adder circuit. T1,T2

20 1 Excess-3 adder circuit, Look-a-head adder circuit T1,T2, T3,T4

21 2 Multiplexer, Higher order Multiplexing, problems T1,T2,T4

Realization of Boolean functions using

22 2 T1,T2,T3,T4

Multiplexers, problems

23 1 Demultiplexer, Higher order demultiplexing T1,T2,T3,T4

24 1 Encoder, Priority Encoder T1,T2,T3,T4

25 2 Design of decoder, problems T1,T2,T4

Realization of Boolean functions using decoders,

26 2 T1,T2,T4

4-bit digital comparator

27 1 problems T1,T2,T4

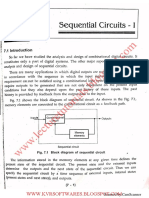

UNIT – IV – Synchronous Sequential logic

Classification of sequential circuits (synchronous

28 1 T3

and asynchronous)

29 1 Basic Flip-Flops, truth tables T3

Excitation tables of NAND RS-Latch, NOR RS-

Latch, RS-Flip-Flop. Excitation tables of JK-flip-

30 2 T3

flop, T-flip-flop, D- flip-flop with reset and clear

terminals

Conversion from one flip-flop to flip-flop, Practice

31 2 T3

class

32 1 Practice class

33 1 Test

UNIT-V-Registers and Counters

34 1 Registers T3

35 2 Shift Register T3

Bi-directional shift register, Universal shift

36 2 T3

register, problems

37 1 Design of Ripple Counters T3

38 1 Design of Synchronous Counters T3

Design of Johnson, Ring Counters. Design of

39 2 T3

Registers-Buffer register, Problems

40 1 Practice class

Faculty HOD Principal

You might also like

- (Get Now) SOAP For Family Medicine by Daniel Maldonado: Â Š PDF Â Š KINDLE Â ŠDocument12 pages(Get Now) SOAP For Family Medicine by Daniel Maldonado: Â Š PDF Â Š KINDLE Â ŠMauricio Solano DiazNo ratings yet

- Coca Cola Beverages Interview Questions and Answers 9291Document11 pagesCoca Cola Beverages Interview Questions and Answers 9291milkesa destaNo ratings yet

- MasterPlay User GuideDocument29 pagesMasterPlay User GuideArul Patmose ParamanathanNo ratings yet

- Boe310 LectureDocument25 pagesBoe310 LectureRaj Gopal MishraNo ratings yet

- 2.20RO2001 - DE & MicroprocessorsDocument5 pages2.20RO2001 - DE & MicroprocessorsRaj PNo ratings yet

- St. Peter'Scollege of Engineeering and Technology Department of Eee Lesson PlanDocument11 pagesSt. Peter'Scollege of Engineeering and Technology Department of Eee Lesson PlanRaj Bharath Raju100% (1)

- Rajiv Gandhi College of Engineering and TechnologyDocument2 pagesRajiv Gandhi College of Engineering and TechnologyKannan AlagumuthiahNo ratings yet

- Digital Principles and System DesignDocument24 pagesDigital Principles and System Designpranav2131No ratings yet

- Up & Uc - LessonPlanDocument2 pagesUp & Uc - LessonPlanKannan AlagumuthiahNo ratings yet

- STLD (EEE) Teaching MethodologyDocument3 pagesSTLD (EEE) Teaching MethodologyRahil HussainNo ratings yet

- Lesson Plan Electrical Circuits 2Document3 pagesLesson Plan Electrical Circuits 2Sunny RoyalNo ratings yet

- Modified Python Lesson PlanDocument3 pagesModified Python Lesson PlanValavala SrinivasuNo ratings yet

- Department: Cse Subject Code & Subject: Cs6201 Digital Principles and System Design Year/Semester: I/II Name of The Faculty Member: Mr.S.MANIKANDANDocument2 pagesDepartment: Cse Subject Code & Subject: Cs6201 Digital Principles and System Design Year/Semester: I/II Name of The Faculty Member: Mr.S.MANIKANDANManiKandan SubbuNo ratings yet

- DigitalDocument2 pagesDigitalsureshsullanNo ratings yet

- Computer Network Lesson PlanDocument3 pagesComputer Network Lesson PlanJoshua eedaNo ratings yet

- Daa Unit 1 LMSDocument66 pagesDaa Unit 1 LMSBobby ReddyNo ratings yet

- CS3351 Dpco Lesson PlanDocument7 pagesCS3351 Dpco Lesson Planmagy1989No ratings yet

- Fmba Lecture Notes NewDocument21 pagesFmba Lecture Notes NewNaveen DhaaramNo ratings yet

- Digital Logic DesignDocument8 pagesDigital Logic DesignShubham ChoksiNo ratings yet

- Chennai Institute of Technolohy, Chennai - 600 069: Department of Mechanical EngineeringDocument3 pagesChennai Institute of Technolohy, Chennai - 600 069: Department of Mechanical EngineeringKishore RaviNo ratings yet

- Lesson Plan - SECTION ADocument2 pagesLesson Plan - SECTION ALoknadh ChNo ratings yet

- Architecture Question.Document3 pagesArchitecture Question.2021000444.deepakNo ratings yet

- Unit - 2 - Fundamentals of Digital ElectronicsDocument117 pagesUnit - 2 - Fundamentals of Digital ElectronicsKISHAN SHUKLANo ratings yet

- Ldica Session Planner2022-23Document2 pagesLdica Session Planner2022-23vijaykannamallaNo ratings yet

- Ldica Session Planner2022-23 LavanyaDocument2 pagesLdica Session Planner2022-23 LavanyavijaykannamallaNo ratings yet

- HVDC Micro Lesson PlanDocument3 pagesHVDC Micro Lesson PlanMr. R. Jagan EEENo ratings yet

- Flat Lesson PlanDocument2 pagesFlat Lesson PlanNeelamani SamalNo ratings yet

- DICADocument2 pagesDICAak5775No ratings yet

- SS LS 2023-2024Document4 pagesSS LS 2023-2024sudhamaniNo ratings yet

- R2018 Curriculum and SyllabiDocument15 pagesR2018 Curriculum and SyllabiMANIMEGALAI M. ECENo ratings yet

- High Clock Rate CMOS Digital Pipeline MultiplierAcDocument5 pagesHigh Clock Rate CMOS Digital Pipeline MultiplierAcIosif MudraNo ratings yet

- Department of Mechanical EngineeringDocument8 pagesDepartment of Mechanical EngineeringKishore RaviNo ratings yet

- Introduction: Digital Systems & Logic Design: by Taweesak ReungpeerakulDocument19 pagesIntroduction: Digital Systems & Logic Design: by Taweesak ReungpeerakulSoman AunNo ratings yet

- C++ Lesson PlanDocument2 pagesC++ Lesson PlansivaNo ratings yet

- Department of Electronics & Communication HKE's S.L.N College of Engineering Assignment BankDocument2 pagesDepartment of Electronics & Communication HKE's S.L.N College of Engineering Assignment Bankvijayarani.katkamNo ratings yet

- Ec6202 Scad MSM PDFDocument92 pagesEc6202 Scad MSM PDFManjuladevi KannanNo ratings yet

- BEE1023 EE113 Digital Electronics 1 Ver2022Document4 pagesBEE1023 EE113 Digital Electronics 1 Ver2022AYYNo ratings yet

- DLD Micro Lesson PlaN 2 - Section CDocument4 pagesDLD Micro Lesson PlaN 2 - Section CMadhavarao K0% (1)

- Embedded SystemDocument28 pagesEmbedded Systemnanobala15No ratings yet

- DSP Couse FileDocument236 pagesDSP Couse FileSamuel BhukyaNo ratings yet

- $warnandhira: Vlsi SimulationDocument3 pages$warnandhira: Vlsi SimulationRamarao BNo ratings yet

- CAS HandoutDocument2 pagesCAS HandoutMohan KolaNo ratings yet

- DIGITAL Course Plan FinalDocument10 pagesDIGITAL Course Plan FinalponniNo ratings yet

- Cs3351-Lesson PlanDocument5 pagesCs3351-Lesson PlandhivyabharathyNo ratings yet

- Rajalakshmi Engineering College: Thandalam, Chennai - 602 105 Lesson PlanDocument6 pagesRajalakshmi Engineering College: Thandalam, Chennai - 602 105 Lesson PlanJefferson ThompsonNo ratings yet

- De-Lesson PlanDocument4 pagesDe-Lesson PlanEzhil Azhahi.AM Assistant ProfessorNo ratings yet

- Introduction Number Systems and Conversion: This Chapter in The Book IncludesDocument29 pagesIntroduction Number Systems and Conversion: This Chapter in The Book Includes임동훈No ratings yet

- Digital Communication: Department of EceDocument4 pagesDigital Communication: Department of EceJefferson ThompsonNo ratings yet

- R23 Yca2002Document4 pagesR23 Yca2002munnisujliNo ratings yet

- JDocument1 pageJ;(No ratings yet

- 4041Document4 pages4041Manu ENo ratings yet

- Vlsidt Syllabus Detailing - 2k15-CourseDocument2 pagesVlsidt Syllabus Detailing - 2k15-CoursevinodNo ratings yet

- Course Handout: Amity University RajasthanDocument5 pagesCourse Handout: Amity University RajasthanKaran MaanNo ratings yet

- Network Programming: Course No: IS ZC462 Course Code:1627Document4 pagesNetwork Programming: Course No: IS ZC462 Course Code:1627reddythNo ratings yet

- CS3351 LPDocument5 pagesCS3351 LPsyed1188No ratings yet

- CS8602 CD Course PlanDocument7 pagesCS8602 CD Course PlanPrasanna LathaNo ratings yet

- Cs8251 Lesson PlanDocument2 pagesCs8251 Lesson Planshajitha120450% (2)

- PDC Lesson Plan - II-IIDocument2 pagesPDC Lesson Plan - II-IISrinivasu RajuNo ratings yet

- Power ElectronicsDocument107 pagesPower ElectronicsMr. VenkateshNo ratings yet

- STLDDocument2 pagesSTLDPrasanth VarasalaNo ratings yet

- Monte Carlo Frameworks: Building Customisable High-performance C++ ApplicationsFrom EverandMonte Carlo Frameworks: Building Customisable High-performance C++ ApplicationsRating: 1.5 out of 5 stars1.5/5 (2)

- UntitledDocument3 pagesUntitledRameshchandra K ECENo ratings yet

- K Rameshchandra - Sept - 2022 - R&D - ReportDocument4 pagesK Rameshchandra - Sept - 2022 - R&D - ReportRameshchandra K ECENo ratings yet

- A Deep Learning Approach For Efficient Decision Making in Healthcare InformaticsDocument14 pagesA Deep Learning Approach For Efficient Decision Making in Healthcare InformaticsRameshchandra K ECENo ratings yet

- RT22045042019Document1 pageRT22045042019Rameshchandra K ECENo ratings yet

- UntitledDocument156 pagesUntitledRameshchandra K ECENo ratings yet

- Unit 1Document22 pagesUnit 1Rameshchandra K ECENo ratings yet

- EthicalDocument2 pagesEthicalRameshchandra K ECENo ratings yet

- UntitledDocument1 pageUntitledRameshchandra K ECENo ratings yet

- UntitledDocument1 pageUntitledRameshchandra K ECENo ratings yet

- Convert The Following. I. AB Ii. 1234 Iii. 10110011 Iv. (24.315) v. (68BE)Document1 pageConvert The Following. I. AB Ii. 1234 Iii. 10110011 Iv. (24.315) v. (68BE)Rameshchandra K ECENo ratings yet

- DLD Unit-2 NotesDocument36 pagesDLD Unit-2 NotesRameshchandra K ECENo ratings yet

- UntitledDocument1 pageUntitledRameshchandra K ECENo ratings yet

- DLD Unit-4 NotesDocument48 pagesDLD Unit-4 NotesRameshchandra K ECENo ratings yet

- Analog Communication April 2019Document5 pagesAnalog Communication April 2019Rameshchandra K ECENo ratings yet

- DLD Unit-5 NotesDocument16 pagesDLD Unit-5 NotesRameshchandra K ECENo ratings yet

- Course Name Digital Logic Design Year/Semester II B. Tech/I Sem L T P C Regulation Year 2021-2022 3 0 0 3 Digital Logic DesignDocument2 pagesCourse Name Digital Logic Design Year/Semester II B. Tech/I Sem L T P C Regulation Year 2021-2022 3 0 0 3 Digital Logic DesignRameshchandra K ECENo ratings yet

- Area Profiler and NAD - LoginsDocument2 pagesArea Profiler and NAD - LoginsRameshchandra K ECENo ratings yet

- FURUNO FAR-FR2855 Installation Manual RDP115 Basic DiagramsDocument86 pagesFURUNO FAR-FR2855 Installation Manual RDP115 Basic Diagramstoumassis_pNo ratings yet

- Kingspan Jindal Ext. Wall Panel SystemDocument32 pagesKingspan Jindal Ext. Wall Panel Systemabhay kumarNo ratings yet

- Kami 3Document2 pagesKami 3KumarNo ratings yet

- Comparision Between Soyabean Milk and Natural MilkDocument3 pagesComparision Between Soyabean Milk and Natural MilkShivam SinghNo ratings yet

- MQP Keys Mbf106Document18 pagesMQP Keys Mbf106Rajeev DayalNo ratings yet

- Biamp Manual Tesira Hd-1 Oct15-1Document16 pagesBiamp Manual Tesira Hd-1 Oct15-1Rachmat Guntur Dwi PutraNo ratings yet

- Relational Model ConceptsDocument5 pagesRelational Model ConceptsAbhinandan BhatNo ratings yet

- Prof. Alberto Berizzi: Dipartimento Di Energia Ph. 02 2399 3728 Email: Alberto - Berizzi@polimi - ItDocument32 pagesProf. Alberto Berizzi: Dipartimento Di Energia Ph. 02 2399 3728 Email: Alberto - Berizzi@polimi - ItMohammed OsmanNo ratings yet

- Toefl Short Course Sesi 3 ReadingDocument8 pagesToefl Short Course Sesi 3 ReadingNurul Hidayati ListyaningrumNo ratings yet

- Bachelor Thesis Presentation ExampleDocument4 pagesBachelor Thesis Presentation ExampleFiona Phillips100% (2)

- Effects of Kinesio Taping On Hemiplegic Hand in Patients With Upper Limb Post-Stroke SpasticityDocument7 pagesEffects of Kinesio Taping On Hemiplegic Hand in Patients With Upper Limb Post-Stroke Spasticityhgood1001No ratings yet

- Iso 13849-1-2023Document164 pagesIso 13849-1-2023gokhanekinci92No ratings yet

- Kagramian Report 2Document12 pagesKagramian Report 2api-700030358No ratings yet

- WellPlan ReportDocument34 pagesWellPlan ReportElmar CahangirovNo ratings yet

- Chapter 11 Power Point (1) - 5 PDFDocument25 pagesChapter 11 Power Point (1) - 5 PDFMuhammad NaveedNo ratings yet

- Exp 01 Determination of DensityDocument16 pagesExp 01 Determination of DensityParithyiMuraliTharanNo ratings yet

- Tech Gr9 m3 Hydraulic Pneumatic SystemsDocument26 pagesTech Gr9 m3 Hydraulic Pneumatic SystemsEduBoard100% (1)

- Stock April 2020Document5 pagesStock April 2020roby aldiNo ratings yet

- FM ExercisesDocument5 pagesFM ExercisesanililhanNo ratings yet

- FGD Vs CompetitorCustomer - Final - LF14000NN & P559000Document9 pagesFGD Vs CompetitorCustomer - Final - LF14000NN & P559000munhNo ratings yet

- Differential Partitioning of Betacyanins and Betaxanthins Employing Aqueous Two Phase ExtractionDocument8 pagesDifferential Partitioning of Betacyanins and Betaxanthins Employing Aqueous Two Phase ExtractionPaul Jefferson Flores HurtadoNo ratings yet

- How To Use Ladybird Readers PDFDocument18 pagesHow To Use Ladybird Readers PDFJonas SilvaNo ratings yet

- Chapter 22 - Physics - Coordinated Science - IGCSE CambridgeDocument154 pagesChapter 22 - Physics - Coordinated Science - IGCSE CambridgeAlvin DuaneNo ratings yet

- ICD - GujaratDocument1,038 pagesICD - GujaratsunilkumarchaudharyNo ratings yet

- Holbright Hb-8212Document1 pageHolbright Hb-8212Eliana Cristina100% (1)

- Technical Drawing ToolsDocument11 pagesTechnical Drawing Toolsdaphne brown-mundleNo ratings yet

- Guide To Iso 9001 2015 PDFDocument15 pagesGuide To Iso 9001 2015 PDFahmed nawaz100% (2)