Professional Documents

Culture Documents

Untitled

Untitled

Uploaded by

Helder CruzOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Untitled

Untitled

Uploaded by

Helder CruzCopyright:

Available Formats

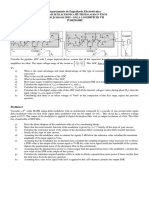

DEPARTAMENTO DE ENGENHARIA ELECTROTÉCNICA

3º TESTE DE ELECTRÓNICA III (2013/2014)

12 DE JUNHO DE 2013 – GRANDE AUDITÓRIO

14:00/15:15H

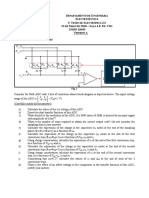

PROBLEM 1:

Consider a second order PLL with the block diagram depicted in Figure 1. The frequency of the

input frequency is 200 Mrad.s-1. Consider that the output frequency of the VCO as a function of the

( )

285 + 1 − e − (vc − 4V ) × 100 if vc > 4 V

control voltage is given by: ωOUT ( vc ) = 5 + 80 × ( vc − 0.5) if 0.5V < vc ≤ 4V [Mrad/s]

5 if vc ≤ 0.5 V

400

384.752

350

300

ωi Id(t) vc(t) v (t) 250

out

PD F(s) VCO ω.out v.c 200

vin(t) ωout ( ) 150

Figure 1: Block diagram of the PLL 100

50

5

0

0 1 2 3 4 5 6 7 8 9 10

0 v.c 10

Figure 2: VCO transfer function

a) Determine the linear model of the VCO for the input frequency value.

b) Considering that a XOR gate is used as phase detector, determine the linear model of the phase

detector, assuming that VDD=5V and that VSS=0V, justify your answer.

c) Considering that the loop filter (F(s)) has a pole and a zero, suggest a circuit that is capable of

implementing this transfer function, justify your answer by calculating the circuit transfer

function.

d) Calculate the closed loop transfer function of the PLL and calculate the values of the components

of the loop filter in order to obtain a closed loop bandwidth of 0.1 Mrad/s and a closed loop

system critically damped.

e) Determine the lock-in range of the PLL assuming that the input signal frequency changes slowly.

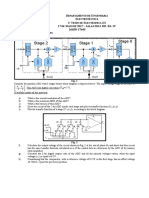

f) Draw the circuit of a 3-state phase-frequency detector with a charge pump current of 10 µA and

determine its linear model.

g) Considering that the loop filter (F(s)) has a pole and a zero, suggest a circuit that is capable of

implementing this transfer function using a charge pump, justify your answer by calculating the

circuit transfer function.

h) Explain why the static phase error of the PLL with this new phase detector is 0.

i) Calculate the closed loop transfer function of the PLL and calculate the values of the components

of the loop filter in order to obtain a closed loop bandwidth of 0.1 Mrad/s and a closed loop

system critically damped.

j) Explain how you would modify the PLL block diagram of figure 1 in order for the PLL to

produce an output frequency equal to 200 Mrad/s from an input frequency equal to 10 Mrad/s.

Calculate any new parameter value of the new block diagram.

You might also like

- SolutionsShumway PDFDocument82 pagesSolutionsShumway PDFjuve A.No ratings yet

- DSA00260586Document6 pagesDSA00260586Msi InfotronicNo ratings yet

- DR-130 Service ManualDocument6 pagesDR-130 Service ManualZarko MatusicNo ratings yet

- Chheda Electricals & Electronics Pvt. LTD.: Product Category: Electronic Ignition UnitDocument3 pagesChheda Electricals & Electronics Pvt. LTD.: Product Category: Electronic Ignition UnitNaveen KumarNo ratings yet

- TP ConvetionDocument11 pagesTP ConvetiondoudouNo ratings yet

- Analog Electronics: Lab Report 4Document8 pagesAnalog Electronics: Lab Report 4Bird BirdNo ratings yet

- Pavans PPT NewDocument23 pagesPavans PPT Newk hemalathaNo ratings yet

- Generators, Motors and How We Get ElectricityDocument14 pagesGenerators, Motors and How We Get ElectricityRizki Jak ManiaNo ratings yet

- Electrical Systems Simulation LAB MANUAL 2019-2020Document25 pagesElectrical Systems Simulation LAB MANUAL 2019-2020Vinay Kumar50% (2)

- I (A) Vs V (V)Document4 pagesI (A) Vs V (V)Freijoth MuñozNo ratings yet

- Exp 8Document9 pagesExp 8neelu marturuNo ratings yet

- ECSE 210 Final Review SessionDocument32 pagesECSE 210 Final Review SessionabccdesNo ratings yet

- Chapter 6. Linear Programming (Q)Document6 pagesChapter 6. Linear Programming (Q)Kristina Cassandra CababatNo ratings yet

- Student Name: A.F.M SALEM MAULA Exam Roll: Class Roll: 2387 Department of PhysicsDocument21 pagesStudent Name: A.F.M SALEM MAULA Exam Roll: Class Roll: 2387 Department of Physicsafm kollolNo ratings yet

- Hall Voltage Vs Magnetic Field For P-TypeDocument2 pagesHall Voltage Vs Magnetic Field For P-TypeSushma Lakshmi RNo ratings yet

- 03 State SpaceDocument11 pages03 State Spacehmanghh2000No ratings yet

- Lab 9Document13 pagesLab 9A. AlghamdiNo ratings yet

- Fuzzy Based DC/DC Boost Converter Design To Enhance Efficacy of Photovoltaic ApplicationDocument12 pagesFuzzy Based DC/DC Boost Converter Design To Enhance Efficacy of Photovoltaic ApplicationArijit SarkarNo ratings yet

- 16bis0091 VL2017181003417 Ast03Document4 pages16bis0091 VL2017181003417 Ast03MassSomeshNo ratings yet

- Laboratoare MEIADocument6 pagesLaboratoare MEIAMiruna Elena FloroiuNo ratings yet

- Chapt 08Document17 pagesChapt 08md.daud.ul.islamNo ratings yet

- Chopper Controlled DC DrivesDocument7 pagesChopper Controlled DC DrivesLasantha AbeykoonNo ratings yet

- Theory 3: Details Accepted Prepared Rev Date Rev NRDocument22 pagesTheory 3: Details Accepted Prepared Rev Date Rev NRRupam BaruahNo ratings yet

- Tugas TRK AsistenDocument34 pagesTugas TRK Asistennisa methildaarNo ratings yet

- Exercise:D1 B. Observation of ACF For A Sinusoidal WaveDocument11 pagesExercise:D1 B. Observation of ACF For A Sinusoidal WaveJarin TasnimNo ratings yet

- Indoor Voltage TransformersDocument4 pagesIndoor Voltage TransformersBruno Nemer TattonNo ratings yet

- Pool PowerMaster DatasheetDocument2 pagesPool PowerMaster DatasheetBazin TsegayeNo ratings yet

- 50-50 Rule: % Completion Budget EV ACDocument3 pages50-50 Rule: % Completion Budget EV ACMohammadNo ratings yet

- Graph ExelDocument2 pagesGraph Exelferhanerida359No ratings yet

- TDC 4 - enDocument4 pagesTDC 4 - enBruno Nemer TattonNo ratings yet

- Department of Electrical Engineering, IIT Delhi ELL100 Introduction To Electrical Engg: Problem Set 10Document3 pagesDepartment of Electrical Engineering, IIT Delhi ELL100 Introduction To Electrical Engg: Problem Set 10Osim AbesNo ratings yet

- Massuse ME-15N Series RelesDocument2 pagesMassuse ME-15N Series RelesMiguel PenarandaNo ratings yet

- Exp04Document4 pagesExp04asifasmat14No ratings yet

- Appendix A1 Data For The IEEE 10-Bus Distribution Test SystemDocument14 pagesAppendix A1 Data For The IEEE 10-Bus Distribution Test SystemSunil MåüřÿäNo ratings yet

- O Understand and Design The Working Principle of C K ConverterDocument3 pagesO Understand and Design The Working Principle of C K Converterakif amirNo ratings yet

- Development of Low-Cost Tesla Transformer For High Performance Testing 115 KV Line Post InsulatorDocument5 pagesDevelopment of Low-Cost Tesla Transformer For High Performance Testing 115 KV Line Post Insulatordcastrelos2000No ratings yet

- A6 Voltage Variations in CapacitorsDocument5 pagesA6 Voltage Variations in CapacitorsMark Jimely FullenteNo ratings yet

- Task 5: K S SOMESH (16BIS0091)Document4 pagesTask 5: K S SOMESH (16BIS0091)MassSomeshNo ratings yet

- Assignment No2 OISP 2024Document5 pagesAssignment No2 OISP 2024trichutichNo ratings yet

- Semiconductor Technical Data: Maximum Ratings Ordering InformationDocument7 pagesSemiconductor Technical Data: Maximum Ratings Ordering InformationArtur AgiNo ratings yet

- Ahmad Lukito - K2319005 - RLCDocument15 pagesAhmad Lukito - K2319005 - RLCAhmad LukitoNo ratings yet

- Cad - ProjectDocument8 pagesCad - ProjectShobyNo ratings yet

- Kurva Isoterm Langmuir: P (Torr)Document4 pagesKurva Isoterm Langmuir: P (Torr)syuqron habibNo ratings yet

- Ekonomi MikroDocument3 pagesEkonomi MikroSyafnavebiolaNo ratings yet

- N° Ciclo TC (Seg) V (RPM) H (%) MH (GR) MC (GR)Document2 pagesN° Ciclo TC (Seg) V (RPM) H (%) MH (GR) MC (GR)Jesús Francisco Vidaňa DuronNo ratings yet

- Mechatronics 1998 PaperDocument16 pagesMechatronics 1998 Paperaaroncete14No ratings yet

- Simulation Result - 100% THDI Vacon NXCDocument4 pagesSimulation Result - 100% THDI Vacon NXCbriamserna91No ratings yet

- AJ P26 DEPOSITO 10 (Star TCC)Document1 pageAJ P26 DEPOSITO 10 (Star TCC)César Luis Castillo ChiletNo ratings yet

- Kabale University: Faculty of Engineering & TechnologyDocument10 pagesKabale University: Faculty of Engineering & Technologykazahuura EdwardNo ratings yet

- KAZAHUURA EDWARD (2) at EdwardDocument9 pagesKAZAHUURA EDWARD (2) at Edwardkazahuura EdwardNo ratings yet

- Electrical EngineeringDocument3 pagesElectrical Engineeringخالد الغامديNo ratings yet

- (A) RC 1/200 For The Resistor, V Ir : Chapter 7, Solution 1Document97 pages(A) RC 1/200 For The Resistor, V Ir : Chapter 7, Solution 1Haseeb ArifNo ratings yet

- Design With Operational Amplifiers and Analog Integrated Circuits 4th Edition Sergio Franco Solutions ManualDocument28 pagesDesign With Operational Amplifiers and Analog Integrated Circuits 4th Edition Sergio Franco Solutions Manualpseudolatakia.drbn100% (23)

- Ir 2104Document14 pagesIr 2104Néstor BernalNo ratings yet

- BEAM DESIGN - RSLT - Member - Detail - 1 - 1 - 348Document22 pagesBEAM DESIGN - RSLT - Member - Detail - 1 - 1 - 348CSEC Uganda Ltd.No ratings yet

- EEN-612: Electrical Transients in Power Systems: Tutorial-03Document2 pagesEEN-612: Electrical Transients in Power Systems: Tutorial-03sohit srivastavaNo ratings yet

- RpdieukhiengocquayDocument9 pagesRpdieukhiengocquay21151016No ratings yet

- GraficasDocument4 pagesGraficasFreijoth MuñozNo ratings yet

- GraficasDocument4 pagesGraficasFreijoth MuñozNo ratings yet

- Electrical and Electronic Principles 3 Checkbook: The Checkbook SeriesFrom EverandElectrical and Electronic Principles 3 Checkbook: The Checkbook SeriesNo ratings yet

- D E E 2 T E III 5 D 2009 - S 1A - VII 10:00 00-11 30: Epartamento de Ngenharia LectrotécnicaDocument1 pageD E E 2 T E III 5 D 2009 - S 1A - VII 10:00 00-11 30: Epartamento de Ngenharia LectrotécnicaHelder CruzNo ratings yet

- Problem 1 A) : Given Dout VNQ Z 1 Z Vin 1 DoutDocument5 pagesProblem 1 A) : Given Dout VNQ Z 1 Z Vin 1 DoutHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- The ADC Requires 3 Conversion Steps, One Per Output Bit.: F F B - F B - F B - F B - FDocument2 pagesThe ADC Requires 3 Conversion Steps, One Per Output Bit.: F F B - F B - F B - F B - FHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- 6.02 Nbits +1.76 25,84 DB: SNR V VDocument2 pages6.02 Nbits +1.76 25,84 DB: SNR V VHelder CruzNo ratings yet

- Z V D F: Problem 1 A)Document5 pagesZ V D F: Problem 1 A)Helder CruzNo ratings yet

- Problem 1 A)Document5 pagesProblem 1 A)Helder CruzNo ratings yet

- UntitledDocument2 pagesUntitledHelder CruzNo ratings yet

- Epartamento de Ngenharia Lectrotécnica º Este de Lectrónica E Unho de ALA Difício ErsionDocument2 pagesEpartamento de Ngenharia Lectrotécnica º Este de Lectrónica E Unho de ALA Difício ErsionHelder CruzNo ratings yet

- UntitledDocument2 pagesUntitledHelder CruzNo ratings yet

- Ko1 10 Ko2 20: ωout vcDocument6 pagesKo1 10 Ko2 20: ωout vcHelder CruzNo ratings yet

- 1 A) B) C) D)Document2 pages1 A) B) C) D)Helder CruzNo ratings yet

- ADC Transfer Function: Vref 1VDocument5 pagesADC Transfer Function: Vref 1VHelder CruzNo ratings yet

- Epartamento de Ngenharia Lectrotécnica º Este de Lectrónica E Unho de Alas E DifícioDocument1 pageEpartamento de Ngenharia Lectrotécnica º Este de Lectrónica E Unho de Alas E DifícioHelder CruzNo ratings yet

- UntitledDocument2 pagesUntitledHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- 5 D J 2017 - S 1C E VII 17:00/18:15H - T: Departamento de Engenharia Electrotécnica 1 E E III / R 3 T 17:00/20:00H - EDocument2 pages5 D J 2017 - S 1C E VII 17:00/18:15H - T: Departamento de Engenharia Electrotécnica 1 E E III / R 3 T 17:00/20:00H - EHelder CruzNo ratings yet

- I V V V: PD F(S) VCO (T) (T) (T) (T)Document1 pageI V V V: PD F(S) VCO (T) (T) (T) (T)Helder CruzNo ratings yet

- Digital To Analog Converters: Conversores de Sinal - 2022/2023 Nuno Paulino - DEEC-FCT/UNLDocument29 pagesDigital To Analog Converters: Conversores de Sinal - 2022/2023 Nuno Paulino - DEEC-FCT/UNLHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- 14 D J 2011 - S 3.9 E Viii 13:00/16:00H: Departamento de Engenharia Electrotécnica 1º E E IIIDocument2 pages14 D J 2011 - S 3.9 E Viii 13:00/16:00H: Departamento de Engenharia Electrotécnica 1º E E IIIHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- Conversores Sinal ADocument55 pagesConversores Sinal AHelder CruzNo ratings yet

- Gain, Attenuation, and DecibelsDocument10 pagesGain, Attenuation, and DecibelsValentina NietoNo ratings yet

- Fishman Prefix Premium Blend BenutzerhandbuchDocument2 pagesFishman Prefix Premium Blend BenutzerhandbuchALFONS KÖTTINGNo ratings yet

- 5.0 Frequency ResponseDocument80 pages5.0 Frequency ResponseIka PriyantiNo ratings yet

- 15EC44 NotesDocument126 pages15EC44 NoteslathavenkyNo ratings yet

- Brüel&Kjær 2607 - Measuring Amplifier - Instruction ManualDocument72 pagesBrüel&Kjær 2607 - Measuring Amplifier - Instruction ManualViktor DömeNo ratings yet

- AsciiDocument1 pageAsciiAniket GuravNo ratings yet

- HYPHA ManualDocument19 pagesHYPHA ManualBrent CrayonNo ratings yet

- Baseband P User GuidelinesDocument41 pagesBaseband P User GuidelinesSaid IhadadeneNo ratings yet

- Experiment - 7 Verification of Sampling Theorem: Name:P.Sai Manoj Date: ROLL NO. 16H61A044 Page NoDocument3 pagesExperiment - 7 Verification of Sampling Theorem: Name:P.Sai Manoj Date: ROLL NO. 16H61A044 Page NoManoj PuliNo ratings yet

- Eqs PresonusDocument5 pagesEqs Presonussergioleit100% (2)

- Digital Signal Processing: Md. Manjurul Gani, Lecturer, EEE, CUETDocument33 pagesDigital Signal Processing: Md. Manjurul Gani, Lecturer, EEE, CUETJamil RofiNo ratings yet

- DIP - Assignment 1 SolutionDocument5 pagesDIP - Assignment 1 Solutionharrisonaeshim27No ratings yet

- 111 - Presentation-14 LCCDE and Block DiagramsDocument13 pages111 - Presentation-14 LCCDE and Block DiagramsDeniz SummerNo ratings yet

- EC6501 DC Rejinpaul Important QuestionsDocument1 pageEC6501 DC Rejinpaul Important QuestionsEASACOLLEGENo ratings yet

- Course Schedule3Document3 pagesCourse Schedule3Matin Sadat BeheshtiNo ratings yet

- Digital Indicator - DN50W PDFDocument1 pageDigital Indicator - DN50W PDFvudinhnambrNo ratings yet

- Project of Dcs 1Document13 pagesProject of Dcs 1Pranil KambleNo ratings yet

- Digital Signal Processing - DR - Prarthan MehtaDocument61 pagesDigital Signal Processing - DR - Prarthan Mehtaelienai1No ratings yet

- Fellgett's Advantage or The Multiplex AdvantageDocument13 pagesFellgett's Advantage or The Multiplex AdvantageMichelle HoltNo ratings yet

- STR-K800 K900Document68 pagesSTR-K800 K900rooster120No ratings yet

- Lecure-4 Biopotential Amplifiers & FiltersDocument87 pagesLecure-4 Biopotential Amplifiers & FiltersNoor Ahmed75% (4)

- DSPDocument28 pagesDSPPalani GnanavelNo ratings yet

- MTP 440 DM: FeaturesDocument2 pagesMTP 440 DM: Featuresseisfuegos1No ratings yet

- Control Tutorials For MATLAB and Simulink - Introduction - Digital Controller DesignDocument12 pagesControl Tutorials For MATLAB and Simulink - Introduction - Digital Controller DesignYasir AlameenNo ratings yet

- Arba Minch University Arba Minch Institute of Technology Department of Electrical and Computer Engineering TitleDocument43 pagesArba Minch University Arba Minch Institute of Technology Department of Electrical and Computer Engineering TitleDawit LelisaNo ratings yet

- Pulse and Digital CircuitDocument32 pagesPulse and Digital Circuitabdulkadir mohamedNo ratings yet

- Digital Signal Processing Lecture Notes 2 PageDocument5 pagesDigital Signal Processing Lecture Notes 2 PageLungelo MkhwanaziNo ratings yet

- Multimedia Commnication Unit 4 VTUDocument41 pagesMultimedia Commnication Unit 4 VTUraghudathesh100% (1)

- 50hz Noise Removal From ECG Power SupplyDocument6 pages50hz Noise Removal From ECG Power SupplyVidhya AigalNo ratings yet

- Experiment No.4Document3 pagesExperiment No.4Tejas PatilNo ratings yet