Professional Documents

Culture Documents

Untitled

Untitled

Uploaded by

Helder CruzOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Untitled

Untitled

Uploaded by

Helder CruzCopyright:

Available Formats

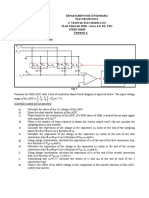

DEPARTAMENTO DE ENGENHARIA

ELECTROTÉCNICA

2º TESTE DE ELECTRÓNICA III

17 DE MAIO DE 2017 – SALAS 201 E 202 ED. IV

16H30-17H45

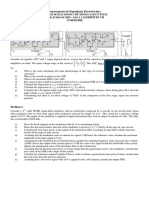

PROBLEM 1: A/D CONVERTERS

Stage 2 Stage 1 Stage 0

vres2 vres0

Sample

Sample

Sample

& Hold

& Hold

& Hold

vin + 2 + 2

- - v

vDAC2 DAC1

DAC

DAC

ADC

ADC

ADC

clk 2 2 clk 2 2 clk 2

dout2 dout1 dout0

Fig. 1

Consider the pipeline ADC with 3 stages whose block diagram is depicted above. The input voltage range of the ADC is

Vref Vref

, . This ADC has digital correction (Vref=1 V).

2 2

(Carefully justify all the answers)

a) What is the overall resolution of the ADC?

b) What is the maximum SNR of this ADC?

c) What is the latency of this ADC?

d) Draw the circuit of the 2-bit ADC inside each stage and plot its transfer function (Dout(vin))

e) Plot the transfer function of a stage (Vres(vin)), according to the block diagram.

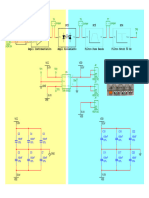

F1

-

2C C 2C Vout

+0.5Vref

F2 F1 F2 F1 F1 F2 +

-0.5Vref b1 b1 b0 b0

vin

Fig. 2

f) Calculate the output voltage of the circuit shown in Fig. 2 at the end of phase F2 and show that this circuit

has the same transfer function calculated in e) if the control bits are determine by the ADC of d) (assume

ideal amplifier)

g) Calculate the 3-bit digital output code of the ADC and all the internal voltages values, when the input

voltage (vin) is equal to 0.2V.

h) Considering that the comparator, with a reference voltage of 0.25V in the first stage, has an offset voltage

of -70mV, repeat the previous question.

You might also like

- AN30G6 XCoursehintDocument178 pagesAN30G6 XCoursehintCatalin SerbanescuNo ratings yet

- Operational Amplifiers and Its Applications: Learning ObjectivesDocument49 pagesOperational Amplifiers and Its Applications: Learning ObjectiveskalyanNo ratings yet

- Cambridge-Audio Azur 340a SeDocument20 pagesCambridge-Audio Azur 340a SeChu Tiến Thịnh100% (1)

- TE550 Blending Controller: Installation, Use and Service ManualDocument89 pagesTE550 Blending Controller: Installation, Use and Service Manualm75% (4)

- 14 D J 2011 - S 3.9 E Viii 13:00/16:00H: Departamento de Engenharia Electrotécnica 1º E E IIIDocument2 pages14 D J 2011 - S 3.9 E Viii 13:00/16:00H: Departamento de Engenharia Electrotécnica 1º E E IIIHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- UntitledDocument2 pagesUntitledHelder CruzNo ratings yet

- 6.02 Nbits +1.76 25,84 DB: SNR V VDocument2 pages6.02 Nbits +1.76 25,84 DB: SNR V VHelder CruzNo ratings yet

- Bloques SubcircuitosDocument1 pageBloques SubcircuitosnessublimeNo ratings yet

- E05 OHL-1 CT (Modified)Document3 pagesE05 OHL-1 CT (Modified)arunNo ratings yet

- Guía de Juntas OmocineticasDocument84 pagesGuía de Juntas OmocineticasHugo MagallanesNo ratings yet

- Aec Lab ManualDocument33 pagesAec Lab Manualganga_ch1No ratings yet

- SKEE 2742 Basic Electronics Lab: Experiment 2 BJT Small-Signal AmplifierDocument8 pagesSKEE 2742 Basic Electronics Lab: Experiment 2 BJT Small-Signal Amplifierمحمد ابو جرادNo ratings yet

- SparkFun HX711 Load CellDocument1 pageSparkFun HX711 Load CellMuhammad Nur IkhsanNo ratings yet

- SS4H-GO Schematic v. 1.1Document1 pageSS4H-GO Schematic v. 1.1Marek DužíNo ratings yet

- Concept of Device Modeling (Version 1.0) : Bee Technologies IncDocument13 pagesConcept of Device Modeling (Version 1.0) : Bee Technologies IncEngr RatulNo ratings yet

- ProposalDocument22 pagesProposalGodfrey ArchibongNo ratings yet

- D2822N ShaoxingSilicoreTechnologyDocument5 pagesD2822N ShaoxingSilicoreTechnologyandrebuhlerNo ratings yet

- Atmega328 Based Circuit Diagram of The ProjectDocument1 pageAtmega328 Based Circuit Diagram of The ProjectKav Mav100% (2)

- SonyDocument17 pagesSonycat cit cutNo ratings yet

- P 16 ProDocument1 pageP 16 Proconfui_463838409No ratings yet

- Assignment 1 Summer Session 2009 10Document5 pagesAssignment 1 Summer Session 2009 10asdf2121No ratings yet

- Gateeasy D To A PDFDocument3 pagesGateeasy D To A PDFShubham kumarNo ratings yet

- Digital To Analog Converter (Dac)Document3 pagesDigital To Analog Converter (Dac)Shimaa BarakatNo ratings yet

- Analog IcDocument3 pagesAnalog IcPraveen kumarNo ratings yet

- Electronic Circuit AnalysisDocument23 pagesElectronic Circuit AnalysisAnonymous uspYoqENo ratings yet

- AN701Document32 pagesAN701Apostasia VitinhoNo ratings yet

- Midterm 11 2022Document4 pagesMidterm 11 2022kunghsiangyuNo ratings yet

- Universidad Politecnica Salesiana. Laboratorio Analogica: Practica 5: Análisis de Característica de Un Diodo A SilicioDocument3 pagesUniversidad Politecnica Salesiana. Laboratorio Analogica: Practica 5: Análisis de Característica de Un Diodo A SiliciojefersonNo ratings yet

- RS232 Connector: AT89C51/52 Programmer Revised by Chin-Shiuh Shieh 2000/03/27Document1 pageRS232 Connector: AT89C51/52 Programmer Revised by Chin-Shiuh Shieh 2000/03/27Areeb AhmedNo ratings yet

- (FL Challenge N3) M Analog To Digital Conversion (ADC)Document2 pages(FL Challenge N3) M Analog To Digital Conversion (ADC)Cent SecurityNo ratings yet

- Pipelined AdcDocument14 pagesPipelined AdcVP SinghNo ratings yet

- Datasheet CXA1352ASDocument17 pagesDatasheet CXA1352ASBuchoriNo ratings yet

- EEE308 Midterm Fall 2023Document3 pagesEEE308 Midterm Fall 2023ANWAR SHADMANNo ratings yet

- Electronics Design MOSFETDocument14 pagesElectronics Design MOSFETbhanuNo ratings yet

- DAC Example Problem - TutorialspointDocument5 pagesDAC Example Problem - Tutorialspointdiether.gozumNo ratings yet

- Statcom PDFDocument77 pagesStatcom PDFMohan ThakreNo ratings yet

- Multistage AmplifiersDocument22 pagesMultistage AmplifiersParvinder SinghNo ratings yet

- Iw1710-01 For 12V@1.5A Adapter DesignDocument17 pagesIw1710-01 For 12V@1.5A Adapter DesignИван АлексиевNo ratings yet

- OP AMP AssignmentDocument8 pagesOP AMP AssignmentPradeep ChauhanNo ratings yet

- Diode Circuit - DPP 03 (Of Lec 09)Document3 pagesDiode Circuit - DPP 03 (Of Lec 09)devdipika992434No ratings yet

- Lab 02Document6 pagesLab 02Rehan BasharatNo ratings yet

- Mi21mtech11003 - BM5023 - 2021 - Lab 2Document7 pagesMi21mtech11003 - BM5023 - 2021 - Lab 2Subhranil RoyNo ratings yet

- General Purpose Amplification ( 12V, 3A) : TransistorsDocument4 pagesGeneral Purpose Amplification ( 12V, 3A) : TransistorsTamulmol69ersNo ratings yet

- High Frequency Laser SoundDocument1 pageHigh Frequency Laser SoundBunyamin AnilNo ratings yet

- Prepared By: : EENG 262: Electronics 2Document6 pagesPrepared By: : EENG 262: Electronics 2علي حسنNo ratings yet

- SSM 2120 Nivel Detector dn126Document8 pagesSSM 2120 Nivel Detector dn126Edson Francisco SilvaNo ratings yet

- ConvertersDocument54 pagesConvertersyoboiiii649No ratings yet

- 4-EC-IES-2013-Conventional Paper-IIDocument6 pages4-EC-IES-2013-Conventional Paper-IIDIGITAL BUSINESSNo ratings yet

- 2-Fold Analogue Limit Monitor 62 100 Safety-Related: Connection Not RequiredDocument20 pages2-Fold Analogue Limit Monitor 62 100 Safety-Related: Connection Not RequiredMohamed OmarNo ratings yet

- CsDocument27 pagesCssujit24chavadaNo ratings yet

- Dýgýtal Voltmeter, Frequencymeter, Ammeter and Voltmeter-Ammeter Dv-Din / Df-Din / Da-Din / Dav-72Document1 pageDýgýtal Voltmeter, Frequencymeter, Ammeter and Voltmeter-Ammeter Dv-Din / Df-Din / Da-Din / Dav-72Zohaib SiddiqueNo ratings yet

- FILTROSDocument3 pagesFILTROSSergio GilNo ratings yet

- Tutorial 5Document3 pagesTutorial 5Saransh MittalNo ratings yet

- Adobe Scan 03 Oct 2023Document5 pagesAdobe Scan 03 Oct 2023Amzad KhanNo ratings yet

- KC868 A128 SchematicDocument13 pagesKC868 A128 SchematicMarek DužíNo ratings yet

- Digital To Analog Converters: Andrew Gardner Muhammad Salman David Fernandes Jevawn RobertsDocument35 pagesDigital To Analog Converters: Andrew Gardner Muhammad Salman David Fernandes Jevawn Robertsmohan inumarthiNo ratings yet

- Single-Ended To Differential Using A Two Op-Amp CircuiDocument9 pagesSingle-Ended To Differential Using A Two Op-Amp CircuiSanjay ParelkarNo ratings yet

- Schematic 1 - TransmitterDocument1 pageSchematic 1 - TransmittermeghsnrynnNo ratings yet

- Simple Addition Permits Voltage Control of DC-DC Converter's OutputDocument4 pagesSimple Addition Permits Voltage Control of DC-DC Converter's OutputCARLOSNo ratings yet

- Dual Power Operational Amplifier: Features DescriptionDocument10 pagesDual Power Operational Amplifier: Features DescriptionlyndondrNo ratings yet

- R1 200K R2 1K C1 0.1uf C2 P1 P2: Audioanalyzer V2.0Document1 pageR1 200K R2 1K C1 0.1uf C2 P1 P2: Audioanalyzer V2.0joxNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- D E E 2 T E III 5 D 2009 - S 1A - VII 10:00 00-11 30: Epartamento de Ngenharia LectrotécnicaDocument1 pageD E E 2 T E III 5 D 2009 - S 1A - VII 10:00 00-11 30: Epartamento de Ngenharia LectrotécnicaHelder CruzNo ratings yet

- The ADC Requires 3 Conversion Steps, One Per Output Bit.: F F B - F B - F B - F B - FDocument2 pagesThe ADC Requires 3 Conversion Steps, One Per Output Bit.: F F B - F B - F B - F B - FHelder CruzNo ratings yet

- Problem 1 A) : Given Dout VNQ Z 1 Z Vin 1 DoutDocument5 pagesProblem 1 A) : Given Dout VNQ Z 1 Z Vin 1 DoutHelder CruzNo ratings yet

- UntitledDocument2 pagesUntitledHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- Z V D F: Problem 1 A)Document5 pagesZ V D F: Problem 1 A)Helder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- Problem 1 A)Document5 pagesProblem 1 A)Helder CruzNo ratings yet

- Epartamento de Ngenharia Lectrotécnica º Este de Lectrónica E Unho de Alas E DifícioDocument1 pageEpartamento de Ngenharia Lectrotécnica º Este de Lectrónica E Unho de Alas E DifícioHelder CruzNo ratings yet

- 1 A) B) C) D)Document2 pages1 A) B) C) D)Helder CruzNo ratings yet

- Epartamento de Ngenharia Lectrotécnica º Este de Lectrónica E Unho de ALA Difício ErsionDocument2 pagesEpartamento de Ngenharia Lectrotécnica º Este de Lectrónica E Unho de ALA Difício ErsionHelder CruzNo ratings yet

- 6.02 Nbits +1.76 25,84 DB: SNR V VDocument2 pages6.02 Nbits +1.76 25,84 DB: SNR V VHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- 5 D J 2017 - S 1C E VII 17:00/18:15H - T: Departamento de Engenharia Electrotécnica 1 E E III / R 3 T 17:00/20:00H - EDocument2 pages5 D J 2017 - S 1C E VII 17:00/18:15H - T: Departamento de Engenharia Electrotécnica 1 E E III / R 3 T 17:00/20:00H - EHelder CruzNo ratings yet

- Ko1 10 Ko2 20: ωout vcDocument6 pagesKo1 10 Ko2 20: ωout vcHelder CruzNo ratings yet

- ADC Transfer Function: Vref 1VDocument5 pagesADC Transfer Function: Vref 1VHelder CruzNo ratings yet

- 14 D J 2011 - S 3.9 E Viii 13:00/16:00H: Departamento de Engenharia Electrotécnica 1º E E IIIDocument2 pages14 D J 2011 - S 3.9 E Viii 13:00/16:00H: Departamento de Engenharia Electrotécnica 1º E E IIIHelder CruzNo ratings yet

- UntitledDocument2 pagesUntitledHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- UntitledDocument2 pagesUntitledHelder CruzNo ratings yet

- Digital To Analog Converters: Conversores de Sinal - 2022/2023 Nuno Paulino - DEEC-FCT/UNLDocument29 pagesDigital To Analog Converters: Conversores de Sinal - 2022/2023 Nuno Paulino - DEEC-FCT/UNLHelder CruzNo ratings yet

- I V V V: PD F(S) VCO (T) (T) (T) (T)Document1 pageI V V V: PD F(S) VCO (T) (T) (T) (T)Helder CruzNo ratings yet

- Conversores Sinal ADocument55 pagesConversores Sinal AHelder CruzNo ratings yet

- 12GX190F Spec Sheet Rev 3Document1 page12GX190F Spec Sheet Rev 3wyatt-jangoNo ratings yet

- Launching A New ProductDocument22 pagesLaunching A New ProductNayomi Ekanayake0% (1)

- Unit 3: Science and Technology and The Human PersonDocument35 pagesUnit 3: Science and Technology and The Human PersonKennethNo ratings yet

- Uce-Ct220S Fault Locator: HOW TO Update TutorialDocument4 pagesUce-Ct220S Fault Locator: HOW TO Update TutorialWawan sahiriNo ratings yet

- Kron PDFDocument8 pagesKron PDFJuan BerríosNo ratings yet

- Compare Your App's Android Vitals and Ratings With Custom Peer Groups - Play Console HelpDocument2 pagesCompare Your App's Android Vitals and Ratings With Custom Peer Groups - Play Console HelpIndobhasa MogNo ratings yet

- Oracle Database 12c Global Data Services - D79244GC10 - 1080544 - USDocument2 pagesOracle Database 12c Global Data Services - D79244GC10 - 1080544 - USJinendraabhiNo ratings yet

- CCD Camera Manual PDFDocument29 pagesCCD Camera Manual PDFAnamNo ratings yet

- Jaw CrusherDocument3 pagesJaw CrusherAlpaniSaraBiaNo ratings yet

- VLF Regen RXDocument6 pagesVLF Regen RXBảo Bình100% (1)

- PDS S-Series Electronic MarshallingDocument42 pagesPDS S-Series Electronic MarshallingisraelalmaguerNo ratings yet

- Spatial-Temporal Information Aggregation and Cross-Modality Interactive Learning For RGB-D-Based Human Action RecognitionDocument12 pagesSpatial-Temporal Information Aggregation and Cross-Modality Interactive Learning For RGB-D-Based Human Action RecognitionPrajwal GNo ratings yet

- SLA Languages ThesisDocument432 pagesSLA Languages ThesismattengggNo ratings yet

- Microsoft Exchange Server PowerShell Essentials - Sample ChapterDocument21 pagesMicrosoft Exchange Server PowerShell Essentials - Sample ChapterPackt PublishingNo ratings yet

- UNIT-1 Data Warehousing Part-IIIDocument68 pagesUNIT-1 Data Warehousing Part-IIIDeepak Varma22No ratings yet

- Evolution of AppleDocument24 pagesEvolution of Appleaddy1920No ratings yet

- Okuma - Manuals - 420 - Parts Book - MechanicDocument133 pagesOkuma - Manuals - 420 - Parts Book - MechanicFerenc SulicsNo ratings yet

- LED Audio VU MeterDocument5 pagesLED Audio VU MetergeislermcNo ratings yet

- Data Sheet: 品 名:Power Supply SupervisorDocument9 pagesData Sheet: 品 名:Power Supply SupervisoranjgarNo ratings yet

- Import Eclipse Model To PetrelDocument4 pagesImport Eclipse Model To PetrelLuis Alberto Colan GarciaNo ratings yet

- PATRIOT350 - PT-BRDocument646 pagesPATRIOT350 - PT-BRVander Daniel100% (1)

- Calibration: Dlc3 TsDocument2 pagesCalibration: Dlc3 TsDannyDDannyDNo ratings yet

- Valve Timing Diagram - 3 PDFDocument3 pagesValve Timing Diagram - 3 PDFDevendraNo ratings yet

- MAC ListingsDocument2 pagesMAC ListingsLuis Caroca GuzmanNo ratings yet

- Repair Manual Hydrostatic Pump Motor PDFDocument112 pagesRepair Manual Hydrostatic Pump Motor PDFВячеслав Шапочка100% (3)

- Project Synopsis: Title of The Project: Problem DefintionDocument2 pagesProject Synopsis: Title of The Project: Problem DefintionSiddhant Singh RanaNo ratings yet

- Address: Mohallah Kot Kalan, Pind Dadan Khan, District Jhelum Mobile: +92-336-5800857Document1 pageAddress: Mohallah Kot Kalan, Pind Dadan Khan, District Jhelum Mobile: +92-336-5800857Umair Ul HassanNo ratings yet