Professional Documents

Culture Documents

Link Street 88E6092/88E6095/ 88E6095F Datasheet: 8 Fe + 3 Ge Stackable Ethernet Switch With Qos and 802.1Q

Link Street 88E6092/88E6095/ 88E6095F Datasheet: 8 Fe + 3 Ge Stackable Ethernet Switch With Qos and 802.1Q

Uploaded by

Mohsen haghighatCopyright:

Available Formats

You might also like

- PortlogdumpDocument128 pagesPortlogdumpdannyboy28No ratings yet

- HX8399-A SHARP AN Prelminary v01.02 150108Document22 pagesHX8399-A SHARP AN Prelminary v01.02 150108liu yaoNo ratings yet

- DBCNRX - Receiver Multicoupler - PDU PDFDocument9 pagesDBCNRX - Receiver Multicoupler - PDU PDFTony WilsonNo ratings yet

- FINAL CHEAT SHEET Industrial Network Security Monitoring Incident ResponseDocument2 pagesFINAL CHEAT SHEET Industrial Network Security Monitoring Incident ResponseAni MNo ratings yet

- Lenovo Legion Y920-17IKB LCFC-DS321 NM-B311 R 0.2 SchematicDocument61 pagesLenovo Legion Y920-17IKB LCFC-DS321 NM-B311 R 0.2 SchematicYetawa GuaviareNo ratings yet

- Qualcomm Low Power Wi Fi Qca4531Document3 pagesQualcomm Low Power Wi Fi Qca4531PintuabcNo ratings yet

- 88E6393X Development Board User ManualDocument8 pages88E6393X Development Board User Manualwxzcldw163.comNo ratings yet

- FibeAir IP-20G GX User Guide G9.2 Rev K PDFDocument926 pagesFibeAir IP-20G GX User Guide G9.2 Rev K PDFanon_845131129100% (1)

- ProfSound1219 PDFDocument72 pagesProfSound1219 PDFTomás PGNo ratings yet

- Marvell Phys Transceivers Alaska 88e151x Datasheet 2018 02 PDFDocument154 pagesMarvell Phys Transceivers Alaska 88e151x Datasheet 2018 02 PDFanhxcoNo ratings yet

- Marvell Phys Transceivers Alaska 88e1111 Technical Product Brief 2013 10Document56 pagesMarvell Phys Transceivers Alaska 88e1111 Technical Product Brief 2013 10Brijesh ShahNo ratings yet

- Dell/Compal Confidential: Schematic DocumentDocument7 pagesDell/Compal Confidential: Schematic Documentsantiago rodriguezNo ratings yet

- UbifsDocument47 pagesUbifsSanel KoncarNo ratings yet

- Intel (R) ME SW Installation GuideDocument31 pagesIntel (R) ME SW Installation Guidearvinarvind60No ratings yet

- Vsat ViasatDocument2 pagesVsat Viasatvsharma26No ratings yet

- TITAN FILEMS 2 8 0-SupportedFormatsDocument14 pagesTITAN FILEMS 2 8 0-SupportedFormatsRobertNo ratings yet

- Hytera SmartDispatch-Net Installation Guide V4.0Document79 pagesHytera SmartDispatch-Net Installation Guide V4.0tanajm60No ratings yet

- UFS Card White Paper 180612 PDFDocument16 pagesUFS Card White Paper 180612 PDFteja C SNo ratings yet

- IPQ4019Document80 pagesIPQ4019oncomNo ratings yet

- Microcontrollres NotesDocument66 pagesMicrocontrollres Notesthiruct77No ratings yet

- HUB Structure PDFDocument40 pagesHUB Structure PDFismailttlNo ratings yet

- 88E1111 Datasheet: Integrated 10/100/1000 Ultra Gigabit Ethernet TransceiverDocument252 pages88E1111 Datasheet: Integrated 10/100/1000 Ultra Gigabit Ethernet TransceiverNicholas MoodyNo ratings yet

- Intel (R) MEBX User Guide PDFDocument57 pagesIntel (R) MEBX User Guide PDFBlubNo ratings yet

- RK1808 Datasheet V1.1Document45 pagesRK1808 Datasheet V1.1shakirNo ratings yet

- SMSC 5.0 EMI - UCP InterfaceDocument105 pagesSMSC 5.0 EMI - UCP InterfacelllollooNo ratings yet

- Schmatics Dell 7548 7547 Quanta AM6 MB - DA0AM6MB8E0 REV E PDFDocument58 pagesSchmatics Dell 7548 7547 Quanta AM6 MB - DA0AM6MB8E0 REV E PDFacsacrNo ratings yet

- HP Z440, Z640, and Z840 Workstation Series: Maintenance and Service GuideDocument132 pagesHP Z440, Z640, and Z840 Workstation Series: Maintenance and Service GuideMiguel PagkalinawanNo ratings yet

- CPU Monitoring With DTS/PECI - Intel Corporation 2010Document23 pagesCPU Monitoring With DTS/PECI - Intel Corporation 2010Somethingreally LongforapptestingNo ratings yet

- 1640 FoxDocument4 pages1640 FoxÁngeles María Días SalazarNo ratings yet

- Software Upgrade Procedure Smartpack2 Controller Udoc 370036.063!1!2 1Document44 pagesSoftware Upgrade Procedure Smartpack2 Controller Udoc 370036.063!1!2 1pap_ingosNo ratings yet

- Block-1 CONSTITUTIONAL FRAMEWORKDocument58 pagesBlock-1 CONSTITUTIONAL FRAMEWORKSachin SonawaneNo ratings yet

- Ic F3022SDocument36 pagesIc F3022SEfren.galNo ratings yet

- Huawei Quidway Ar 2921 GuideDocument59 pagesHuawei Quidway Ar 2921 Guideanoop.ashu9376No ratings yet

- 90DIB-R5 Advanced Service and Maintenace Manual ENG V2.1Document278 pages90DIB-R5 Advanced Service and Maintenace Manual ENG V2.1Hytera MNC580No ratings yet

- Technical Note: DDR4 Point-to-Point Design GuideDocument31 pagesTechnical Note: DDR4 Point-to-Point Design GuideAnh Viet NguyenNo ratings yet

- TJ1600 Product Family HD GuideDocument192 pagesTJ1600 Product Family HD Guideanon_238578985No ratings yet

- Os 1Document46 pagesOs 1G.m. RajaNo ratings yet

- PCMCIA Wireless LAN Card: User's ManualDocument48 pagesPCMCIA Wireless LAN Card: User's Manualrecompacted100% (1)

- Foundry Diagnostic GuideDocument80 pagesFoundry Diagnostic GuidelightpaceNo ratings yet

- TOSCA Simple Profile YAML v1.3 OsDocument376 pagesTOSCA Simple Profile YAML v1.3 OsElena SpataforaNo ratings yet

- V2.2-En SDI1606 8 Segment & 7 Grid LED Driver With Boost - Jan15 - 18 (XHF)Document16 pagesV2.2-En SDI1606 8 Segment & 7 Grid LED Driver With Boost - Jan15 - 18 (XHF)AnkitShingalaNo ratings yet

- Radc TR 85 91 - May1985Document441 pagesRadc TR 85 91 - May1985sezgin bayramNo ratings yet

- Emus Mnc310c DatasheetDocument6 pagesEmus Mnc310c DatasheetpeterNo ratings yet

- Westfield Stratford: Sustainability Statement (2007)Document16 pagesWestfield Stratford: Sustainability Statement (2007)Ravi WoodsNo ratings yet

- KnoxDocument31 pagesKnoxTairo BonillaNo ratings yet

- 88E1111 SFP RefDsgn Schematics Rev 1 0newDocument3 pages88E1111 SFP RefDsgn Schematics Rev 1 0newKukla LossNo ratings yet

- RUCKUS 08070 Command ReferenceDocument2,730 pagesRUCKUS 08070 Command ReferenceSathish KannahNo ratings yet

- Flexi Remote Radio Head 2TX 900 (FHDB) PDFDocument4 pagesFlexi Remote Radio Head 2TX 900 (FHDB) PDFAryaNo ratings yet

- AN 835 - Intel PAM4 Signaling BasicsDocument52 pagesAN 835 - Intel PAM4 Signaling BasicsDestinationUnknown88No ratings yet

- U Interface For AM3440 A/B/C User'S ManualDocument17 pagesU Interface For AM3440 A/B/C User'S ManualTariq SaeedNo ratings yet

- Compal La-5892p r1.0 SchematicsDocument50 pagesCompal La-5892p r1.0 Schematicsadysan73No ratings yet

- Gren TechDocument47 pagesGren TechAkbar HussainNo ratings yet

- HP Ahl50 Abl52 La-C701pDocument61 pagesHP Ahl50 Abl52 La-C701pmohammadsajjad sedqiNo ratings yet

- 801G GigaPointDocument3 pages801G GigaPointjaafer adelNo ratings yet

- 29344636A Remocon CodesADocument20 pages29344636A Remocon CodesAjohnwienerNo ratings yet

- Juniper ACX DatasheetDocument7 pagesJuniper ACX Datasheetmach75No ratings yet

- IQBoard Boot MessageDocument19 pagesIQBoard Boot MessageIoannisNo ratings yet

- Technical Note: Software Device Drivers For Micron MT29F NAND Flash MemoryDocument12 pagesTechnical Note: Software Device Drivers For Micron MT29F NAND Flash MemorygogiNo ratings yet

- Marvell Linkstreet 88E6060Document164 pagesMarvell Linkstreet 88E6060kazokinoNo ratings yet

- AS7316-26XB: DatasheetDocument4 pagesAS7316-26XB: DatasheetMohsen haghighatNo ratings yet

- 512Mb DDR2 SDRAM - H5PS518 (6) 2KFRDocument64 pages512Mb DDR2 SDRAM - H5PS518 (6) 2KFRMohsen haghighatNo ratings yet

- Cell Site Gateway Bare-Metal Hardware: DatasheetDocument3 pagesCell Site Gateway Bare-Metal Hardware: DatasheetMohsen haghighatNo ratings yet

- AS7716-24SC Switch: DatasheetDocument3 pagesAS7716-24SC Switch: DatasheetMohsen haghighatNo ratings yet

- Perform: 14 Slot ATCA DC Shelf User ManualDocument47 pagesPerform: 14 Slot ATCA DC Shelf User ManualMohsen haghighatNo ratings yet

- 3.26.2020 I2C Unbounded - Solve Your 2-Wire ChallengesDocument14 pages3.26.2020 I2C Unbounded - Solve Your 2-Wire ChallengesMohsen haghighatNo ratings yet

- Automotive DDR4 SDRAM: MT40A512M8 MT40A256M16 FeaturesDocument384 pagesAutomotive DDR4 SDRAM: MT40A512M8 MT40A256M16 FeaturesMohsen haghighatNo ratings yet

- Pulse-Width Modulation (PWM) Technology: Web: EmailDocument9 pagesPulse-Width Modulation (PWM) Technology: Web: EmailMohsen haghighatNo ratings yet

- PMD Layer Pcs Layer IEEE 802.3ba STANDARD: 100/40 Gbps Ethernet - Are You Ready?Document1 pagePMD Layer Pcs Layer IEEE 802.3ba STANDARD: 100/40 Gbps Ethernet - Are You Ready?Mohsen haghighatNo ratings yet

- 100GE and 40GE PCS Overview: IEEE 802.3az November 2008 DallasDocument27 pages100GE and 40GE PCS Overview: IEEE 802.3az November 2008 DallasMohsen haghighatNo ratings yet

- Pushpin™ Heat Sink Assembly: Ats-09C-174-C2-R0Document1 pagePushpin™ Heat Sink Assembly: Ats-09C-174-C2-R0Mohsen haghighatNo ratings yet

- 1.35V Automotive DDR3L SDRAM Data Sheet AddendumDocument3 pages1.35V Automotive DDR3L SDRAM Data Sheet AddendumMohsen haghighatNo ratings yet

- NEC - iPASOLINK VR2 DatasheetDocument57 pagesNEC - iPASOLINK VR2 DatasheetCh Augusto100% (1)

- Cambium Networks Data Sheet WiFi-6 XV2-2T1 APDocument8 pagesCambium Networks Data Sheet WiFi-6 XV2-2T1 APrudnei marinho santosNo ratings yet

- Wireless Lans and Pans: 01204325: Data Communication and Computer NetworksDocument28 pagesWireless Lans and Pans: 01204325: Data Communication and Computer NetworksĐức ThắngNo ratings yet

- Chap Alcatel LucentdevicesDocument28 pagesChap Alcatel LucentdevicesVitaliy PoberezniyNo ratings yet

- AC1200 Wi-Fi Router: Product HighlightsDocument3 pagesAC1200 Wi-Fi Router: Product HighlightsMAX REYESNo ratings yet

- 100-105 Exam Dumps With PDF and VCE Download (1-50)Document24 pages100-105 Exam Dumps With PDF and VCE Download (1-50)Vadinho85% (13)

- NetPoint Pro 6x2.4 G2 Data SheetDocument2 pagesNetPoint Pro 6x2.4 G2 Data SheetMartine OneNo ratings yet

- Cisco 2960g 8tcDocument5 pagesCisco 2960g 8tcZts MksNo ratings yet

- Ether ChannelDocument2 pagesEther ChannelAlex AlvarezNo ratings yet

- Certicicaciones 0605 PDFDocument597 pagesCerticicaciones 0605 PDFMontecinos SusanNo ratings yet

- 8 - PPT-5 Collision and Broadcast DomainsDocument11 pages8 - PPT-5 Collision and Broadcast Domainshar maNo ratings yet

- Switching PDFDocument104 pagesSwitching PDFRajkeen ChamanshaikhNo ratings yet

- Data Center SolutionDocument37 pagesData Center SolutionHumbulani D SioboNo ratings yet

- Agregacion de EnlacesDocument3 pagesAgregacion de EnlacesGabriel CastroNo ratings yet

- Carlos Cordeiro: CTO, Wireless Communications Intel Corporation July 2020Document23 pagesCarlos Cordeiro: CTO, Wireless Communications Intel Corporation July 2020Jose Arturo Bustamante LazcanoNo ratings yet

- Eltex ALL 2019 07 enDocument84 pagesEltex ALL 2019 07 enTrần Đình DũngNo ratings yet

- LAN TechnologyDocument175 pagesLAN TechnologySantosh SinghNo ratings yet

- IEEE 802 StandardsDocument14 pagesIEEE 802 StandardsHoney RamosNo ratings yet

- Chapter 8 Exam CCNP Switch 2016 PDFDocument8 pagesChapter 8 Exam CCNP Switch 2016 PDFYovani AlvaradoNo ratings yet

- H660GWDocument2 pagesH660GWQiandra kamilahNo ratings yet

- HOW TO Automate WiDocument11 pagesHOW TO Automate WiAl 1No ratings yet

- Networking mx9116n - User's Guide - en Us PDFDocument732 pagesNetworking mx9116n - User's Guide - en Us PDFUmAiR ANo ratings yet

- Ethernet Cheat PaperDocument7 pagesEthernet Cheat PaperBSAScitiNo ratings yet

- WWW Netwifistore Com Ruckus EOL ASPDocument6 pagesWWW Netwifistore Com Ruckus EOL ASPSAMUEL KAMAUNo ratings yet

- Resmlac 8emg CapsDocument3 pagesResmlac 8emg CapsvamshimusicalNo ratings yet

- Ch4.RS InstructorPPT Chapter3 FinalDocument13 pagesCh4.RS InstructorPPT Chapter3 FinalManisara PuenteNo ratings yet

- Brain Dump JNO-360: SectionsDocument260 pagesBrain Dump JNO-360: SectionsCao Vu ThangNo ratings yet

- Spark DatasheetDocument2 pagesSpark DatasheetAno InkNo ratings yet

- CMU-CS S252 - Introduction To Network - Telecommunication Technology - 2020S - Lecture Slides - 5Document24 pagesCMU-CS S252 - Introduction To Network - Telecommunication Technology - 2020S - Lecture Slides - 5Quang Trần MinhNo ratings yet

- Switched Ethernet vs. Classic EthernetDocument3 pagesSwitched Ethernet vs. Classic EthernetDon WaltonNo ratings yet

Link Street 88E6092/88E6095/ 88E6095F Datasheet: 8 Fe + 3 Ge Stackable Ethernet Switch With Qos and 802.1Q

Link Street 88E6092/88E6095/ 88E6095F Datasheet: 8 Fe + 3 Ge Stackable Ethernet Switch With Qos and 802.1Q

Uploaded by

Mohsen haghighatOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Link Street 88E6092/88E6095/ 88E6095F Datasheet: 8 Fe + 3 Ge Stackable Ethernet Switch With Qos and 802.1Q

Link Street 88E6092/88E6095/ 88E6095F Datasheet: 8 Fe + 3 Ge Stackable Ethernet Switch With Qos and 802.1Q

Uploaded by

Mohsen haghighatCopyright:

Available Formats

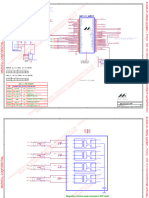

Link Street® 88E6092/88E6095/

88E6095F Datasheet

8 FE + 3 GE Stackable Ethernet Switch with QoS

and 802.1Q

Doc. No. MV-S102629-00 Rev. C

June 9, 2006

Link Street® 88E6092/88E6095/88E6095F

8 FE + 3 GE Stackable Ethernet Switch with QoS and 802.1Q

Document Status

Advance This document contains design specifications for initial product development. Specifications may change

Information without notice. Contact Marvell Field Application Engineers for more information.

Preliminary This document contains preliminary data, and a revision of this document will be published at a later date.

Information Specifications may change without notice. Contact Marvell Field Application Engineers for more information.

Final This document contains specifications on a product that is in final release. Specifications may change without

Information notice. Contact Marvell Field Application Engineers for more information.

Revision Code: Rev. C

Advance Technical Publication: 1.40

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express

written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no warranty of any kind, expressed or implied, with regard

to any information contained in this document, including, but not limited to, the implied warranties of merchantability or fitness for any particular purpose. Further, Marvell does not warrant the

accuracy or completeness of the information, text, graphics, or other items contained within this document.

Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use Marvell products in these

types of equipment or applications.

With respect to the products described herein, the user or recipient, in the absence of appropriate U.S. government authorization, agrees:

1) Not to re-export or release any such information consisting of technology, software or source code controlled for national security reasons by the U.S. Export Control Regulations ("EAR"),

to a national of EAR Country Groups D:1 or E:2;

2) Not to export the direct product of such technology or such software, to EAR Country Groups D:1 or E:2, if such technology or software and direct products thereof are controlled for national

security reasons by the EAR; and,

3) In the case of technology controlled for national security reasons under the EAR where the direct product of the technology is a complete plant or component of a plant, not to export to EAR

Country Groups D:1 or E:2 the direct product of the plant or major component thereof, if such direct product is controlled for national security reasons by the EAR, or is subject to controls under

the U.S. Munitions List ("USML").

At all times hereunder, the recipient of any such information agrees that they shall be deemed to have manually signed this document in connection with their receipt of any such information.

Copyright © 2006. Marvell International Ltd. All rights reserved. Marvell, the Marvell logo, Moving Forward Faster, Alaska, Fastwriter, Datacom Systems on Silicon, Libertas, Link Street, NetGX,

PHYAdvantage, Prestera, Raising The Technology Bar, The Technology Within, Virtual Cable Tester, and Yukon are registered trademarks of Marvell. Ants, AnyVoltage, Discovery, DSP

Switcher, Feroceon, GalNet, GalTis, Horizon, Marvell Makes It All Possible, RADLAN, UniMAC, and VCT are trademarks of Marvell. All other trademarks are the property of their respective

owners.

Doc. No. MV-S102629-00 Rev. C CONFIDENTIAL Copyright © 2006 Marvell

Page 2 Document Classification: Proprietary Information June 9, 2006, Advance

Link Street® 88E6092/88E6095/88E6095F

8 FE + 3 GE Stackable Ethernet Switch with QoS and 802.1Q

O VERVIEW

The Marvell® 88E6092, 88E6095, and 88E6095F Tree Protocol, 802.1w Rapid Spanning Tree (88E6095

devices are each single-chip 8-port 10/100 plus 3 port and 88E6095F only), 802.1s Multiple VLAN Spanning

Gigabit Ethernet switches with support for Quality of Tree (88E6095 and 88E6095F only), programmable

Service (QoS), 802.1Q, and RMON counters. They per-port VLAN configurations, 802.1Q and Port States,

contain eight 10BASE-T/100BASE-TX transceivers support fully managed switches and truly isolated

(PHYs), and three SERDES interfaces that can be WAN vs. LAN firewall applications. The devices sup-

used to connect to external Marvell 10/100/1000 triple port 4,096 802.1Q VLAN IDs which can be enabled on

speed Ethernet transceivers (PHYs). a per port basis. Three levels of 802.1Q security is

supported with error frame trapping and logging.

The 88E6092 is designed for unmanaged or smart

managed applications, while the 88E6095 is for fully The devices provide an 8K MAC address lookup table

managed applications with enhanced features for which allows for up to 8K active nodes to be con-

stacking. The 88E6095F device is also for fully man- nected with the switch. Back-pressure and Pause

aged applications and stacking, and includes fiber frame-based flow control schemes are included to

enable and controls on all ports.The devices integrate support zero packet loss under temporary traffic con-

QoS with four levels of priority per port. The QoS gestion. The MAC units in the devices comply fully

architecture switches packets into one of four traffic with the applicable sections of IEEE 802.3.

class queues based upon Port, IEEE 802.1p, IPv4

The PHY and SERDES units in the devices are

Type of Service (TOS) or Differentiated Services (Diff-

designed with the Marvell® cutting-edge mixed-signal

Serv), IPv6 Traffic Class, 802.1Q VLAN ID, DA MAC

processing technology for digital implementation of

address or SA MAC address. Back-pressure and

adaptive equalization and clock data recovery. Special

pause frame-based flow control schemes are included

power management techniques are used to facilitate

to support zero packet loss under temporary traffic

low power dissipation and high port count integration.

congestion. The lookup engine allows for up to 8K

Both the PHY and MAC units in the devices comply

active nodes to be connected with the switch.

fully with the applicable sections of IEEE 802.3, IEEE

The switches contain eleven independent 802.3 media 802.3u, and IEEE 802.3x standards.

access controllers (MACs), a high-speed, non-block-

The devices’ many operating modes can be config-

ing four traffic class QoS switch fabric, a high-perfor-

ured using SMI (serial management interface - MDC/

mance address lookup engine, and a 1 Mbit frame

MDIO) and/or a low cost serial EEPROM (93C46, C56

buffer memory. Up to 32 or more 88E6095 devices can

or C66). A standalone QoS mode is also supported.

be cascaded. One or more devices can be used to

create larger switches, e.g 24 FE + 2 GE or 48 FE + 4 A PPLICATIONS

GE. The devices are designed for cost-sensitive low to • 24 FE + 2 GE switch using three 88E6095

high port count switch systems that require Quality of devices (Stackable, Managed) or three 88E6092

Service, Trunking, Stacking(88E6095 and 888E6095F devices (Smart, Unmanaged)

only), and/or Spanning Tree.

• 48 FE + 4 GE switch using six 88E6095 devices

The devices offer enhanced stacking capabilities that with a single 88E6185 (Non blocking, Stackable,

enable multiple devices and/or systems to act as a sin- Managed) or six 88E6092 devices and one

gle unit. These features include the ability to Link 88E6182 device (Smart, Unmanaged)

Aggregate ports between boxes in a stack, monitor • 24 FE + 4 GE switch using three 88E6095

any port from any other port in the stack, and create devices with a single 88E6185 (10 port GE

port-based VLANs using any port(s) within the stack. switch)—Non blocking, stackable, Managed or

The ninth and tenth ports’ optional (G)MII (or MII) inter- three 88E6092 and 88E6182 devices (Smart,

face supports a direct connection to Management or Unmanaged)

Router CPUs with integrated MACs. For the 88E6092/ • 8 FE + 2 1000BASE-X using a single 88E6095

88E6095 devices, Port 9 is only MII-PHY or MII-MAC device (Managed) or 88E6092 (Smart, Unman-

mode capable, while Port 10 can be configured in aged)

either GMII mode, MII-PHY or MII-MAC mode. Port 9 • SOHO/SMB router with eight FE and two GE

and Port 10 of the 88E6095F device are both capable ports

of GMII/MII MAC or PHY mode. These interfaces, • Fiber to the Curb cascade applications

along with BPDU handling for IEEE 802.1D Spanning

Copyright © 2006 Marvell CONFIDENTIAL Doc. No. MV-S102629-00 Rev. C

June 9, 2006, Advance Document Classification: Proprietary Information Page 3

Link Street® 88E6092/88E6095/88E6095F

8 FE + 3 GE Stackable Ethernet Switch with QoS and 802.1Q

F EATURES • Ports 8, 9 & 10 can optionally be configured as

fiber ports (1000BASE-X) with direct connection

• Single chip integration of an 11 port 8-FE + 3-GE

to lasers

QoS switch and memory in a 20 x 20 mm 176-pin

TQFP package (88E6092/88E6095 device), or 24 • Ports 9 and 10 can support GMII Mode (full-

x 24 mm 216 LQFP (88E6095F device) duplex), MII-MAC Mode (Forward) or MII-PHY

Mode (Reverse—full-duplex) interface options for

• Enables stackable systems through standard

management and firewall applications (Port 9 is

Ethernet interfaces (88E6095 and 88E6095F

MII only in the 88E6092/88E6095 devices)

devices only)

• Quality of Service support with four traffic classes

• Each GE port works at 10 Mbps or 100 Mbps, full

or half-duplex mode, or 1000 Mbps full-duplex

• QoS determined by Port, IEEE 802.1p tagged mode

frames, IPv4’s Type of Service (TOS) & Differenti-

• Shared 1 Mbit on-chip memory-based switch fab-

ated Services (DS), IPv6’s Traffic Class 802.1Q

ric with true non-blocking switching performance

VID, Destination MAC address, or Source MAC

address • High performance lookup engine with support for

up to 8K MAC address entries with automatic

• 802.1X MAC based authentication

learning and aging

• Port Trunking across chips

• Flexible LED support for Link, Speed, Duplex

• Port Monitoring/Mirroring across chips Mode, Collision, and Tx/Rx Activities

• 802.1Q VLAN support for the full 4,096 VLAN IDs • Supports a low-cost 25 MHz XTAL clock source

• Egress tagging/untagging selectable per port or • Low power dissipation PAVE = 1W

by 802.1Q VLAN ID

• Supports the Marvell® Distributed Switching

• Port based VLANs supported in any combination Architecture (DSA)

across multiple chips

• for STP, up to 32 cascaded devices, and CPU-

• Port States & BPDU handling for Spanning Tree directed packet processing

• 28 32-bit and 2 64-bit RMON Counters per port • 176-TQFP package (88E6092/88E6095 device)

• Integrated with eight independent Auto-Crossover and 216-LQFP package (88E6095F device)

Fast Ethernet transceivers fully compliant with the • 88E6095 and 88E6095F available in Commercial

applicable sections of IEEE802.3 and and Industrial grade

IEEE802.3u

• 100% pin compatible to the 88E6095 or

88E6095F device

• Integrated with three independent triple speed

SERDES transceivers to interface with Marvell®

Alaska® gigabit copper PHYs

Doc. No. MV-S102629-00 Rev. C CONFIDENTIAL Copyright © 2006 Marvell

Page 4 Document Classification: Proprietary Information June 9, 2006, Advance

Table 1: 88E6092/88E6095/88E6095F Device Differences

88E60 92 8 8E609 5 88E60 95F

Smart/ M an ag ed/ Mana ged /

Des cription Un mana ge d Stack able Sta cka ble

FE PHY and GE SERDES 8+3 8+3 8+3

Fe atur es

FE Fiber Support 0 0 8

# GMII/MII (Shared w/SERDES) 1/2 1/2 2/2

Packet Buffer Memory 1 Mbit 1 Mbit 1 Mbit

# MAC Addresses 8K 8K 8K

Queues per Port 4 4 4

Q oS

802.1p, Port, TOS/DS, IPv6, TC, MAC Yes Yes Yes

Priority Override (DA, SA, VID), Remap No Yes Yes

Port -based and 802.1Q VLANs Yes Yes Yes

VLAN

Maximum number of Shared 802.1Q VLANs 4096 4096 4096

Maximum number of Independent 802.1Q VLANs 256 256 256

Double Tagging (Q in Q) No Yes Yes

Stacking Support No Yes Yes

Cro ss-ch ip

Cross -chip Trunking (#Trunks/#Ports) Yes (8/8) Yes (16/8) Yes (16/8)

Cross-chip Port Based VLANs Yes Yes Yes

Cross-chip Flow Control Yes Yes Yes

Distributed Switching Architecture (DSA) Tag Support Yes Yes Yes

802.1D Spanning Tree Yes Yes Yes

Ma nag e-

802.1w/s (Rapid/Multiple) STP No Yes Yes

ment

Port Mirroring Yes Yes Yes

IGMP/MLD Snooping Yes Yes Yes

Ingress Storm Limiting Yes Yes Yes

Egress Rate Shaping No Yes Yes

Oth er

802.1X Port & MAC Authentication Yes Yes Yes

Industrial Grade No Yes Yes

Package 176-pin LQFP 176-pin LQFP 216-pin LQFP

Copyright © 2006 Marvell CONFIDENTIAL Doc. No. MV-S102629-00 Rev. C

June 9, 2006, Advance Document Classification: Proprietary Information Page 5

Link Street® 88E6092/88E6095/88E6095F

8 FE + 3 GE Stackable Ethernet Switch with QoS and 802.1Q

10BASE-T

P0_TX Port States

100BASE-TX

MAC & Tag

Transceiver

P0_RX w/Auto Crossover

Processing RESETn

10BASE-T

P1_TX Port States

100BASE-TX

MAC & Tag 1 Mbit Embedded Switch Fabric Memory

Transceiver

P1_RX w/Auto Crossover

Processing

XTAL_IN

10BASE-T

P2_TX Port States XTAL_OUT

100BASE-TX

MAC & Tag

Transceiver

P2_RX w/Auto Crossover

Processing

10BASE-T

P3_TX Port States

100BASE-TX EE_CS

MAC & Tag

Transceiver Queue Controller with Register EE_CLK

P3_RX w/Auto Crossover

Processing

Four Traffic Classes Loader EE_DIN

EE_DOUT

10BASE-T

P4_TX Port States

100BASE-TX

MAC & Tag

Transceiver

P4_RX w/Auto Crossover

Processing MDC_CPU

CPU/Reg

MDIO_CPU

Time Slot Port Controller

Look-up Engine Interface

INTn

10BASE-T

P5_TX Port States

100BASE-TX

MAC & Tag

Transceiver

P5_RX w/Auto Crossover

Processing

10BASE-T

P6_TX Port States

100BASE-TX

MAC & Tag Switch

Transceiver 8K Entry MAC Address SW_MODE[1:0]

P6_RX w/Auto Crossover

Processing

Table

Registers

10BASE-T

P7_TX Port States

100BASE-TX

MAC & Tag

Transceiver

P7_RX w/Auto Crossover

Processing

4,096 Entry 802.1Q VLAN PHY

P8_TX Triple Speed & Port States

Fiber Enable Table Polling Unit

1000BASE-X GMAC & Tag

and Controls

P8_RX SERDES Processing

External

P9_TX Triple Speed & Port States 28 32-bit and 2 64-bit

Fiber Enable PHY MDC_PHY

1000BASE-X GMAC & Tag RMON Counters per Port

and Controls Reg MDIO_PHY

P9_RX SERDES Processing

Interface

MAC or PHY Mode

MII Interface

P10_TX Triple Speed & Port States

Fiber Enable FE Transceiver LEDs 3 x 8 LEDs

1000BASE-X GMAC & Tag

and Controls

P10_RX SERDES Processing

MAC or PHY Mode

GMII/MII Interface

88E6092/88E6095 176 TQFP Top Level Block Diagram

Doc. No. MV-S102629-00 Rev. C CONFIDENTIAL Copyright © 2006 Marvell

Page 6 Document Classification: Proprietary Information June 9, 2006, Advance

10BASE-T

P0_TX Port States

Fiber Enable 100BASE-TX/FX

MAC & Tag

and Controls Transceiver

P0_RX w/Auto Crossover

Processing RESETn

10BASE-T

P1_TX Port States

Fiber Enable 100BASE-TX/FX

MAC & Tag 1 Mbit Embedded Switch Fabric Memory

and Controls Transceiver

P1_RX w/Auto Crossover

Processing

XTAL_IN

10BASE-T

P2_TX Port States XTAL_OUT

Fiber Enable 100BASE-TX/FX

MAC & Tag

and Controls Transceiver

P2_RX w/Auto Crossover

Processing

10BASE-T

P3_TX Port States

Fiber Enable 100BASE-TX/FX EE_CS

MAC & Tag

and Controls Transceiver Queue Controller with Register EE_CLK

P3_RX w/Auto Crossover

Processing

Four Traffic Classes Loader EE_DIN

EE_DOUT

10BASE-T

P4_TX Port States

Fiber Enable 100BASE-TX/FX

MAC & Tag

and Controls Transceiver

P4_RX w/Auto Crossover

Processing MDC_CPU

CPU/Reg

MDIO_CPU

Time Slot Port Controller

Look-up Engine Interface

INTn

10BASE-T

P5_TX Port States

Fiber Enable 100BASE-TX/FX

MAC & Tag

and Controls Transceiver

P5_RX w/Auto Crossover

Processing

10BASE-T

P6_TX Port States

Fiber Enable 100BASE-TX/FX

MAC & Tag Switch

and Controls Transceiver 8K Entry MAC Address SW_MODE[1:0]

P6_RX w/Auto Crossover

Processing

Table

Registers

10BASE-T

P7_TX Port States

Fiber Enable 100BASE-TX/FX

MAC & Tag

and Controls Transceiver

P7_RX w/Auto Crossover

Processing

4,096 Entry 802.1Q VLAN PHY

P8_TX Triple Speed & Port States

Fiber Enable Table Polling Unit

1000BASE-X GMAC & Tag

and Controls

P8_RX SERDES Processing

External

P9_TX Triple Speed & Port States 28 32-bit and 2 64-bit

Fiber Enable PHY MDC_PHY

1000BASE-X GMAC & Tag RMON Counters per Port

and Controls Reg MDIO_PHY

P9_RX SERDES Processing

Interface

MAC or PHY Mode

GMII/MII Interface

3 x 8 LEDs

P10_TX Triple Speed & Port States

Fiber Enable FE Transceiver LEDs

1000BASE-X GMAC & Tag

and Controls

P10_RX SERDES Processing Serial LEDs

MAC or PHY Mode

GMII/MII Interface

88E6095F 216 LQFP Top Level Block Diagram

Copyright © 2006 Marvell CONFIDENTIAL Doc. No. MV-S102629-00 Rev. C

June 9, 2006, Advance Document Classification: Proprietary Information Page 7

Link Street® 88E6092/88E6095/88E6095F

8 FE + 3 GE Stackable Ethernet Switch with QoS and 802.1Q

Table of Contents

SECTION 1. SIGNAL DESCRIPTION ............................................................................ 18

1.1 Pin Description ......................................................................................................................... 20

SECTION 2. APPLICATION EXAMPLES ....................................................................... 56

2.1 Examples using the 88E6095 Device...................................................................................... 56

2.2 Device Physical Interfaces ...................................................................................................... 60

2.2.1 10/100 PHY Interface................................................................................................................... 60

2.2.2 SERDES or (G)MII Interface ........................................................................................................ 60

2.2.3 Digital Interface Options............................................................................................................... 63

2.2.4 PHY Polling Unit (PPU)................................................................................................................ 68

2.2.5 24 Port Switch Configuration........................................................................................................ 68

SECTION 3. SWITCH CORE FUNCTIONAL DESCRIPTION ............................................. 69

3.1 Switch Data Flow ...................................................................................................................... 69

3.2 Physical Interface ..................................................................................................................... 69

3.3 Media Access Controllers (MAC) ............................................................................................ 70

3.3.1 Backoff ......................................................................................................................................... 70

3.3.2 Half-duplex Flow Control.............................................................................................................. 70

3.3.3 Full-duplex Flow Control .............................................................................................................. 71

3.3.4 Forcing Flow Control in the MAC ................................................................................................. 72

3.3.5 MAC Based RMON/Statistics Counters ....................................................................................... 73

3.3.6 Policy Based RMON/Statistics Counters ..................................................................................... 78

3.4 Basic Switch Operation ........................................................................................................... 79

3.4.1 Lookup Engine ............................................................................................................................. 79

3.4.2 Address Searching or Translation................................................................................................ 79

3.4.3 Automatic Address Learning ........................................................................................................ 80

3.4.4 Automatic Address Aging............................................................................................................. 81

3.4.5 CPU Directed Address Learning .................................................................................................. 81

3.4.6 802.1X Source MAC Address Checking ...................................................................................... 81

3.4.7 Multiple Address Database Support (DBNum)............................................................................. 82

3.4.8 Management/802.1D BPDU Frame Detection ............................................................................. 83

3.4.9 MUX’ing or Ignoring Address Translation .................................................................................... 84

3.4.10 Address Translation Unit Operations ........................................................................................... 85

3.5 Ingress Policy ........................................................................................................................... 91

3.5.1 Port States for 802.1D Spanning Tree ......................................................................................... 91

3.5.2 802.1X MAC Address Authentication........................................................................................... 92

3.5.3 Forward Unknown/Secure Port .................................................................................................... 92

3.5.4 Forward Unknown for Multicasts.................................................................................................. 92

3.5.5 Quality of Service (QoS) Classification ........................................................................................ 93

Doc. No. MV-S102629-00 Rev. C CONFIDENTIAL Copyright © 2006 Marvell

Page 8 Document Classification: Proprietary Information June 9, 2006, Advance

3.5.6 Port Based VLANs ........................................................................................................................94

3.5.7 802.1Q VLANs ..............................................................................................................................97

3.5.8 Switching Frames Back to their Source Port ................................................................................98

3.5.9 Tunneling Frames Through VLANs ..............................................................................................98

3.5.10 802.1s Per VLAN Spanning Tree (88E6095 and 88E6095F Only)...............................................98

3.5.11 VLAN Translation Unit Operations................................................................................................99

3.5.12 IEEE Tagged Frame Handling ....................................................................................................105

3.5.13 Priority from IPv4 & IPv6 Frames................................................................................................108

3.5.14 IGMP/MLD Snooping ..................................................................................................................109

3.5.15 Ingress Rate Limiting ..................................................................................................................111

3.5.16 Ingress on Distributed Switching Architecture (DSA) Tag Ports .................................................112

3.5.17 Switch Ingress Header for Routers .............................................................................................115

3.5.18 Ingress Double VLAN Tagging (88E6095 and 88E6095F Only).................................................117

3.6 Queue Controller.....................................................................................................................119

3.6.1 Frame Latencies .........................................................................................................................119

3.6.2 No Head-of-Line Blocking ...........................................................................................................119

3.6.3 QoS with and without Flow Control.............................................................................................119

3.6.4 Guaranteed Frame Delivery without Flow Control ......................................................................120

3.6.5 Fixed or Weighted Priority...........................................................................................................120

3.6.6 The Queues ................................................................................................................................120

3.6.7 Queue Manager ..........................................................................................................................121

3.6.8 Output Queues............................................................................................................................121

3.6.9 Multicast Handler ........................................................................................................................122

3.7 Egress Policy ..........................................................................................................................123

3.7.1 Tagging and Untagging Frames .................................................................................................123

3.7.2 Egress Double VLAN Tagging (88E6095 and 88E6095F devices Only) ....................................125

3.7.3 Port States ..................................................................................................................................126

3.7.4 Egress Rate Shaping (88E6095 and 88E6095F devices only)...................................................126

3.7.5 Egress on DSA Tag Ports...........................................................................................................127

3.7.6 Switch Egress Header for Routers..............................................................................................131

3.8 Port Monitoring Support ........................................................................................................132

3.9 Port Trunking Support............................................................................................................133

3.10 Spanning Tree Support ..........................................................................................................134

3.11 Embedded Memory .................................................................................................................135

3.12 Interrupt Controller .................................................................................................................135

SECTION 4. PHYSICAL INTERFACE (PHY) FUNCTIONAL DESCRIPTION (P0 TO P7) ... 136

4.1 Transmit PCS and PMA ..........................................................................................................138

4.1.1 100BASE-TX Transmitter ...........................................................................................................138

4.1.2 4B/5B Encoding ..........................................................................................................................138

4.1.3 Scrambler....................................................................................................................................138

4.1.4 NRZ to NRZI Conversion ............................................................................................................138

4.1.5 Pre-Driver and Transmit Clock....................................................................................................138

4.1.6 Multimode Transmit DAC............................................................................................................138

Copyright © 2006 Marvell CONFIDENTIAL Doc. No. MV-S102629-00 Rev. C

June 9, 2006, Advance Document Classification: Proprietary Information Page 9

Link Street® 88E6092/88E6095/88E6095F

8 FE + 3 GE Stackable Ethernet Switch with QoS and 802.1Q

4.2 Receive PCS and PMA ........................................................................................................... 139

4.2.1 10-BASE-T/100BASE-TX Receiver ........................................................................................... 139

4.2.2 AGC and Baseline Wander ........................................................................................................ 139

4.2.3 ADC and Digital Adaptive Equalizer........................................................................................... 139

4.2.4 Digital Phased Locked Loop (DPLL) .......................................................................................... 139

4.2.5 NRZI to NRZ Conversion ........................................................................................................... 139

4.2.6 Descrambler............................................................................................................................... 139

4.2.7 Serial to Parallel Conversion and 5B/4B Code-Group Alignment .............................................. 140

4.2.8 5B/4B Decoder........................................................................................................................... 140

4.2.9 Setting Cable Characteristics..................................................................................................... 142

4.2.10 Scrambler/Descrambler ............................................................................................................. 142

4.2.11 Link Monitor................................................................................................................................ 143

4.2.12 Auto-Negotiation ........................................................................................................................ 144

4.2.13 Register Update ......................................................................................................................... 144

4.2.14 Next Page Support..................................................................................................................... 144

4.2.15 Status Registers......................................................................................................................... 144

4.3 Power Management................................................................................................................ 145

4.3.1 Low Power Modes...................................................................................................................... 145

4.3.2 MAC Interface and PHY Configuration for Low Power Modes................................................... 145

4.3.3 IEEE Power Down Mode............................................................................................................ 145

4.4 Far End Fault Indication (FEFI) ............................................................................................. 146

4.5 Virtual Cable Tester® Feature ............................................................................................... 147

4.6 Data Terminal Equipment (DTE) Detect................................................................................ 148

4.7 Auto MDI/MDIX Crossover ..................................................................................................... 150

4.8 Copper Line Loopback........................................................................................................... 151

4.9 LED Interface .......................................................................................................................... 152

4.9.1 Parallel LED Interface ................................................................................................................ 152

4.9.2 Using Two Color LEDs............................................................................................................... 154

4.9.3 Serial LED Interface (88E6095F Device Only)........................................................................... 157

4.9.4 Single and Dual LED Modes ...................................................................................................... 157

SECTION 5. SERIAL MANAGEMENT INTERFACE (SMI) ............................................. 162

5.1 MDC/MDIO Read and Write Operations................................................................................ 162

SECTION 6. SWITCH REGISTER DESCRIPTION ......................................................... 164

6.1 Register Types........................................................................................................................ 167

6.2 Multi-chip Addressing Mode ................................................................................................. 168

6.3 Single-chip Addressing Mode ............................................................................................... 171

6.4 Switch Port Registers ............................................................................................................ 173

6.5 Switch Global Registers ........................................................................................................ 196

Doc. No. MV-S102629-00 Rev. C CONFIDENTIAL Copyright © 2006 Marvell

Page 10 Document Classification: Proprietary Information June 9, 2006, Advance

6.6 Switch Global 2 Registers ......................................................................................................224

6.7 EEPROM Programming Format .............................................................................................231

SECTION 7. PHY REGISTER DESCRIPTION ............................................................. 233

SECTION 8. ELECTRICAL SPECIFICATIONS.............................................................. 268

8.1 Absolute Maximum Ratings ...................................................................................................268

8.2 Recommended Operating Conditions ..................................................................................269

8.3 Thermal Conditions for 88E6092/88E6095 devices 176-pin TQFP Package......................270

8.4 Thermal Conditions for 88E6095FF device 216-pin LQFP Package...................................271

8.5 DC Electrical Characteristics .................................................................................................272

8.5.1 Current Consumption..................................................................................................................272

8.6 AC Electrical Specifications ..................................................................................................277

8.6.1 Receiver AC Characteristics .......................................................................................................277

8.7 GMII Interface Timing .............................................................................................................279

8.7.2 GMII Receive Timing ..................................................................................................................280

8.8 MII MAC Mode Clock Timing ..................................................................................................281

8.9 SERDES (Serial Interface) Timing ........................................................................................289

SECTION 9. PACKAGE MECHANICAL DIMENSIONS .................................................. 291

SECTION 10. ORDERING INFORMATION .................................................................... 295

10.1 Ordering Part Numbers and Package Markings ..................................................................295

10.1.1 RoHS 5/6 Marking Examples......................................................................................................296

10.1.2 RoHS 6/6 Compliant Marking Examples....................................................................................299

Copyright © 2006 Marvell CONFIDENTIAL Doc. No. MV-S102629-00 Rev. C

June 9, 2006, Advance Document Classification: Proprietary Information Page 11

Link Street® 88E6092/88E6095/88E6095F

8 FE + 3 GE Stackable Ethernet Switch with QoS and 802.1Q

List of Tables

Table 1: 88E6092/88E6095/88E6095F Device Differences ................................................................................. 5

Table 2: Pin Type Definitions.............................................................................................................................. 20

Table 3: Network 10/100 PHY Interface (Ports 0 to 7) ....................................................................................... 21

Table 4: PHY Configuration (Ports 0 to 7) .......................................................................................................... 22

Table 5: Port Status LEDs (Ports 0 to 7) ............................................................................................................ 24

Table 6: SERDES/1000BASE-X Interface (Ports 8 to 10) .................................................................................. 25

Table 7: GMII/MII Receive Interface (Port 9 is MII only - 88E6092/88E6095 devices only) ............................... 27

Table 8: GMII/MII Transmit Interface (Port 9) ..................................................................................................... 29

Table 9: GMII/MII Receive Interface (Port 10) .................................................................................................... 32

Table 10: GMII/MII Transmit Interface (Port 10) ................................................................................................... 34

Table 11: Regulator & Reference ......................................................................................................................... 37

Table 12: System.................................................................................................................................................. 38

Table 13: Register Access Interface..................................................................................................................... 39

Table 14: Serial EEPROM Interface ..................................................................................................................... 41

Table 15: Switch Configuration Interface.............................................................................................................. 44

Table 16: Power & Ground ................................................................................................................................... 45

Table 19: 88E6092/88E6095 Device Interfaces ................................................................................................... 60

Table 20: 88E6095F Device Interfaces ................................................................................................................ 60

Table 21: Format of Pause ................................................................................................................................... 71

Table 22: Ingress Statistics Counters ................................................................................................................... 74

Table 23: Egress Statistics Counters ................................................................................................................... 76

Table 24: ATU Operation Registers ..................................................................................................................... 85

Table 25: ATU Data bits ....................................................................................................................................... 86

Table 26: ATU Get Next Operation Register Usage............................................................................................. 88

Table 27: ATU Load/Purge Operation Register Usage ........................................................................................ 89

Table 28: ATU Get/Clear Violation Data Register Usage ..................................................................................... 90

Table 29: Port State Options ................................................................................................................................ 91

Table 30: VLANTable Settings for Figure 15 ........................................................................................................ 95

Table 31: VLANTable Settings for Figure 16 ........................................................................................................ 96

Table 32: 802.1s Port State Options .................................................................................................................... 98

Table 33: VTU Operation Registers ..................................................................................................................... 99

Table 34: VTU Entry Format............................................................................................................................... 100

Table 35: VTU Get Next Operation Register Usage........................................................................................... 102

Table 36: VTU Load/Purge Operation Register Usage ...................................................................................... 103

Table 37: VTU Get/Clear Violation Data Register Usage ................................................................................... 104

Table 38: Example VID Assignment Summary .................................................................................................. 107

Table 39: Ingress Forward Tag Fields ................................................................................................................ 113

Table 40: Ingress From_CPU Tag Fields ........................................................................................................... 114

Table 41: Egress Forward Tag Fields ................................................................................................................ 128

Table 42: Egress To_CPU Tag Fields ................................................................................................................ 129

Doc. No. MV-S102629-00 Rev. C CONFIDENTIAL Copyright © 2006 Marvell

Page 12 Document Classification: Proprietary Information June 9, 2006, Advance

Table 43: Egress Header Fields ..........................................................................................................................131

Table 44: 5B/4B Code Mapping ..........................................................................................................................141

Table 45: Scrambler Settings ..............................................................................................................................142

Table 46: Operating Mode Power Consumption .................................................................................................145

Table 47: FEFI Select..........................................................................................................................................146

Table 48: Registers for DTE Detect ....................................................................................................................149

Table 49: MDI/MDIX Pin Functions .....................................................................................................................150

Table 50: Parallel LED Hardware Defaults..........................................................................................................152

Table 51: Parallel LED Display Interpretation......................................................................................................153

Table 52: Serial LED Hardware Defaults (S = Single).........................................................................................158

Table 53: Serial LED Display Order ....................................................................................................................158

Table 54: Single LED Display Mode....................................................................................................................159

Table 55: Dual LED Display Mode ......................................................................................................................160

Table 56: Serial Management Interface Protocol Example .................................................................................163

Table 57: Register Map—Multi-Chip Addressing Mode ......................................................................................164

Table 58: Register Map—Single-Chip Addressing Mode ....................................................................................164

Table 59: SMI Command Register ......................................................................................................................169

Table 60: SMI Data Register ...............................................................................................................................170

Table 61: Port Status Register ............................................................................................................................174

Table 62: Port Configuration Matrix.....................................................................................................................177

Table 63: PCS Control Register ..........................................................................................................................178

Table 64: Switch Identifier Register.....................................................................................................................179

Table 65: Port Control Register ...........................................................................................................................180

Table 66: Port Control 1 ......................................................................................................................................183

Table 67: Port Based VLAN Map ........................................................................................................................184

Table 68: Default Port VLAN ID & Priority, .........................................................................................................185

Table 69: Port Control 2 Register ........................................................................................................................186

Table 70: Rate Control ........................................................................................................................................189

Table 71: Rate Control 2 .....................................................................................................................................190

Table 72: Port Association Vector .......................................................................................................................191

Table 73: InDiscards Low Counter ......................................................................................................................192

Table 74: InDiscards High Counter .....................................................................................................................192

Table 75: InFiltered Counter................................................................................................................................192

Table 76: OutFiltered Counter .............................................................................................................................193

Table 77: Port IEEE Priority Remapping Registers (88E6095 and 88E6095F devices only)..............................194

Table 78: Port IEEE Priority Remapping Registers (88E6095 and 88E6095F devices only)..............................195

Table 79: Switch Global Status Register .............................................................................................................197

Table 80: Switch MAC Address Register Bytes 0 & 1 ........................................................................................199

Table 81: Switch MAC Address Register Bytes 2 & 3, ........................................................................................199

Table 82: Switch MAC Address Register Bytes 4 & 5 .........................................................................................199

Table 83: Switch Global Control Register...........................................................................................................200

Table 84: VTU Operation Register ......................................................................................................................202

Table 85: VTU VID Register ...............................................................................................................................204

Table 86: VTU Data Register Ports 0 to 3 ...........................................................................................................205

Copyright © 2006 Marvell CONFIDENTIAL Doc. No. MV-S102629-00 Rev. C

June 9, 2006, Advance Document Classification: Proprietary Information Page 13

Link Street® 88E6092/88E6095/88E6095F

8 FE + 3 GE Stackable Ethernet Switch with QoS and 802.1Q

Table 87: VTU Data Register Ports 4 to 7 .......................................................................................................... 206

Table 88: VTU Data Register Port 8 to 10 .......................................................................................................... 207

Table 89: ATU Control Register ......................................................................................................................... 208

Table 90: ATU Operation Register ..................................................................................................................... 209

Table 91: ATU Data Register ............................................................................................................................. 211

Table 92: ATU MAC Address Register Bytes 0 & 1 ........................................................................................... 212

Table 93: ATU MAC Address Register Bytes 2 & 3 .......................................................................................... 212

Table 94: ATU MAC Address Register Bytes 4 & 5 ........................................................................................... 212

Table 95: IP-PRI Mapping Register 0 ................................................................................................................. 213

Table 96: IP-PRI Mapping Register 1 ................................................................................................................. 213

Table 97: IP-PRI Mapping Register 2 ................................................................................................................. 214

Table 98: IP-PRI Mapping Register 3 ................................................................................................................. 214

Table 99: IP-PRI Mapping Register 4 ................................................................................................................. 215

Table 100:IP-PRI Mapping Register 5 ................................................................................................................. 215

Table 101:IP-PRI Mapping Register 6 ................................................................................................................. 216

Table 102:IP-PRI Mapping Register 7 ................................................................................................................. 216

Table 103:IEEE-PRI Register .............................................................................................................................. 217

Table 104:Core Tag Type.................................................................................................................................... 218

Table 105:Monitor Control ................................................................................................................................... 219

Table 106:Global Control 2.................................................................................................................................. 220

Table 107:Stats Operation Register .................................................................................................................... 221

Table 108:Stats Counter Register Bytes 3 & 2 .................................................................................................... 223

Table 109:Stats Counter Register Bytes 1 & 0 .................................................................................................... 223

Table 110:MGMT Enable Register ...................................................................................................................... 225

Table 111:Flow Control Delay Register ............................................................................................................... 225

Table 112:Switch Management Register............................................................................................................. 226

Table 113:Device Mapping Table Register ......................................................................................................... 228

Table 114:Trunk Mask Table Register ................................................................................................................ 229

Table 115:Trunk Members Table Register .......................................................................................................... 230

Table 116:PHY Register Map .............................................................................................................................. 233

Table 117:PHY Control Register ......................................................................................................................... 234

Table 118:PHY Status Register........................................................................................................................... 237

Table 119:PHY Identifier ..................................................................................................................................... 239

Table 120:PHY Identifier ..................................................................................................................................... 239

Table 121:Auto-Negotiation Advertisement Register .......................................................................................... 240

Table 122:Link Partner Ability Register (Base Page) .......................................................................................... 242

Table 123:Link Partner Ability Register (Next Page) ........................................................................................... 243

Table 124:Auto-Negotiation Expansion Register................................................................................................. 244

Table 125:Next Page Transmit Register ............................................................................................................. 245

Table 126:Link Partner Next Page Register ........................................................................................................ 246

Table 127:PHY Specific Control Register............................................................................................................ 247

Table 128:PHY Specific Status Register ............................................................................................................. 250

Table 129:PHY Interrupt Enable.......................................................................................................................... 252

Table 130:PHY Interrupt Status........................................................................................................................... 254

Doc. No. MV-S102629-00 Rev. C CONFIDENTIAL Copyright © 2006 Marvell

Page 14 Document Classification: Proprietary Information June 9, 2006, Advance

Table 131:PHY Interrupt Port Summary (Global) .................................................................................................256

Table 132:Receive Error Counter.........................................................................................................................257

Table 133:LED Parallel Select Register (bits 11:0 are Global bits) .....................................................................258

Table 134:LED Stream Select for Serial LEDs (Global Register) - 88E6095F Only ............................................260

Table 135:PHY LED Control Register (bits 14:0 are Global bits) .........................................................................262

Table 136:PHY Manual LED Override .................................................................................................................263

Table 137:VCT™ Register for TXP/N Pins...........................................................................................................265

Table 138:VCT™ Register for RXP/N pins...........................................................................................................266

Table 139:PHY Specific Control Register II..........................................................................................................267

Table 140: Absolute Maximum Ratings................................................................................................................268

Table 141:Recommended Operating Conditions .................................................................................................269

Table 142:Current Consumption ..........................................................................................................................272

Table 143:Digital Operating Conditions................................................................................................................273

Table 144:Transmitter DC Characteristics with Px_VTT = 1.5V Typical ..............................................................274

Table 145:Transmitter DC Characteristics with Px_VTT = 1.2V Typical ..............................................................274

Table 146:Receiver DC Characteristics ...............................................................................................................275

Table 147:IEEE DC Transceiver Parameters.......................................................................................................276

Table 148:Reset and Configuration Timing ..........................................................................................................277

Table 149:Clock Timing........................................................................................................................................278

Table 150:GMII Transmit Timing ..........................................................................................................................279

Table 151:GMII Receive Timing ...........................................................................................................................280

Table 152:MII MAC Mode Clock Timing...............................................................................................................281

Table 153:MII Receive Timing—MAC Mode 100 Mbps Operation.......................................................................282

Table 154:MII Receive Timing—MAC Mode 200 Mbps Operation.......................................................................282

Table 155:MII Transmit Timing—MAC Mode 100 Mbps Operation......................................................................283

Table 156:MII Transmit Timing—MAC Mode 200 Mbps Operation......................................................................284

Table 157:Serial Management Interface Clock Timing (CPU Set) .......................................................................285

Table 158:Serial Management Interface Data Timing (CPU Set).........................................................................286

Table 159:Serial Management Interface Timing (PHY Set) .................................................................................287

Table 160:EEPROM Timing .................................................................................................................................288

Table 161: SERDES (Serial Interface) Transmitter AC Characteristics ...............................................................289

Table 162: SERDES (Serial Interface) Receiver AC Characteristics ...................................................................289

Table 163:IEEE AC Parameters...........................................................................................................................290

Table 164:88E6092/88E6095 176-Pin TQFP EPAD Package Dimensions in mm ..............................................292

Table 165:88E6095F 216-pin LQFP EPAD Package Dimensions .......................................................................294

Table 166:88E6092/88E6095/88E6095F Part Order Options - RoHS 5/6 Compliant Package ...........................295

Table 167:88E6092/88E6095/88E6095F Part Order Options - RoHS 6/6 Compliant Package ...........................295

Copyright © 2006 Marvell CONFIDENTIAL Doc. No. MV-S102629-00 Rev. C

June 9, 2006, Advance Document Classification: Proprietary Information Page 15

Link Street® 88E6092/88E6095/88E6095F

8 FE + 3 GE Stackable Ethernet Switch with QoS and 802.1Q

List of Figures

Figure 1: 88E6092/88E6095 Device 176 TQFP EPAD Package Pinout............................................................ 18

Figure 2: 88E6095F Device 216 LQFP EPAD Package Pinout ......................................................................... 19

Figure 3: 16 FE + 2 GE Ports............................................................................................................................. 56