Professional Documents

Culture Documents

Di146 0

Di146 0

Uploaded by

amitOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Di146 0

Di146 0

Uploaded by

amitCopyright:

Available Formats

DI-146 Design Idea

®

TOPSwitch-HX

35 W LCD Monitor Power Supply

Application Device Power Output Input Voltage Output Voltage Topology

LCD Monitor TOP258PN 35 W 90 – 264 VAC 5 V, 15 V Flyback

Design Highlights minimize cost by eliminating external heatsinks. Ideal applications

• High efficiency include LCD monitor power supplies, which typically require low

• >83% full load efficiency (Meets CEC 2008 requirements standby and no-load power consumption.

of 82%)

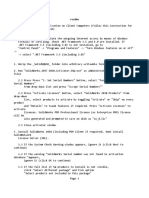

• Delivers 35 W at 50° C ambient without requiring an external The AC input is rectified (D1–D4), filtered (C4) and connected

heat sink across the primary side power components (T1 and U1). Diodes

• Low no-load and standby power consumption D1 and D3 were selected as fast recovery diodes for better EMI

• 0.55 W standby output power for <1 W input performance. EMI filtering is provided by components, C4, C5,

• No-load power consumption <160 mW at 230 VAC L1, C7 and C11. Thermistor RT1 limits the inrush current drawn

• Integrated safety/reliability features: by the circuit on application of input AC.

• Accurate, auto-recovering, hysteretic thermal shutdown

function maintains safe IC temperatures under all conditions To optimize efficiency under all load conditions, U1 operates in

• Auto-restart protects against output short circuits and open one of four modes. From no-load to full load, these are: multi-

feedback loops cycle modulation, fixed frequency PWM (25 kHz), variable

• Output OVP configurable for latching or self recovering frequency PWM and fixed frequency PWM (66 kHz). In all modes

• Meets EN55022 and CISPR-22 Class B conducted EMI with the controller maintains a linear relationship between duty cycle

>10 dBμV margin and control pin current so that the transition between modes is

seamless.

Operation

The isolated flyback converter shown in Figure 1 was designed

Zener diode VR2 and resistor R5 form the latching output over-

around a member of the TOPSwitch-HX family, the TOP258PN

voltage protection (OVP) circuit. Increased voltage at the output

(U1). A device in the P package (8-pin DIP) was selected to

C6 C7 C12

3.9 nF 2.2 nF R11 470 pF

1 kV 250 VAC 33 7 100 V

D7 C13 C14 C15

R6 T1 SB580 680 MF 680 MF L2 220 MF

22 k7 2 EER28 7 25 V 25 V 3.3 MH 25 V +15 V,

2W 1.9 A

D1 D2 VR1 C16 C18

P6KE170A 470 pF R12 L3 RTN

1N4937 1N4007 33 7 3.3 MH 220 MF

100 V 10 V

3 11 +5 V,

1.7 A

R7 D8

10 7 SB530

4 9

1/2 W RTN

C10 C17

6 2200 MF

D3 10 MF

1N4937 D5 R10 50 V C11 10 V

D4 R3 D6

2.0 M7 FR106 FR106 4.7 7 2.2 nF R19

1N4007 250 VAC

5 10 7

L1 R4

6.8 mH 2.0 M7 VR3

R14 BZX79-B10

C5 C4 R13 22 7 10 V

R1 R2 22 nF 100 MF 330 7 C19 2%

1 M7 1 M7 630 V 400 V VR2 1.0 MF

R5 1N5250B 50 V

5.1 k7 20 V U2B

C3 PC817A R15

F1 220 nF 1 k7

3.15 A 275 VAC

U2A

TOPSwitch-HX PC817A

RT1 O D M U1

L 10 7 t R18 R20

CONTROL TOP258PN 255k7 12.4 k7

E C 1% 1%

R16 R17

10 k7 10 k7

N S R8 D9

C8 6.8 7 1N4148

90 - 265 C21

VAC 100 nF

50 V C9 220 nF

47 MF 50 V

16 V C20

10 MF U3 R21

50 V TL431 10 k7

2% 1%

PI-4797-011608

Figure 1. Universal input, 35 W Output, LCD Power Supply, Using a TOP258PN With No External Heat Sink.

www.powerint.com January 2008

will also result in an increased voltage at the output of the bias 80

PI-4798-090407

winding. Zener VR2 will break down, and current will flow into the

M pin of U1. When the M pin current exceeds 112 μA, the M pin 70

voltage is internally reduced by 0.5 V. If the M pin current exceeds QP

60

336 μA, the OV condition causes a latched shutdown. If the M AV

pin current is between 112 μA and 336 μA for >100 μs, the 50

shutdown is hysteretic. Resistor R5 defines the M pin current. 40

dBMV

Output voltage feedback is derived from both the outputs for 30

better cross-regulation. Capacitor C19 and resistor R14 form the 20

phase boost network and provide adequate phase margin to

ensure stable operation over the entire operating voltage range. 10

Resistors R19 and VR3 improve cross regulation when only the 0

5 V output is loaded, preventing the 15 V output operating at the

higher end of the specification. -10

Key Design Points -20

0.15 1.0 10.0 100.0

• Capacitor C5 is a decoupling capacitor connected across the

DC supply and is located physically close to the high frequency MHz

switching circuit, which helps in reducing differential mode EMI. Figure 2. Worst Case Conducted EMI (230 VAC).

• If latching OVP is desired, the value of R5 should be reduced to

20 Ω to allow for more current into the M pin.

• Design the RCD clamp (R6, R7, C6 and D5) for normal opera- Transformer Parameters

tion, thereby maximizing efficiency at light load. Zener diode EER28 NC-2H or equivalent, gapped for ALG of

VR1 provides a defined maximum clamp voltage and typically Core Material

148 nH/t2

only conducts during load transients or during an overload Bobbin EER28, 12 pin, Horizontal

condition.

3mm margins on both sides of bobbin to meet

• The secondary side snubber (R11, C12, R12 and C16) reduce

safety

high frequency secondary diode ringing and improve EMI. Primary: 20T × 1 AWG 26, tape

• In a three-wire system, placing Y capacitors between line/ Winding Details Bias: 9T × 2, AWG 26, 3 layers, tape

neutral and earth ground helps reduce common mode EMI. 5 V: 3T, foil 0.52 mm thickness

• As the output return is connected to safety earth ground, two 15 V: 5T × 3, AWG 26, 3 layers tape

2.2 nF Y capacitors (C7 and C11) are acceptable. For floating Primary: 50T × 1, AWG 26, tape

outputs, the maximum capacitance is normally limited to 1 x 2.2 Primary-1 (4-3), Bias (6-5), 5 V (11-9),

Winding Order

nF due to line frequency leakage current limits. 15 V (7-11), Primary-2 (3-2)

• Soft finish capacitor C20 ensures no output overshoot at start- Primary Inductance 1041 μH, ±10%

up. Diode D9 isolates this capacitor from the feedback loop Resonant

after start-up. Resistor R16 allows a path for this capacitor to 1000 kHz (minimum)

Frequency

discharge into the 5 V load.

Leakage

Inductance 30 μH (maximum)

Table 1. Transformer Parameters. (NC = No Connection).

Power Integrations Power Integrations reserves the right to make changes to its products at any time to improve reliability or manufacturability. Power

5245 Hellyer Avenue Integrations does not assume any liability arising from the use of any device or circuit described herein. POWER INTEGRATIONS

San Jose, CA 95138, USA. MAKES NO WARRANTY HEREIN AND SPECIFICALLY DISCLAIMS ALL WARRANTIES INCLUDING, WITHOUT LIMITATION, THE IMPLIED

Main: +1 408-414-9200 WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS.

Customer Service The products and applications illustrated herein (transformer construction and circuits external to the products) may be covered by

Phone: +1-408-414-9665 one or more U.S. and foreign patents or potentially by pending U.S. and foreign patent applications assigned to Power Integrations.

Fax: +1-408-414-9765 A complete list of Power Integrations' patents may be found at www.powerint.com. Power Integrations grants

Email: usasales@powerint.com its customers a license under certain patent rights as set forth at http://www.powerint.com/ip.htm.

The PI logo, TOPSwitch, TinySwitch, LinkSwitch, DPA-Switch, PeakSwitch, EcoSmart, Clampless, E-Shield, Filterfuse, StackFET,

On the Web PI Expert and PI FACTS are trademarks of Power Integrations, Inc. Other trademarks are property of their respective companies.

www.powerint.com ©2007, Power Integrations, Inc.

C

01/08 DI-146

You might also like

- Di22 HP 70 W 19 V External Laptop Adapter Schematic DiagramDocument2 pagesDi22 HP 70 W 19 V External Laptop Adapter Schematic DiagramTonpitonpi Ton Pi75% (4)

- The Hendershot Generator - Free EnergyDocument15 pagesThe Hendershot Generator - Free Energyoapred97% (33)

- 1008AE Specification: Specialty SummarizeDocument11 pages1008AE Specification: Specialty Summarizenovram novNo ratings yet

- MPPT Solar Controller Manual From MakeSkyBlueDocument5 pagesMPPT Solar Controller Manual From MakeSkyBluexinn-495% (22)

- Logik 26SDocument21 pagesLogik 26SRamsi SembiringNo ratings yet

- Di-187 Design Idea Topswitch-Hx: 35 W LCD MonitorDocument2 pagesDi-187 Design Idea Topswitch-Hx: 35 W LCD MonitorIvanê FonsecaNo ratings yet

- Di-198 Design Idea Linkswitch-Cv: Wide Range DVD Player Multiple Output Power Supply Without Need For OptocouplerDocument2 pagesDi-198 Design Idea Linkswitch-Cv: Wide Range DVD Player Multiple Output Power Supply Without Need For OptocouplerAllyfranhy Nunes AlvesNo ratings yet

- Di-91 Design Idea Tinyswitch-Iii: 12 W Universal Input CV AdapterDocument2 pagesDi-91 Design Idea Tinyswitch-Iii: 12 W Universal Input CV Adapterahmed chaouki ChamiNo ratings yet

- TNY278PNDocument4 pagesTNY278PNJose BenavidesNo ratings yet

- Top259en PDFDocument2 pagesTop259en PDFJose BenavidesNo ratings yet

- Di-123 Design Idea Tinyswitch-Iii: 9.65 W, Dual Output Power Supply For Residential Heating ControlDocument2 pagesDi-123 Design Idea Tinyswitch-Iii: 9.65 W, Dual Output Power Supply For Residential Heating Controlahmed chaouki ChamiNo ratings yet

- DatasheetDocument2 pagesDatasheetRyanz Nayrz100% (1)

- Features: Lt1375/Lt1376 1.5A, 500Khz Step-Down Switching RegulatorsDocument29 pagesFeatures: Lt1375/Lt1376 1.5A, 500Khz Step-Down Switching RegulatorsSergio MuriloNo ratings yet

- Di-143 Design Idea Topswitch-Hx: High Effi Ciency Inkjet Power Supply Provides Up To 80 Watts of Peak PowerDocument2 pagesDi-143 Design Idea Topswitch-Hx: High Effi Ciency Inkjet Power Supply Provides Up To 80 Watts of Peak PowerJose BenavidesNo ratings yet

- 45W Ac-Dc Adapter With Standby Function: AN1134 Application NoteDocument9 pages45W Ac-Dc Adapter With Standby Function: AN1134 Application NoteGrzegorz WegnerNo ratings yet

- Pdiol 2008dec24 Supply An 01Document3 pagesPdiol 2008dec24 Supply An 01Roberto De Mesa PNo ratings yet

- An2001 Application Note: Vipower™: The Viper53-E Single Output Reference Board With 90 To 264 Vac Input, 24 W OutputDocument6 pagesAn2001 Application Note: Vipower™: The Viper53-E Single Output Reference Board With 90 To 264 Vac Input, 24 W OutputamitNo ratings yet

- LNK364PNDocument2 pagesLNK364PNJose Benavides100% (2)

- TOPSwitch Buck Converter (NonIsolated)Document2 pagesTOPSwitch Buck Converter (NonIsolated)vladimir022009No ratings yet

- DE1 Lab ReportDocument7 pagesDE1 Lab ReportRuth Abegail de VeraNo ratings yet

- Obsolete Product(s) - Obsolete Product(s) : EVL6562A-TM-80WDocument6 pagesObsolete Product(s) - Obsolete Product(s) : EVL6562A-TM-80Wkamran moradiNo ratings yet

- Mains Failure Indicator AlarmDocument33 pagesMains Failure Indicator AlarmamolNo ratings yet

- STR-A6100: SeriesDocument2 pagesSTR-A6100: SeriesY. Leonel MolinaNo ratings yet

- TNY264PNDocument6 pagesTNY264PNJose Benavides100% (1)

- Design Principle Circuit Descripition: A) B) C) D) E) F) G) H) I)Document33 pagesDesign Principle Circuit Descripition: A) B) C) D) E) F) G) H) I)AJAY VISHNU M SNo ratings yet

- 1.5A Switch Step Down Switching Regulator: 1 General FeaturesDocument11 pages1.5A Switch Step Down Switching Regulator: 1 General FeaturesRene gNo ratings yet

- Buck Based LED DriverDocument22 pagesBuck Based LED DriverCruz JimenezNo ratings yet

- Topswitch: Flyback Transformer Design For Power SuppliesDocument12 pagesTopswitch: Flyback Transformer Design For Power SuppliesShirish BhagwatNo ratings yet

- ACPL-C87AT/ACPL-C87BT: Data SheetDocument16 pagesACPL-C87AT/ACPL-C87BT: Data SheetMattias RahmNo ratings yet

- Application Note An-45 Linkswitch-Cv Family: Design GuideDocument18 pagesApplication Note An-45 Linkswitch-Cv Family: Design Guidebharath prabhuNo ratings yet

- FAN7314A - : LCD Backlight Inverter Drive ICDocument3 pagesFAN7314A - : LCD Backlight Inverter Drive ICКОРЮН ГАБРИЕЛЯНNo ratings yet

- AIC2323Document13 pagesAIC2323Firman SyahNo ratings yet

- TNY268PNDocument2 pagesTNY268PNJose BenavidesNo ratings yet

- AL9910/ AL9910A/ AL9910-5/ AL9910A-5: Universal High Voltage High Brightness Led DriverDocument15 pagesAL9910/ AL9910A/ AL9910-5/ AL9910A-5: Universal High Voltage High Brightness Led DrivernareshNo ratings yet

- Hardware Implementation: 10.1 Inverter DesignDocument10 pagesHardware Implementation: 10.1 Inverter DesignSandeep SNo ratings yet

- Fundamentals of PWM SMPSDocument7 pagesFundamentals of PWM SMPSRagnar RagnarsonNo ratings yet

- L 6928D - ReguladorDocument9 pagesL 6928D - ReguladorTiago LeonhardtNo ratings yet

- Halogen 12vDocument17 pagesHalogen 12veryNo ratings yet

- Tps54332 3.5-A, 28-V, 1-Mhz, Step-Down DC-DC Converter With Eco-Mode™Document35 pagesTps54332 3.5-A, 28-V, 1-Mhz, Step-Down DC-DC Converter With Eco-Mode™dedy gunawanNo ratings yet

- Tops WithDocument8 pagesTops Withtiburcio2000No ratings yet

- 2 UkDocument2 pages2 UkJosé ManuelNo ratings yet

- 28V 3A Step-Down Switching Regulator: Power Management Features DescriptionDocument19 pages28V 3A Step-Down Switching Regulator: Power Management Features Descriptionteban09No ratings yet

- Evaluation and Finding of Isolated Flyback Converter: © 2016 ROHM Co.,LtdDocument29 pagesEvaluation and Finding of Isolated Flyback Converter: © 2016 ROHM Co.,LtdNhatNo ratings yet

- sc4525c 1278277Document23 pagessc4525c 1278277Paulo OliveiraNo ratings yet

- Slua 253Document4 pagesSlua 253armin rahmatiNo ratings yet

- L5972DDocument10 pagesL5972DLuis Enrique De los Santos FarfánNo ratings yet

- Di 124Document2 pagesDi 124shreyNo ratings yet

- 4274GV50 5v Regulator PDFDocument13 pages4274GV50 5v Regulator PDFvanadium0No ratings yet

- Dsa 00284855Document14 pagesDsa 00284855kasih lestariiNo ratings yet

- Data SheetDocument6 pagesData SheetTuấn Âm Thanh Hi-endNo ratings yet

- En - Power Factor Corrector Controllers PortfolioDocument26 pagesEn - Power Factor Corrector Controllers PortfolioHai Quan NguyenNo ratings yet

- Control IC For Single-Ended and Push-Pull Switched-Mode Power Supplies (SMPS) TDA 4718 ADocument17 pagesControl IC For Single-Ended and Push-Pull Switched-Mode Power Supplies (SMPS) TDA 4718 ASledge HammerNo ratings yet

- Power Supply Trainer Using Lm723 IcDocument8 pagesPower Supply Trainer Using Lm723 IcDinesh Kumar MehraNo ratings yet

- Descriptio Features: LT1505 Constant-Current/Voltage High Efficiency Battery ChargerDocument16 pagesDescriptio Features: LT1505 Constant-Current/Voltage High Efficiency Battery ChargerCarlos Henrique RibasNo ratings yet

- 74LVC1G04Document16 pages74LVC1G04docoodo123No ratings yet

- Need of MicrocontrollerDocument18 pagesNeed of MicrocontrollerRaji PNo ratings yet

- DatasheetDocument11 pagesDatasheetGeorges TaradauxNo ratings yet

- Features: LT1176/LT1176-5 Step-Down Switching RegulatorDocument8 pagesFeatures: LT1176/LT1176-5 Step-Down Switching RegulatorDreavus HashirobiNo ratings yet

- NCP 1055 ST 100Document26 pagesNCP 1055 ST 100NacerNo ratings yet

- 1 CL23XX EN Rev.1.0 2641Document11 pages1 CL23XX EN Rev.1.0 2641Sumit SinghNo ratings yet

- 3 A, 2 MHZ Buck-Regulating Led Driver: Description Features and BenefitsDocument12 pages3 A, 2 MHZ Buck-Regulating Led Driver: Description Features and BenefitsElizabet VallejoNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- 410bew37037364 - Ac0346194 CPP BFLDocument20 pages410bew37037364 - Ac0346194 CPP BFLamitNo ratings yet

- BL Shanghai Belling ULN2003 - C2690547Document7 pagesBL Shanghai Belling ULN2003 - C2690547amitNo ratings yet

- 500 MaDocument2 pages500 MaamitNo ratings yet

- 4100CD37037361 SoaDocument2 pages4100CD37037361 SoaamitNo ratings yet

- Eap 1.5Document20 pagesEap 1.5amitNo ratings yet

- Mr. Paul Arunachal El-Mech Ofr 060422Document8 pagesMr. Paul Arunachal El-Mech Ofr 060422amitNo ratings yet

- LP YOR2 As CWOEh 1 F CDocument1 pageLP YOR2 As CWOEh 1 F CamitNo ratings yet

- MAjuw PLZ8 Z VAMH6 GDocument5 pagesMAjuw PLZ8 Z VAMH6 GamitNo ratings yet

- Techno Times WebsiteDocument4 pagesTechno Times WebsiteamitNo ratings yet

- IRI-22877-Howrah - Ernakulam Antyodaya ExpressDocument1 pageIRI-22877-Howrah - Ernakulam Antyodaya ExpressamitNo ratings yet

- Micromachines 12 00571Document14 pagesMicromachines 12 00571amitNo ratings yet

- Technical Information: Display Console SpecificationsDocument1 pageTechnical Information: Display Console SpecificationsamitNo ratings yet

- Arb 1375Document69 pagesArb 1375amitNo ratings yet

- DSAFRAZ0020366Document3 pagesDSAFRAZ0020366amitNo ratings yet

- Canon LBP 2900 3000 Service ManualDocument136 pagesCanon LBP 2900 3000 Service ManualamitNo ratings yet

- LJ MOPIER 320 - FunctionalOverviewDocument71 pagesLJ MOPIER 320 - FunctionalOverviewamitNo ratings yet

- Oriss Quartz Kitchen Sink Price ListDocument4 pagesOriss Quartz Kitchen Sink Price ListamitNo ratings yet

- prv6 239985Document7 pagesprv6 239985amitNo ratings yet

- WP CatlougeDocument12 pagesWP CatlougeamitNo ratings yet

- 64034-m6vlq GrandDocument37 pages64034-m6vlq GrandamitNo ratings yet

- SR CatalogDocument196 pagesSR CatalogamitNo ratings yet

- Wbut MSC SyllabusDocument23 pagesWbut MSC SyllabusamitNo ratings yet

- Dro 1Document3 pagesDro 1amitNo ratings yet

- SW Installation For JiwagoDocument5 pagesSW Installation For JiwagoamitNo ratings yet

- Features: Elektronische Bauelemente NPN TypeDocument2 pagesFeatures: Elektronische Bauelemente NPN TypeamitNo ratings yet

- Amit Kumar Das: 32, Ezra Street, 9 Floor, Room No.-965 Kolkata-700001 EmailDocument2 pagesAmit Kumar Das: 32, Ezra Street, 9 Floor, Room No.-965 Kolkata-700001 EmailamitNo ratings yet

- UG CBCS Syllabus 2018 NewDocument21 pagesUG CBCS Syllabus 2018 NewamitNo ratings yet

- Nitriding DatasheetDocument4 pagesNitriding DatasheetamitNo ratings yet

- 58 CBBBBBF 09 C 4Document41 pages58 CBBBBBF 09 C 4amitNo ratings yet

- Project On Bakery by AmitDocument5 pagesProject On Bakery by AmitamitNo ratings yet

- CT354 Optocoupler DatasheetDocument10 pagesCT354 Optocoupler DatasheetFrame JoshNo ratings yet

- Synchronous MachineDocument19 pagesSynchronous MachineRavindra JoshiNo ratings yet

- ABTED205162E - 4 - Diagramas ElectricosDocument8 pagesABTED205162E - 4 - Diagramas Electricospablo ignacio cancino molinaNo ratings yet

- 9800 Illustrated Parts Manual: 5375787-1EN-04 Rev 9Document348 pages9800 Illustrated Parts Manual: 5375787-1EN-04 Rev 9Rudimar SaggioratoNo ratings yet

- Applied Sciences: Safety Issues Referred To Induced Sheath Voltages in High-Voltage Power Cables-Case StudyDocument16 pagesApplied Sciences: Safety Issues Referred To Induced Sheath Voltages in High-Voltage Power Cables-Case Studynalvaro88No ratings yet

- Session 2-1Document46 pagesSession 2-1Youssef El-HendawyNo ratings yet

- Site Acceptance Test Report For LV CableDocument4 pagesSite Acceptance Test Report For LV CableGajendran SriramNo ratings yet

- TC74HC14AP, TC74HC14AF: Hex Schmitt InverterDocument7 pagesTC74HC14AP, TC74HC14AF: Hex Schmitt InverterAmirNo ratings yet

- Afridi CV 2013Document13 pagesAfridi CV 2013seyed mohsen SalehiNo ratings yet

- 2018 OA 25 Rule 16 330Document4 pages2018 OA 25 Rule 16 330Reeman432No ratings yet

- Diala AX TdsDocument2 pagesDiala AX TdsAbdalhakeem Al turkyNo ratings yet

- Design and Fabrication of Automatic Single Axis Solar Tracker For Solar PanelDocument4 pagesDesign and Fabrication of Automatic Single Axis Solar Tracker For Solar PanelLuis Miguel Fenco LlanosNo ratings yet

- Siesta I TS Version 3.2Document122 pagesSiesta I TS Version 3.2Ignacio Nicolas50% (2)

- Kenworth T440 T470 T660 W900 Late Model T800 PMG Installation GuideDocument8 pagesKenworth T440 T470 T660 W900 Late Model T800 PMG Installation GuideMario SanchezNo ratings yet

- Case Study Presentation On LGDocument22 pagesCase Study Presentation On LGShamim KhanNo ratings yet

- Cybenetics - Evaluation - Report - Galax - OMEGA GLX1000Document12 pagesCybenetics - Evaluation - Report - Galax - OMEGA GLX1000intel boyNo ratings yet

- Unit IDocument6 pagesUnit ILevingstan YesudhasNo ratings yet

- NUREG CR-3263 Correlation of Electrical Cable Failure With Mechanical Degradation (NUREG CR-3263, SAND83-2622)Document100 pagesNUREG CR-3263 Correlation of Electrical Cable Failure With Mechanical Degradation (NUREG CR-3263, SAND83-2622)jimodexueNo ratings yet

- Instructions For Appropriate HandlingDocument4 pagesInstructions For Appropriate HandlingAlioune Badara DioufNo ratings yet

- Case Study On Inductive Proximity SwitchesDocument4 pagesCase Study On Inductive Proximity SwitchesMANASNo ratings yet

- Roland VM-3100 - VM-3100 Pro ContentsDocument1 pageRoland VM-3100 - VM-3100 Pro Contentstuxedo44No ratings yet

- ENA - TS - 41-37 - Part - 3 CBDocument40 pagesENA - TS - 41-37 - Part - 3 CBRodolfo DelgadoNo ratings yet

- Revised Syllabus of Physics - 2022 23 of HS 2nd Year New 1Document5 pagesRevised Syllabus of Physics - 2022 23 of HS 2nd Year New 1Prajnan pratim SharmaNo ratings yet

- 530AID01 DS en PDFDocument4 pages530AID01 DS en PDFHatem LaadhariNo ratings yet

- DR 890 Vs DR900 SepcDocument1 pageDR 890 Vs DR900 SepclinaNo ratings yet

- Competency Based Learning Material: Electrical Installation AND Maintenance NC IiDocument59 pagesCompetency Based Learning Material: Electrical Installation AND Maintenance NC IiTimothy John Natal Mandia100% (2)

- CVTDocument4 pagesCVTscribdkkkNo ratings yet