Professional Documents

Culture Documents

Assignment-2 Vlsi 29.04.2023

Assignment-2 Vlsi 29.04.2023

Uploaded by

040-Nishanth0 ratings0% found this document useful (0 votes)

12 views1 pageThe document outlines an assignment for a VLSI Design course. It provides details on the submission date, deadline, and instructions. Students are to answer a minimum of 20 questions out of the 25 total questions provided. The questions cover various topics in VLSI design including MOS fabrication procedures, logic gate design, DRAM operations, testability concepts, and more. Maximum marks are provided for each question.

Original Description:

Original Title

ASSIGNMENT-2 VLSI 29.04.2023

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThe document outlines an assignment for a VLSI Design course. It provides details on the submission date, deadline, and instructions. Students are to answer a minimum of 20 questions out of the 25 total questions provided. The questions cover various topics in VLSI design including MOS fabrication procedures, logic gate design, DRAM operations, testability concepts, and more. Maximum marks are provided for each question.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

0 ratings0% found this document useful (0 votes)

12 views1 pageAssignment-2 Vlsi 29.04.2023

Assignment-2 Vlsi 29.04.2023

Uploaded by

040-NishanthThe document outlines an assignment for a VLSI Design course. It provides details on the submission date, deadline, and instructions. Students are to answer a minimum of 20 questions out of the 25 total questions provided. The questions cover various topics in VLSI design including MOS fabrication procedures, logic gate design, DRAM operations, testability concepts, and more. Maximum marks are provided for each question.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

You are on page 1of 1

Assignment -2,subject:VLSI DESIGN ,SUB Code: 20EC C23 , VI SEM,ECE -E1,

submission date:29.04.2023, Deadline for submission:4.05.2023

-------------------------------------------------------------------------------------------------------------------------------

Answer any 6 questions from 1 to 11 questions and 12 to 25 compulsory MAX:100

Total :Min 20 questions out of 25

S. STEM CO BTL

no

1 Describe constructional features and performance characteristic of Pseudo- NMOS logic and 4 4

2 a. Derive pull up to pull down ratio for an NMOS inverter driven by another NMOS inverter. 4 1

b. Derive pull up to pull down ratio for an NMOS inverter driven by one or more pass transistors.

3 Clearly explain about ION-IMPLANTATION step in IC fabrication 3 2

4 Define Chemical Vapor Deposition 3 5

5 Draw circuit diagram of Bi-CMOS 2-input NAND gate 4 4

6 Define charge leakage in DRAM 5 2

5 Explain the NMOS &CMOS fabrication procedure 3 2

6 Design an area efficient layout diagram for the CMOS logic shown below Y = (A + B + C). 4 4

7 Explain various steps involved in photo lithography 5 4

8 Explain the design of MOS inverter with different loads 4 4

9 a) Realize XOR and XNOR circuits using transmission gates. b) transmission gates compared to pass txr 4 5

11 Draw the circuit diagrams and the corresponding stick diagrams for nMOS and CMOS inverters 4 2

12 Explain the Ion Implantation system in detail? 3 4

13 Design a D-FF using Transmission gate logic? 4 3

14 a) Compare SRAM and DRAM , b) Explain read and write operation of 3T DRAM 4 4

15 Explain read and write operations of 6T SRAM cell 5 2

Find the test vector for the following circuit using path sensitization method when path 3 is struck at 0. 5 3

16 Define controllability and observability 5 2

17 Draw the symbolic layout for the CMOS inverter and write the general CMOS logic gate layout 4 2

guidelines

18 Fault models (stuck-at 1 and stuck – at-0)-Path sensitization 5 5

19 What is the need of testability? Explain design for testability 5 4

20 Write a short note MOS layers and symbolic diagram translation to MASK form 3 4

21 A)Explain different forms of pull-ups used as load in CMOS enhancement. 4 2

B) Determine pull-up to pull-down ratio of an NMOS inverter when driven through one or more pass

transistors. 4 5

22 A) What is stick diagram and explain about different symbols used for components in Stick diagram. 3 4

Draw the stick and layout for a two input CMOS NAND gate

B) Design a stick diagram and layout for two input CMOS NAND gate indicating all the regions and

layers 4 5

23 a)Draw and explain the BiCMOS inverter, Bi-Cmos NAND & Bi-CMOS two-input NOR gates 3 2

b) Draw and explain NOR and NAND based ROM memory design

24 a)Draw and explain AND/OR representation of PLA b)Explain the challenges in testing of VLSI design 5 1

25 a)Explain the D-Algorithm with example b) Describe the ASIC and SOC 5 4

You might also like

- LO4: Testing: Unit 18-Computer Systems HardwareDocument8 pagesLO4: Testing: Unit 18-Computer Systems Hardware20holmesloNo ratings yet

- Module 05 - Macros 1 Rev 03Document14 pagesModule 05 - Macros 1 Rev 03ercanpekNo ratings yet

- Determination of The Effective Path of Contact of Undercut Involute Gear TeethDocument10 pagesDetermination of The Effective Path of Contact of Undercut Involute Gear Teethpriyanka moulikNo ratings yet

- 49 Test Bank 13Document13 pages49 Test Bank 13PL NLNo ratings yet

- Eprvd-102 Eprds-102a - 01.12 PDFDocument2 pagesEprvd-102 Eprds-102a - 01.12 PDFNaresh KumarNo ratings yet

- 18EI56Document6 pages18EI56Rocky BhaiNo ratings yet

- Advanced Digital VLSI Design (ECE 521) (Makeup) PDFDocument2 pagesAdvanced Digital VLSI Design (ECE 521) (Makeup) PDFRahul PinnamaneniNo ratings yet

- Vlsi QB - 22-23 - Mid - NewDocument4 pagesVlsi QB - 22-23 - Mid - Newyadhardha LingalaNo ratings yet

- M.Tech I Semester Supplementary Examinations February/March 2018Document1 pageM.Tech I Semester Supplementary Examinations February/March 2018baburao_kodavatiNo ratings yet

- VLSID R20 Q BankDocument4 pagesVLSID R20 Q BankSATYA SRI LIKHITHA DUSANAPUDINo ratings yet

- Gujarat Technological UniversityDocument1 pageGujarat Technological UniversityHet ShahNo ratings yet

- VLSI AssignDocument5 pagesVLSI AssignSrideviasokanNo ratings yet

- 20A04606 Basic VLSI DesignDocument1 page20A04606 Basic VLSI Design21x51a3249No ratings yet

- 19ec4202 Digital Ic DesignDocument5 pages19ec4202 Digital Ic Designsrihari_56657801No ratings yet

- EC19641-VLSI Design Part B Question BankDocument2 pagesEC19641-VLSI Design Part B Question BankmyavananNo ratings yet

- VLSI Model PAPER EEDocument2 pagesVLSI Model PAPER EEANUPAM KUMAR MISHRANo ratings yet

- BEC 306 VLSI Design End Term 2016 PAPERDocument2 pagesBEC 306 VLSI Design End Term 2016 PAPERmaanasvimahajan1319No ratings yet

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayNo ratings yet

- Vlsi QP 21,22Document11 pagesVlsi QP 21,22Arunitha ArulnathanNo ratings yet

- Time: 3 Hours Full Marks: 70Document3 pagesTime: 3 Hours Full Marks: 70pikluNo ratings yet

- CMOS Q BankDocument3 pagesCMOS Q BankRathore Yuvraj SinghNo ratings yet

- Eee ADocument6 pagesEee ASundaravadivel ArumugamNo ratings yet

- Question Paper Code: X10348: Reg. NoDocument2 pagesQuestion Paper Code: X10348: Reg. NoJaikumar RajendranNo ratings yet

- Question BankDocument13 pagesQuestion BankRishi JhaNo ratings yet

- 523 BA19 Ad 01Document5 pages523 BA19 Ad 01ramesh1926No ratings yet

- VLSI Question PaperDocument3 pagesVLSI Question Paper209X1A04D2 SHAIK ASMANo ratings yet

- WWW - Manaresults.Co - In: (Electronics and Communication Engineering)Document8 pagesWWW - Manaresults.Co - In: (Electronics and Communication Engineering)Adhvay KrishnaNo ratings yet

- VLSI Question BankDocument2 pagesVLSI Question BankVikash SharmaNo ratings yet

- Be Winter 2022Document2 pagesBe Winter 2022kaushal.21beect008No ratings yet

- BEC 306 VLSI Design End Term 2018 PAPERDocument2 pagesBEC 306 VLSI Design End Term 2018 PAPERmaanasvimahajan1319No ratings yet

- MCS 218Document2 pagesMCS 218Ujjwal BarmanNo ratings yet

- Time: 3 Hours Total Marks: 70: PD PLDocument1 pageTime: 3 Hours Total Marks: 70: PD PLDeepanshi RuhelaNo ratings yet

- VLSI DESIGN Question Bank: Unit 1Document12 pagesVLSI DESIGN Question Bank: Unit 1Babu GundlapallyNo ratings yet

- EC8095 QB VLSI DesignDocument10 pagesEC8095 QB VLSI DesignBhuvana EshwariNo ratings yet

- Guru Nanak Institutions Technical Campus (Autonomous) : Question Bank With Blooms Taxonomy Level (BTL)Document3 pagesGuru Nanak Institutions Technical Campus (Autonomous) : Question Bank With Blooms Taxonomy Level (BTL)sahithikocharlakotaNo ratings yet

- Vlsi Design Question Bank EEC 703Document10 pagesVlsi Design Question Bank EEC 703selvi0412No ratings yet

- 18CS44@AzDOCUMENTS inDocument6 pages18CS44@AzDOCUMENTS inAzeem TopNo ratings yet

- WWW - Manaresults.Co - In: (Electronics and Communication Engineering)Document2 pagesWWW - Manaresults.Co - In: (Electronics and Communication Engineering)venkiscribd444No ratings yet

- Vlsi QB LongDocument2 pagesVlsi QB LongTajinder SinghNo ratings yet

- VLSI DesignDocument1 pageVLSI DesignSurendar AviNo ratings yet

- 2020 09 14SupplementaryCS405CS405 D Ktu QbankDocument3 pages2020 09 14SupplementaryCS405CS405 D Ktu QbankCigi ManojNo ratings yet

- VTU Model Question Papers VI Sem ECE - TCEDocument44 pagesVTU Model Question Papers VI Sem ECE - TCEMr Ashutosh SrivastavaNo ratings yet

- Question Bank Fundamentals of CMOS VLSI-10EC56 15-16Document10 pagesQuestion Bank Fundamentals of CMOS VLSI-10EC56 15-16Pranav KpNo ratings yet

- CS405 Computer System Architecture, December 2019Document3 pagesCS405 Computer System Architecture, December 2019KarthikaNo ratings yet

- C G192056 Pages:3: Answer All Questions, Each Carries 4 MarksDocument3 pagesC G192056 Pages:3: Answer All Questions, Each Carries 4 MarksCigi ManojNo ratings yet

- 15A04802 Low Power VLSI Circuits & SystemsDocument1 page15A04802 Low Power VLSI Circuits & SystemsContent for all CreatorNo ratings yet

- VlSI Design OU Question PaperDocument1 pageVlSI Design OU Question PapershivagurramNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)Shri VarshaNo ratings yet

- MCS-218 Ignouassignmentguru - Com519Document11 pagesMCS-218 Ignouassignmentguru - Com519नितिन पटवालNo ratings yet

- M.Tech. Degree Examination, Dec.08/Jan.09: Advances in VLSI DesignDocument1 pageM.Tech. Degree Examination, Dec.08/Jan.09: Advances in VLSI DesignRavindra vsNo ratings yet

- VLSI Assignment 3Document2 pagesVLSI Assignment 3RIONA RACHEL JACOBNo ratings yet

- Be Summer 2021Document2 pagesBe Summer 2021Sandip SolankiNo ratings yet

- KVDocument2 pagesKVsrilatha sriNo ratings yet

- C G192056 Pages:3: Answer All Questions, Each Carries 4 MarksDocument3 pagesC G192056 Pages:3: Answer All Questions, Each Carries 4 MarksVicNo ratings yet

- Ec 703 2019-20Document2 pagesEc 703 2019-202000520310061No ratings yet

- VLSI Design Unit-2 Question BankDocument1 pageVLSI Design Unit-2 Question BankmadhuNo ratings yet

- MCS-218 AllDocument17 pagesMCS-218 Allxitere5524No ratings yet

- Question BankDocument9 pagesQuestion BankNiyas AhamedNo ratings yet

- Vlsi Model 4-QPDocument2 pagesVlsi Model 4-QPsanthoshNo ratings yet

- VLSI Design-QBANKDocument13 pagesVLSI Design-QBANKjascnjNo ratings yet

- Previous Question PapersDocument4 pagesPrevious Question Papersshaker423No ratings yet

- Dec 2018/ Jan 2019Document2 pagesDec 2018/ Jan 2019Kalyan HvNo ratings yet

- VLSI PapersDocument6 pagesVLSI PapersSandip SolankiNo ratings yet

- Enabling Technologies for High Spectral-efficiency Coherent Optical Communication NetworksFrom EverandEnabling Technologies for High Spectral-efficiency Coherent Optical Communication NetworksNo ratings yet

- Unit V - Decoders To AddersDocument36 pagesUnit V - Decoders To Adders040-NishanthNo ratings yet

- Presentation-048Document13 pagesPresentation-048040-NishanthNo ratings yet

- ARM Introduction-1Document26 pagesARM Introduction-1040-NishanthNo ratings yet

- ARM Thumb Instruction SetDocument21 pagesARM Thumb Instruction Set040-NishanthNo ratings yet

- Esp 32 PPT - CbitDocument16 pagesEsp 32 PPT - Cbit040-NishanthNo ratings yet

- Final Mini Project PresentationDocument20 pagesFinal Mini Project Presentation040-NishanthNo ratings yet

- MP PDFDocument45 pagesMP PDF040-NishanthNo ratings yet

- MINIPROJECTDocument8 pagesMINIPROJECT040-NishanthNo ratings yet

- Diagnosis Banding DepresiDocument9 pagesDiagnosis Banding DepresiHarton MuhammadNo ratings yet

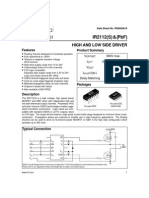

- Ir2112 (S) & (PBF) : High and Low Side DriverDocument17 pagesIr2112 (S) & (PBF) : High and Low Side DriverMugahed DammagNo ratings yet

- GEORGIA - Konstantine KintsurashviliDocument7 pagesGEORGIA - Konstantine KintsurashviliAsian Development BankNo ratings yet

- CH-5,6,7,8 and 9Document87 pagesCH-5,6,7,8 and 9Hirpha FayisaNo ratings yet

- Unit V Unit CommitmentDocument8 pagesUnit V Unit CommitmentDrAurobinda BagNo ratings yet

- Rman DocumentDocument11 pagesRman Documentsantababu100% (2)

- MagentoDocument131 pagesMagentomkfriends007No ratings yet

- 1797 In535 - en P PDFDocument16 pages1797 In535 - en P PDFMancamiaicuruNo ratings yet

- CMS V1.4Document82 pagesCMS V1.4ShtomaNo ratings yet

- EdmDocument12 pagesEdmRajuRamRainNo ratings yet

- KPC3051 - KPC3052: PhotocouplerDocument4 pagesKPC3051 - KPC3052: PhotocouplerFadi NajjarNo ratings yet

- Surveying and Transportation EngineeringDocument34 pagesSurveying and Transportation EngineeringRimar LiguanNo ratings yet

- F22bdocs1m01050 1673359114Document2 pagesF22bdocs1m01050 1673359114Gohar FatimaNo ratings yet

- Unit 5: Central Processing UnitDocument56 pagesUnit 5: Central Processing UnitgobinathNo ratings yet

- MuJava Supporting DocumentationDocument22 pagesMuJava Supporting DocumentationKhushboo KhannaNo ratings yet

- Core Concepts of Accounting Information Systems Simkin 13th Edition Solutions ManualDocument13 pagesCore Concepts of Accounting Information Systems Simkin 13th Edition Solutions ManualElizabethMackxwps100% (44)

- 4-4 Swarm DLDocument28 pages4-4 Swarm DLAnonymous qrKwdO100% (4)

- Penetration Test ReportDocument27 pagesPenetration Test ReportKnowhereDLNo ratings yet

- Aluminum Alloy DatabaseDocument5 pagesAluminum Alloy Databaserizviabbas2012100% (1)

- June 2022 (v3) QP - Paper 3 CAIE Physics IGCSEDocument16 pagesJune 2022 (v3) QP - Paper 3 CAIE Physics IGCSElikhithfantasticNo ratings yet

- DVR ThesisDocument41 pagesDVR ThesisJeffersonGoVaO'Neil100% (1)

- BMS ReportDocument40 pagesBMS Reportsafura aliyaNo ratings yet

- Specifications Airbus Series 2Document4 pagesSpecifications Airbus Series 2flightstudentNo ratings yet

- Arduino Tutorial OV7670 Camera ModuleDocument18 pagesArduino Tutorial OV7670 Camera ModuleKabilesh CmNo ratings yet

- Natural Wormholes As Gravitational LensesDocument4 pagesNatural Wormholes As Gravitational Lensesdiegok64No ratings yet

- Climax and Structure in OdysseyDocument6 pagesClimax and Structure in Odysseygratielageorgianastoica0% (1)