Professional Documents

Culture Documents

C 07 Samp 4

C 07 Samp 4

Uploaded by

Dario DoctorsOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

C 07 Samp 4

C 07 Samp 4

Uploaded by

Dario DoctorsCopyright:

Available Formats

Section 7.

12

VHDL Sequential-Circuit Design Features

545

test_vectors ([CLOCK, X] -> [ .C. , 1] -> [ .C. , 1] -> [ .C. , 1] -> [ .C. , 1] -> [ 0 , 0] -> [ 0 , 1] -> [ .C. , 1] -> [ .C. , 0] -> [ 0 , 0] -> [ 0 , 1] -> [ .C. , 0] -> [ .C. , 1] -> [ 0 , 0] -> [ 0 , 1] -> [ .C. , 0] -> [ .C. , 1] -> [ .C. , 1] ->

do not test (A LASTA) = 10 in state LOOKING, or (A B LASTA) = 100 in state OK. Thus, generating a complete set of test vectors for fault-detection purposes is a process best left to an automatic test-generation program. In Table 7-35, we petered out after writing vectors for the first few states; completing the test vectors is left as an exercise (7.92). Still, on the functional testing side, writing a few vectors to exercise the machines most basic functions can weed out obvious design errors early in the process. More subtle design errors are best detected by a thorough system-level simulation.

7.12 VHDL Sequential-Circuit Design Features

Most of the VHDL features that are needed to support sequential-circuit design, in particular, processes, were already introduced in Section 4.7 and were used in the VHDL sections in Chapter 5. This section introduces just a couple more features and gives simple examples of how they are used. Larger examples appear in the VHDL sections of Chapter 8.

7.12.1 Feedback Sequential Circuits A VHDL process and the simulators event-list mechanism for tracking signal changes form the fundamental basis for handling feedback sequential circuits in VHDL. Remember that feedback sequential circuits may change state in response to input changes, and these state changes are manifested by changes propagating in a. feedback loop until the feedback loop stabilizes. In simulation,

Copyright 1999 by John F. Wakerly Copying Prohibited

DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY

Table 7-35 Test vectors for the combination-lock state machine of Table 7-31.

[ S [.X. [.X. [.X. [ZIP [ZIP [ZIP [ZIP [X0 [X0 [X0 [X0 [X01 [X01 [X01 [X0 [X01 [X011 , , , , , , , , , , , , , , , , , , UNLK, .X. , .X. , .X. , .X. , 0 , 0 , .X. , .X. , 0 , 0 , .X. , .X. , 0 , 0 , .X. , .X. , .X. , HINT]) .X. ]; .X. ]; .X. ]; .X. ]; 1 ]; 0 ]; .X. ]; .X. ]; 0 ]; 1 ]; .X. ]; .X. ]; 0 ]; 1 ]; .X. ]; .X. ]; .X. ]; " " " " " " " " " " " " " " " " " Since no reset input, apply a 'synchronizing sequence' to reach a known starting state Test Mealy outputs for both values of X Test ZIP-->ZIP (X==1) and ZIP-->X0 (X==0) Test Mealy outputs for both values of X Test X0-->X0 (X==0) and X0-->X01 (X==1) Test Mealy outputs for both values of X Test X01-->X0 (X==0) Get back to X01 Test X01-->X011 (X==1)

546

Chapter 7

Sequential Logic Design Principles

DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY

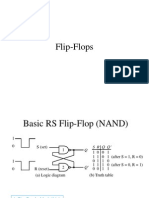

Table 7-36 Dataflow VHDL for an S-R latch.

library IEEE; use IEEE.std_logic_1164.all; entity Vsrlatch is port (S, R: in STD_LOGIC; Q, QN: buffer STD_LOGIC ); end Vsrlatch; architecture Vsrlatch_arch of Vsrlatch is begin QN <= S nor Q; Q <= R nor QN; end Vsrlatch_arch;

this is manifested by the simulator putting signal changes on the event list and scheduling processes to re-run in delta time and propagate these signal changes until no more signal changes are scheduled. Table 7-36 is a VHDL program for an S-R latch. The architecture contains two concurrent assignment statements, each of which gives rise to a process as discussed in Section 4.7.9. These processes interact to create the simple latching behavior of an S-R latch. The VHDL simulation is faithful enough to handle the case where both S and R are asserted simultaneously. The most interesting result in simulation occurs if you negate S and R simultaneously. Recall from the box on page 440 that a real S-R latch may oscillate or go into a metastable state in this situation. The simulation will potentially loop forever as each execution of one assignment statement triggers another execution of the other. After some number of repetitions, a well designed simulator will discover the problemdelta time keeps advancing while simulated time does notand halt the simulation.

WHAT DO U WANT?

It would be nice if the S-R-latch model in Table 7-36 produced a 'U' output whenever S and R were negated simultaneously, but its not that good. However, the language is powerful enough that experienced VHDL designers can easily write a model with that behavior. Such a model would make use of VHDLs time-modeling facilities, which we havent discussed, to model the latchs recovery time (see box on page 441) and force a 'U' output if a second input change occurs too soon. Its even possible to model a maximum assumed metastability resolution time in this way. Note that if a circuit has the possibility of entering a metastable state, theres no guarantee that the simulation will detect it, especially in larger designs. The best way to avoid metastability problems in a system design is to clearly identify and protect its asynchronous boundaries, as discussed in Section 8.9.

Copyright 1999 by John F. Wakerly

Copying Prohibited

Section 7.12

VHDL Sequential-Circuit Design Features

547

library IEEE; use IEEE.std_logic_1164.all;

entity VposDff is port (CLK, CLR, D: in STD_LOGIC; Q, QN: out STD_LOGIC ); end VposDff;

architecture VposDff_arch of VposDff is begin process (CLK, CLR) begin if CLR='1' then Q <= '0'; QN <= '1'; elsif CLK'event and CLK='1' then Q <= D; QN <= not D; end if; end process; end VposDff_arch;

7.12.2 Clocked Circuits In practice, the majority of digital designs that are modeled using VHDL are clocked, synchronous systems using edge-triggered flip-flops. In addition to what weve already learned about VHDL, theres just one more feature needed to describe edge-triggered behavior. The event attribute can be attached to a signal name to yield a value of type boolean that is true if an event on the signal caused the encompassing process to run in the current simulation cycle, and false otherwise. Using the event attribute, we can model the behavior of a positive-edge triggered D flip-flop with asynchronous clear as shown in Table 7-37. Here, the asynchronous clear input CLR overrides any behavior on the clock input CLK, and is therefore checked first, in the if clause. If CLR is negated, then the elsif clause is checked, and its statements are executed on the rising edge of CLK. Note that CLK'event is true for any change on CLK, and CLK='1' is checked to limit triggering to just the rising edge of CLK. There are many other ways to construct processes or statements with edge-triggered behavior; Table 7-38 shows two more ways to describe a D flip-flop (without a CLR input). In the test bench for a clocked circuit, one of things you need to do is to generate a system clock signal. This can be done quite easily with a loop inside a process, as shown in Table 7-39 for a 100 MHz clock with a 60% duty cycle.

process wait until CLK'event and CLK='1'; Q <= D; end process;

Q <= D when CLK'event and CLK='1' else Q;

DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY

event attribute

Table 7-37 Behavioral VHDL for a positive-edgetriggered D flip-flop.

Table 7-38 Two more ways to describe a positiveedge-triggered D flip-flop.

Copyright 1999 by John F. Wakerly

Copying Prohibited

548

Chapter 7

Sequential Logic Design Principles

Table 7-39 Clock process within a test bench.

DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY

SYNTHESIS STUFF You may be wondering, how does a synthesis tool convert the edgetriggered behavior described in Table 7-37 or 7-38 into an efficient flip-flop realization? Most tools recognize only a few predetermined ways of expressing edge-triggered behavior, and map those into predetermined flipflop components in the target technology. The Synopsis synthesis engine used in the Xilinx Foundation Series 1.5 software recognizes the CLK'event and CLK='1' expression that we use in this book. Even with that as a given, VHDL has many different ways of expressing the same functionality, as we showed in Table 7-38. Peter Ashenden, author of The Designers Guide to VHDL (Morgan Kaufmann, 1996), ran these statements and one other, with some modification, through several different synthesis tools. Only one of them was able to synthesize three out of the four forms; most could handle only two. So, you need to follow the method that is prescribed by the tool you use.

architecture TB_arch of TB is signal MCLK: STD_LOGIC; signal ... -- Declare other input and output signals process -- Clock generator begin MCLK <= 1; -- Start at 1 at time 0 loop MCLK <= 0 after 6 ns; MCLK <= 1 after 4 ns; end loop; end process;

process -- Generate the rest of the input stimulii , check outputs begin ... end;

References

The problem of metastability has been around for a long time. Greek philosophers wrote about the problem of indecision thousands of years ago. A group of modern philosophers named Devo sang about metastability in the title song of their Freedom of Choice album. And the U.S. Congress still cant decide how to save Social Security. Scan capability was first deployed in latches, not flip-flops, in IBM IC designs decades ago. Edward J. McCluskey has a very good discussion of this and other scan methods in Logic Design Principles (Prentice Hall, 1986).

Copyright 1999 by John F. Wakerly Copying Prohibited

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5821)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (898)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (403)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Clock Domain Crossing: Issues and Solutions: Udit Kumar, DCG Sakshi Gupta, TRND Bhanu Prakash, DCGDocument53 pagesClock Domain Crossing: Issues and Solutions: Udit Kumar, DCG Sakshi Gupta, TRND Bhanu Prakash, DCGSiddharth Sabharwal60% (5)

- Metastability and SynchronizationDocument48 pagesMetastability and SynchronizationDollaRaiNo ratings yet

- Multi Clock DesignDocument37 pagesMulti Clock DesignRoc Kim Sí ĐiểuNo ratings yet

- TN005 Reset Synchronization v00Document6 pagesTN005 Reset Synchronization v00Brahmam MadamanchiNo ratings yet

- STA FinalDocument66 pagesSTA FinalgauravkshriNo ratings yet

- CharFlo-Memory Compiler Tech Rev10.3-2010JuneDocument33 pagesCharFlo-Memory Compiler Tech Rev10.3-2010Junevikramkolanu100% (1)

- Sva CDC Paper Dvcon2006Document6 pagesSva CDC Paper Dvcon2006vikkisachdevaNo ratings yet

- VLSI Lab Viva Question With AnswersDocument15 pagesVLSI Lab Viva Question With Answersaamreen81833% (3)

- Chapter 3 KeyDocument48 pagesChapter 3 Keyrktiwary256034100% (2)

- Meridian White Paper 2008Document20 pagesMeridian White Paper 2008avdhesh7No ratings yet

- What Is MetastabilityDocument4 pagesWhat Is MetastabilityRakesh KumarNo ratings yet

- A Technique To Remove Glitches in Physical Design StageDocument120 pagesA Technique To Remove Glitches in Physical Design Stageసుశీల్ శరత్No ratings yet

- I. Blocking vs. Nonblocking AssignmentsDocument24 pagesI. Blocking vs. Nonblocking AssignmentsPrashanth AraliNo ratings yet

- Timing Issues in FPGA Synchronous Circuit Design: ECE 428 Programmable ASIC DesignDocument33 pagesTiming Issues in FPGA Synchronous Circuit Design: ECE 428 Programmable ASIC DesignVarun KondagunturiNo ratings yet

- Data Transfer Between Asynchronous Clock DomainsDocument10 pagesData Transfer Between Asynchronous Clock DomainsShiva ShankarNo ratings yet

- CDC by Ajaysimha - VlsiDocument14 pagesCDC by Ajaysimha - VlsiPriyanka GollapallyNo ratings yet

- Litterick CDC SlidesDocument16 pagesLitterick CDC SlidessheikmydeenNo ratings yet

- CDC UserDocument493 pagesCDC Userchhari450% (2)

- Metastable Recovery in Virtex-Ii Pro FpgasDocument5 pagesMetastable Recovery in Virtex-Ii Pro FpgasaaantennaNo ratings yet

- Timing in Digital CircuitsDocument18 pagesTiming in Digital Circuitsshrish9999No ratings yet

- Challenges in Verification of Clock DomainsDocument8 pagesChallenges in Verification of Clock DomainsKi KiNo ratings yet

- Verification OverviewDocument123 pagesVerification OverviewSamNo ratings yet

- 1 MetastabilityDocument58 pages1 Metastability0106062007No ratings yet

- 6.004 Computation Structures: Mit OpencoursewareDocument8 pages6.004 Computation Structures: Mit OpencoursewareravindarsinghNo ratings yet

- Topic 6 - Clocking & Met A StabilityDocument9 pagesTopic 6 - Clocking & Met A Stabilityanish1988100% (1)

- Meta StabilityDocument16 pagesMeta StabilitySahil SharmaNo ratings yet

- CDCDocument38 pagesCDCRamakrishnaRao SoogooriNo ratings yet

- Flip FlopsDocument25 pagesFlip FlopsNagul MeeraNo ratings yet

- Digital Logic ReviewDocument56 pagesDigital Logic ReviewLamija NukicNo ratings yet

- Structural FunctionalDocument37 pagesStructural Functionalgaru1991No ratings yet