Professional Documents

Culture Documents

D ft1208dj ft1208mj ft1204mj ft1204dj ft1208bj ft1208nj ft1204bj T

D ft1208dj ft1208mj ft1204mj ft1204dj ft1208bj ft1208nj ft1204bj T

Uploaded by

MindSet MarcosOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

D ft1208dj ft1208mj ft1204mj ft1204dj ft1208bj ft1208nj ft1204bj T

D ft1208dj ft1208mj ft1204mj ft1204dj ft1208bj ft1208nj ft1204bj T

Uploaded by

MindSet MarcosCopyright:

Available Formats

FT12...

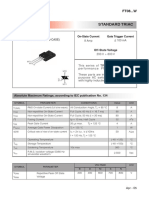

INSULATED LOGIC LEVEL TRIAC

On-State Current Gate Trigger Current

12 Amp £ 10 mA (08)

INSULATED TO-220AB £ 5 mA (04)

Off-State Voltage

200 V ÷ 800 V

FEATURES

Glass/passivated die junctions

Provides voltage insulated tab (rated at 2500V RMS)

Medium current Triac

Low thermal resistance

High surge current capability

Low forward voltage drop

1

23 Solder dip 260ºC, 10s

Component in accordance to RoHS 2011/65/EU

and WEEE 2002/96/EC

Meets MSL level 3, per J-STD-020, LF maximum

peak of 260º C

Certified compliance of UL 1557 Standard for Electrically

Isolated Semiconductors. Fille reference E320541, Vol. 3

MECHANICAL DATA

MT1 (1) Case: INSULATED TO-220AB. Epoxy meets UL 94V-0

flammability rating.

G (3)

Polarity: As marked on the body.

Terminals : Matte tin plated leads, solderable per

MIL-STD-750 Method 2026, J-STD-002 and JESD22-B102.

Consumer grade, meets JESD 201 class 1A whisker test.

TYPICAL APPLICATIONS

MT2 (2)

Logic level versions are designed to interface directly

with low power drivers such as microcontrollers.

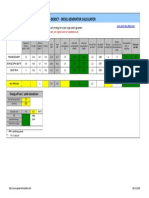

Maximun Ratings and Electrical Characteristics at 25°C

SYMBOL PARAMETER CONDITIONS Value Unit

IT(RMS) RMS On-state Current (full sine wave) All Conduction Angle, Tc = 90 °C 12 A

ITSM Non-repetitive On-State Current Full Cycle, 60 Hz (t = 16.7 ms) 125 A

ITSM Non-repetitive On-State Current Full Cycle, 50 Hz (t = 20 ms) 120 A

2

It Fusing Current tp = 10 ms, Half Cycle 72 A 2s

IGM Peak Gate Current 20 µs max. Tj = 125 °C 4 A

PG(AV) Average Gate Power Dissipation Tj = 125 °C 1 W

dI/dt Critical rate of rise of on-state current IG = 2x IGT, tr £100ns 50 A/µs

f = 120 Hz, Tj = 125 °C

Tj Operating Temperature (-40 +125) °C

Tstg Storage Temperature (-40 +125) °C

Tsld Soldering Temperature 10s max 260 °C

Viso R.M.S. isolation voltage 50/60 Hz 2.500 Vac

sinusoidal waveform

VOLTAGE Unit

SYMBOL PARAMETER

B D M N

VDRM/VRRM Repetitive Peak Off State Voltage 200 400 600 800 V

www.fagorelectronica.com Version: Oct-12

Document Name: ft12jll Page Number: 1/6

FT12...J

INSULATED LOGIC LEVEL TRIAC

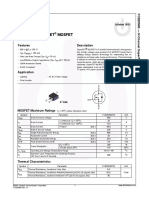

Electrical Characteristics at Tamb = 25 °C

SENSITIVITY

SYMBOL PARAMETER CONDITIONS Quadrant Unit

04 08

IGT (1) Gate Trigger Current VD = 12 VDC, RL = 33W, Tj = 25 °C Q1÷Q3 MAX 5 10 mA

Q4 MAX - - mA

VGT Gate Trigger Voltage VD = 12 VDC, RL = 33W, Tj = 25 °C Q1÷Q3 MAX 1.3 1.3 V

Q1÷Q4 MAX - - V

VGD Gate Non Trigger Voltage VD = VDRM, RL = 3.3 KW, Tj = 125 °C Q1÷Q3 MIN 0.2 0.2 V

Q1÷Q4 MIN - - V

(2)

IH Holding Current IT = 100 mA, Gate open, Tj = 25 °C MAX 15 mA

IL Latching Current IG = 1.2 IGT, Tj = 25 °C Q1,Q3 MAX 10 25 mA

Q2 MAX 15 30 mA

(2)

dV/dt Critical Rate of Voltage Rise VD = 0.67 x VDRM, Gate open MIN 20 40 V/µs

Tj = 125 °C

(2)

(dl/dt)c Critical Rate of Current Rise (dv/dt)c = 0.1 V/µs Tj = 125 °C MIN 3.5 6.5 A/ms

(dv/dt)c = 10 V/µs Tj = 125 °C MIN 1 2.9 A/ms

VTM (2) On-state Voltage IT = 17 Amp, tp = 380 µs, Tj = 25 °C MAX 1.55 V

(2)

Vt (o) Threshold Voltage Tj = 125 °C MAX 0.85 V

(2)

rd Dynamic resistance Tj = 125 °C MAX 35 mW

IDRM/IRRM Off-State Leakage Current VD = VDRM, Tj = 125 °C MAX 1 mA

VR = VRRM, Tj = 25 °C MAX 5 µA

Rth(j-c) Thermal Resistance for AC 360° conduction angle 2.3 °C/W

Junction-Case

Rth(j-a) Thermal Resistance

Junction-Ambient 60 °C/W

(1) Minimum IGT is guaranted at 5% of IGT max.

(2) For either polarity of electrode MT2 voltage with reference to electrode MT1.

Part Number Information

F T 12 08 B J 00 TU

FAGOR PACKAGING

FORMING

TRIAC

CASE

VOLTAGE

CURRENT

SENSITIVITY

www.fagorelectronica.com Version: Oct-12

Document Name: ft12jll Page Number: 2/6

FT12...J

INSULATED LOGIC LEVEL TRIAC

Ordering information

PREFERRED P/N PACKAGE CODE DELIVERY MODE BASE QUANTITY UNIT WEIGHT (g)

FT1208MJ 00TU TU TUBE 1000 2.30

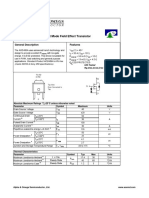

Package Outline Dimensions: (mm) INSULATED TO-220AB

Optional with chamfer

DIMENSIONS

REF. Milimeters

Min. Max.

A

øP A 4.32 4.62

E A1 A1 1.21 1.29

A2 2.40 2.70

b 0.80 0.83

Q

H1 b2 1.40 --

Marking code

Format type c 0.42 0.48

D

MC Year code D 15.5 15.68

D1 XXXJ 9.26 9.42

D1

WWY E 10.08 10.24

Test sort name L1 e 2.54 2.54

Week code e1 5.08 5.08

b2 L H1 6.24 6.26

L 12.81 13.81

L1 3.28 4.17

P 3.70 3.80

b c Q 2.75 2.85

e A2

e1

Mounting Torque 0.8 N.m

www.fagorelectronica.com Version: Oct-12

Document Name: ft12jll Page Number: 3/6

FT12...J

INSULATED LOGIC LEVEL TRIAC

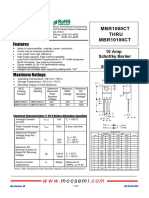

Ratings and Characteristics (Ta 25 ºC unless otherwise noted)

Fig. 1: Maximum power dissipation versus Fig. 2: RMS on-state current versus case

RMS on-state current (full cycle). temperature (full cycle).

P (W) IT(RMS)(A)

16 14

13

14 12

11

12

10

10 9

8

8 7

6

6 5

4

4

3

2 2

1

IT(RMS)(A) Tc (°C)

0 0

0 1 2 3 4 5 6 7 8 9 10 11 12 0 25 50 75 100 125

Fig. 3: Relative variation of thermal Fig. 4: On-state characteristics (maximum

impedance versus pulse duration. values)

K=[Zth / Rth] ITM (A)

1E+0 200

Zth(j-c)

100

Tj max

1E-1

Zth(j-a)

10 Tj = 25 °C

Tj max

Vto = 0.85 V

Rd = 35 mW

tp (s) VTM (V)

1E-2 1

1E-3 1E-2 1E-1 1E+0 1E+1 1E+2 5E+2 0.5 1.0 1.5 2 2.5 3 3.5 4 4.5 5

Fig. 6: Non repetitive surge peak on-state

Fig. 5: Surge peak on-state current versus current for a sinusoidal pulse with width:

number of cycles tp < 20 ms, and corresponding value of I t.

2

2 2

I TSM (A) ITSM(A). I t (A s)

140 1000

130 Tj initial=25 °C

120 t=20ms ITSM

One cycle

100

90

Non repetitive

80 Tj initial = 25 °C

2

70 It

100

60

50

40

30

20

10

Number of cycles tp(ms)

0 10

1 10 100 1000 1 10 20

www.fagorelectronica.com Version: Oct-12

Document Name: ft12jll Page Number: 4/6

FT12...J

INSULATED LOGIC LEVEL TRIAC

Ratings and Characteristics (Ta 25 ºC unless otherwise noted)

Fig. 7: Relative variation of gate trigger Fig. 8: Relative variation of critical rate of

current, holding current and latching versus decrease of main current versus junction

junction temperature (typical values) temperature

IGT,IH,IL[Tj]/IGT,IH,IL.[Tj=25°C] (dI/dt)c [Tj]/(dI/dc)c [Tj specified]

2.5 6

5

2.0

IGT

4

1.5

3

IH&IL

1.0

2

0.5

1

Tj(ºC) Tj(°C)

0 0

-40 -20 0 20 40 60 80 100120140 0 25 50 75 100 125

Fig. 9: Relative variation of critical rate

of decrease of main current versus

(dV/dt)c (typical values).

2.0

1.8

1.6

1.4

1.2

1.0

0.8

0.6 (dV/dt)c (V/µS)

0.4

0.1 1.0 10.0 100.0

www.fagorelectronica.com Version: Oct-12

Document Name: ft12jll Page Number: 5/6

FT12....J

INSULATED LOGIC LEVEL TRIAC

Disclaimer

All product, product specifications and data are subject to change without notice to improve reliability,

function or design or otherwise.

Fagor Electrónica, S.Coop., its affiliates, agents, and employees, and all persons acting on its or their

behalf (collectively, "Fagor"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained

in any datasheet or in any other disclosure relating to any product.

Fagor makes no warranty, representation or guarantee regarding the suitability of the products for any particular

purpose or the continuing production of any product. To the maximum extent permitted by applicable law,

Fagor disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all

liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied

warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Fagor's knowledge

of typical requirements that are often placed on Fagor products in generic applications. Such statements are not

binding statements about the suitability of products for a particular application. It is the customer's responsibility

to validate that a particular product with the properties described in the product specification is suitable for use in a

particular application. Parameters provided in datasheets and/or specifications may vary in different applications

and performance may vary over time. All operating parameters, including typical parameters, must be validated

for each customer application by the customer's technical experts. Product specifications do not expand or

otherwise modify Fagor's terms and conditions of purchase, including but nos limited to the warranty expressed

therein.

Except as expressly indicated in writing. Fagor products are not designed for use in medical, life-saving, or

life-sustaining applications or for any other application in which the failure of the Fagor product could result in

personal injury or death. Customers using or selling Fagor products not expressly indicated for use in such

applications do so at their own risk and agree to fully indemnify and hold Fagor and its distributors harmless from

and against any and all claims, liabilities, expenses and damages arising or resulting in connection with such use

or sale, including attomeys fees, even if such claim alleges that Fagor or its distributor was negligent regarding

the design or manufacture of the part. Please contact authorized Fagor personnel to obtain written terms and

conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this

document or by any conduct of Fagor, Product names and markings noted herein may be trademarks of their

respective owners.

www.fagorelectronica.com Version: Oct-12

Document Name: ft12jll Page Number: 6/6

You might also like

- Linde R14 WL - 115 - EN - 0609Document358 pagesLinde R14 WL - 115 - EN - 0609cristiancerda82% (11)

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Digital Electronics, Volume 1 Combinational Logic Circuits by Tertulien Ndjountche (Z-Lib - Org) - 178-190Document13 pagesDigital Electronics, Volume 1 Combinational Logic Circuits by Tertulien Ndjountche (Z-Lib - Org) - 178-190Shendy ArsellaNo ratings yet

- Fagor FT0109MN00RB DatasheetDocument6 pagesFagor FT0109MN00RB DatasheetJose BenavidesNo ratings yet

- Sensitive Gate SCR: 800 V 12 Amp 200 ADocument7 pagesSensitive Gate SCR: 800 V 12 Amp 200 AfrancoNo ratings yet

- Bta 12 6008 Impressora SansungDocument6 pagesBta 12 6008 Impressora SansungLuciano Francisco Dos SantosNo ratings yet

- FT12 WSTDocument4 pagesFT12 WSTJavier BelizanNo ratings yet

- Media 3323329Document6 pagesMedia 3323329Daniel MesiNo ratings yet

- WFF13N50 WinsemisemiconductorDocument8 pagesWFF13N50 WinsemisemiconductorHamilton Jorge SilvaNo ratings yet

- Datasheet SFP50N06 PDFDocument7 pagesDatasheet SFP50N06 PDFAdeniltonNo ratings yet

- SMAJ5.0 - Inyector Poe 48-24 Datasheetz PDFDocument4 pagesSMAJ5.0 - Inyector Poe 48-24 Datasheetz PDFAntoni MonteroNo ratings yet

- 20N60M2EP Mark STP20N60M2-EP 600V 13A FETDocument14 pages20N60M2EP Mark STP20N60M2-EP 600V 13A FETRuslanNo ratings yet

- Bta06 600BDocument7 pagesBta06 600BMikhaelA.RodriguezNo ratings yet

- Standard TriacDocument4 pagesStandard TriacHector Alberto SanchezNo ratings yet

- Fcb20N60: N-Channel Superfet MosfetDocument9 pagesFcb20N60: N-Channel Superfet MosfetEo GpNo ratings yet

- SBL2030PT, SBL2040PT: Vishay General SemiconductorDocument4 pagesSBL2030PT, SBL2040PT: Vishay General SemiconductortallertecuNo ratings yet

- IRFS630A - N CH, Power MOSFET 200V, 6.5A 25ºC, 4.1A 100ºC, 4v Vgs (TH)Document8 pagesIRFS630A - N CH, Power MOSFET 200V, 6.5A 25ºC, 4.1A 100ºC, 4v Vgs (TH)LangllyNo ratings yet

- DC Components Co., LTD.: SK22 Thru SK28Document2 pagesDC Components Co., LTD.: SK22 Thru SK28serrano.flia.coNo ratings yet

- STB 8 NM 60 DDocument13 pagesSTB 8 NM 60 DErkanNo ratings yet

- Stp8Nc50 - Stp8Nc50Fp Stb8Nc50-1: N-Channel 500V - 0.7 - 8A To-220/To-220Fp/I2Pak Powermesh Ii MosfetDocument11 pagesStp8Nc50 - Stp8Nc50Fp Stb8Nc50-1: N-Channel 500V - 0.7 - 8A To-220/To-220Fp/I2Pak Powermesh Ii MosfetAbraham Esteban DominguezNo ratings yet

- SB160 Schottky Diode 60V 1a PDFDocument3 pagesSB160 Schottky Diode 60V 1a PDFdemostenessNo ratings yet

- STTH212: DescriptionDocument11 pagesSTTH212: DescriptionPablo Gonzalez RivielloNo ratings yet

- Surface Mount - 600W SMA6J SeriesDocument6 pagesSurface Mount - 600W SMA6J Seriessalesiano05No ratings yet

- Littelfuse Thyristor BTB12 600BW3 D Datasheet pdf-1372438Document7 pagesLittelfuse Thyristor BTB12 600BW3 D Datasheet pdf-1372438asperfudNo ratings yet

- Stp80Nf55-06 - Stp80Nf55-06Fp Stb80Nf55-06-1: N-Channel 55V - 0.005 - 80A To-220/To-220Fp/I Pak Stripfet Power MosfetDocument10 pagesStp80Nf55-06 - Stp80Nf55-06Fp Stb80Nf55-06-1: N-Channel 55V - 0.005 - 80A To-220/To-220Fp/I Pak Stripfet Power MosfetCelso SáNo ratings yet

- BT152 PhilipsSemiconductorsDocument8 pagesBT152 PhilipsSemiconductorsDiego RicardoNo ratings yet

- MDF10N60G 1Document6 pagesMDF10N60G 1samvick103No ratings yet

- sk13 DiodeDocument3 pagessk13 DiodeДрагиша Небитни ТрифуновићNo ratings yet

- SB120 Thru SB160: Vishay General SemiconductorDocument4 pagesSB120 Thru SB160: Vishay General SemiconductorrezaNo ratings yet

- Ug2A, Ug2B, Ug2C, Ug2D: Vishay General SemiconductorDocument5 pagesUg2A, Ug2B, Ug2C, Ug2D: Vishay General SemiconductorKhan SahibNo ratings yet

- RL204 PDFDocument4 pagesRL204 PDFFederico TorreNo ratings yet

- P6SMB300CADocument6 pagesP6SMB300CAMuzaffer NizamNo ratings yet

- Stps 10120 CDocument9 pagesStps 10120 CLEWIS RODRIGUEZNo ratings yet

- Data SheetDocument5 pagesData SheetLucas QuarchioniNo ratings yet

- Uufggf 5 UDocument7 pagesUufggf 5 UYousef KassimNo ratings yet

- Fda 69 N 25Document8 pagesFda 69 N 25Jose Altamiranda GarcesNo ratings yet

- SK32 - SK36: Surface Mount Schottky Barrier RectifierDocument2 pagesSK32 - SK36: Surface Mount Schottky Barrier RectifierAnonymous 50FYYM2No ratings yet

- HX50N06 Heatsink Planar N-Channel Power MOSFETDocument6 pagesHX50N06 Heatsink Planar N-Channel Power MOSFETDaniel OrtizNo ratings yet

- MDF11N60: N-Channel MOSFET 600V, 11A, 0.55Document6 pagesMDF11N60: N-Channel MOSFET 600V, 11A, 0.55Ariel MercochaNo ratings yet

- 3N80Document6 pages3N80hectorsevillaNo ratings yet

- ss12t3, ss14t3 OnDocument7 pagesss12t3, ss14t3 Onadian herawanNo ratings yet

- STP20NM60FDDocument12 pagesSTP20NM60FDinsptrafaelNo ratings yet

- Surface Mount - 400W SMAJ SeriesDocument7 pagesSurface Mount - 400W SMAJ Seriesgonzalo2205No ratings yet

- Data SheetDocument2 pagesData Sheetalain rougetNo ratings yet

- High Commutation Triac: TO220-ABDocument5 pagesHigh Commutation Triac: TO220-ABFelipe AcelasNo ratings yet

- MDP2N60/MDF2N60: N-Channel MOSFET 600V, 2.0A, 4.5Document8 pagesMDP2N60/MDF2N60: N-Channel MOSFET 600V, 2.0A, 4.5Erroz RosadiNo ratings yet

- Datasheet - HK p9nc60 41128 PDFDocument9 pagesDatasheet - HK p9nc60 41128 PDFJacson FagundesNo ratings yet

- Stp6Nk90Z - Stp6Nk90Zfp STB6NK90Z - STW7NK90ZDocument14 pagesStp6Nk90Z - Stp6Nk90Zfp STB6NK90Z - STW7NK90ZjoelpalzaNo ratings yet

- 1.0 Amp. at 40ºC 600 V To 1000 V: Current VoltageDocument4 pages1.0 Amp. at 40ºC 600 V To 1000 V: Current Voltagepopescu danielaNo ratings yet

- Irf 634 BDocument8 pagesIrf 634 BAhmed ShagidullinNo ratings yet

- Ultra Low V 0.43 V at I 5 A: Vishay General SemiconductorDocument6 pagesUltra Low V 0.43 V at I 5 A: Vishay General SemiconductorInés DominguezNo ratings yet

- S2a Series - L1701-1113146Document7 pagesS2a Series - L1701-1113146Joko MulyadiNo ratings yet

- Ft0107ma PDFDocument4 pagesFt0107ma PDFAnatoly WolkoffNo ratings yet

- TRIAC FT08 - FagorDocument5 pagesTRIAC FT08 - FagorAdelmo DarioNo ratings yet

- Surface Mount Triac: SOT223 (Plastic)Document4 pagesSurface Mount Triac: SOT223 (Plastic)Mike BrdnNo ratings yet

- 28N50F FairchildSemiconductorDocument8 pages28N50F FairchildSemiconductorgabosakrNo ratings yet

- Datasheet PDFDocument10 pagesDatasheet PDFShikamaru MendozaNo ratings yet

- P6NK90ZFP STMicroelectronicsDocument12 pagesP6NK90ZFP STMicroelectronics15265562No ratings yet

- BT139Document6 pagesBT139BryanTipánNo ratings yet

- MAC223A6, MAC223A8, MAC223A10 Triacs: Silicon Bidirectional ThyristorsDocument8 pagesMAC223A6, MAC223A8, MAC223A10 Triacs: Silicon Bidirectional ThyristorsrobystwnNo ratings yet

- MCR100W 10M 0-2902672Document12 pagesMCR100W 10M 0-2902672chawkigenieNo ratings yet

- Lenoxx TV7114 STH239-F2 V11214Document11 pagesLenoxx TV7114 STH239-F2 V11214MindSet MarcosNo ratings yet

- Data Sheet: BTA204S Series D, E and F BTA204M Series D, E and FDocument8 pagesData Sheet: BTA204S Series D, E and F BTA204M Series D, E and FMindSet MarcosNo ratings yet

- R1 IF SMDDocument2 pagesR1 IF SMDMindSet MarcosNo ratings yet

- Data SheetDocument5 pagesData SheetMindSet MarcosNo ratings yet

- STM 4472Document7 pagesSTM 4472MindSet MarcosNo ratings yet

- Aula 1 Docs Vs 8eth06fppbf DatasheetDocument9 pagesAula 1 Docs Vs 8eth06fppbf DatasheetMindSet MarcosNo ratings yet

- T-CON Samsung LN26A330-1Document2 pagesT-CON Samsung LN26A330-1MindSet MarcosNo ratings yet

- MGD623SDocument2 pagesMGD623SMindSet MarcosNo ratings yet

- DatasheetDocument15 pagesDatasheetMindSet MarcosNo ratings yet

- MMS9014 L TPDocument2 pagesMMS9014 L TPMindSet MarcosNo ratings yet

- Features 10N65 650V N-Channel MOSFET: TO-220F PackageDocument7 pagesFeatures 10N65 650V N-Channel MOSFET: TO-220F PackageMindSet MarcosNo ratings yet

- 24AA02 24LC02B 24FC02 2K I2C Serial EEPROM 2000170-2577009Document52 pages24AA02 24LC02B 24FC02 2K I2C Serial EEPROM 2000170-2577009MindSet MarcosNo ratings yet

- Utc3842 YouwangelectronicsDocument9 pagesUtc3842 YouwangelectronicsMindSet MarcosNo ratings yet

- MBR1080CTDocument3 pagesMBR1080CTMindSet MarcosNo ratings yet

- 5 GHZ Airmax Ac Cpe With Wi-Fi Management RadioDocument24 pages5 GHZ Airmax Ac Cpe With Wi-Fi Management RadioMindSet MarcosNo ratings yet

- Philips+TPM18 7L+LADocument59 pagesPhilips+TPM18 7L+LAMindSet MarcosNo ratings yet

- Up Down Left Right L1 L2 Triangle Fork Square Circle R1 R2: KC2616 Wireless Gamepad TXDocument3 pagesUp Down Left Right L1 L2 Triangle Fork Square Circle R1 R2: KC2616 Wireless Gamepad TXMindSet MarcosNo ratings yet

- Schottky Rectifier 60 Amp: Bulletin PD-20635 Rev. A 12/01Document6 pagesSchottky Rectifier 60 Amp: Bulletin PD-20635 Rev. A 12/01MindSet MarcosNo ratings yet

- 6c SMDDocument4 pages6c SMDMindSet MarcosNo ratings yet

- 2N3055 NPN Silicon Darlingtons: Absolute Maximum RatingsDocument3 pages2N3055 NPN Silicon Darlingtons: Absolute Maximum RatingsMindSet MarcosNo ratings yet

- A78Rxxpic: DescriptionDocument7 pagesA78Rxxpic: DescriptionMindSet MarcosNo ratings yet

- Eetop - CN 100 Power Tips For FPGA Designers Stavinov EvgeniDocument409 pagesEetop - CN 100 Power Tips For FPGA Designers Stavinov EvgeniywkaiNo ratings yet

- Ds180 7series OverviewDocument18 pagesDs180 7series OverviewRakesh KhannaNo ratings yet

- Basic Principles of To ZXMSG 5200Document57 pagesBasic Principles of To ZXMSG 5200abtNo ratings yet

- Adjustable Power Supply Circuit Using LM317 Voltage Regulator ICDocument4 pagesAdjustable Power Supply Circuit Using LM317 Voltage Regulator ICsud100% (1)

- Communication Systems EE 385 6 Semester 2012 EE 385, 6 Semester, 2012Document21 pagesCommunication Systems EE 385 6 Semester 2012 EE 385, 6 Semester, 2012Waleed RazaNo ratings yet

- C264 Documentation: CPU275 (CPU Type 4)Document12 pagesC264 Documentation: CPU275 (CPU Type 4)lucasNo ratings yet

- Powerful Open Software Key FeaturesDocument2 pagesPowerful Open Software Key FeaturesCristian SmarandacheNo ratings yet

- Ieee Papers For DownloadDocument2 pagesIeee Papers For DownloadSuresh KumarNo ratings yet

- Calculator Energy Genset Diesel Electric GeneratorDocument1 pageCalculator Energy Genset Diesel Electric GeneratorarunNo ratings yet

- CS-OHS-32 - Maintenance and Testing of Entity Works, Electrical Installations and Equipment (07 15) - CS Energy RegisteredDocument15 pagesCS-OHS-32 - Maintenance and Testing of Entity Works, Electrical Installations and Equipment (07 15) - CS Energy RegisteredRana ImtiazNo ratings yet

- Manual 3AP2 FI 420kV PDFDocument122 pagesManual 3AP2 FI 420kV PDFbesaret100% (1)

- Lab ECM346 LEVEL 0 Electricity Supply - Three Phase SystemDocument3 pagesLab ECM346 LEVEL 0 Electricity Supply - Three Phase SystemWahedaNo ratings yet

- Digiflex KMTDocument58 pagesDigiflex KMTsarafciger12350% (2)

- DSD Lab 10Document8 pagesDSD Lab 10Shayan AmjadNo ratings yet

- Lesson Plan Digital ElectronicsDocument3 pagesLesson Plan Digital ElectronicsManjula sNo ratings yet

- TOKS Catalouge PDFDocument56 pagesTOKS Catalouge PDFMuskaan AroraNo ratings yet

- Wave Proagation in Waveguides - Nptel MaterialDocument15 pagesWave Proagation in Waveguides - Nptel MaterialSANTHIPRIYANo ratings yet

- System For Optimising Pump Station Control - Part II: World Pumps July 2004Document4 pagesSystem For Optimising Pump Station Control - Part II: World Pumps July 2004Rahmi ArslanNo ratings yet

- ISEI 2010-Diagnostics Techniques of Power TransformersDocument80 pagesISEI 2010-Diagnostics Techniques of Power TransformersAli Naderian100% (3)

- Riscv InstructionsDocument1 pageRiscv Instructionsturple100% (1)

- PF 520 530 FS C2026MFP C2126MFP PL UkDocument8 pagesPF 520 530 FS C2026MFP C2126MFP PL Ukradutranzy1No ratings yet

- Features: Boya Microelectronics Memory SeriesDocument46 pagesFeatures: Boya Microelectronics Memory Seriesmirage0706No ratings yet

- Class 4 ComputerDocument3 pagesClass 4 ComputerumeshNo ratings yet

- Electron Microscopy: by Dr. Kaustab GhoshDocument9 pagesElectron Microscopy: by Dr. Kaustab GhoshNehal Aswani 19BEC1125No ratings yet

- Energies 12 04093 v2 PDFDocument17 pagesEnergies 12 04093 v2 PDFMohammedAzharuddinSNo ratings yet

- DVM Fan Coil Unit IM EN DB68-07322A-00 170619 PDFDocument56 pagesDVM Fan Coil Unit IM EN DB68-07322A-00 170619 PDFRm MohNo ratings yet

- ProfimDocument5 pagesProfimFernando ValenciaNo ratings yet