Professional Documents

Culture Documents

HDL Syllabus

HDL Syllabus

Uploaded by

Sujith RohitCopyright:

Available Formats

You might also like

- Complete List of PeopleSoft TablesDocument4 pagesComplete List of PeopleSoft TablesAlexvalenciaayola100% (1)

- Chapter-3 Formation of Electronic Contracts: Contracts in The Context of Information TechnologyDocument57 pagesChapter-3 Formation of Electronic Contracts: Contracts in The Context of Information TechnologyMary PoppinsNo ratings yet

- Course Handbook EEE344 DSD - FA19Document12 pagesCourse Handbook EEE344 DSD - FA19Zain JavedNo ratings yet

- TCP/IP Sockets in Java: Practical Guide for ProgrammersFrom EverandTCP/IP Sockets in Java: Practical Guide for ProgrammersRating: 4 out of 5 stars4/5 (5)

- Basic Manual: Hf/Vhf/Uhf All Mode TransceiverDocument100 pagesBasic Manual: Hf/Vhf/Uhf All Mode TransceiverBob MartinNo ratings yet

- SEM3 SyllabusDocument7 pagesSEM3 Syllabushollandw2001No ratings yet

- Verilog HDL SyllabusDocument2 pagesVerilog HDL Syllabussuhas RNo ratings yet

- Open Source SyllabusDocument2 pagesOpen Source SyllabusUmaMaheswariShanmugamNo ratings yet

- Operating System SyllabusDocument3 pagesOperating System SyllabusBRAHMA REDDY AAKUMAIIA100% (1)

- Srm-Object Oriented Programming in CDocument5 pagesSrm-Object Oriented Programming in CVallam RameshNo ratings yet

- File 1704210712 0006745 IntroductoryCNDocument18 pagesFile 1704210712 0006745 IntroductoryCNcutiemegha512No ratings yet

- Course DescriptionDocument8 pagesCourse DescriptionKiranKumarNo ratings yet

- Digital Design With HDL: With Effect From The Academic Year 2005 - 2006Document1 pageDigital Design With HDL: With Effect From The Academic Year 2005 - 2006attarbabaNo ratings yet

- MCA Syllabus - 1st Sem PDFDocument32 pagesMCA Syllabus - 1st Sem PDFshatabdi mukherjeeNo ratings yet

- SyllabusDocument3 pagesSyllabusSHAIK MOHAMMED YASEEN,Cse2020 Vel Tech, ChennaiNo ratings yet

- SyllabusDocument36 pagesSyllabusJenitha JoelNo ratings yet

- Ece 2003Document3 pagesEce 2003gokulNo ratings yet

- 0b9e4data Warehousing and Data Mining - MergedDocument14 pages0b9e4data Warehousing and Data Mining - MergedAkhil_Jain_1678No ratings yet

- COAVITDocument3 pagesCOAVITnikshithNo ratings yet

- QwevvcccccccrDocument6 pagesQwevvcccccccrcool_spNo ratings yet

- QwevvcccccccrDocument6 pagesQwevvcccccccrcool_spNo ratings yet

- Mrit Devops Full Notes PDFDocument214 pagesMrit Devops Full Notes PDFdheerajakhil2003No ratings yet

- Multicore Architecture and Programming1 - P21EC7024Document4 pagesMulticore Architecture and Programming1 - P21EC7024Kumar N KrishnaMurthyNo ratings yet

- 3rd Semester SyllabusDocument22 pages3rd Semester Syllabuscebex22655No ratings yet

- 22cs4001 Dbms Lab ManualDocument69 pages22cs4001 Dbms Lab ManualR.MADHU SUDHANAN HICET STAFF EIENo ratings yet

- SyllabusDocument13 pagesSyllabusKartikey KatyalNo ratings yet

- For Bachelor of Science in Information Technology (2022 Course) (With Effect From 2022-23)Document6 pagesFor Bachelor of Science in Information Technology (2022 Course) (With Effect From 2022-23)Mit MakwanaNo ratings yet

- M.e.estDocument2 pagesM.e.estShiyamala JeyakumarNo ratings yet

- IDE-1 Courses SyllabusDocument8 pagesIDE-1 Courses SyllabusPulluru Sreenivas Sai LokeshNo ratings yet

- Csesyll 2022Document55 pagesCsesyll 2022Mohan H GNo ratings yet

- DPCO Syllabus (Theory Cum Practical)Document2 pagesDPCO Syllabus (Theory Cum Practical)yogeshwaran.r2022lcseNo ratings yet

- ACA-2 DCN ECE 221 - HO - VijayDocument14 pagesACA-2 DCN ECE 221 - HO - VijayAkshay kumar Akshay kumarNo ratings yet

- CS Course OutcomesDocument6 pagesCS Course Outcomesrojamani gantaNo ratings yet

- BSCS SubjectsDocument20 pagesBSCS SubjectsMark Dipad100% (2)

- HTTP - App - Utu.ac - in - Utuexmanagement - Exammsters - Syllabus - CE2010-Operating System1Document4 pagesHTTP - App - Utu.ac - in - Utuexmanagement - Exammsters - Syllabus - CE2010-Operating System1ꌩꍏꌗꃅꋪꍏꀭ T͡ᎻმƘ๏ԻNo ratings yet

- Syllabus and StructureDocument90 pagesSyllabus and Structure1032210521No ratings yet

- 504Document78 pages504Anil TripathiNo ratings yet

- Syllabus: (Tentative) Bachelor of Technology (B. Tech.) Data Science and Artificial Intelligence (DSAI)Document53 pagesSyllabus: (Tentative) Bachelor of Technology (B. Tech.) Data Science and Artificial Intelligence (DSAI)Mohit KulhariNo ratings yet

- MCA Syllabus (2 Years)Document87 pagesMCA Syllabus (2 Years)Rishiram LamichhaneNo ratings yet

- 6th Sem.Document17 pages6th Sem.suraj pahariNo ratings yet

- MCA2013 IISem SyllabusDocument9 pagesMCA2013 IISem SyllabusvijayakumarknNo ratings yet

- Computer Programming - IIDocument2 pagesComputer Programming - IISuresh RamanujamNo ratings yet

- Digital Design Lab ManualDocument39 pagesDigital Design Lab ManualDhananjayaNo ratings yet

- Study Plan EE-221 Digital Logic DesignDocument5 pagesStudy Plan EE-221 Digital Logic Designnauman yasinNo ratings yet

- IT4030 - Computer NetworksDocument5 pagesIT4030 - Computer Networksmakanijenshi2409No ratings yet

- MS110 Business Systems Analysis Course Outline 2011 12Document7 pagesMS110 Business Systems Analysis Course Outline 2011 12Fuzail NaseerNo ratings yet

- Oop Syllabus GoodDocument4 pagesOop Syllabus Goodabhi shekNo ratings yet

- SyllabusDocument4 pagesSyllabusSindhuNo ratings yet

- SyllabusDocument80 pagesSyllabusDhananjay JahagirdarNo ratings yet

- VHDL Programming: Course Code: BTC 501 Credit Units: 03Document22 pagesVHDL Programming: Course Code: BTC 501 Credit Units: 03abhishekNo ratings yet

- Syllabus Sem 7Document15 pagesSyllabus Sem 7Shankar SinghNo ratings yet

- Course Outline-Ramesh-III BCOM (CA) - Fundsmentals of Internet and Web TechnilogiesDocument5 pagesCourse Outline-Ramesh-III BCOM (CA) - Fundsmentals of Internet and Web Technilogiesnav_alexNo ratings yet

- Operating System QuantumDocument85 pagesOperating System QuantumVarnika TomarNo ratings yet

- CSE 357 Zero LectureDocument16 pagesCSE 357 Zero Lectureashokgehlot2100No ratings yet

- Proposed Course Outline (EEEB1014)Document11 pagesProposed Course Outline (EEEB1014)KumaarSheerrwinNo ratings yet

- Sno Course Total Marks Mid Sem Exam Sem End Exam Teaching Hours CreditsDocument10 pagesSno Course Total Marks Mid Sem Exam Sem End Exam Teaching Hours CreditsbalaNo ratings yet

- 12Pcs05 Advanced Java Programming: 4 Credits Unit - IDocument4 pages12Pcs05 Advanced Java Programming: 4 Credits Unit - IJothi KumarNo ratings yet

- Syllabus 5th SemDocument3 pagesSyllabus 5th SemAnkur PrasadNo ratings yet

- BCA Syllabus SemIV 2023 24 KMCLUDocument13 pagesBCA Syllabus SemIV 2023 24 KMCLUlossno26No ratings yet

- SCHEME - G Fifth Semester (CO)Document42 pagesSCHEME - G Fifth Semester (CO)RazeenKhanNo ratings yet

- Cs 205 Prog in C SylDocument11 pagesCs 205 Prog in C SylkgmmetNo ratings yet

- Mastering Python: A Comprehensive Guide to ProgrammingFrom EverandMastering Python: A Comprehensive Guide to ProgrammingNo ratings yet

- DC Traction Using A Chopper - 20bee008Document4 pagesDC Traction Using A Chopper - 20bee008Sujith RohitNo ratings yet

- ESE - EVEN - III Year - POSTPONE CIRCULARDocument1 pageESE - EVEN - III Year - POSTPONE CIRCULARSujith RohitNo ratings yet

- BATCH 12 AbstractDocument1 pageBATCH 12 AbstractSujith RohitNo ratings yet

- Cofffeee Pre Placement Preparation Program - Starts 28 MayDocument3 pagesCofffeee Pre Placement Preparation Program - Starts 28 MaySujith RohitNo ratings yet

- Hindustan EventDocument7 pagesHindustan EventSujith RohitNo ratings yet

- RC CompetitionDocument1 pageRC CompetitionSujith RohitNo ratings yet

- Fee ReceiptDocument1 pageFee ReceiptSujith RohitNo ratings yet

- TRD711870922Document4 pagesTRD711870922Sujith RohitNo ratings yet

- SNMV College EventDocument4 pagesSNMV College EventSujith RohitNo ratings yet

- Smart BusDocument1 pageSmart BusSujith RohitNo ratings yet

- BATCH-01 (20bee008)Document23 pagesBATCH-01 (20bee008)Sujith RohitNo ratings yet

- New Doc 09-Dec-2022 5.48 PMDocument1 pageNew Doc 09-Dec-2022 5.48 PMSujith RohitNo ratings yet

- IndexDocument3 pagesIndexSujith RohitNo ratings yet

- TPSC Online Application ProcessDocument41 pagesTPSC Online Application ProcesssamadarchakrabortyNo ratings yet

- Soldier Health and Position Tracking System Using GpsDocument6 pagesSoldier Health and Position Tracking System Using GpssamNo ratings yet

- Srikanth ResumeDocument2 pagesSrikanth Resumesrikanth9073No ratings yet

- Cambridge International Advanced Subsidiary and Advanced LevelDocument16 pagesCambridge International Advanced Subsidiary and Advanced LevelAl-Sami MashrafeeNo ratings yet

- Server Refresh Planning Guide PDFDocument20 pagesServer Refresh Planning Guide PDFK Kunal RajNo ratings yet

- Reliability and Its Application in TQMDocument15 pagesReliability and Its Application in TQMVijay Anand50% (2)

- Atomix 00582W ManualDocument4 pagesAtomix 00582W ManualJbl IncNo ratings yet

- DNS in Lync Server 2010Document13 pagesDNS in Lync Server 2010kamakom78No ratings yet

- TP70P-211LC1T/ TP04P-20EXL1T Operation Manual TP70P-211LC1T/ TP04P-20EXL1TDocument85 pagesTP70P-211LC1T/ TP04P-20EXL1T Operation Manual TP70P-211LC1T/ TP04P-20EXL1TFrancisco HenriqueNo ratings yet

- Genelec Monitor Setup Guide 2011Document17 pagesGenelec Monitor Setup Guide 2011Bubu PokoNo ratings yet

- Erdinger Block Diagram: Kabylake-UDocument94 pagesErdinger Block Diagram: Kabylake-UEduinMaracuchoFernandezChaparroNo ratings yet

- Manual de Snap Circuits Light en Español Del 82 Al 177 ProyectoDocument39 pagesManual de Snap Circuits Light en Español Del 82 Al 177 Proyectosamuel.guardado.rodriguezNo ratings yet

- Calderas Baxi Power HT45-150 KW PDFDocument38 pagesCalderas Baxi Power HT45-150 KW PDFgiovanniNo ratings yet

- 3 Algorithm Analysis-2Document6 pages3 Algorithm Analysis-2Sherlen me PerochoNo ratings yet

- Minor Project Details (Responses)Document40 pagesMinor Project Details (Responses)himanshuNo ratings yet

- SmartCare SAS SolutionDocument28 pagesSmartCare SAS SolutionSouhir AhmedNo ratings yet

- Im153 1 - 153 2Document11 pagesIm153 1 - 153 2am198801No ratings yet

- LG G4 Stylus - Schematic Diagarm PDFDocument97 pagesLG G4 Stylus - Schematic Diagarm PDFRally Pc50% (2)

- Notable Software System FailuresDocument5 pagesNotable Software System FailuresFAHAD AHMADNo ratings yet

- iPhone-Marketing PlanDocument11 pagesiPhone-Marketing Planrarerahul01No ratings yet

- One Pager v2Document2 pagesOne Pager v2JuanCarlosMarrufoNo ratings yet

- Matseis-1.8 ManualDocument141 pagesMatseis-1.8 ManualOmegaUserNo ratings yet

- Social Media Strategies For Choruses PresentationDocument84 pagesSocial Media Strategies For Choruses PresentationEveryman EleanyaNo ratings yet

- List of Approved Calculators For The LeDocument2 pagesList of Approved Calculators For The LeCho Hei CHANNo ratings yet

- Digital Image Processing: Submitted by Riya ShajiDocument30 pagesDigital Image Processing: Submitted by Riya ShajiRiya ShajiNo ratings yet

- Acoustic Comfort Optimization Based On An Innovative TPA MethodDocument37 pagesAcoustic Comfort Optimization Based On An Innovative TPA MethodJOLITO RAMOSNo ratings yet

- Resume NishantDocument3 pagesResume NishantNishantvermaNo ratings yet

HDL Syllabus

HDL Syllabus

Uploaded by

Sujith RohitOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

HDL Syllabus

HDL Syllabus

Uploaded by

Sujith RohitCopyright:

Available Formats

Course Code: 19EEEN1034 Course Title: Hardware Description Language

Course Category: Professional Elective Course Level: Mastery

L:T:P(Hours/Week): Credits: 3 Total Contact Hours:45 Max Marks:100

3: 0: 0

Pre-requisites

Digital Electronics

Course Objectives

The course is intended to:

1. Explain the Verilog Overview and Hierarchical Modeling Concepts

2. Explain the Basic concepts and Modules & Ports

3. Discuss Gate Level and Data flow Modeling

4. Explain Behavioral Modeling

5. Enlighten on overview of VHDL

Unit I Verilog Overview and Hierarchical Modeling Concepts 10 Hours

Evolution of Computer-Aided Digital Design- Emergence of HDLs- Typical Design

Flow- Importance of HDLs-Popularity of HDL- Trends in HDLs. Top-down and

bottom-up design methodology -Modules –Instances- Components of a

simulation- Design block, Stimulus block

Unit II Basic concepts, Modules & Ports 8 Hours

Basic Concepts: Lexical conventions-data types- system tasks- compiler directives.

Modules and Ports Module: Definition- port declaration- connecting ports-hierarchical

name referencing.

Unit III Gate Level and Data flow Modeling 10 Hours

Gate-Level Modeling: Modeling using basic Verilog gate primitive- description of and/or

and buf/not type gates- rise, fall and turn-off delays- min, max, and typical delays.

Dataflow Modeling: Continuous assignments-delay specification-expressions-

Passed in Board of Studies meeting Approved in Academic Council meeting

BOS Convener BOS Chairman

operators-operands-operator types.

Unit IV Behavioral Modeling 7 Hours

Structured procedures-initial and always- blocking and non-blocking statements - delay

control- generate statement - event control - conditional statements - Multiway

branching – loops - sequential and parallel blocks

Unit V Tasks ,Functions and Modeling Techniques 10 Hours

Differences between tasks and functions, declaration, invocation, automatic tasks and

Functions, Procedural continuous assignments, overriding parameters, conditional

compilation andExecution, useful system tasks.

Course Outcomes Cognitive

At the end of this course, students will be able to: Level

CO1: Explain the Verilog Overview and Hierarchical Modeling Concepts Understand

CO2: Implement the Basic concepts in simple circuits Apply

CO3: Examine Gate Level and Data flow Modeling Apply

CO4: Execute Behavioral Modeling in verilog Apply

CO5: Describe on modeling techniques Understand

Text Book(s):

T1. Samir Palnitkar, ―Verilog HDL: A Guide to Digital Design and Synthesis‖, Pearson

Education, 2nd Edition 2003

T2. Kevin Skahill, ―VHDL for Programmable Logic‖, PHI/Pearson education, 2006.

Reference Book(s):

R1. Donald E. Thomas, Philip R. Moorby, ―The Verilog Hardware Description

Language‖, Springer Science,Business Media, LLC,1996

R2. Michael D. Ciletti, ―Advanced Digital Design with the Verilog HDL‖ Pearson

(Prentice Hall), 2nd Edition.2011

Passed in Board of Studies meeting Approved in Academic Council meeting

BOS Convener BOS Chairman

You might also like

- Complete List of PeopleSoft TablesDocument4 pagesComplete List of PeopleSoft TablesAlexvalenciaayola100% (1)

- Chapter-3 Formation of Electronic Contracts: Contracts in The Context of Information TechnologyDocument57 pagesChapter-3 Formation of Electronic Contracts: Contracts in The Context of Information TechnologyMary PoppinsNo ratings yet

- Course Handbook EEE344 DSD - FA19Document12 pagesCourse Handbook EEE344 DSD - FA19Zain JavedNo ratings yet

- TCP/IP Sockets in Java: Practical Guide for ProgrammersFrom EverandTCP/IP Sockets in Java: Practical Guide for ProgrammersRating: 4 out of 5 stars4/5 (5)

- Basic Manual: Hf/Vhf/Uhf All Mode TransceiverDocument100 pagesBasic Manual: Hf/Vhf/Uhf All Mode TransceiverBob MartinNo ratings yet

- SEM3 SyllabusDocument7 pagesSEM3 Syllabushollandw2001No ratings yet

- Verilog HDL SyllabusDocument2 pagesVerilog HDL Syllabussuhas RNo ratings yet

- Open Source SyllabusDocument2 pagesOpen Source SyllabusUmaMaheswariShanmugamNo ratings yet

- Operating System SyllabusDocument3 pagesOperating System SyllabusBRAHMA REDDY AAKUMAIIA100% (1)

- Srm-Object Oriented Programming in CDocument5 pagesSrm-Object Oriented Programming in CVallam RameshNo ratings yet

- File 1704210712 0006745 IntroductoryCNDocument18 pagesFile 1704210712 0006745 IntroductoryCNcutiemegha512No ratings yet

- Course DescriptionDocument8 pagesCourse DescriptionKiranKumarNo ratings yet

- Digital Design With HDL: With Effect From The Academic Year 2005 - 2006Document1 pageDigital Design With HDL: With Effect From The Academic Year 2005 - 2006attarbabaNo ratings yet

- MCA Syllabus - 1st Sem PDFDocument32 pagesMCA Syllabus - 1st Sem PDFshatabdi mukherjeeNo ratings yet

- SyllabusDocument3 pagesSyllabusSHAIK MOHAMMED YASEEN,Cse2020 Vel Tech, ChennaiNo ratings yet

- SyllabusDocument36 pagesSyllabusJenitha JoelNo ratings yet

- Ece 2003Document3 pagesEce 2003gokulNo ratings yet

- 0b9e4data Warehousing and Data Mining - MergedDocument14 pages0b9e4data Warehousing and Data Mining - MergedAkhil_Jain_1678No ratings yet

- COAVITDocument3 pagesCOAVITnikshithNo ratings yet

- QwevvcccccccrDocument6 pagesQwevvcccccccrcool_spNo ratings yet

- QwevvcccccccrDocument6 pagesQwevvcccccccrcool_spNo ratings yet

- Mrit Devops Full Notes PDFDocument214 pagesMrit Devops Full Notes PDFdheerajakhil2003No ratings yet

- Multicore Architecture and Programming1 - P21EC7024Document4 pagesMulticore Architecture and Programming1 - P21EC7024Kumar N KrishnaMurthyNo ratings yet

- 3rd Semester SyllabusDocument22 pages3rd Semester Syllabuscebex22655No ratings yet

- 22cs4001 Dbms Lab ManualDocument69 pages22cs4001 Dbms Lab ManualR.MADHU SUDHANAN HICET STAFF EIENo ratings yet

- SyllabusDocument13 pagesSyllabusKartikey KatyalNo ratings yet

- For Bachelor of Science in Information Technology (2022 Course) (With Effect From 2022-23)Document6 pagesFor Bachelor of Science in Information Technology (2022 Course) (With Effect From 2022-23)Mit MakwanaNo ratings yet

- M.e.estDocument2 pagesM.e.estShiyamala JeyakumarNo ratings yet

- IDE-1 Courses SyllabusDocument8 pagesIDE-1 Courses SyllabusPulluru Sreenivas Sai LokeshNo ratings yet

- Csesyll 2022Document55 pagesCsesyll 2022Mohan H GNo ratings yet

- DPCO Syllabus (Theory Cum Practical)Document2 pagesDPCO Syllabus (Theory Cum Practical)yogeshwaran.r2022lcseNo ratings yet

- ACA-2 DCN ECE 221 - HO - VijayDocument14 pagesACA-2 DCN ECE 221 - HO - VijayAkshay kumar Akshay kumarNo ratings yet

- CS Course OutcomesDocument6 pagesCS Course Outcomesrojamani gantaNo ratings yet

- BSCS SubjectsDocument20 pagesBSCS SubjectsMark Dipad100% (2)

- HTTP - App - Utu.ac - in - Utuexmanagement - Exammsters - Syllabus - CE2010-Operating System1Document4 pagesHTTP - App - Utu.ac - in - Utuexmanagement - Exammsters - Syllabus - CE2010-Operating System1ꌩꍏꌗꃅꋪꍏꀭ T͡ᎻმƘ๏ԻNo ratings yet

- Syllabus and StructureDocument90 pagesSyllabus and Structure1032210521No ratings yet

- 504Document78 pages504Anil TripathiNo ratings yet

- Syllabus: (Tentative) Bachelor of Technology (B. Tech.) Data Science and Artificial Intelligence (DSAI)Document53 pagesSyllabus: (Tentative) Bachelor of Technology (B. Tech.) Data Science and Artificial Intelligence (DSAI)Mohit KulhariNo ratings yet

- MCA Syllabus (2 Years)Document87 pagesMCA Syllabus (2 Years)Rishiram LamichhaneNo ratings yet

- 6th Sem.Document17 pages6th Sem.suraj pahariNo ratings yet

- MCA2013 IISem SyllabusDocument9 pagesMCA2013 IISem SyllabusvijayakumarknNo ratings yet

- Computer Programming - IIDocument2 pagesComputer Programming - IISuresh RamanujamNo ratings yet

- Digital Design Lab ManualDocument39 pagesDigital Design Lab ManualDhananjayaNo ratings yet

- Study Plan EE-221 Digital Logic DesignDocument5 pagesStudy Plan EE-221 Digital Logic Designnauman yasinNo ratings yet

- IT4030 - Computer NetworksDocument5 pagesIT4030 - Computer Networksmakanijenshi2409No ratings yet

- MS110 Business Systems Analysis Course Outline 2011 12Document7 pagesMS110 Business Systems Analysis Course Outline 2011 12Fuzail NaseerNo ratings yet

- Oop Syllabus GoodDocument4 pagesOop Syllabus Goodabhi shekNo ratings yet

- SyllabusDocument4 pagesSyllabusSindhuNo ratings yet

- SyllabusDocument80 pagesSyllabusDhananjay JahagirdarNo ratings yet

- VHDL Programming: Course Code: BTC 501 Credit Units: 03Document22 pagesVHDL Programming: Course Code: BTC 501 Credit Units: 03abhishekNo ratings yet

- Syllabus Sem 7Document15 pagesSyllabus Sem 7Shankar SinghNo ratings yet

- Course Outline-Ramesh-III BCOM (CA) - Fundsmentals of Internet and Web TechnilogiesDocument5 pagesCourse Outline-Ramesh-III BCOM (CA) - Fundsmentals of Internet and Web Technilogiesnav_alexNo ratings yet

- Operating System QuantumDocument85 pagesOperating System QuantumVarnika TomarNo ratings yet

- CSE 357 Zero LectureDocument16 pagesCSE 357 Zero Lectureashokgehlot2100No ratings yet

- Proposed Course Outline (EEEB1014)Document11 pagesProposed Course Outline (EEEB1014)KumaarSheerrwinNo ratings yet

- Sno Course Total Marks Mid Sem Exam Sem End Exam Teaching Hours CreditsDocument10 pagesSno Course Total Marks Mid Sem Exam Sem End Exam Teaching Hours CreditsbalaNo ratings yet

- 12Pcs05 Advanced Java Programming: 4 Credits Unit - IDocument4 pages12Pcs05 Advanced Java Programming: 4 Credits Unit - IJothi KumarNo ratings yet

- Syllabus 5th SemDocument3 pagesSyllabus 5th SemAnkur PrasadNo ratings yet

- BCA Syllabus SemIV 2023 24 KMCLUDocument13 pagesBCA Syllabus SemIV 2023 24 KMCLUlossno26No ratings yet

- SCHEME - G Fifth Semester (CO)Document42 pagesSCHEME - G Fifth Semester (CO)RazeenKhanNo ratings yet

- Cs 205 Prog in C SylDocument11 pagesCs 205 Prog in C SylkgmmetNo ratings yet

- Mastering Python: A Comprehensive Guide to ProgrammingFrom EverandMastering Python: A Comprehensive Guide to ProgrammingNo ratings yet

- DC Traction Using A Chopper - 20bee008Document4 pagesDC Traction Using A Chopper - 20bee008Sujith RohitNo ratings yet

- ESE - EVEN - III Year - POSTPONE CIRCULARDocument1 pageESE - EVEN - III Year - POSTPONE CIRCULARSujith RohitNo ratings yet

- BATCH 12 AbstractDocument1 pageBATCH 12 AbstractSujith RohitNo ratings yet

- Cofffeee Pre Placement Preparation Program - Starts 28 MayDocument3 pagesCofffeee Pre Placement Preparation Program - Starts 28 MaySujith RohitNo ratings yet

- Hindustan EventDocument7 pagesHindustan EventSujith RohitNo ratings yet

- RC CompetitionDocument1 pageRC CompetitionSujith RohitNo ratings yet

- Fee ReceiptDocument1 pageFee ReceiptSujith RohitNo ratings yet

- TRD711870922Document4 pagesTRD711870922Sujith RohitNo ratings yet

- SNMV College EventDocument4 pagesSNMV College EventSujith RohitNo ratings yet

- Smart BusDocument1 pageSmart BusSujith RohitNo ratings yet

- BATCH-01 (20bee008)Document23 pagesBATCH-01 (20bee008)Sujith RohitNo ratings yet

- New Doc 09-Dec-2022 5.48 PMDocument1 pageNew Doc 09-Dec-2022 5.48 PMSujith RohitNo ratings yet

- IndexDocument3 pagesIndexSujith RohitNo ratings yet

- TPSC Online Application ProcessDocument41 pagesTPSC Online Application ProcesssamadarchakrabortyNo ratings yet

- Soldier Health and Position Tracking System Using GpsDocument6 pagesSoldier Health and Position Tracking System Using GpssamNo ratings yet

- Srikanth ResumeDocument2 pagesSrikanth Resumesrikanth9073No ratings yet

- Cambridge International Advanced Subsidiary and Advanced LevelDocument16 pagesCambridge International Advanced Subsidiary and Advanced LevelAl-Sami MashrafeeNo ratings yet

- Server Refresh Planning Guide PDFDocument20 pagesServer Refresh Planning Guide PDFK Kunal RajNo ratings yet

- Reliability and Its Application in TQMDocument15 pagesReliability and Its Application in TQMVijay Anand50% (2)

- Atomix 00582W ManualDocument4 pagesAtomix 00582W ManualJbl IncNo ratings yet

- DNS in Lync Server 2010Document13 pagesDNS in Lync Server 2010kamakom78No ratings yet

- TP70P-211LC1T/ TP04P-20EXL1T Operation Manual TP70P-211LC1T/ TP04P-20EXL1TDocument85 pagesTP70P-211LC1T/ TP04P-20EXL1T Operation Manual TP70P-211LC1T/ TP04P-20EXL1TFrancisco HenriqueNo ratings yet

- Genelec Monitor Setup Guide 2011Document17 pagesGenelec Monitor Setup Guide 2011Bubu PokoNo ratings yet

- Erdinger Block Diagram: Kabylake-UDocument94 pagesErdinger Block Diagram: Kabylake-UEduinMaracuchoFernandezChaparroNo ratings yet

- Manual de Snap Circuits Light en Español Del 82 Al 177 ProyectoDocument39 pagesManual de Snap Circuits Light en Español Del 82 Al 177 Proyectosamuel.guardado.rodriguezNo ratings yet

- Calderas Baxi Power HT45-150 KW PDFDocument38 pagesCalderas Baxi Power HT45-150 KW PDFgiovanniNo ratings yet

- 3 Algorithm Analysis-2Document6 pages3 Algorithm Analysis-2Sherlen me PerochoNo ratings yet

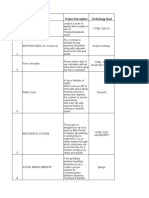

- Minor Project Details (Responses)Document40 pagesMinor Project Details (Responses)himanshuNo ratings yet

- SmartCare SAS SolutionDocument28 pagesSmartCare SAS SolutionSouhir AhmedNo ratings yet

- Im153 1 - 153 2Document11 pagesIm153 1 - 153 2am198801No ratings yet

- LG G4 Stylus - Schematic Diagarm PDFDocument97 pagesLG G4 Stylus - Schematic Diagarm PDFRally Pc50% (2)

- Notable Software System FailuresDocument5 pagesNotable Software System FailuresFAHAD AHMADNo ratings yet

- iPhone-Marketing PlanDocument11 pagesiPhone-Marketing Planrarerahul01No ratings yet

- One Pager v2Document2 pagesOne Pager v2JuanCarlosMarrufoNo ratings yet

- Matseis-1.8 ManualDocument141 pagesMatseis-1.8 ManualOmegaUserNo ratings yet

- Social Media Strategies For Choruses PresentationDocument84 pagesSocial Media Strategies For Choruses PresentationEveryman EleanyaNo ratings yet

- List of Approved Calculators For The LeDocument2 pagesList of Approved Calculators For The LeCho Hei CHANNo ratings yet

- Digital Image Processing: Submitted by Riya ShajiDocument30 pagesDigital Image Processing: Submitted by Riya ShajiRiya ShajiNo ratings yet

- Acoustic Comfort Optimization Based On An Innovative TPA MethodDocument37 pagesAcoustic Comfort Optimization Based On An Innovative TPA MethodJOLITO RAMOSNo ratings yet

- Resume NishantDocument3 pagesResume NishantNishantvermaNo ratings yet