Professional Documents

Culture Documents

CA3089 Renesas

CA3089 Renesas

Uploaded by

Adriano Gaiolas ArtesanaisOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CA3089 Renesas

CA3089 Renesas

Uploaded by

Adriano Gaiolas ArtesanaisCopyright:

Available Formats

DATASHEET

UCT

L ET E P RO D CEME

NT

CA3089 OBSO DED REPLA

EN

COMM FN561

FM IF System NO RE Rev 4.00

October 2002

Description Features

Intersil CA3089 is a monolithic integrated circuit that pro-

• For FM IF Amplifier Applications in High-Fidelity,

.

vides all the functions of a comprehensive FM-IF system.

Automotive, and Communications Receivers

The block diagram shows the CA3089 features, which

include a three-stage FM-IF amplifier/limiter configuration • Includes: IF Amplifier, Quadrature Detector, AF

with level detectors for each stage, a doubly-balanced Preamplifier, and Specific Circuits for AGC, AFC, Muting

quadrature FM detector and an audio amplifier that features (Squelch), and Tuning Meter

the optional use of a muting (squelch) circuit.

• Exceptional Limiting Sensitivity

The advanced circuit design of the IF system includes desir- at -3dB Point . . . . . . . . . . . . . . . . . . . . . . . . . . 12V (Typ)

able deluxe features such as delayed AGC for the RF tuner,

• Low Distortion:

and AFC drive circuit, and an output signal to drive a tuning

(with Double-Tuned Coil) . . . . . . . . . . . . . . . . . 0.1% (Typ)

meter and/or provide stereo switching logic. In addition, inter-

nal power supply regulators maintain a nearly constant cur- • Single-Coil Tuning Capability

rent drain over the voltage supply range of +8.5V to +16V.

• High Recovered Audio . . . . . . . . . . . . . . . . . 400mV (Typ)

The CA3089 is ideal for high-fidelity operation. Distortion in a

• Provides Specific Signal for Control of Interchannel Muting

CA3089 FM-IF System is primarily a function of the phase

(Squelch)

linearity characteristic of the outboard detector coil.

• Provides Specific Signal for Direct Drive of a Tuning Meter

• Provides Delayed AGC Voltage for RF Amplifier

Part Number Information

• Provides a Specific Circuit for Flexible AFC

PART TEMP. RANGE

NUMBER (oC) PACKAGE PKG. NO. • Internal Supply-Voltage Regulators

CA3089E -40 to 85 16 Ld PDIP E16.3

CA3089M1 -40 to 85 20 Ld SOIC M20.3

(3089M)

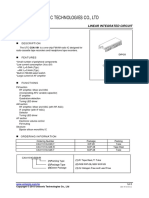

Pinouts

CA3089 CA3089

(PDIP) (SOIC)

TOP VIEW TOP VIEW

GND 1 20 GND

IF IN 1 16 NC IF IN 2 19 DELAYED AGC

INPUT BYPASS 2 15 DELAYED AGC INPUT BYPASS 3 18 GND

DC FB BYPASS 3 14 SUBSTRATE (GND) DC FB BYPASS 4 17 SUBSTRATE (GND)

FRAME GND 4 13 TUNING METER OUT FRAME GND 5 16 TUNING METER OUT

MUTE CONTROL 5 12 MUTE LOGIC MUTE CONTROL 6 15 MUTE LOGIC

AUDIO OUT 6 11 V+ AUDIO OUT 7 14 V+

AFC OUT 7 10 REF BIAS AFC OUT 8 13 REF BIAS

IF OUT 9 12 QUADRATURE INPUT

IF OUT 8 9 QUADRATURE INPUT

GND 10 11 NC

FN561 Rev 4.00 Page 1 of 8

October 2002

CA3089

Absolute Maximum Ratings Thermal Information

Supply Voltage Thermal Resistance (Typical, Note 1) JA (oC/W)

Between V+ and Frame GND . . . . . . . . . . . . . . . . . . . . . . . . .16V PDIP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Between V+ and Substrate GND . . . . . . . . . . . . . . . . . . . . . . .16V SOIC Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

DC Current (Out of Delayed AGC). . . . . . . . . . . . . . . . . . . . . . . 2mA Maximum Junction Temperature (Plastic Package) . . . . . . . 150oC

Operating Conditions Maximum Storage Temperature Range . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . 300oC

Temperature Range. . . . . . . . . . . . . . . . . . . . . . . . . . -40oC to 85oC

(SOIC - Lead Tips Only)

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. JA is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications V+ = 12V (See Figures 3 and 4)

(NOTE 3) TEMP.

PARAMETER TEST CONDITIONS (oC) MIN TYP MAX UNITS

DC CHARACTERISTICS

Quiescent Circuit Current No signal input, Non muted 25 16 23 30 mA

DC Voltages Terminal 1 (IF Input) 25 1.2 1.9 2.4 V

Terminal 2 (AC Return to Input) 25 1.2 1.9 2.4 V

Terminal 3 (DC Bias to Input) 25 1.2 1.9 2.4 V

Terminal 6 (Audio Output) 25 5.0 5.6 6.0 V

Terminal 10 (DC Reference) 25 5.0 5.6 6.0 V

DYNAMIC CHARACTERISTICS

Input Limiting Voltage (-3dB point), V1 (lim) - fO = 10.7MHz, 25 - 12 25 V

AM Rejection (Terminal 6), AMR VIN = 0.1V, fMOD = 400Hz, 25 45 55 - dB

AM Mod. = 30% Deviation = 75kHz

Recovered AF Voltage (Terminal 6) VO (AF) VIN = 0.1V 25 300 400 500 mV

Total Harmonic Single Tuned (Terminal 6) 25 - 0.5 1.0 %

Distortion, THD Double Tuned (Terminal 6) 25 - 0.1 - %

(Note 2)

Signal Plus Noise to Noise Ratio (Terminal 6) 25 60 67 - dB

NOTES:

2. THD characteristics are essentially a function of the phase characteristics of the network connected between Terminals 8, 9, and 10.

3. Terminal numbers refer to 16 Lead PDIP.

Application Information

RECOVERED AUDIO (dB) MUTING CONTROL

V+ = 12V, TA 25oC

5k V+ = 12V, TA = 25oC

125 10 7

0 6

A

AT MAXIMUM RESISTANCE

RECOVERED AUDIO FROM FULL OUTPUT

CURRENT INTO TERMINAL 7 (A)

100

-10 (LEFT COORDINATE) 5

75

50

-20 TUNER AGC DC VOLTAGE AT 4

DC (V)

25 TERM. 15 (RIGHT COORDINATE)

0 -30 VOLTAGE AT TERMINAL 13 3

METER CIRCUIT (33k TO GND)

-25 (RIGHT COORDINATE)

-40 2

-50

-75 -50 1

-100

-125 -60

-100 -50 0 50 100 1 10 100 1K 10K 100K

CHANGE IN FREQUENCY (kHz) INPUT SIGNAL (V)

FIGURE 1. AFC CHARACTERISTICS (CURRENT AT FIGURE 2. MUTING ACTION, TUNER AGC, AND TUNING

TERMINAL 7) vs CHANGE IN FREQUENCY. (SEE METER OUTPUT vs INPUT SIGNAL VOLTAGE.

TEST CIRCUIT FIGURE 3) (SEE TEST CIRCUIT FIGURE 3)

FN561 Rev 4.00 Page 2 of 8

October 2002

CA3089

Test Circuits

3K

L 100

(NOTE 5) pF

V+ = 12V C1

22H C 5K

T (NOTE 8)

100 V+ = 12V

0.05F 11 22H C2 5K

8 pF

9 0.05F 11 100

SIGNAL 0.01F 3.9K 8 pF

INPUT 1

VOLTAGE 10 SIGNAL 0.01F 9

AFC OUTPUT 8.2K

51 7 INPUT 1

2.7K VOLTAGE 10

AUDIO 7 AFC OUTPUT

3 CA3089E 6 51

OUT

2.7K AUDIO

0.01 12 3 CA3089E 6

F 5 0.01 OUT

0.02 F 0.01 12 0.01

F 2 13 470 F 5 F

0.001 0.02

15 F F 2 13 470

0.001

14 0.001 0.33F F

F 120K 15

4 0.001 0.33F

10 33K 14 120K

F

K 0.5M 4

10 33K

150A K 0.5M

FULL 150A

TUNING METER

SCALE FULL

TUNING METER

SCALE

NOTES: NOTES:

4. All resistance values are in ohms. 7. All resistance values are in ohms.

5. L tunes with 100pF (C) at 10.7MHz. 8. T PRI. - Q0 (unloaded) 75 (tunes with 100pF (C1) 20 of 34e on

7/ ” dia. form).

6. Q0 (unloaded) 75 (G.I. Automatic Mfg. Div. EX22741 or equivalent) 32

9. SEC. - Q0 (unloaded) 75 (tunes with 100pF (C2) 20 of 34e on

7/ ” dia. form).

32

10. kQ (percent of critical coupling) 70%.

(Adjusted for coil voltage VC) = 150mV.

Above values permit proper operation of mute (squelch) circuit

“E” type slugs, spacing 4mm.

FIGURE 3. TEST CIRCUIT FOR CA3089E USING A SINGLE- FIGURE 4. TEST CIRCUIT FOR CA3089E USING A DOUBLE-

TUNED DETECTOR COIL TUNED DETECTOR COIL

Test Applications

L (NOTE 14)

V+ = 12V 100pF

100

C

0.01F 0.05F 22

H

11 3.9K

220pF 250pF 8

1 9

300 FM CERAMIC 10

INPUT IF OUT FILTER 330 2.7K

TUNER AUDIO

(NOTE 12) (NOTE 13) 3 CA3089E

CA3089E 6

OUT

0.01F

2

14

NOTES: 4

11. All resistance values are in ohms.

12. Waller 4SN3FIC or equivalent.

13. Murata SFG 10.7mA or equivalent.

14. L tunes with 100pF (C) at 10.7MHz Q0 unloaded 75 Performance Data at fO = 98MHz, fMOD = 400Hz, Deviation = 75kHz:

(G.I. EX22741 or equivalent). -3dB Limiting Sensitivity . . . . . . . . . . . . . . . . . . 2V (Antenna Level)

20dB Quieting Sensitivity . . . . . . . . . . . . . . . . . 1V (Antenna Level)

30dB Quieting Sensitivity . . . . . . . . . . . . . . . .1.5V (Antenna Level)

FIGURE 5. TYPICAL FM TUNER USING THE CA3089E WITH A SINGLE TUNED DETECTOR COIL

FN561 Rev 4.00 Page 3 of 8

October 2002

CA3089

Test Applications (Continued)

FIGURE 6A. BOTTOM VIEW OF PRINTED CIRCUIT BOARD FIGURE 6B. COMPONENT SIDE - TOP VIEW

FIGURE 6. ACTUAL SIZE PHOTOGRAPHS OF THE CA3089E AND OUTBOARD COMPONENTS MOUNTED ON A PRINTED-CIRCUIT BOARD

Block Diagram

L

(NOTE 16)

QUADRATURE

INPUT

V+ 22H

C=

100pF

TO INTERNAL 11 IF REFERENCE

8 9 10

REGULATORS OUT BIAS

IF IF AMPLIFIER AFC AFC

7

INPUT AMPL. OUTPUT

1ST IF 2ND IF 3RD IF QUADRATURE

1 AMPL. AMPL. AMPL. DETECTOR AUDIO

AUDIO

6

AMPL. OUTPUT

3

0.02 0.02F AUDIO MUTING

F MUTE

2 LEVEL LEVEL LEVEL LEVEL SENSITIVITY

(SQUELCH) 5

DETECTOR DETECTOR DETECTOR DETECTOR

CONTROL

DELAYED

AMPL.

AGC FOR

RF AMPL

TUNING 470 120K

15 MUTE (SQUELCH)

METER 12

DRIVE CIRCUIT

CIRCUIT 500K

10K FRAME SUBSTRATE 0.33F

150A TO STEREO

4 14 13

METER THRESHOLD

33K TUNING METER OUTPUT LOGIC CIRCUITS

NOTES:

15. All resistance values are in ohms.

16. L Tunes with 100pF (C) at 10.7MHz.

17. QO @ 75 (G.I. EX22741 or equivalent).

18. Pin numbers refer to 16 lead DIP.

FN561 Rev 4.00 Page 4 of 8

October 2002

CA3089

Schematic Diagram

IF AMPLIFIER

Q9 Q15

A Q21

R18 R19 Q22 R27

C 2K R23 750

R6 R7 R10 R11 2K

2K

2K 2K 2K 2K

R24

C11 C12 C13 C14 480

1 1 1 1

B R25

1.5K

V+

V+ V+

Q3 Q4

C1

1 Q19

Q20

Q8 Q7 Q14 Q13 R28

C2 R20

1 750

Q8A Q7A Q14A Q13A 2K

IF

INPUT Q11 Q16Q17

Q10 R16A R21

1 Q1 Q2 R12A R15A

R13A 2K 480

2K 2K

2K

Q18 R22 SEE

Q12

2 C3 R16 1.5K NEXT

0.2 2.7K

Q6 R13 R14 R12 R15 PAGE

R17

2.7K 360 2.7K 2.7K

INPUT R2 360

BYPASSING 30K C4

R3

0.2

360

3

R1

30K

V+

V+

Q74

R50 R51 R59 R60

500 5K 150 300

C6 C7 C8

C5 3

Q58 2 3 3

Q61 Q64 Q68 Q75 Q77

Q60 Q63 Q69 Q84

Q59 Q62 Q70 Q76

R52 R53 R56 R61

400 600 600 4K

AGC FOR TUNING

15 13 METER

RF AMPL.

NOTE: Pin numbers refer to 16 lead PDIP.

LEVEL DETECTOR AND METER CIRCUIT

FN561 Rev 4.00 Page 5 of 8

October 2002

CA3089

Schematic Diagram (Continued)

9 QUADRATURE REF 10 8 IF 11 V+

INPUT BIAS OUT

DETECTOR AUDIO

R33 R32 AMPLIFIER

500 500

R37 R38 R44 R42

166 500 500 166

Q35

Q23

Q44 Q46 Q53 Q51

Q24 Q25 Q32 Q33 R31

390

Q45 A Q54

R26 R34

10K 10K

R40 R41

Q26 Q34 500 500

R63 R64

300 300

Q48 Q49

Q39 Q79 Q81

Q38

Q50

Q80

R35

AUDIO

D2 D3 2.2K OUT

Q40 Q82

R49 6

5K

Q27 Q41

Q83

R29 R36

200 200 V+

R65

5

R45 R39 R43 50K MUTE

R9

10K Q28 V+ 500 500 500 CONTROL

Q5

Q30

A Q47 Q52

Z1 Q31

R8 Q29 Q43

C D4

2K

Q42

AFC

B R30 D5 R54 OUTPUT

R5 480

4K 5K R46 7

Z2 Q56

R55 4.2K

D1 13K

R4 Q55 Q57

480 Q65

Q66 BIAS R47 R48

Q67 SUPPLY 500 500

AFC AMPLIFIER

R57 R62

C9

10K V+

10 4 FRAME 14 SUBSTRATE

Q71 500

Q78

Q72

Q73

C10

10 R58 NOTES:

50 19. All resistance values are in ohms.

MUTE

12

LOGIC 20. All capacitance values are in pF.

21. Pin numbers refer to 16 lead PDIP.

MUTE DRIVE

FN561 Rev 4.00 Page 6 of 8

October 2002

CA3089

Dual-In-Line Plastic Packages (PDIP)

E16.3 (JEDEC MS-001-BB ISSUE D)

N

16 LEAD DUAL-IN-LINE PLASTIC PACKAGE

E1

INDEX INCHES MILLIMETERS

AREA 1 2 3 N/2

SYMBOL MIN MAX MIN MAX NOTES

-B-

A - 0.210 - 5.33 4

-A-

D E A1 0.015 - 0.39 - 4

BASE A2 0.115 0.195 2.93 4.95 -

PLANE A2

-C- A

B 0.014 0.022 0.356 0.558 -

SEATING

PLANE L C

L B1 0.045 0.070 1.15 1.77 8, 10

D1 A1 eA C 0.008 0.014 0.204 0.355 -

D1

B1 e D 0.735 0.775 18.66 19.68 5

eC C

B

eB D1 0.005 - 0.13 - 5

0.010 (0.25) M C A B S

E 0.300 0.325 7.62 8.25 6

NOTES:

E1 0.240 0.280 6.10 7.11 5

1. Controlling Dimensions: INCH. In case of conflict between English and

Metric dimensions, the inch dimensions control. e 0.100 BSC 2.54 BSC -

2. Dimensioning and tolerancing per ANSI Y14.5M-1982. eA 0.300 BSC 7.62 BSC 6

3. Symbols are defined in the “MO Series Symbol List” in Section 2.2 of eB - 0.430 - 10.92 7

Publication No. 95.

L 0.115 0.150 2.93 3.81 4

4. Dimensions A, A1 and L are measured with the package seated in JE-

DEC seating plane gauge GS-3. N 16 16 9

5. D, D1, and E1 dimensions do not include mold flash or protrusions. Rev. 0 12/93

Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

6. E and eA are measured with the leads constrained to be perpendic-

ular to datum -C- .

7. eB and eC are measured at the lead tips with the leads unconstrained.

eC must be zero or greater.

8. B1 maximum dimensions do not include dambar protrusions. Dambar

protrusions shall not exceed 0.010 inch (0.25mm).

9. N is the maximum number of terminal positions.

10. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3,

E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

FN561 Rev 4.00 Page 7 of 8

October 2002

CA3089

Small Outline Plastic Packages (SOIC)

N M20.3 (JEDEC MS-013-AC ISSUE C)

20 LEAD WIDE BODY SMALL OUTLINE PLASTIC PACKAGE

INDEX

AREA H 0.25(0.010) M B M

INCHES MILLIMETERS

E

SYMBOL MIN MAX MIN MAX NOTES

-B-

A 0.0926 0.1043 2.35 2.65 -

1 2 3 A1 0.0040 0.0118 0.10 0.30 -

L

B 0.013 0.0200 0.33 0.51 9

SEATING PLANE C 0.0091 0.0125 0.23 0.32 -

-A- D 0.4961 0.5118 12.60 13.00 3

D A h x 45o

E 0.2914 0.2992 7.40 7.60 4

-C- e 0.050 BSC 1.27 BSC -

µ

e H 0.394 0.419 10.00 10.65 -

A1

C h 0.010 0.029 0.25 0.75 5

B 0.10(0.004)

L 0.016 0.050 0.40 1.27 6

0.25(0.010) M C A M B S

N 20 20 7

NOTES: 0o 8o 0o 8o -

1. Symbols are defined in the “MO Series Symbol List” in Section 2.2 of Rev. 0 12/93

Publication Number 95.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimension “D” does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006

inch) per side.

4. Dimension “E” does not include interlead flash or protrusions. Interlead

flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

5. The chamfer on the body is optional. If it is not present, a visual index

feature must be located within the crosshatched area.

6. “L” is the length of terminal for soldering to a substrate.

7. “N” is the number of terminal positions.

8. Terminal numbers are shown for reference only.

9. The lead width “B”, as measured 0.36mm (0.014 inch) or greater

above the seating plane, shall not exceed a maximum value of

0.61mm (0.024 inch)

10. Controlling dimension: MILLIMETER. Converted inch dimensions

are not necessarily exact.

© Copyright Intersil Americas LLC 2002. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted

in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such

modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are

current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its

subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN561 Rev 4.00 Page 8 of 8

October 2002

You might also like

- Becker 6019 Aux Input RetrofitDocument2 pagesBecker 6019 Aux Input RetrofitSh Medo MedoNo ratings yet

- Samsung Digital Recorder: SVR-S820 / S410Document19 pagesSamsung Digital Recorder: SVR-S820 / S410John Appleseed100% (2)

- CA3100TDocument7 pagesCA3100THisham MehremNo ratings yet

- Features Description: FM IF SystemDocument8 pagesFeatures Description: FM IF Systemluiz augusto torrecilhas TorrecilhasNo ratings yet

- Color TV China Circuit Diagram TCL Chassis M113Document9 pagesColor TV China Circuit Diagram TCL Chassis M113Gary Nugas100% (1)

- ND-60SG: IndexDocument20 pagesND-60SG: IndexPaulo chagas paulo ratoNo ratings yet

- DatasheetDocument9 pagesDatasheetjim campbellNo ratings yet

- Nippon PDFDocument96 pagesNippon PDFEugen BratuNo ratings yet

- Data Sheet: Self Tuned Radio (STR)Document32 pagesData Sheet: Self Tuned Radio (STR)Paulo SampaioNo ratings yet

- CI CA3094B DatasheetDocument14 pagesCI CA3094B DatasheetRogerio EngelNo ratings yet

- DatasheetDocument18 pagesDatasheetGurue AlonNo ratings yet

- Ca3130, Ca3130A: 15Mhz, Bimos Operational Amplifier With Mosfet Input/Cmos Output FeaturesDocument18 pagesCa3130, Ca3130A: 15Mhz, Bimos Operational Amplifier With Mosfet Input/Cmos Output FeaturesJosé Moisés Nuñez SilvaNo ratings yet

- Service Manual: SC-TM23Document124 pagesService Manual: SC-TM23Omar FloresNo ratings yet

- Datasheet Tea5757Document32 pagesDatasheet Tea5757Rubens Vaz PintoNo ratings yet

- Casio tv-1900bxm SMDocument21 pagesCasio tv-1900bxm SMДмитрий АртюхNo ratings yet

- Service Manual For M28 One-Chip Chassis: PART I. Servicing PrecautionsDocument56 pagesService Manual For M28 One-Chip Chassis: PART I. Servicing PrecautionsPetrica Dan DinuNo ratings yet

- Datasheet 1619Document12 pagesDatasheet 1619AtulNo ratings yet

- Panasonic CQ-MX0470LC SUZUKI Audio CarDocument33 pagesPanasonic CQ-MX0470LC SUZUKI Audio CarHayri ÖzNo ratings yet

- UTC CXA1191 Linear Integrated Circuit: FM/AM RadioDocument8 pagesUTC CXA1191 Linear Integrated Circuit: FM/AM RadioA Daniel LazarescuNo ratings yet

- AKIRADocument38 pagesAKIRAhanifrathorNo ratings yet

- Features Description: FM IF SystemDocument7 pagesFeatures Description: FM IF Systemlu1agpNo ratings yet

- Unisonic Technologies Co., LTD: 4 Pin Dip Phototransistor PhotocouplerDocument7 pagesUnisonic Technologies Co., LTD: 4 Pin Dip Phototransistor PhotocouplerAbdul Rauf MughalNo ratings yet

- Precision Waveform Generator: ... The Analog Plus CompanyDocument17 pagesPrecision Waveform Generator: ... The Analog Plus CompanySy Phan MinhNo ratings yet

- Unisonic Technologies Co., LTD: FM/AM RadioDocument8 pagesUnisonic Technologies Co., LTD: FM/AM RadioCyber XNo ratings yet

- LA1265Document15 pagesLA1265gavrilaemiNo ratings yet

- 40m CW m0dgqDocument8 pages40m CW m0dgqapsNo ratings yet

- Cxa1691 PDFDocument11 pagesCxa1691 PDFȺɌįfNo ratings yet

- 21.5" LCD Color Monitor Aoc F22: 6.2 Electric Block DiagramDocument10 pages21.5" LCD Color Monitor Aoc F22: 6.2 Electric Block DiagramsilasjaderNo ratings yet

- Aoc F22Document10 pagesAoc F22gabriel teixeiraNo ratings yet

- DTMF Receiver For Telephones: BU8874 / BU8874FDocument10 pagesDTMF Receiver For Telephones: BU8874 / BU8874FYazan HaidarNo ratings yet

- Icl8038 PDFDocument12 pagesIcl8038 PDFmarcosNo ratings yet

- Akira Ct-29tw9an Chassis 5p60 PDFDocument38 pagesAkira Ct-29tw9an Chassis 5p60 PDFhanifrathorNo ratings yet

- Circuit DescriptionDocument4 pagesCircuit DescriptionTony SalvianoNo ratings yet

- Ka 22427Document3 pagesKa 22427Cibi CristianNo ratings yet

- Datasheet Tea 5757hDocument32 pagesDatasheet Tea 5757hJose BenavidesNo ratings yet

- Data Sheet: Single Standard VIF-PLL With QSS-IF and FM-PLL DemodulatorDocument36 pagesData Sheet: Single Standard VIF-PLL With QSS-IF and FM-PLL DemodulatorzatarnajibNo ratings yet

- TCL M113 Tmpa8809 MC4406 SMDocument90 pagesTCL M113 Tmpa8809 MC4406 SMYanto LufiNo ratings yet

- Temp 13083111391929Document13 pagesTemp 13083111391929sebas ruizNo ratings yet

- UPC1892Document43 pagesUPC1892Hari HaranNo ratings yet

- Grundig gmm1100-stf55-1001 t2s08 Chassis (ET)Document23 pagesGrundig gmm1100-stf55-1001 t2s08 Chassis (ET)Simion VictorasNo ratings yet

- Fpab30bh60 278404Document12 pagesFpab30bh60 278404soundmallick43No ratings yet

- UC3842B/3843B: Unisonic Technologies Co., LTDDocument11 pagesUC3842B/3843B: Unisonic Technologies Co., LTDvannadioNo ratings yet

- TCL Chassis M113 SINGER SCT-29128 - Service - ManualDocument90 pagesTCL Chassis M113 SINGER SCT-29128 - Service - ManualAjith Priyalal75% (4)

- Seatel Vsat ArbitratorDocument10 pagesSeatel Vsat ArbitratorFlavioNo ratings yet

- Cxa 1619Document11 pagesCxa 1619hellomotol7No ratings yet

- m28 Service ManualDocument81 pagesm28 Service ManualMohamed HaidaraNo ratings yet

- Casio Cdp-130 SMDocument42 pagesCasio Cdp-130 SMBrian Hutama SusiloNo ratings yet

- ICL8038Document14 pagesICL8038RAYLINo ratings yet

- SA2111CDocument9 pagesSA2111CGilmar FerreiraNo ratings yet

- 80 Meter CW ARDF Receiver: The Foxfinder-80 Web UpdateDocument20 pages80 Meter CW ARDF Receiver: The Foxfinder-80 Web Updateag1tatorNo ratings yet

- TC 1475Document20 pagesTC 1475pedroleyvafandinoNo ratings yet

- Tda7265 (30W+30W)Document18 pagesTda7265 (30W+30W)ShiguMiku TheyNo ratings yet

- TL494Document7 pagesTL494Share KhNo ratings yet

- Anasat Ku Band Rev3Document62 pagesAnasat Ku Band Rev3adi matraNo ratings yet

- CQ-ES7880AZ: Am/Fm/Mpx Electronic Tuning RADIO With 6-Disc CD ChangerDocument28 pagesCQ-ES7880AZ: Am/Fm/Mpx Electronic Tuning RADIO With 6-Disc CD Changerdiablohuno100% (1)

- M64894FP/GP: Mitsubishi Ic (TV)Document9 pagesM64894FP/GP: Mitsubishi Ic (TV)Julio Rafael GamboaNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- 150ma, Low-Dropout Regulator, Ultralow-Power, I 1 A With Pin-Selectable, Dual-Level Output VoltageDocument31 pages150ma, Low-Dropout Regulator, Ultralow-Power, I 1 A With Pin-Selectable, Dual-Level Output Voltagehuan nguyenNo ratings yet

- Presented By, Uma .B. S Ii Sem Mtech (1MS11MSC013) Department of Mechanical EngineeringDocument18 pagesPresented By, Uma .B. S Ii Sem Mtech (1MS11MSC013) Department of Mechanical EngineeringJyoti Sharma100% (1)

- Inventec: Smb2 Smb1 1.CEC Close Npce781 Pin Smb3 1.chargeDocument1 pageInventec: Smb2 Smb1 1.CEC Close Npce781 Pin Smb3 1.chargeSuriya MasuNo ratings yet

- Yuasa Technical Data Sheet: The World's Leading Battery ManufacturerDocument1 pageYuasa Technical Data Sheet: The World's Leading Battery ManufacturerAshraf Sayed ShabaanNo ratings yet

- Schematic Diagram PDFDocument12 pagesSchematic Diagram PDFDELTA TELECOMNo ratings yet

- Honeywell Sensing Micropressure Board Mount Pressure MPR Series Datasheet 32332628 G en PDFDocument25 pagesHoneywell Sensing Micropressure Board Mount Pressure MPR Series Datasheet 32332628 G en PDFChris SmithNo ratings yet

- Manual Rico Service PDFDocument2,757 pagesManual Rico Service PDFAlejandro José SosaNo ratings yet

- K02-S01 Rev 2 Mar 2019 (A) Plant Paging and PA System SpecificationDocument8 pagesK02-S01 Rev 2 Mar 2019 (A) Plant Paging and PA System SpecificationMohamed AdelNo ratings yet

- DAC Makes Controller Programmable: Programmble Voltage, Programmable Controller, Dynamic Voltage, Core VoltageDocument4 pagesDAC Makes Controller Programmable: Programmble Voltage, Programmable Controller, Dynamic Voltage, Core VoltageJonathan JaegerNo ratings yet

- 13th PPT (Inductosyn)Document16 pages13th PPT (Inductosyn)Zubair AhmedNo ratings yet

- L E 2 0 Safety Evalution UnitDocument63 pagesL E 2 0 Safety Evalution UnitTeppo ErkkiläNo ratings yet

- Cryogenic MOS Transistor Model: Arnout Beckers, Farzan Jazaeri, and Christian EnzDocument9 pagesCryogenic MOS Transistor Model: Arnout Beckers, Farzan Jazaeri, and Christian EnzTim MazumdarNo ratings yet

- FX-20 Diagrama y Fallas PDFDocument20 pagesFX-20 Diagrama y Fallas PDFGilberto PorfirioNo ratings yet

- Titanus Top Sens 2Document105 pagesTitanus Top Sens 2Robert CurculescuNo ratings yet

- 4311b ManualDocument4 pages4311b Manualvova1cleric198830No ratings yet

- Physical Layer: Data and SignalsDocument65 pagesPhysical Layer: Data and SignalsHana hanaNo ratings yet

- AEMC Model 4500 Digital Ground Resistance Tester ManualDocument47 pagesAEMC Model 4500 Digital Ground Resistance Tester ManualBilly BadaceNo ratings yet

- Electrical Calculator: - I2 SeriesDocument46 pagesElectrical Calculator: - I2 SeriessyahabdulrizalNo ratings yet

- 7310 Installation InstructionsDocument2 pages7310 Installation InstructionsmohamedNo ratings yet

- STEP 2 Course Material: Control Unit (MCU)Document19 pagesSTEP 2 Course Material: Control Unit (MCU)Mahmoud MohamedNo ratings yet

- User Manual: Models: D24h-G9, D32h-G9, D40f-G9, D50x-G9, V405-G9, V505-G9 & V655-G9Document55 pagesUser Manual: Models: D24h-G9, D32h-G9, D40f-G9, D50x-G9, V405-G9, V505-G9 & V655-G9Jeff JueNo ratings yet

- Service Manual: Pcg-C1Vp/C1VpkDocument20 pagesService Manual: Pcg-C1Vp/C1VpkEnrique CedeñoNo ratings yet

- TFM 94 SeriesDocument2 pagesTFM 94 Seriesluat1983No ratings yet

- Seven Level Asymmetric Cascade Inverter With Space Vector PWM Added PR ControlDocument6 pagesSeven Level Asymmetric Cascade Inverter With Space Vector PWM Added PR ControlAhmad MqdadNo ratings yet

- Setup: Deep Sea Electronics Dse857 Usb - Rs485 Converter Installation InstructionsDocument2 pagesSetup: Deep Sea Electronics Dse857 Usb - Rs485 Converter Installation InstructionsYaseen SagarNo ratings yet

- Sounders For CO / NO2 System: Carbon Monoxide Detection SystemDocument2 pagesSounders For CO / NO2 System: Carbon Monoxide Detection SystemfesterrNo ratings yet

- Pig&Dan: Technical Rider (DJ - Set)Document2 pagesPig&Dan: Technical Rider (DJ - Set)Alex LosaNo ratings yet

- Mechatronics Design 1 Second Mid Term Exam 2010-2011Document2 pagesMechatronics Design 1 Second Mid Term Exam 2010-2011seraj sersawi100% (1)