Professional Documents

Culture Documents

PC100 Sdram - 144 Pin - Sodimm

PC100 Sdram - 144 Pin - Sodimm

Uploaded by

dinhdtdOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

PC100 Sdram - 144 Pin - Sodimm

PC100 Sdram - 144 Pin - Sodimm

Uploaded by

dinhdtdCopyright:

Available Formats

M464S3254BT1 PC100 SODIMM

M464S3254BT1 SDRAM SODIMM

32Mx64 SDRAM SODIMM based on 16Mx16, 4Banks, 8K Refresh,3.3V Synchronous DRAMs with SPD

GENERAL DESCRIPTION FEATURE

The Samsung M464S3254BT1 is a 32M bit x 64 Synchronous • Performance range

Dynamic RAM high density memory module. The Samsung Part No. Max Freq. (Speed)

M464S3254BT1 consists of eight CMOS 16M x 16 bit with M464S3254BT1-L1H /C1H 100MHz (10ns @ CL=2)

4banks Synchronous DRAMs in TSOP-II 400mil package and a M464S3254BT1-L1L /C1L 100MHz (10ns @ CL=3)

2K EEPROM in 8-pin TSSOP package on a 144-pin glass-epoxy

• Burst mode operation

substrate. Three 0.1uF decoupling capacitors are mounted on • Auto & self refresh capability (8192 Cycles/64ms)

the printed circuit board in parallel for each SDRAM. The • LVTTL compatible inputs and outputs

M464S3254BT1 is a Small Outline Dual In-line Memory Module • Single 3.3V ± 0.3V power supply

and is intended for mounting into 144-pin edge connector sock- • MRS cycle with address key programs

ets. Latency (Access from column address)

Synchronous design allows precise cycle control with the use of Burst length (1, 2, 4, 8 & Full page)

system clock. I/O transactions are possible on every clock cycle. Data scramble (Sequential & Interleave)

Range of operating frequencies, programmable latencies allows • All inputs are sampled at the positive going edge of the

the same device to be useful for a variety of high bandwidth, system clock

• Serial presence detect with EEPROM

high performance memory system applications.

• PCB : Height (1,250mil), double sided component

PIN CONFIGURATIONS (Front side/back side) PIN NAMES

Pin Front Pin Back Pin Front Pin Back Pin Front Pin Back Pin Name Function

A0 ~ A12 Address input (Multiplexed)

1 VSS 2 VSS 51 DQ14 52

DQ46 95 DQ21 96 DQ53

BA0 ~ BA1 Select bank

3 DQ0 4 DQ32 53 DQ15 54

DQ47 97 DQ22 98 DQ54

5 DQ1 6 DQ33 55 VSS 56VSS 99 DQ23 100 DQ55 DQ0 ~ DQ63 Data input/output

7 DQ2 8 DQ34 57 NC 58NC 101 VDD 102 VDD CLK0 ~ CLK1 Clock input

9 DQ3 10 DQ35 59 NC 60NC 103 A6 104 A7 CKE0 ~ CKE1 Clock enable input

11 VDD 12 VDD 105 A8 106 BA0 CS0 ~ CS1 Chip select input

13 DQ4 14 DQ36 Voltage Key 107 VSS 108 VSS RAS Row address strobe

15 DQ5 16 DQ37 109 A9 110 BA1

CAS Column address strobe

17 DQ6 18 DQ38 61 CLK0 62 CKE0 111 A10/AP 112 A11

WE Write enable

19 DQ7 20 DQ39 63 VDD 64 VDD 113 VDD 114 VDD

21 VSS 22 VSS 65 RAS 66 CAS 115 DQM2 116 DQM6 DQM0 ~ 7 DQM

23 DQM0 24 DQM4 67 WE 68 CKE1 117 DQM3 118 DQM7 VDD Power supply (3.3V)

25 DQM1 26 DQM5 69 CS0 70 A12 119 VSS 120 VSS VSS Ground

27 VDD 28 VDD 71 CS1 72 *A13 121 DQ24 122 DQ56 SDA Serial data I/O

29 A0 30 A3 73 DU 74 CLK1 123 DQ25 124 DQ57 SCL Serial clock

31 A1 32 A4 75 VSS 76 VSS 125 DQ26 126 DQ58

DU Don′t use

33 A2 34 A5 77 NC 78 NC 127 DQ27 128 DQ59

NC No connection

35 VSS 36 VSS 79 NC 80 NC 129 VDD 130 VDD

37 DQ8 38 DQ40 81 VDD 82 VDD 131 DQ28 132 DQ60 * These pins are not used in this module.

39 DQ9 40 DQ41 83 DQ16 84 DQ48 133 DQ29 134 DQ61 ** These pins should be NC in the system

41 DQ10 42 DQ42 85 DQ17 86 DQ49 135 DQ30 136 DQ62 which does not support SPD.

43 DQ11 44 DQ43 87 DQ18 88 DQ50 137 DQ31 138 DQ63

45 VDD 46 VDD 89 DQ19 90 DQ51 139 VSS 140 VSS

47 DQ12 48 DQ44 91 VSS 92 VSS 141 **SDA 142 **SCL

49 DQ13 50 DQ45 93 DQ20 94 DQ52 143 VDD 144 VDD

SAMSUNG ELECTRONICS CO., Ltd. reserves the right to change products and specifications without notice.

Rev. 0.0 April 2000

M464S3254BT1 PC100 SODIMM

PIN CONFIGURATION DESCRIPTION

Pin Name Input Function

CLK System clock Active on the positive going edge to sample all inputs.

Disables or enables device operation by masking or enabling all inputs except

CS Chip select

CLK, CKE and DQM

Masks system clock to freeze operation from the next clock cycle.

CKE should be enabled at least one cycle prior to new command.

CKE Clock enable

Disable input buffers for power down in standby.

CKE should be enabled 1CLK+tSS prior to valid command.

Row/column addresses are multiplexed on the same pins.

A0 ~ A12 Address

Row address : RA0 ~ RA12, Column address : CA0 ~ CA8

Selects bank to be activated during row address latch time.

BA0 ~ BA1 Bank select address

Selects bank for read/write during column address latch time.

Latches row addresses on the positive going edge of the CLK with RAS low.

RAS Row address strobe

Enables row access & precharge.

Latches column addresses on the positive going edge of the CLK with CAS low.

CAS Column address strobe

Enables column access.

Enables write operation and row precharge.

WE Write enable

Latches data in starting from CAS, WE active.

Makes data output Hi-Z, tSHZ after the clock and masks the output.

DQM0 ~ 7 Data input/output mask

Blocks data input when DQM active. (Byte masking)

DQ0 ~ 63 Data input/output Data inputs/outputs are multiplexed on the same pins.

VDD/VSS Power supply/ground Power and ground for the input buffers and the core logic.

Rev. 0.0 April 2000

M464S3254BT1 PC100 SODIMM

FUNCTIONAL BLOCK DIAGRAM

CS1

CS0

DQM0 DQM4

LDQM CS LDQM CS LDQM CS LDQM CS

DQ0 DQ0 DQ0 DQ32 DQ0 DQ0

DQ1 DQ1 DQ1 DQ33 DQ1 DQ1

DQ2 DQ2 U0 DQ2 U4 DQ34 DQ2 U2 DQ2 U6

DQ3 DQ3 DQ3 DQ35 DQ3 DQ3

DQ4 DQ4 DQ4 DQ36 DQ4 DQ4

DQ5 DQ5 DQ5 DQ37 DQ5 DQ5

DQ6 DQ6 DQ6 DQ38 DQ6 DQ6

DQ7 DQ7 DQ7 DQ39 DQ7 DQ7

DQM1 UDQM UDQM DQM5 UDQM UDQM

DQ8 DQ8 DQ8 DQ40 DQ8 DQ8

DQ9 DQ9 DQ9 DQ41 DQ9 DQ9

DQ10 DQ10 DQ10 DQ42 DQ10 DQ10

DQ11 DQ11 DQ11 DQ43 DQ11 DQ11

DQ12 DQ12 DQ12 DQ44 DQ12 DQ12

DQ13 DQ13 DQ13 DQ45 DQ13 DQ13

DQ14 DQ14 DQ14 DQ46 DQ14 DQ14

DQ15 DQ15 DQ15 DQ47 DQ15 DQ15

DQM2 DQM6

LDQM CS LDQM CS LDQM CS LDQM CS

DQ16 DQ0 DQ0 DQ48 DQ0 DQ0

DQ17 DQ1 DQ1 DQ49 DQ1 DQ1

DQ18 DQ2 U1 DQ2 U5 DQ50 DQ2 U3 DQ2 U7

DQ19 DQ3 DQ3 DQ51 DQ3 DQ3

DQ20 DQ4 DQ4 DQ52 DQ4 DQ4

DQ21 DQ5 DQ5 DQ53 DQ5 DQ5

DQ22 DQ6 DQ6 DQ54 DQ6 DQ6

DQ23 DQ7 DQ7 DQ55 DQ7 DQ7

DQM3 UDQM UDQM DQM7 UDQM UDQM

DQ24 DQ8 DQ8 DQ56 DQ8 DQ8

DQ25 DQ9 DQ9 DQ57 DQ9 DQ9

DQ26 DQ10 DQ10 DQ58 DQ10 DQ10

DQ27 DQ11 DQ11 DQ59 DQ11 DQ11

DQ28 DQ12 DQ12 DQ60 DQ12 DQ12

DQ29 DQ13 DQ13 DQ61 DQ13 DQ13

DQ30 DQ14 DQ14 DQ62 DQ14 DQ14

DQ31 DQ15 DQ15 DQ63 DQ15 DQ15

A0 ~ A12, BA0 & 1 SDRAM U0 ~ U7

RAS SDRAM U0 ~ U7

Serial PD

CAS SDRAM U0 ~ U7 SDA

SCL

WE SDRAM U0 ~ U7 SA0 SA1 SA2 WP

CKE0 SDRAM U0 ~ U3

CKE1 SDRAM U4 ~ U7

10Ω

DQn Every DQ pin of SDRAM

U0/U4

U1/U5

VDD CLK0/1

Three 0.1 uF X7R 0603 Capacitors U2/U6

To all SDRAMs

per each SDRAM

Vss U3/U7

Rev. 0.0 April 2000

M464S3254BT1 PC100 SODIMM

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Value Unit

Voltage on any pin relative to Vss VIN, VOUT -1.0 ~ 4.6 V

Voltage on VDD supply relative to Vss VDD, VDDQ -1.0 ~ 4.6 V

Storage temperature TSTG -55 ~ +150 °C

Power dissipation PD 8 W

Short circuit current IOS 50 mA

Note : Permanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

DC OPERATING CONDITIONS AND CHARACTERISTICS

Recommended operating conditions (Voltage referenced to VSS = 0V, TA = 0 to 70°C)

Parameter Symbol Min Typ Max Unit Note

Supply voltage VDD 3.0 3.3 3.6 V

Input high voltage VIH 2.0 3.0 VDDQ+0.3 V 1

Input low voltage VIL -0.3 0 0.8 V 2

Output high voltage VOH 2.4 - - V IOH = -2mA

Output low voltage VOL - - 0.4 V IOL = 2mA

Input leakage current ILI -10 - 10 uA 3

Notes : 1. VIH (max) = 5.6V AC.The overshoot voltage duration is ≤ 3ns.

2. VIL (min) = -2.0V AC. The undershoot voltage duration is ≤ 3ns.

3. Any input 0V ≤ VIN ≤ VDDQ.

Input leakage currents include Hi-Z output leakage for all bi-directional buffers with Tri-State outputs.

CAPACITANCE (VDD = 3.3V, TA = 23°C, f = 1MHz, VREF = 1.4V ± 200 mV)

Parameter Symbol Min Max Unit

Input capacitance (A0 ~ A12, BA0 ~ BA1) CIN1 25 45 pF

Input capacitance (RAS, CAS, WE) CIN2 25 45 pF

Input capacitance (CKE0 ~ CKE1) CIN3 15 25 pF

Input capacitance (CLK0 ~ CLK1) CIN4 15 21 pF

Input capacitance (CS0 ~ CS1) CIN5 15 25 pF

Input capacitance (DQM0 ~ DQM7) CIN6 8 10 pF

Data input/output capacitance (DQ0 ~ DQ63) COUT 13 18 pF

Rev. 0.0 April 2000

M464S3254BT1 PC100 SODIMM

DC CHARACTERISTICS

(Recommended operating condition unless otherwise noted, TA = 0 to 70°C)

Version

Parameter Symbol Test Condition Unit Note

-1H -1L

Burst length = 1

Operating current

ICC1 tRC ≥ tRC(min) 700 mA 1

(One bank active)

IO = 0 mA

Precharge standby current ICC2P CKE ≤ VIL(max), tCC = 10ns 16

mA

in power-down mode ICC2PS CKE & CLK ≤ VIL(max), tCC =∞ 16

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = 10ns

ICC2N 128

Precharge standby current Input signals are changed one time during 20ns

mA

in non power-down mode CKE ≥ VIH(min), CLK ≤ VIL(max), tCC =∞

ICC2NS 112

Input signals are stable

Active standby current in ICC3P CKE ≤ VIL(max), tCC = 10ns 48

mA

power-down mode ICC3PS CKE & CLK ≤ VIL(max), tCC =∞ 48

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = 10ns

Active standby current in ICC3N 280 mA

Input signals are changed one time during 20ns

non power-down mode

(One bank active) CKE ≥ VIH(min), CLK ≤ VIL(max), tCC =∞

ICC3NS 240 mA

Input signals are stable

IO = 0 mA

Operating current Page burst

ICC4 720 mA 1

(Burst mode) 4Banks activated

tCCD = 2CLKs

Refresh current ICC5 tRC ≥ tRC(min) 980 mA 2

C 24 mA

Self refresh current ICC6 CKE ≤ 0.2V

L 16 mA

Notes : 1. Measured with outputs open.

2. Refresh period is 64ms.

3. Unless otherwise noted, input swing level is CMOS(VIH/VIL=VDDQ/VSSQ)

Rev. 0.0 April 2000

M464S3254BT1 PC100 SODIMM

AC OPERATING TEST CONDITIONS (VDD = 3.3V ± 0.3V, TA = 0 to 70°C)

Parameter Value Unit

AC input levels (Vih/Vil) 2.4/0.4 V

Input timing measurement reference level 1.4 V

Input rise and fall time tr/tf = 1/1 ns

Output timing measurement reference level 1.4 V

Output load condition See Fig. 2

3.3V Vtt = 1.4V

1200Ω 50Ω

VOH (DC) = 2.4V, IOH = -2mA

Output Output Z0 = 50Ω

VOL (DC) = 0.4V, IOL = 2mA

50pF 50pF

870Ω

(Fig. 1) DC output load circuit (Fig. 2) AC output load circuit

OPERATING AC PARAMETER

(AC operating conditions unless otherwise noted)

Version

Parameter Symbol Unit Note

-1H -1L

Row active to row active delay tRRD(min) 20 20 ns 1

RAS to CAS delay tRCD(min) 20 20 ns 1

Row precharge time tRP(min) 20 20 ns 1

tRAS(min) 50 50 ns 1

Row active time

tRAS(max) 100 us

Row cycle time tRC(min) 70 70 ns 1

Last data in to row precharge tRDL(min) 2 CLK 2,5

Last data in to Active delay tDAL(min) 2 CLK + 20 ns - 5

Last data in to new col. address delay tCDL(min) 1 CLK 2

Last data in to burst stop tBDL(min) 1 CLK 2

Col. address to col. address delay tCCD(min) 1 CLK 3

CAS latency=3 2

Number of valid output data ea 4

CAS latency=2 1

Notes : 1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time

and then rounding off to the next higher integer.

2. Minimum delay is required to complete write.

3. All parts allow every cycle column address change.

4. In case of row precharge interrupt, auto precharge and read burst stop.

5. For -1H/1L, tRDL=1CLK and tDAL=1CLK+20ns is also supported .

SAMSUNG recommends tRDL=2CLK and tDAL=2CLK + 20ns.

Rev. 0.0 April 2000

M464S3254BT1 PC100 SODIMM

AC CHARACTERISTICS (AC operating conditions unless otherwise noted)

REFER TO THE INDIVIDUAL COMPONENT, NOT THE WHOLE MODULE.

-1H -1L

Parameter Symbol Unit Note

Min Max Min Max

CAS latency=3 10 10

CLK cycle time tCC 1000 1000 ns 1

CAS latency=2 10 12

CAS latency=3 6 6

CLK to valid output delay tSAC ns 1,2

CAS latency=2 6 7

CAS latency=3 3 3

Output data hold time tOH ns 2

CAS latency=2 3 3

CLK high pulse width tCH 3 3 ns 3

CLK low pulse width tCL 3 3 ns 3

Input setup time tSS 2 2 ns 3

Input hold time tSH 1 1 ns 3

CLK to output in Low-Z tSLZ 1 1 ns 2

CAS latency=3 6 6

CLK to output in Hi-Z tSHZ ns

CAS latency=2 6 7

Notes : 1. Parameters depend on programmed CAS latency.

2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.

3. Assumed input rise and fall time (tr & tf) = 1ns.

If tr & tf is longer than 1ns, transient time compensation should be considered,

i.e., [(tr + tf)/2-1]ns should be added to the parameter.

Rev. 0.0 April 2000

M464S3254BT1 PC100 SODIMM

SIMPLIFIED TRUTH TABLE

Command CKEn-1 CKEn CS RAS CAS WE DQM BA0,1 A10/AP A12, A11 Note

A9 ~ A0

Register Mode register set H X L L L L X OP code 1,2

Auto refresh H 3

H L L L H X X

Entry L 3

Refresh Self

L H H H 3

refresh Exit L H X X

H X X X 3

Bank active & row addr. H X L L H H X V Row address

Read & Auto precharge disable L Column 4

column address H X L H L H X V address

Auto precharge enable H (A0 ~ A8) 4,5

Write & Auto precharge disable L Column 4

column address H X L H L L X V address

Auto precharge enable H (A0 ~ A8) 4,5

Burst stop H X L H H L X X 6

Bank selection V L

Precharge H X L L H L X X

All banks X H

H X X X

Clock suspend or Entry H L X

L V V V X

active power down

Exit L H X X X X X

H X X X

Entry H L X

L H H H

Precharge power down mode X

H X X X

Exit L H X

L V V V

DQM H X V X 7

H X X X

No operation command H X X X

L H H H

(V=Valid, X=Don′t care, H=Logic high, L=Logic low)

Notes : 1. OP Code : Operand code

A0 ~ A12 & BA0 ~ BA1 : Program keys. (@ MRS)

2. MRS can be issued only at all banks precharge state.

A new command can be issued after 2 clock cycles of MRS.

3. Auto refresh functions are as same as CBR refresh of DRAM.

The automatical precharge without row precharge command is meant by "Auto".

Auto/self refresh can be issued only at all banks precharge state.

4. BA0 ~ BA1 : Bank select addresses.

If both BA0 and BA1 are "Low" at read, write, row active and precharge, bank A is selected.

If both BA0 is "High" and BA1 is "Low" at read, write, row active and precharge, bank B is selected.

If both BA0 is "Low" and BA1 is "High" at read, write, row active and precharge, bank C is selected.

If both BA0 and BA1 are "High" at read, write, row active and precharge, bank D is selected.

If A10/AP is "High" at row precharge, BA0 and BA1 is ignored and all banks are selected.

5. During burst read or write with auto precharge, new read/write command can not be issued.

Another bank read/write command can be issued after the end of burst.

New row active of the associated bank can be issued at tRP after the end of burst.

6. Burst stop command is valid at every burst length.

7. DQM sampled at positive going edge of a CLK and masks the data-in at the very CLK (Write DQM latency is 0),

but makes Hi-Z state the data-out of 2 CLK cycles after. (Read DQM latency is 2)

Rev. 0.0 April 2000

M464S3254BT1 PC100 SODIMM

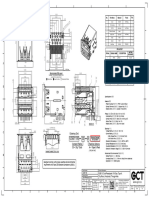

PACKAGE DIMENSIONS

Units : Inches (Millimeters)

2.66

(67.56)

2.50

(63.60) 2-R 0.078 Min

(2.00 Min)

0.16 ± 0.039

(4.00 ± 0.10)

(31.75)

1.25

(20.00)

0.79

(6.0)

0.24

1 59 61 143

0.13 0.91 1.29 2-φ 0.07

(3.30) (23.20) (32.80) (1.80)

0.18

(4.60)

0.083

(2.10)

0.10

(2.50)

Z Y

0.15

(3.70)

2 60 62 144

(2.540 Min)

0.100 Min

0.150 Max 0.024 ± 0.001

(3.80 Max) (0.600 ± 0.050)

(3.20 Min)

(4.00 Min)

0.157 Min

0.125 Min

0.16 ± 0.0039

(4.00 ± 0.10) 0.008 ±0.006

(0.200 ±0.150)

0.06 ± 0.0039

0.03 TYP

0.04 ± 0.0039 (1.50 ± 0.1)

(0.80 TYP)

(1.00 ± 0.10)

Detail Z Detail Y

Tolerances : ±.006(.15) unless otherwise specified

The used device is 16Mx16 SDRAM, TSOP

SDRAM Part No. : K4S561632B

Rev. 0.0 April 2000

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

You might also like

- Basic CNC Operations ManualDocument11 pagesBasic CNC Operations ManualDANG HOANG0% (1)

- Chapter1 - Basic Concepts & Computer - EvolutionDocument67 pagesChapter1 - Basic Concepts & Computer - EvolutionElias HedamoNo ratings yet

- Pc100 Sdram Module KMM366S1723T Preliminary: Revision HistoryDocument11 pagesPc100 Sdram Module KMM366S1723T Preliminary: Revision Historyfalco2010No ratings yet

- NT1GD64S8HA0FM / NT1GD64S8HB0FM 1GB: 128M X 64 PC2700 / PC2100 Unbuffered DDR SO-DIMM 200 Pin Unbuffered DDR SO-DIMM FeaturesDocument14 pagesNT1GD64S8HA0FM / NT1GD64S8HB0FM 1GB: 128M X 64 PC2700 / PC2100 Unbuffered DDR SO-DIMM 200 Pin Unbuffered DDR SO-DIMM FeaturesLuis Carlos Cardenas MancoNo ratings yet

- DDR1 SODIMM 512Mb Die BDocument18 pagesDDR1 SODIMM 512Mb Die BNeraw KozeyNo ratings yet

- A-Data: Synchronous DRAM 1M X 16 Bit X 4 Banks General Description FeaturesDocument9 pagesA-Data: Synchronous DRAM 1M X 16 Bit X 4 Banks General Description FeaturesJim LiebNo ratings yet

- 2 (1) M Words X 8 (16) Bits X 4 Banks (64-MBIT) Synchronous Dynamic RamDocument68 pages2 (1) M Words X 8 (16) Bits X 4 Banks (64-MBIT) Synchronous Dynamic RamФат Хыу НгуенNo ratings yet

- Product Sheet Ddr3 So DimmDocument3 pagesProduct Sheet Ddr3 So Dimmmartin sembinelliNo ratings yet

- Sdram: M12L2561616A (2S)Document45 pagesSdram: M12L2561616A (2S)api-432313169No ratings yet

- Datashet Etron TechDocument54 pagesDatashet Etron TechAndres OrjuelaNo ratings yet

- MH8S64DBKG - 7,-7L,-8,-8L: Preliminary SpecDocument56 pagesMH8S64DBKG - 7,-7L,-8,-8L: Preliminary Specthe_answerNo ratings yet

- Ts256mlq64v6u 2980 SDocument3 pagesTs256mlq64v6u 2980 SDaniel KupferNo ratings yet

- JM667QSJ-1G 2162 SDocument3 pagesJM667QSJ-1G 2162 Sgns_vcNo ratings yet

- 4GB Unbuffered Ddr3 Sdram Sodimm: HB3SU004GFM8DMA33 (512M Words X 64bits, 2 Rank)Document10 pages4GB Unbuffered Ddr3 Sdram Sodimm: HB3SU004GFM8DMA33 (512M Words X 64bits, 2 Rank)anon_616563053No ratings yet

- 256M As4c16m16d1Document67 pages256M As4c16m16d1sumitkumarNo ratings yet

- Operation Temperature Condition - 40 85 : Features General DescriptionDocument29 pagesOperation Temperature Condition - 40 85 : Features General DescriptionJuan GutierrezNo ratings yet

- Datasheet - HK M12l128168a 2875070 PDFDocument45 pagesDatasheet - HK M12l128168a 2875070 PDFحازم اشنينوNo ratings yet

- 64Mb Synchronous DRAM Specification: A3V64S40GTPDocument40 pages64Mb Synchronous DRAM Specification: A3V64S40GTPJeferson AndradeNo ratings yet

- Hy57v641620hg (16M)Document12 pagesHy57v641620hg (16M)vetchboyNo ratings yet

- Features: 200pin Unbuffered Ddr2 Sdram So-Dimms Based On 1Gb Version CDocument23 pagesFeatures: 200pin Unbuffered Ddr2 Sdram So-Dimms Based On 1Gb Version CAthal-wardNo ratings yet

- D42 27180S 001 DDR4 ECC SODIMM 3200 22 512x8 4GB S-3106771Document17 pagesD42 27180S 001 DDR4 ECC SODIMM 3200 22 512x8 4GB S-3106771ManunoghiNo ratings yet

- 2M X 32 Sdram: 512K X 32bit X 4 Banks Synchronous DRAM LVTTL (3.3V)Document12 pages2M X 32 Sdram: 512K X 32bit X 4 Banks Synchronous DRAM LVTTL (3.3V)vsc2012No ratings yet

- Sdram 1M X 16 Bit X 4 Banks: Synchronous DRAMDocument44 pagesSdram 1M X 16 Bit X 4 Banks: Synchronous DRAMvetchboyNo ratings yet

- ST7565R DatasheetDocument72 pagesST7565R DatasheetRaissan ChedidNo ratings yet

- D32 27245S 001 DDR4 ECC DIMM 3200 22 1024x8 8GB SA-3107331Document17 pagesD32 27245S 001 DDR4 ECC DIMM 3200 22 1024x8 8GB SA-3107331ManunoghiNo ratings yet

- M12L64164ADocument46 pagesM12L64164AivoroNo ratings yet

- D52 27244S 001 DDR4 REG DIMM 3200 22 1024x8 8GB SA-3107177Document17 pagesD52 27244S 001 DDR4 REG DIMM 3200 22 1024x8 8GB SA-3107177ManunoghiNo ratings yet

- Ddr3 Sdram Unbuffered Sodimms Based On 1Gb B-Die: Hmt164S6Bfr6C Hmt112S6Bfr6C Hmt125S6Bfr8CDocument51 pagesDdr3 Sdram Unbuffered Sodimms Based On 1Gb B-Die: Hmt164S6Bfr6C Hmt112S6Bfr6C Hmt125S6Bfr8COrlando SedamanoNo ratings yet

- 4GB Registered DDR2 SDRAM DIMM: EBE41AE4ACFA (512M Words 72 Bits, 2 Ranks)Document27 pages4GB Registered DDR2 SDRAM DIMM: EBE41AE4ACFA (512M Words 72 Bits, 2 Ranks)ramgopalreddykNo ratings yet

- D32 27306S 001 DDR4 ECC DIMM 3200 22 2048x8 32GB S-3106760Document17 pagesD32 27306S 001 DDR4 ECC DIMM 3200 22 2048x8 32GB S-3106760ManunoghiNo ratings yet

- Memory Module Specifications: KVR667D2D4F5/2G 2GB 256M X 72-Bit PC2-5300 Cl5 Ecc 240-Pin FbdimmDocument7 pagesMemory Module Specifications: KVR667D2D4F5/2G 2GB 256M X 72-Bit PC2-5300 Cl5 Ecc 240-Pin FbdimmHippyKillerNo ratings yet

- EM638165TS Rev3.2Document51 pagesEM638165TS Rev3.2Elnino HartonoNo ratings yet

- 128Mb Synchronous DRAM Specification: A3V28S40JTPDocument40 pages128Mb Synchronous DRAM Specification: A3V28S40JTPCarlos Alonso Gonzalez VazquesNo ratings yet

- ¡ Semiconductor: DescriptionDocument40 pages¡ Semiconductor: DescriptionOrangelin SantaellaNo ratings yet

- 128mbit DDR SDRAM: Revision 1.3 August 2001Document19 pages128mbit DDR SDRAM: Revision 1.3 August 2001Juan SilvaNo ratings yet

- Em63a165ts v1Document51 pagesEm63a165ts v1api-432313169No ratings yet

- ST7565RDocument72 pagesST7565Rjon_scribd2372No ratings yet

- K4D261638FDocument18 pagesK4D261638F9183290782No ratings yet

- MSM5416273 50GS K - To - MSM5416273 70GS KDocument41 pagesMSM5416273 50GS K - To - MSM5416273 70GS KDiego SerranoNo ratings yet

- A3S56D30FTP ZentelDocument40 pagesA3S56D30FTP Zenteldata binkusNo ratings yet

- 128M (8Mx16) GDDR SDRAM: HY5DU281622ETDocument34 pages128M (8Mx16) GDDR SDRAM: HY5DU281622ETBoris LazarchukNo ratings yet

- EM638165TS-5G ChipDocument53 pagesEM638165TS-5G ChipAlberto BalintNo ratings yet

- MT48LC1M16A1Document51 pagesMT48LC1M16A1NalsonNo ratings yet

- M12l64164a (2y) PDFDocument45 pagesM12l64164a (2y) PDFTeddy KhantNo ratings yet

- 128mbit SDRAM: 2M X 16bit X 4 Banks Synchronous DRAM LVTTLDocument11 pages128mbit SDRAM: 2M X 16bit X 4 Banks Synchronous DRAM LVTTLThiago Cristiano TavaresNo ratings yet

- R11-0852 - SU3B1333B2G9 - DDR3-1333 - CL9 - 2GB - 128Mx8 - Halogen Free - ECC SO-DIMM - V0Document17 pagesR11-0852 - SU3B1333B2G9 - DDR3-1333 - CL9 - 2GB - 128Mx8 - Halogen Free - ECC SO-DIMM - V0Raul AlfaroNo ratings yet

- HB52E328EM-A6B Módulo de MemoriaDocument19 pagesHB52E328EM-A6B Módulo de MemoriaIgnacio Romero ANo ratings yet

- EM63B165TS - Rev 2.0Document53 pagesEM63B165TS - Rev 2.0silva_marcosrNo ratings yet

- HY57V561620Document13 pagesHY57V561620Saleem BegNo ratings yet

- 128M (4Mx32) GDDR SDRAM: HY5DU283222AFDocument32 pages128M (4Mx32) GDDR SDRAM: HY5DU283222AFAlfonso BasileNo ratings yet

- D22 27308S 001 DDR4 SODIMM 3200 22 2048x8 32GB SA - 3106646Document17 pagesD22 27308S 001 DDR4 SODIMM 3200 22 2048x8 32GB SA - 3106646ManunoghiNo ratings yet

- 196 124334 HT16C21Document34 pages196 124334 HT16C21jeeep32No ratings yet

- AT93CXXDocument15 pagesAT93CXXcallkalaiNo ratings yet

- DS1501/DS1511: Y2K-Compliant Watchdog Real-Time ClocksDocument20 pagesDS1501/DS1511: Y2K-Compliant Watchdog Real-Time Clocksfulk1989No ratings yet

- MSM6544Document13 pagesMSM6544Shuvamay GuhaNo ratings yet

- Uveprom: Austin Semiconductor, IncDocument11 pagesUveprom: Austin Semiconductor, Incpuh1967No ratings yet

- Si 5326Document72 pagesSi 5326林俊成No ratings yet

- Features Description: DD DDQ DD DDQDocument35 pagesFeatures Description: DD DDQ DD DDQLucas EgidioNo ratings yet

- 256K X 16 4Mb Asynchronous SRAMDocument14 pages256K X 16 4Mb Asynchronous SRAMThein Htoon lwinNo ratings yet

- 42 45SM RM Vm32160e 276692Document34 pages42 45SM RM Vm32160e 276692asdNo ratings yet

- MemoriaDocument7 pagesMemoriaEduardo TaglialavoreNo ratings yet

- USB1100Document2 pagesUSB1100dinhdtdNo ratings yet

- 2575T-12 NationalSemiconductorDocument27 pages2575T-12 NationalSemiconductordinhdtdNo ratings yet

- Data Sheet Acquired From Harris Semiconductor SCHS093C Revised October 2003Document23 pagesData Sheet Acquired From Harris Semiconductor SCHS093C Revised October 2003dinhdtdNo ratings yet

- Tps 54610Document32 pagesTps 54610dinhdtdNo ratings yet

- AD9971Document2 pagesAD9971dinhdtdNo ratings yet

- TEMI2000 Comm (Eng)Document62 pagesTEMI2000 Comm (Eng)dinhdtdNo ratings yet

- DDR1 Sdram 3.3V - 184 Pin - UdimmDocument15 pagesDDR1 Sdram 3.3V - 184 Pin - UdimmdinhdtdNo ratings yet

- DRV 8801Document34 pagesDRV 8801dinhdtdNo ratings yet

- Schematics Dell 5559 3559 LA-D071P R10Document64 pagesSchematics Dell 5559 3559 LA-D071P R10dinhdtdNo ratings yet

- Kavo 4425 4426 Easydrive ConverterDocument70 pagesKavo 4425 4426 Easydrive ConverterdinhdtdNo ratings yet

- TORX173 ToshibaSemiconductorDocument7 pagesTORX173 ToshibaSemiconductordinhdtdNo ratings yet

- Operation: Hydraulic, Heated, Plural Component ProportionerDocument40 pagesOperation: Hydraulic, Heated, Plural Component ProportionerdinhdtdNo ratings yet

- 300ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatorDocument11 pages300ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatordinhdtdNo ratings yet

- Maapc900-Eng V1.51 PDFDocument559 pagesMaapc900-Eng V1.51 PDFdinhdtdNo ratings yet

- Features: Mau200 SeriesDocument4 pagesFeatures: Mau200 SeriesdinhdtdNo ratings yet

- National VP-8177a Fm-Am Signal GeneratorDocument42 pagesNational VP-8177a Fm-Am Signal GeneratordinhdtdNo ratings yet

- CNC PDFDocument876 pagesCNC PDFdinhdtdNo ratings yet

- En DM00093903Document36 pagesEn DM00093903anjanNo ratings yet

- CH 2 Input Output Memory DeviceDocument14 pagesCH 2 Input Output Memory DeviceChandrasekhar ShirolkarNo ratings yet

- Forouzan 5Document41 pagesForouzan 5Angelo ViniciusNo ratings yet

- CS NotezDocument207 pagesCS Notezcollins chinsungweNo ratings yet

- Unit 1 Inside The PC Core ComponentsDocument85 pagesUnit 1 Inside The PC Core Componentskasyap raut100% (2)

- STM32H7 Series Product OverviewDocument65 pagesSTM32H7 Series Product OverviewMichelangelo VetrugnoNo ratings yet

- User Manual: Published February 2004Document36 pagesUser Manual: Published February 2004Ion CausNo ratings yet

- Computer Organization and Assembly Language: Laboratory ManualDocument25 pagesComputer Organization and Assembly Language: Laboratory ManualMohd ShahNo ratings yet

- 5SVA User's ManualDocument38 pages5SVA User's ManualTommy NagyNo ratings yet

- GROUP 4 - Memory and Power Supply, Their Common Problem and SolutionDocument31 pagesGROUP 4 - Memory and Power Supply, Their Common Problem and SolutionOluwatimilehin AdebajoNo ratings yet

- Mutter CourageDocument39 pagesMutter CourageFederico PittoNo ratings yet

- Dell H815dw S2815dn DiagDocument80 pagesDell H815dw S2815dn DiagTaur1968No ratings yet

- 2011 AL ICT Model Paper EnglishDocument18 pages2011 AL ICT Model Paper EnglishSasika Pamuditha0% (1)

- Question BankDocument10 pagesQuestion BankgurugovanNo ratings yet

- CSS NCII ModuleDocument213 pagesCSS NCII Moduletonet enteaNo ratings yet

- DRAM Command GuideDocument2 pagesDRAM Command Guidepacot24No ratings yet

- EPD Unit 4 SlidesDocument79 pagesEPD Unit 4 SlidesAdvaith S . KumarNo ratings yet

- Lecture 10: Memory System - Memory Technology: CSE 564 Computer Architecture Summer 2017Document44 pagesLecture 10: Memory System - Memory Technology: CSE 564 Computer Architecture Summer 2017Richu GuptaNo ratings yet

- SramDocument31 pagesSramParth RamanujNo ratings yet

- ZX Spectrum Service ManualDocument60 pagesZX Spectrum Service ManualTudor StanciuNo ratings yet

- Continued From Part-1: The Patent Office Journal No. 50/2021 Dated 10/12/2021 60292Document686 pagesContinued From Part-1: The Patent Office Journal No. 50/2021 Dated 10/12/2021 60292safsdaNo ratings yet

- Computer Fundamentals Bba 1st SemDocument22 pagesComputer Fundamentals Bba 1st SemRahul Gupta79No ratings yet

- Different Types of RAM SDRAM (Synchronous DRAM)Document2 pagesDifferent Types of RAM SDRAM (Synchronous DRAM)Pro KodigoNo ratings yet

- How To Check MemoryDocument15 pagesHow To Check MemoryNimbark HirenkumarNo ratings yet

- Memory InterfacingDocument29 pagesMemory Interfacingabhi198808No ratings yet

- BIOS SettingDocument8 pagesBIOS Settingmagdiel joelNo ratings yet

- DFI 3p1Document147 pagesDFI 3p1Lee Yuan-ShengNo ratings yet

- Memory Hierarchy Design: A Quantitative Approach, Fifth EditionDocument112 pagesMemory Hierarchy Design: A Quantitative Approach, Fifth EditionErz SeNo ratings yet