Professional Documents

Culture Documents

Algorithm For Compiling Unrestricted Ladder Diagra

Algorithm For Compiling Unrestricted Ladder Diagra

Uploaded by

Longphi GameOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Algorithm For Compiling Unrestricted Ladder Diagra

Algorithm For Compiling Unrestricted Ladder Diagra

Uploaded by

Longphi GameCopyright:

Available Formats

See discussions, stats, and author profiles for this publication at: https://www.researchgate.

net/publication/289945343

Algorithm for Compiling Unrestricted Ladder Diagram to IEC 61131-3

Compliant Instruction List

Article · July 2011

CITATIONS READS

2 450

3 authors, including:

Kando Hamiyanze Moonga

University of Johannesburg

7 PUBLICATIONS 17 CITATIONS

SEE PROFILE

All content following this page was uploaded by Kando Hamiyanze Moonga on 10 July 2018.

The user has requested enhancement of the downloaded file.

Proceedings of the World Congress on Engineering 2011 Vol II

WCE 2011, July 6 - 8, 2011, London, U.K.

Algorithm for Compiling Unrestricted Ladder

Diagram to IEC 61131-3 Compliant Instruction

List

Kando Hamiyanze Moonga, Member IAENG, You Linru, and Liu Shaojun

LD to IL code on an unrestricted LD. The only restrictions if

Abstract—The paper presents an algorithm for generation of any are made during LD network to topological network

Instruction List (IL) code from Programmable Logic conversion.

Controllers (PLC) Ladder Diagram (LD) based on treating LD We propose a Two Stack Depth First Search (TSDFS)

as a tree with single root left bar and treating LD components

separately in accordance with their type. In this algorithm we

algorithm to traverse the LD tree as presented in this paper.

use virtual nodes, and they play a central role in the whole The TSDFS algorithm uses virtual nodes, which are merging

algorithm implementation. The LD is presented as an activity and splitting points, and takes advantage of LD semantics and

on vertex (AOV) diagraph. Then we establish activity on a IL semantics relationships to traverse a LD diagraph and

vertex to transform LD to IL. Nodes are treated according to convert it to IL code. It requires a parser to convert the LD

their type and the topological sorting of the AOV diagraph. The network to a format that can easily be traversed by the

algorithm is a general transformation algorithm for

transformation from any complex LD to IL. It has been applied

algorithm.

in the design of a software PLC and successfully compiled to IL. The algorithm is very simple but extremely effective in

code generation. It does not need to convert the LD

Index Terms— AOV diagraph, IEC 61131-3 standard, topological map into any other tree. It loads the LD

Instruction list, programmable logic controllers PLC, topological map and output IL code to file.

unrestricted ladder diagram The semantics of LD and IL does not necessitate a binary

tree to compile to IL. The two program semantics, the LD and

IL networks have a very close relationship which makes code

I. INTRODUCTION generation very interesting and can be converted between the

A programmable logic controller (PLC) is a digital logic

device and has been in use since the 1960s. At that time

it was meant to replace hard wired electromechanical

two.

II. GRAPH THEORY AND DATA STRUCTURES

switches and circuits from the automation industry. The From computer science theory, a graph G = (V, E) is

initial programming language therefore resembles to circuit

defined by a set of vertices V, and a set of edges E. In

diagram and is known as Ladder Diagram (LD). Today there

modeling networks the vertices may represent various

are various low programming languages among these is the

entities such as cities and junctions in road networks. There

low level Instruction List (IL) which has assembly language

mnemonics and is used on embedded platforms as it can be are different types of graphs: directed and undirected graphs,

converted directly to binary code. The IEC 61131-3 standard weighted and un weighted graphs, cyclic and acyclic graphs.

is an international standard meant to unify the programming Trees are connected acyclic undirected graphs. A graph can

languages on PLC. Both LD and IL are contained in this be represented as using a matrix M with adjacency matrix or

standard. adjacency list.

This paper proposes an algorithm for code generation from A directed acyclic graph (DAG) is a digraph that has no

directed cycles. A topological ordering of a digraph is a

numbering v1, ..., vn of the vertices such that for every edge

Manuscript received February 22, 2011; revised March 23, 2011.

Kando Hamiyanze Moonga was with Otis Elevators, Zambia, he is now a

(vi , vj), we have i < j Therefore a topological ordering

Staff Development Fellow at the University of Zambia, Lusaka, Zambia, and satisfies the vertex precedence constraints.

a masters student in automation at South China University of Technology, The in degree of a vertex is the number of edges incident to

Guangzhou, 510640 China (phone: 02-038672340; e-mail:

the vertex and the out degree is the number of edges from the

moonga2002@yahoo.com).

You Linru is a Professor in the School of Automation at South China vertex.

University of Technology, Guangzhou, 510640 China (e-mail:

aulryou@scut.edu.cn). Theorem

Liu Shaojun is an Assistant Professor in the School of Automation, South

China University of Technology, Guangzhou, 510640 China (e-mail: A digraph admits a topological ordering if and only if it is a

shjliu@scut.edu.cn). DAG.

ISBN: 978-988-19251-4-5 WCE 2011

ISSN: 2078-0958 (Print); ISSN: 2078-0966 (Online)

Proceedings of the World Congress on Engineering 2011 Vol II

WCE 2011, July 6 - 8, 2011, London, U.K.

by the fact that any node can have utmost two branches. If

III. SEMANTIC REPRESENTATION OF LADDER DIAGRAM the out degree in an AOV diagraph is 1, representing the

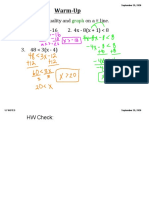

Figure 1 gives a semantic representation of ladder diagram. series ‘AND’ relations between the vertex and its successor

Details on LD semantics are analyzed in [1]. vertices, then we should create an ‘AND’ node in binary tree.

If the out degree of a vertex in an AOV diagraph is equal or

Netw1 greater than 2, representing the parallel ‘OR’ relations

between the vertex and its successor vertices, then we should

create an ‘OR’ node in binary tree. Finally the binary tree is

traversed by postorder algorithm and each leaf node forms an

J IL program, but the leaf node which corresponds to a virtual

node in the AOV diagraph can not form any instruction”. In

[4] an AOV diagraph is used to compile directly from LD to

Interval

Structured Text Language, STL.

In this paper we compile LD to IL code directly from the

AOV diagraph. With this algorithm we relax the restrictions

on LD to compile to IL and we develop a clear and concise

Netw2 direct relationship between the two languages which has in

the past hampered the flexibility on compiling from ladder

diagram to IL as noted in [3] or instruction list to LD. We use

depth first search (dfs) to traverse the graph and generate IL.

The algorithm uses the fact that no any node has in degree or

out degree greater than one. Only virtual nodes will have out

degree or in degree greater than one, these are therefore used

to control the dfs algorithm for parallel networks. Fig.2 is

based on the LD in Fig.1 and gives the designation for

various nodes used in this paper.

Fig. 1. Ladder Diagram with Two Networks or Rungs This paper will use the following notations: Source nodes

will be denoted as sNODE, terminal or sink node as tNODE,

Since LD networks were adopted from circuit theory, the virtual nodes as xNODE and function blocks as fNODEs,

rules that would apply are similar to those of electric current contact nodes as bNODEs. We also have special node types

and therefore reverse current is not allowed as done in these are ftNODEs and fsNODEs. These nodes are associated

circuits where diodes direct current direction. The LD with function blocks, and are very important to correctly

network restricts current direction where we get the left bar generate the code for complex networks with various types of

as source and we traverse as indicated by arrows or adjacency function blocks including non standard function blocks. The

when presented as a graph. xNODEs, sNODEs, ftNODEs and fsNODEs help to make

decisions during graph traversal and code generation.

IV. LADDER DIAGRAM AS A GRAPH OR TOPOLOGICAL

NETWORK V. LD NETWORK (GRAPH) AS A LD TREE

LD semantics simplifies the analysis of a graph created A LD presented as a diagraph can be considered as a tree

based on LD. A graph created directly from LD semantics with the root as a single entity left bar.

assumes diagraph as shown in Fig.2. Taking the left bar as a In this paper we present a different notion of a tree as

source node, it will have only one source node, the left bar to opposed to general computer science theory on trees as

traverse the entire graph. It can have several sink nodes as the branches will be allowed to merge and split. This is what we

application allows, but these have out degree equal to zero shall mean here by a tree:

and in degree equal to one, the source has in degree equal to 1) The left bar holds roots or it’s the ground that hold the

zero and can have plenty of out degree depending on your roots, like all natural trees grow from the ground, but the

application. Then all the other nodes have in degree and out ground is one entity. All roots are found in this same

degree equal to one. Then virtual nodes are required to ground. Given a forest therefore, though naturally roots

represent the interconnection for parallel network. Virtual will be different, the ground is still the same and it

nodes have in degree or out degree greater than or equal to supplies water to all the branches and leaves of all the

one. Given the source then we can begin to generate code by trees in a forest. This is true with the left bar on LD

depth first traversal till we reach a virtual node. networks and therefore true on any graph drawn from the

Most algorithms are based on converting the LD graph to a LD network no matter how complex the LD maybe,

binary tree [7], [2], and use binary tree traversal algorithms taking note of item 3 below. With this approach

such as postorder. Others [3] have used Two Terminal Series therefore, a LD network can never be a forest, but can be

Parallel, TTSP algorithm and then binary decomposition tree. a complex tree with one root. The root has in degree

In binary tree form, all the nodes are considered as leaves. zero.

“The left bar is the root of the binary tree. It is characterized 2) As opposed to binary tree representation where all nodes

ISBN: 978-988-19251-4-5 WCE 2011

ISSN: 2078-0958 (Print); ISSN: 2078-0966 (Online)

Proceedings of the World Congress on Engineering 2011 Vol II

WCE 2011, July 6 - 8, 2011, London, U.K.

are leaves including virtual nodes, here the output nodes Input: LD Topological map or AOV diagraph

Output: IL

on LD are considered as leaves, and that’s the furthest

we can go in the tree from the root. These nodes have out 1. Initialize:

degree zero. Start node Stack:=empty

3) The virtual nodes allow merging of branches and End node Stack:=empty

All other variables initialized.

splitting of branches. Split branches will also lead to Load the Root ID into Start node Stack equivalent to sNODE out

other leaves which are terminal nodes. Therefore the LD degree each time incrementing the start index. Start index to point

graph has trees and branches merging or splitting. to sNODE the Root, on top of stack. Now pop the top of stack

and assign to the Depth First Search (DFS) proceed to 2.

4) Traversal within a branch is allowed only from the root

to towards the leaves just as water moves from the roots 2. begin (At start node Get the unvisited adjacent )

towards leaves through branches. while (there are bNODEs proceed with DFS algorithm and

generate IL code for the branch till you reach a tNODE or

5) All leaves are reachable from the root, or otherwise xNODE)

error; graph does not meet the LD semantics. if ( xNODE proceed to 3)

6) All nodes along a simple branch have in degree one and else if ( tNODE go to 7)

out degree one. else go to 10

3. At xNODE check node status;

Secondly we add constraints to satisfy LD semantic. if (we are meeting this xNODE for the first time) go to 4

else (top of end index points to this xNODE pop End node Stack

and go to 5)

4. Make this xNODE as an end node and put it’s ID on End

node Stack equivalent to its in degree each time incrementing

the end index. Then go to 5

5. Process this xNODE and increment the in degree processing

bNODE

count for this node.

if(the in degree processing count equal to the xNODE in degree)

bNODE

go to 6

tNODE

else if (Start node Stack not empty) get the start node ID from

bNODE

stack by popping Start node Stack assign ID to DFS then go to

2

sNODE xNODE bNODE xNODE bNODE bNODE

xNODE else go to10.

bNODE

6. Make this node a start node, put its ID on Start node Stack

equivalent to its out degree

bNODE bNODE

bNODE bNODE

if (Start node Stack not empty,) pop the Start node Stack

assign ID to DFS and then go to 2

bNODE xNODE xNODE xNODE

tNODE else go to 10.

7. Process this tNODE then

bNODE if (Start node Stack is empty ) proceed to 8

ftNODE fNODE fsNODE

Root else pop the Start node Stack assign to DFS and then go to 2

Function block Terminal

Entry with in degree point

i 8. if (End node Stack empty and statistic check correct) proceed

and out degree At leaf

to 9

equal to one else go to 10

9. Code generation successful

Fig.2. Ladder Diagram AOV diagraph as Interconnected Trees with exit (Normal)

Merging Branches

10. Code generation failure. Encountered an error,

exit (error)

The vertical bar for the sNODE in Fig.2 implies that you can have many

other complex branches rooted at sNODE, but the the algorithm still

stands and it will terminate correctly at the last branch on the furthest Fig.3 Two Stack Depth First Search Algorithm

leaf that is the tNODE from the source. Termination of code

generation is done at a terminal node and not at any other During loading entries on end stack, if End node Stack is

node, otherwise error. an array, and the xNODE index is 5, and the xNODE has in

degree equal to 3, then we put 3 entries in the End node Stack

each time incrementing the End node Index, which is used to

index the array. If using pointers, then three entries have to be

VI. TWO STACK DEPTH FIRST SEARCH IL CODE GENERATION entered and the pointer incremented each time we do an entry

ALGORITHM to point to top of stack. Then you need to pop three times in

order to exhaust the entries from stack for this xNODE.

We now propose a Two Stack Depth First Traversal Similarly you do the same for the start nodes for the entries in

algorithm to generate instruction list. This algorithm uses the the Start node Stack.

power of recursion to traverse the given tree and two stacks; In the algorithm the word process implies write the label,

one for start nodes and one for end node. opcode, operand\s and comments to file for the IL instruction.

ISBN: 978-988-19251-4-5 WCE 2011

ISSN: 2078-0958 (Print); ISSN: 2078-0966 (Online)

Proceedings of the World Congress on Engineering 2011 Vol II

WCE 2011, July 6 - 8, 2011, London, U.K.

In addition to this algorithm there are a few control boolean VIII.GENERATING IL CODE FROM FUNCTION BLOCKS AND

variables to ensure we get the correct semantics for the IL. MATHEMATICAL EXPRESSIONS

These they help to make decisions about what opcode and Mathematical expressions are considered as function

operand to use, especially at the sNODE and xNODE but blocks. This separates the code that transverse the graph from

they are not relevant for this paper. Decisions are such as ‘LD the code embedded in the function blocks or mathematical

helper’, or ‘LD %B0’. Each node keeps its element type. expressions. In this way then a mathematical expression is

These are LD element types such as input, input not, jump,etc. simply a node and at first can be considered to be a black box

Then the code generation can be embedded into a switch except its instance designation and if using EN and ENO

statement. Opcodes such as OR and or with modifiers as boolean variables. EN is considered as a special terminal

specified in IEC61131-3 are found at xNODEs; ST, STN and node, ftNODE which points to a particular function block

JMP etc are found at tNODEs; AND, ANDN are met along a instance. It is considered as a terminal node in IL code while

particular branch. The CAL and CALC are found at fNODEs. non terminal as regards to TSDFS algorithm as it has out

Additional commands are embedded in function blocks; such degree equal to one and it’s adjacent is the function block.

as ADD, MUL, SQRT, DIV,GT,GE etc these could be Therefore an fNODE is preceded by at least one ftNODE and

mathematical expressions as explained in section 8. It could succeeded by at least one fsNODE. The ftNODEs and

also be a sub program or routine or data structures such as fsNODEs could be more than one on a function block. When

arrays. this is the case the function block will be treated like an

xNODE all the in degree is processed and then finally we call

VII. STATISTICS CHECK FOR CONFORMANCE TO LD SEMANTICS the function block then we proceed to execute on its out

Once we begin the traversal, successful exit is only degree.

allowed at a tNODE, unless we encountered an error. During Only one ftNODE should point to the function block, this

code generation if the start stack becomes empty and end is the node that invokes the function block.

stack is also empty and we are at a terminal node, tNODE, Certain function blocks are independent from the rest of the

then this implies we have traversed the entire graph and network. These connect direct to the root and can be called

reached all the nodes and therefore each time we reach a even at the beginning of scan cycle depending on

terminal node we check whether our start stack and end stack implementation, by unconditional call, CAL.

are empty. In fact checking of stacks is done each time we The example code given in Fig.4 was generated from the

pop from stack. Both must be empty at the same time when Ladder diagram in Fig.1. %DT0.Q is considered as a special

we are at a tNODE. If not we pop the start node and go to that source node, fsNODE it succeeds the function block node

node and traverse the unvisited branch using DFS. Of course and the function block node designation will point to this

you can add other error checking mechanism, but the ones node, and each node keeps all the necessary variables for

presented here ensure that the traversal was done correctly invocation. %DT0.Q is a derived variable from the instance

and the graph was drawn to LD semantics, otherwise the name and it’s an output variable. With regard to IL code

graph does not meet LD semantics. semantics it is a source node, while with regard to TSDFS it’s

At termination all statistics are checked to ensure the graph not a source node as it has in degree equal to one. Other

was correct and the generated code is correct. We carry out a functions will have other data types and variables as inputs

count of all the processed node types, that’s fNODEs, and out puts but the reasoning remains the same. Separate

bNODEs, tNODEs, fsNODEs, ftNODEs and sNODEs. Then algorithms then evaluate the mathematical expressions and

we compare with the statistics generated by the LD to graph the code is appended to the instruction list to have a complete

parser and should tally otherwise error. As an example if you code generation. Part of the code could be from library

have an unconnected node from Ladder diagram, then it functions.

won’t be reached from the root, and if the node count is %DT0 is an instance of a library function. The function

correct from the LD to graph parser, then the node count from instance is established by invoking the function block with

the TSDFS will be less by that particular node. If there are parameters to execute. Whilst in ladder you need to draw

any reductions required for the network are done by the LD these instances separately, on IL you just provide parameters

to graph parser, and the final result presented to the TSDFS is and space to keep these parameters and that creates this

as required for the IL code. It is worth also to note that though instance. Assuming on your software PLC you have the

termination is done at a tNODE, further check of the entire given library function.

code is required to ensure correctness. For example a tNODE In [3, Fig 5] is a similar network to Netw2. Such a network

could be a JMP statement and the label operand to the JMP could not be easily converted into IL using the TTSP

opcode might not exist therefore a warning should be issued algorithm used in that paper. In this paper we generate the

by the compiler, jumping to a non existent label. code for such networks. In fact Netw1 is even more complex.

Function blocks present a challenge and therefore these The algorithm enters at the root, meets %I0 line 1 and exits at

should be presented in the correct way in order to produce output %Q3, line 48 with the IL code.

correct code. In the next section we present an analysis on the

function blocks for the code generation based on the TSDFS

algorithm.

ISBN: 978-988-19251-4-5 WCE 2011

ISSN: 2078-0958 (Print); ISSN: 2078-0966 (Online)

Proceedings of the World Congress on Engineering 2011 Vol II

WCE 2011, July 6 - 8, 2011, London, U.K.

1 Netw1: LDN %I0 36 Netw2: LD %I7 IX. IMPLEMENTATION OF NON STANDARD FUNCTION BLOCKS

2 OR ( 37 AND %I8 TO COMPLY WITH IEC61131-3 STANDARD.

3 LDN %I6 38 OR (

4 OR ( 39 LD %I9 In this section we shall interchangeably use function and

5 LD %I4 40 ST helper3 function block. The difference between a function and a

6 ANDN %I5 41 AND %I10

7 ) 42 )

function block is the former has no memory while the latter

8 ANDN %I1 43 AND %B10 has memory.

9 ) 44 OR ( The use of function blocks on LD allows highly complex

10 OR ( 45 LD helper3 manipulation of non Boolean data to be done on LD networks.

11 LD %I2 46 AND %I13

12 ST helper1 47 ) Since LD is Boolean, a function or function block must be

13 AND %I3 48 ST %Q3 preceded by at least one Boolean input and at least one

14 ) Boolean output. These allow LD to give a call to the function

15 ST helper2

16 ANDN %B0

block and present a Boolean output based on the result of the

17 OR ( evaluation to the function block. The IEC 61131-3 standard

18 LD helper2 introduced EN as input variable and ENO as output variable

19 ANDN %B2 for standard function blocks. When EN is true, then the

20 AND %B1

21 ) function block will be executed. A successful evaluation of

22 ST %Q0 the function will set ENO. IEC 61131-3 allows non standard

23 ANDN %B4 function blocks as well. Other Boolean variables can be

24 OR (

25 LD helper2

added to functions or function blocks and then these can be

26 ANDN %B3 connected to the rest of the LD thereby creating a complex

27 OR ( network.

28 LD helper1

29 AND %I15 (*system dependent implementation of absolute time, say linux epoch*)

30 )

31 ST EN FUNCTION_BLOCK D_TOD

32 CALC %DT0 (PDT: =T#1268976547s, interval: =T#3600s) VAR_INPUT

33 LD %DT0.Q interval: TIME; (*in seconds*)

34 ) PDT: TIME; (*Preset date and time as absolute

35 JMP Netw3 time in seconds, ref system epoch*)

END_VAR

LD %SW0 (*system abs time in s*)

Fig.4 Generated Instruction List GT PDT

ST Q (*Boolean variable*)

The algorithm uses a ‘Look ahead’ function which returns JMPC LABEL

RET

the number of nodes from a given starting node (sNODE or LABEL:LD PDT

xNODE) to a given end node (xNODE) or till we meet a ADD interval

tNODE. The returned value helps to decide the opcode and ST PDT

END_FUNCTION_BLOCK

operand to use at the start of another branch in parallel

branches, whether to use ‘OR’ without modifier or ‘OR ‘and %DT0: D_TOD;

‘(‘modifier or ‘OR’ and ‘N’ modifier. Also when the out

degree is greater than one at an xNODE, we need to decide Fig.5 Example of a Library Function

whether to ‘ST helper’ or not when moving away from an

xNODE. All non Boolean calculations are done by the system on

In Fig.4 line 21 the ‘OR’ branch ends and the parallel which the LD is running. Code from any of these function

network ends but another parallel network begins on the out blocks is generated separately and then appended. For

degree of the xNODE. By help of a ‘Look ahead’, we do not embedded systems it can be assumed therefore that a

‘ST helper’ though out degree is two. The code on line 22 compliant PLC system supports all the standard functions

implies store Current Result (CR) to %Q0 and retain the and function block unless specified by the manufacturer.

contents of CR. %Q0 <— CR, CR does not change, then we Therefore a declaration of the instance variable based on the

‘ANDN’ CR with the next operand %B4 on line 23, this standard function block and call to the function block with

changes the contents of CR. required parameters is enough to have portable code. For non

Line 31 is useless in this code snippet since invoking the standard function block you need to declare the function

function block is based on the CR for a conditional call and block, and then declare the instance variables.

EN is not used anywhere else rendering it useless. Could be Fig.5 gives an example of a declaration of a function block

useful if we had had other Boolean variables to be processed and declaration of the instance variable. The function block

instance appears on Fig.1 Netw1. Based on the given LD, the

as inputs to the function block after line 31 and then we can

function block instance is given a conditional call. Therefore

use LD EN then CALC %DT0. Since the function block is

the Instruction List uses operator CALC. If EN is always true,

preceded by a complex network it’s given a conditional call. that is connected to the left bar on LD, then the function block

Therefore line 31 can be deleted. is given a non conditional call, CAL. At the bottom of Fig.5,

In the next section we give an analysis of function blocks the statement %DT0 D_TOD; is a declaration of the function

and the use of EN and ENO and non standard function instance. We can now use variable %DT0 as a function block

blocks. instance.

ISBN: 978-988-19251-4-5 WCE 2011

ISSN: 2078-0958 (Print); ISSN: 2078-0966 (Online)

Proceedings of the World Congress on Engineering 2011 Vol II

WCE 2011, July 6 - 8, 2011, London, U.K.

With this function block, %SW0 is considered as a system [7] H.A. Barker, J. Song and P Townsend, “A rule based procedure for

generating programmable controller code from graphical input in the

variable on the particular PLC. It stores the current date and form of ladder diagrams”,Eng. Appl. Of AI.,1989, Vol.2 December, c

time as a single absolute long integer LINT in seconds since 1989 Pineridge Press Ltd

the epoch. For example on Linux system this is taken as

January 1st 1970, therefore system dependent. In fact

computers regard and store time as a basic single quantity

which is only converted to date and time in user space for

readability. PDT is the preset date and time. We assume that

it is converted to LINT by the editor functions upon entry

through user interface in this PLC and therefore the function

block instance keeps this value to memory as LINT and is

retained even on power failure. Interval is the time in seconds

at which the output generation is repeated. It could be every

hour, minute or days or even years. The editor would allow

you to enter these values in various forms such as days,

seconds, years or a combination using IEC standard entry for

time variable such as DT and conversion can be done by the

function block itself or the system

The code in Fig.5 assumes your system is a 32 bit word

register, and therefore the entire 32 bit word is loaded into

registers for manipulation. In fact the IEC 61131-3 standard

does not assume any specific machine, so the details will be

system dependent. For further details on processor

implementation based on IEC 61131-3 standard refer to [5]

and [6].

X. CONCLUSION

This paper has proposed a TSDFS algorithm to generate

IEC 61131-3 compliant Instruction List code from

unrestricted Ladder Diagram with complex network and

function blocks. With this algorithm we relaxed the

restrictions on LD to compile to IL and we developed a clear

and concise direct relationship between the two languages

which has in the past hampered the flexibility on compiling

from ladder diagram to IL or instruction list to LD. It has also

given details about function block implementation on LD and

how IL code can be generated for such networks using the

same algorithm.

Future work will be to use a reverse to the algorithm to

compile from IL to LD.

REFERENCES

[1] Mark Minus, “Creating Semantic Representations of Diagrams”,

Springer-Verlag Berlin Heidelberg 2000

[2] Ge Fen, Wu Ning, “A transformation Algorithm of Ladder Diagram

into Instruction List Based on AOV Digraph and Binary

Tree”,IEEE,2006

[3] Y. Yan, Hangping Zhang, “Compiling Ladder Diagram into Instruction

List to Comply with IEC 61131-3”, 2010 Elsevier B.V. All rights

reserved

[4] Liuwen Huang, Wei Liu, Zhanqing Liu “Algorithm of Transformation

from PLC Ladder Diagram to Structured Text”, The Ninth

International Conference on Electronic Measurement & Instruments

ICEMI’2009

[5] Motohiko Okabe, “Development of Processor Directly Executing IEC

61131-3 Language”, SICE Annual Conference 2008 August 20-22,

2008, The University Electro-Communications, Japan

[6] Snaider Carrillo L., Agenor Polo Z. Mario Esmeral P. “Design and

Implementation of an Embedded Microprocessor Compatible with IL

Language in Accordance to the Norm IEC 61131-3”, Proceedings of

the 2005 International Conference on Reconfigurable Computing and

FPGAs (ReConFig 2005) 0-7695-2456-7/05 © 2005 IEEE

ISBN: 978-988-19251-4-5 WCE 2011

ISSN: 2078-0958 (Print); ISSN: 2078-0966 (Online)

View publication stats

You might also like

- History of The DDR German ShepherdsDocument7 pagesHistory of The DDR German ShepherdsIvan RogachevNo ratings yet

- Beech 1900 ManualDocument2 pagesBeech 1900 ManualAlmir Rodrigues0% (2)

- EKV MOSFET Model Implementation in Matlab and Verilog-ADocument4 pagesEKV MOSFET Model Implementation in Matlab and Verilog-AmaxsilverNo ratings yet

- SIP5 7KE85 V07.80 Manual C018-6 en PDFDocument502 pagesSIP5 7KE85 V07.80 Manual C018-6 en PDFDoan Anh TuanNo ratings yet

- Philip Merlan, From Platonism To NeoplatonismDocument267 pagesPhilip Merlan, From Platonism To NeoplatonismAnonymous fgaljTd100% (1)

- Research On FPGA-based Programmable Logic ControllDocument9 pagesResearch On FPGA-based Programmable Logic ControllzERONo ratings yet

- Material DicaDocument157 pagesMaterial DicaganeshNo ratings yet

- Module-4 VHDL & Flip FlopsDocument30 pagesModule-4 VHDL & Flip FlopsAisiri SrinathNo ratings yet

- Design and Implementation For Ladder Diagram in HyDocument8 pagesDesign and Implementation For Ladder Diagram in HyMoucha JustdoitNo ratings yet

- DigitalDocument22 pagesDigitalأيوب حسنNo ratings yet

- Ladder Logic BasicsDocument13 pagesLadder Logic BasicsBILLYNo ratings yet

- Implementation of Low Power Ternary Logic Gates Using CMOS TechnologyDocument4 pagesImplementation of Low Power Ternary Logic Gates Using CMOS TechnologyDivya MokaraNo ratings yet

- Microwind - Ternary PaperDocument4 pagesMicrowind - Ternary PaperDivya MokaraNo ratings yet

- VLSI Design NotesDocument69 pagesVLSI Design NotesPragnan Chakravorty100% (1)

- LOW-LEVEL Design EntryDocument24 pagesLOW-LEVEL Design Entryrpa projectNo ratings yet

- Digital Design Through Verilog PDFDocument68 pagesDigital Design Through Verilog PDFSammed UpadhyeNo ratings yet

- M2 (Mechatronics)Document21 pagesM2 (Mechatronics)Sarah J SinfuegoNo ratings yet

- Ch17. Chapter LANDocument25 pagesCh17. Chapter LANMenow ShutterNo ratings yet

- A Bond Graph Representation Approach For Automated Analog Filter DesignDocument6 pagesA Bond Graph Representation Approach For Automated Analog Filter Designgeerthi vasanNo ratings yet

- Printed CircuitDocument6 pagesPrinted CircuitJeff GicharuNo ratings yet

- Symbolic Model Checking For Channel-Based Component ConnectorsDocument19 pagesSymbolic Model Checking For Channel-Based Component ConnectorsSoumik SinhaNo ratings yet

- Null 3Document9 pagesNull 3gonegone044No ratings yet

- An Equivalent Circuit Model of Miniature Double E-Shaped Meander Line Printed Monopole AntennaDocument5 pagesAn Equivalent Circuit Model of Miniature Double E-Shaped Meander Line Printed Monopole AntennababuNo ratings yet

- Data Encoding Techniques For Reducing Energy Consumption in Network-On-ChipDocument4 pagesData Encoding Techniques For Reducing Energy Consumption in Network-On-ChiplambanaveenNo ratings yet

- Formulating Structural Matrices of Equations of Electric Circuits Containing Dependent Sources, With The Use of The Maple ProgramDocument5 pagesFormulating Structural Matrices of Equations of Electric Circuits Containing Dependent Sources, With The Use of The Maple ProgramBeny AbdouNo ratings yet

- Logic Synthesis - WikipediaDocument4 pagesLogic Synthesis - WikipediasukhoiNo ratings yet

- Multiplexer-Based Design of Adders/Subtractors and Logic Gates For Low Power VLSI ApplicationsDocument8 pagesMultiplexer-Based Design of Adders/Subtractors and Logic Gates For Low Power VLSI ApplicationssunilNo ratings yet

- Reduced Order Modeling For Transient Analysis of Carbon Nanotubes InterconnectsDocument6 pagesReduced Order Modeling For Transient Analysis of Carbon Nanotubes InterconnectsRavi KakaniNo ratings yet

- Design of LDPC Codes: A Survey and New ResultsDocument21 pagesDesign of LDPC Codes: A Survey and New Resultskunduru_reddy_3No ratings yet

- Electronic Digital CircuitsDocument33 pagesElectronic Digital Circuitskathrin_jazz26No ratings yet

- Optical Orthogonal Codes: Design,: 1, 1) ThisDocument10 pagesOptical Orthogonal Codes: Design,: 1, 1) ThisRazzleNo ratings yet

- ALS SurveyDocument19 pagesALS Survey張哲銘No ratings yet

- DCCBIJCAPaper PublicationDocument11 pagesDCCBIJCAPaper PublicationMohamed ElfikkyNo ratings yet

- IIIT Network Design D.deepak IIIT HyderabadDocument9 pagesIIIT Network Design D.deepak IIIT HyderabadHarshit PahujaNo ratings yet

- Digital System Modelling Using Hardware Description Language (HDL)Document56 pagesDigital System Modelling Using Hardware Description Language (HDL)nuratierah yusofNo ratings yet

- Programmable Logic Controller (PLC) - Programming LanguagesDocument23 pagesProgrammable Logic Controller (PLC) - Programming LanguagesHussain YousifNo ratings yet

- 01051759Document5 pages01051759Aarif MalikNo ratings yet

- Electronic Design Automation Using Object Oriented ElectronicsDocument7 pagesElectronic Design Automation Using Object Oriented ElectronicsHarsha Vardhan SripathiNo ratings yet

- 615 Hybrid Pipeline SOLAR 2007Document7 pages615 Hybrid Pipeline SOLAR 2007susareshNo ratings yet

- VHDL (VHSIC Hardware Description Language) Is A LanguageDocument25 pagesVHDL (VHSIC Hardware Description Language) Is A LanguageDhananjaya DhanuNo ratings yet

- Accettura Et Al GTTI2013Document6 pagesAccettura Et Al GTTI2013Jaime Alberto Parra PlazasNo ratings yet

- Digital Electronics Lab Manual For Cse & ItDocument72 pagesDigital Electronics Lab Manual For Cse & ItSairam DasariNo ratings yet

- Relay Logic ABBDocument11 pagesRelay Logic ABBjuljan sinaniNo ratings yet

- VHDL Microproject ReportDocument15 pagesVHDL Microproject ReportHitesh TumsareNo ratings yet

- CN QB-FinalDocument2 pagesCN QB-Finalpatrick ParkNo ratings yet

- Week10 Module10Document8 pagesWeek10 Module10buscainojed078No ratings yet

- Carry Select AdderDocument72 pagesCarry Select Adderharshithakr100% (1)

- Conceptual Design of A Complex Engineering System Through Coupled SelectionDocument5 pagesConceptual Design of A Complex Engineering System Through Coupled SelectionRavi Kiran GotetiNo ratings yet

- Ontology-Based Knowledge Representation of Failure Mode and Effect Analysis On Electric/Electronic Architecture Modeling Conforming To The ISO 26262Document6 pagesOntology-Based Knowledge Representation of Failure Mode and Effect Analysis On Electric/Electronic Architecture Modeling Conforming To The ISO 26262rahul1990bhatiaNo ratings yet

- Solid State PHDocument4 pagesSolid State PHAvishek ChakrabortyNo ratings yet

- An FPGA Based Microblaze Soft Core Architecture For 2D-LiftingDocument8 pagesAn FPGA Based Microblaze Soft Core Architecture For 2D-LiftingpriyabinduNo ratings yet

- Graph Distance For Complex NetworksDocument6 pagesGraph Distance For Complex NetworksIt's RohanNo ratings yet

- Seminar - Abstract Models (State Diagrams, Dataflow & Sequencing Graphs)Document15 pagesSeminar - Abstract Models (State Diagrams, Dataflow & Sequencing Graphs)aman shaikhNo ratings yet

- Hardware Description Language or HDL Is Any Language From A Class ofDocument11 pagesHardware Description Language or HDL Is Any Language From A Class ofAnand PrajapatiNo ratings yet

- Coupling-Driven Signal Encoding Scheme For Low-Power Interface DesignDocument4 pagesCoupling-Driven Signal Encoding Scheme For Low-Power Interface DesignshastryNo ratings yet

- Lukasiewicz Logic ArraysDocument7 pagesLukasiewicz Logic Arrayspelle svanslosNo ratings yet

- Verilog - Excellent ExplanationDocument18 pagesVerilog - Excellent ExplanationRida AmjadNo ratings yet

- Computer CircuitryDocument10 pagesComputer Circuitryomer aljanabyNo ratings yet

- Ko EtterDocument1 pageKo EttermonamomeniNo ratings yet

- Digital Integrated Circuit: IntroductionDocument5 pagesDigital Integrated Circuit: IntroductionPolkam SrinidhiNo ratings yet

- Understanding The Low Power Abstraction: Dr. Gary Delp Erich Marschner Kenneth BakalarDocument7 pagesUnderstanding The Low Power Abstraction: Dr. Gary Delp Erich Marschner Kenneth BakalarYasser NaguibNo ratings yet

- Midterm Report Format PDFDocument25 pagesMidterm Report Format PDFLucy HeartfilliaNo ratings yet

- Dwaraka Nadh K: Mobile:8504080654,8500353334Document3 pagesDwaraka Nadh K: Mobile:8504080654,8500353334anon_396084846No ratings yet

- An Exploratory Study of GFRP Rebar With Ribs Containing Milled Glass FibersDocument9 pagesAn Exploratory Study of GFRP Rebar With Ribs Containing Milled Glass FibersShoban Senapathi MNo ratings yet

- Pil 01 PilcDocument6 pagesPil 01 Pilcpingu 132435No ratings yet

- Tempeh or Tempe (: Rhizopus OligosporusDocument7 pagesTempeh or Tempe (: Rhizopus OligosporusAndrei VladNo ratings yet

- Servicio y Reparación GenieDocument268 pagesServicio y Reparación Geniejonny david martinez perezNo ratings yet

- Deluge Valve Installation ManualDocument7 pagesDeluge Valve Installation Manualrahull.miishraNo ratings yet

- Secondary and Tertiary Industries of PakistanDocument21 pagesSecondary and Tertiary Industries of PakistanMuhammad Talha Subhani0% (1)

- Mento - Katalog Master Flo Choke Valves - 17.08.20 - LowDocument37 pagesMento - Katalog Master Flo Choke Valves - 17.08.20 - Lowsherif aymanNo ratings yet

- Mesología BERQUEDocument6 pagesMesología BERQUEPanchita PonisioNo ratings yet

- Traffic Flow - WikipediaDocument146 pagesTraffic Flow - WikipediaAngeline AgunatNo ratings yet

- Biochemical Aspects of CellDocument39 pagesBiochemical Aspects of CellHaroon BadarNo ratings yet

- Assign 01 (8610) Wajahat Ali Ghulam BU607455 B.ed 1.5 YearsDocument9 pagesAssign 01 (8610) Wajahat Ali Ghulam BU607455 B.ed 1.5 YearsAima Kha KhanNo ratings yet

- RPLL NewDocument74 pagesRPLL NewMeta learnNo ratings yet

- Brkipm-3017 2Document112 pagesBrkipm-3017 2Adilson PedroNo ratings yet

- Variables On Both Sides of EquationsDocument17 pagesVariables On Both Sides of EquationsShatakshi DixitNo ratings yet

- Basic Troubleshooting CLARKDocument21 pagesBasic Troubleshooting CLARKRaul E. SoliNo ratings yet

- A Review On Rasamanjari: It's Contribution in Pharmaceutical ScienceDocument3 pagesA Review On Rasamanjari: It's Contribution in Pharmaceutical ScienceEditor IJTSRDNo ratings yet

- Siskyou Bombing RangeDocument114 pagesSiskyou Bombing RangeCAP History LibraryNo ratings yet

- Anode InfoDocument5 pagesAnode InfoEberg NlnoNo ratings yet

- Dwnload Full Laboratory Manual For Anatomy and Physiology 6th Edition Marieb Solutions Manual PDFDocument34 pagesDwnload Full Laboratory Manual For Anatomy and Physiology 6th Edition Marieb Solutions Manual PDFhelgasonrosario100% (12)

- Initial Newborn AssessmentDocument14 pagesInitial Newborn Assessmentaclark831No ratings yet

- MATH 5 Q4 Module 2 Vizualizing Volume of Cube and Rectangular PrismDocument21 pagesMATH 5 Q4 Module 2 Vizualizing Volume of Cube and Rectangular PrismAnj De Guzman75% (4)

- 6.MAY DIEN TIM 6-12 KENH - GreyDocument3 pages6.MAY DIEN TIM 6-12 KENH - GreyPhạm Thanh VyNo ratings yet

- 19 Fingal Development Plan 2017-2023 - Strategic Environmental Assessment Statement PDFDocument110 pages19 Fingal Development Plan 2017-2023 - Strategic Environmental Assessment Statement PDFdi TalapaniniNo ratings yet

- Callistephus Chinensis GalaDocument4 pagesCallistephus Chinensis GalaBacic SanjaNo ratings yet