Professional Documents

Culture Documents

1.6mm X 1.0mm DFN Package Saves Board: Transient Voltage Suppressing Device For ESD and Surge Protection

1.6mm X 1.0mm DFN Package Saves Board: Transient Voltage Suppressing Device For ESD and Surge Protection

Uploaded by

xXMythicalRoseXOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

1.6mm X 1.0mm DFN Package Saves Board: Transient Voltage Suppressing Device For ESD and Surge Protection

1.6mm X 1.0mm DFN Package Saves Board: Transient Voltage Suppressing Device For ESD and Surge Protection

Uploaded by

xXMythicalRoseXCopyright:

Available Formats

AZ3505-01F

Transient Voltage Suppressing Device

For ESD and Surge Protection

Features AZ3505-01F is a unique design which includes

ESD/Surge protection for one line with proprietary clamping cell in a single package.

uni-directional During transient conditions, the proprietary

Provide transient protection for one line to clamping cell prevents over-voltage on the power

IEC 61000-4-2 (ESD) ±30kV (air / contact) line or control/data lines, protecting any

IEC 61000-4-4 (EFT) 80A (5/50ns) downstream components.

IEC 61000-4-5 (Lightning) 200A (8/20µs)

AZ3505-01F may be used to meet the ESD

For operating voltage of 4.5V and below

immunity requirements of IEC 61000-4-2, Level 4

1.6mm x 1.0mm DFN package saves board

(±15kV air, ±8kV contact discharge).

space

High surge protection

Fast turn-on and low clamping voltage

Solid-state silicon-avalanche and active circuit Circuit Diagram /

triggering technology Pin Configuration

Green part

Applications

Vbat pin for mobile device

Power line protection

Mobile phones

Hand held portable applications

Description

AZ3505-01F is a design which includes a

uni-directional surge rated clamping cell to

protect one power line, or one control line, or one DFN1610P2E (Bottom View)

low-speed data line in an electronic system. The

AZ3505-01F has been specifically designed to

protect sensitive components which are

connected to power and control lines from

over-voltage damage and latch-up caused by

Electrostatic Discharging (ESD), Electrical Fast

Transients (EFT), Lightning, and Cable

Discharge Event (CDE).

Revision 2017/12/27 © 2017-2018 Amazing Micro. 1 www.amazingIC.com

AZ3505-01F

Transient Voltage Suppressing Device

For ESD and Surge Protection

SPECIFICATIONS

ABSOLUTE MAXIMUM RATINGS (TA= 25oC, unless otherwise specified)

PARAMETER SYMBOL RATING UNITS

Peak Pulse Current (tp=8/20µs) IPP (Note 1) 200 A

Operating Supply Voltage (pin-1 to pin-2) VDC 4.95 V

ESD per IEC 61000-4-2 (Air) VESD-1 ±30 kV

ESD per IEC 61000-4-2 (Contact) VESD-2 ±30

o

Lead Soldering Temperature TSOL 260 (10 sec.) C

o

Operating Temperature TOP -55 to +125 C

o

Storage Temperature TSTO -55 to +150 C

ELECTRICAL CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS MINI TYP MAX UNITS

Reverse Stand-Off

VRWM Pin-1 to pin-2, T=25 oC. 4.5 V

Voltage

Reverse Leakage VRWM = 4.5V, T=25 oC, pin-1 to

ILeak 100 nA

Current pin-2.

Reverse Breakdown IBV = 1mA, T=25 oC, pin-1 to

VBV 5 7 V

Voltage pin-2.

IF = 15mA, T=25 oC, pin-2 to

Forward Voltage VF 0.8 1 V

pin-1.

IPP = 100A, tp=8/20µs, T=25 oC,

10.5

pin-1 to pin-2.

Surge Clamping

VCL-surge V

Voltage (Note 1) o

IPP = 200A, tp=8/20µs, T=25 C,

16.5

pin-1 to pin-2.

IEC 61000-4-2 +8kV (ITLP = 16A),

ESD Clamping

VCL-ESD Contact mode, T=25 oC, pin-1 to 5.5 V

Voltage (Note 2)

pin-2.

ESD Dynamic Turn-on IEC 61000-4-2 0~+8kV, Contact

Rdynamic 0.03 Ω

Resistance mode, T=25 oC, pin-1 to pin-2.

Channel Input VR = 0V, f = 1MHz, T=25 oC, pin-1

CIN 310 400 pF

Capacitance to pin-2.

Note 1: The Peak Pulse Current measured conditions: tp= 8/20µs, 2Ω source impedance.

Note 2: ESD Clamping Voltage was measured by Transmission Line Pulsing (TLP) System.

TLP conditions: Z0= 50Ω, tp= 100ns, tr= 1ns.

Revision 2017/12/27 © 2017-2018 Amazing Micro. 2 www.amazingIC.com

AZ3505-01F

Transient Voltage Suppressing Device

For ESD and Surge Protection

Typical Characteristics

Reverse Clamping Voltage vs. Peak Pulse Current Forward Clamping Voltage vs. Peak Pulse Current

20 15

19 14

18

13

17

16 12

15 11

Clamping Voltage (V)

Clamping Voltage (V)

14

10

13

12 9

11 8

10

7

9

8 6

7 5

6 Waveform Waveform

5 4

Parameters: Parameters:

4 tr = 8µs 3 tr = 8µs

3 td = 20µs 2 td = 20µs

2 Source impedance = 2ohm Source impedance = 2ohm

1 1

0 0

0 20 40 60 80 100 120 140 160 180 200 220 0 20 40 60 80 100 120 140 160 180 200 220

Peak Pulse Current (A) Peak Pulse Current (A)

Transmission Line Pulsing (TLP) Measurement Typical Variation of CIN vs. VIN

18 320

Transmission Line Pulsing (TLP) Current (A)

17 V_pulse 310 f = 1MHz, T = 25°C

16 Pulse from a

300

15 transmission line TLP_I

14 100ns + 290

13 TLP_V DUT 280

Capacitance (pF)

12

_ 270

11

10 260

9 250

8 240

7

6

230

5 220

4 210

3

200

2

1 190

0 180

0 1 2 3 4 5 6 7 8 0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5

Transmission Line Pulsing (TLP) Voltage (V) Input Voltage (V)

Revision 2017/12/27 © 2017-2018 Amazing Micro. 3 www.amazingIC.com

AZ3505-01F

Transient Voltage Suppressing Device

For ESD and Surge Protection

Applications

In order to obtain enough suppression of ESD

The AZ3505-01F is designed to protect one line

induced transient, a good circuit board is critical.

against system ESD/EFT/Lightning pulses by

Thus, the following guidelines are recommended:

clamping them to an acceptable reference.

Minimize the path length between the

The usage of the AZ3505-01F is shown in Fig. 1. protected lines and the AZ3505-01F.

Protected lines, such as data lines, control lines, Place the AZ3505-01F near the input

or power lines, are connected to pin 1. The pin 2 terminals or connectors to restrict transient

should be connected directly to a ground plane coupling.

on the board. All path lengths connected to the The ESD current return path to ground

pins of AZ3505-01F should be kept as short as should be kept as short as possible.

possible to minimize parasitic inductance in the Use ground planes whenever possible.

board traces. NEVER route critical signals near board

edges and near the lines which the ESD

transient easily injects to.

Fig. 1

Revision 2017/12/27 © 2017-2018 Amazing Micro. 4 www.amazingIC.com

AZ3505-01F

Transient Voltage Suppressing Device

For ESD and Surge Protection

Fig. 2 shows another simplified example of using low-speed data lines, and power lines from ESD

AZ3505-01F to protect the control lines, transient stress.

VDD

Chip-B

AZ3505-01F

1

Chip-A

Low-speed Control Line

Data Line

2

Chip-C

AZ3505-01F

1

AZ3505-01F

1

2

2

GND

Fig. 2

Revision 2017/12/27 © 2017-2018 Amazing Micro. 5 www.amazingIC.com

AZ3505-01F

Transient Voltage Suppressing Device

For ESD and Surge Protection

Mechanical Details

PACKAGE DIMENSIONS

DFN1610P2E MILLIMETERS

SYMBOL

PACKAGE DIAGRAMS MIN. NOM. MAX.

D 0.95 1.00 1.05

E

E 1.55 1.60 1.65

C 0.75 0.80 0.85

A 0.45 0.50 0.55

D

A1 - 0.02 0.05

e1 1.10BSC

F 0.10 0.15 0.20

H 0.15 0.20 0.25

1 2 L 0.35 0.40 0.45

Top View

H

LAND LAYOUT

e1

1 2

Bottom View

F Notes:

A1 This LAND LAYOUT is for reference

Side View purposes only. Please consult your

manufacturing partners to ensure your

company’s PCB design guidelines are met.

Revision 2017/12/27 © 2017-2018 Amazing Micro. 6 www.amazingIC.com

AZ3505-01F

Transient Voltage Suppressing Device

For ESD and Surge Protection

MARKING CODE

Part Number Marking Code

AZ3505-01F.R7G

YX

(Green Part)

Note. Green means Pb-free, RoHS, and

Top View Halogen free compliant.

Y = Device Code

X = Date Code

Ordering Information

PN# Material Type Reel size MOQ MOQ/internal box MOQ/carton

AZ3505-01F.R7G Green T/R 7 inch 3,000/reel 4 reels = 12,000/box 6 boxes = 72,000/carton

Revision History

Revision Modification Description

Revision 2017/12/27 Formal Release.

Revision 2017/12/27 © 2017-2018 Amazing Micro. 7 www.amazingIC.com

You might also like

- DuasDocument180 pagesDuasdn08smmcNo ratings yet

- Intuitive Knowing As Spiritual ExperienceDocument237 pagesIntuitive Knowing As Spiritual ExperienceHugo Martin100% (1)

- Info 1Document28 pagesInfo 1Veejay Soriano Cuevas0% (1)

- Secador SchulzDocument16 pagesSecador SchulzSantiagoAlpala100% (1)

- AZ3105-01F DatasheetDocument5 pagesAZ3105-01F DatasheetttNo ratings yet

- AZ5413-01F.R7GR DatasheetDocument7 pagesAZ5413-01F.R7GR DatasheetttNo ratings yet

- Az5a75 01FDocument7 pagesAz5a75 01FttNo ratings yet

- AZ3133-04F DatasheetDocument7 pagesAZ3133-04F DatasheetttNo ratings yet

- IEC 61000-4-2 (ESD) 20kV (Air), 12kV (Contact) IEC 61000-4-4 (EFT) 40A (5/50ns) IEC 61000-4-5 (Lightning) 7A (8/20 S) Cable Discharge Event (CDE)Document6 pagesIEC 61000-4-2 (ESD) 20kV (Air), 12kV (Contact) IEC 61000-4-4 (EFT) 40A (5/50ns) IEC 61000-4-5 (Lightning) 7A (8/20 S) Cable Discharge Event (CDE)cafosokNo ratings yet

- AZ2115-05C.R7G (Datasheet)Document7 pagesAZ2115-05C.R7G (Datasheet)ttNo ratings yet

- Az5b75 01BDocument6 pagesAz5b75 01BttNo ratings yet

- 0402 Small DFN Package Saves Board SpaceDocument7 pages0402 Small DFN Package Saves Board Spacecarlos rumboNo ratings yet

- IEC 61000-4-2 (ESD) 20kV (Air), 15kV (Contact) IEC 61000-4-4 (EFT) 50A (5/50ns) Cable Discharge Event (CDE)Document6 pagesIEC 61000-4-2 (ESD) 20kV (Air), 15kV (Contact) IEC 61000-4-4 (EFT) 50A (5/50ns) Cable Discharge Event (CDE)Ion PetruscaNo ratings yet

- Azc199 02SDocument8 pagesAzc199 02SHamzaNo ratings yet

- ESD Protection AZC099-04S PDFDocument12 pagesESD Protection AZC099-04S PDFChrist TianNo ratings yet

- Az5b0s 01FDocument6 pagesAz5b0s 01FJC CNo ratings yet

- Ultra Low Capacitance: 0.4pF Typical: Suitable For, 17V and Below, Operating Voltage ApplicationsDocument7 pagesUltra Low Capacitance: 0.4pF Typical: Suitable For, 17V and Below, Operating Voltage ApplicationsttNo ratings yet

- Esda 25 B 1Document5 pagesEsda 25 B 1aleregsilva7321No ratings yet

- WILLSEMI Will Semicon ESD5311N 2 TR - C153721 PDFDocument5 pagesWILLSEMI Will Semicon ESD5311N 2 TR - C153721 PDFPippoNo ratings yet

- ESD5302N WillSEMIDocument7 pagesESD5302N WillSEMIRenato Luiz TécnicoNo ratings yet

- ESDA25B1: Transil Array For Esd ProtectionDocument5 pagesESDA25B1: Transil Array For Esd Protectiondrain rainNo ratings yet

- Low Voltage Clamp For ESD and CDE Protection: Protection Products Protection Products - Microclamp Description FeaturesDocument6 pagesLow Voltage Clamp For ESD and CDE Protection: Protection Products Protection Products - Microclamp Description FeaturesAmirNo ratings yet

- Slvu2 8Document10 pagesSlvu2 8hadiNo ratings yet

- For Operating Voltage of 5V and Below Ultra Low Capacitance: 0.5pF TypicalDocument10 pagesFor Operating Voltage of 5V and Below Ultra Low Capacitance: 0.5pF TypicalTri Nguyen Real EstateNo ratings yet

- ESDA25DB3: Transil Array For Esd ProtectionDocument5 pagesESDA25DB3: Transil Array For Esd ProtectionZoltán ÁgostonNo ratings yet

- For Operating Voltage of 3.3V and Below Ultra Low Capacitance: 0.45pF TypicalDocument9 pagesFor Operating Voltage of 3.3V and Below Ultra Low Capacitance: 0.45pF TypicalChithiran C SspNo ratings yet

- Esdalc6v1 1u2Document11 pagesEsdalc6v1 1u2Aditya SrivatsavNo ratings yet

- DatasheetDocument6 pagesDatasheetMatthewNo ratings yet

- Hoja de Datos Diodo El61Document6 pagesHoja de Datos Diodo El61Yeik Frey Caro CNo ratings yet

- Rectifier Diodes BYV29F, BYV29X Series Ultrafast: Features Symbol Quick Reference DataDocument7 pagesRectifier Diodes BYV29F, BYV29X Series Ultrafast: Features Symbol Quick Reference DataMiguel AngelNo ratings yet

- Data Sheet: BYV29F, BYV29X SeriesDocument10 pagesData Sheet: BYV29F, BYV29X SeriesDavid MarcosNo ratings yet

- SYT06S03DVCDocument9 pagesSYT06S03DVCttNo ratings yet

- SR05 N2195 Rev.aDocument5 pagesSR05 N2195 Rev.aMauricio T CostaNo ratings yet

- Littelfuse TVS Diode Array SD C Datasheet - pdf-1667453Document27 pagesLittelfuse TVS Diode Array SD C Datasheet - pdf-1667453SinyxNo ratings yet

- Byw80 200Document8 pagesByw80 200SevNo ratings yet

- Data Sheet: BYV29F, BYV29X SeriesDocument10 pagesData Sheet: BYV29F, BYV29X Seriesorlando gordonNo ratings yet

- SLP1210N6Document7 pagesSLP1210N6NalsonNo ratings yet

- ITA6V1U1: Transil Array For Dataline ProtectionDocument5 pagesITA6V1U1: Transil Array For Dataline ProtectionZoltán ÁgostonNo ratings yet

- TS25P05G-K Series - C2104Document5 pagesTS25P05G-K Series - C2104Francisco CardonaNo ratings yet

- CDDFN10-2574N - Surface Mount TVS Diode Array: Features ApplicationsDocument6 pagesCDDFN10-2574N - Surface Mount TVS Diode Array: Features ApplicationsAlexNo ratings yet

- MSB30M: Glass Passivated Surface Mount Bridge Rectifiers Reverse Voltage - 1000 Volts Forward Current - 3.0 AmpereDocument6 pagesMSB30M: Glass Passivated Surface Mount Bridge Rectifiers Reverse Voltage - 1000 Volts Forward Current - 3.0 Ampere建昇李No ratings yet

- SM10LZ47Document3 pagesSM10LZ47faraeinshirazi.1998No ratings yet

- Data SheetDocument10 pagesData SheetRaphael Silveira de SouzaNo ratings yet

- STTA2512P STTA5012TV1/2: Turboswitch Ultra-Fast High Voltage DiodeDocument9 pagesSTTA2512P STTA5012TV1/2: Turboswitch Ultra-Fast High Voltage DiodeDavid ReyesNo ratings yet

- Es1f Ds enDocument7 pagesEs1f Ds enTito PeñaNo ratings yet

- BYV255V: High Efficiency Fast Recovery Rectifier DiodesDocument5 pagesBYV255V: High Efficiency Fast Recovery Rectifier DiodesaleksNo ratings yet

- STK554U392A-E: Inverter Power H-IC For 3-Phase Motor DriveDocument15 pagesSTK554U392A-E: Inverter Power H-IC For 3-Phase Motor Drivegotcha75No ratings yet

- File 201709281703398218Document3 pagesFile 201709281703398218Victor CaprielNo ratings yet

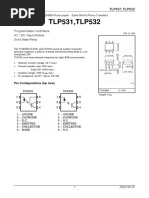

- TLP531, TLP532Document9 pagesTLP531, TLP532leon silvaNo ratings yet

- AB01B Data Sheet: V 800 V, I 0.5 A, T 200 Ns Fast Recovery DiodeDocument5 pagesAB01B Data Sheet: V 800 V, I 0.5 A, T 200 Ns Fast Recovery DiodeytnateNo ratings yet

- TST10H45C: Taiwan SemiconductorDocument5 pagesTST10H45C: Taiwan Semiconductorn tanevarNo ratings yet

- Rectifier Diodes BYQ28X Series Ultrafast: General Description Quick Reference DataDocument6 pagesRectifier Diodes BYQ28X Series Ultrafast: General Description Quick Reference Databugy costyNo ratings yet

- TLP731, TLP732: Office Machine Household Use Equipment Solid State Relay Switching Power SupplyDocument10 pagesTLP731, TLP732: Office Machine Household Use Equipment Solid State Relay Switching Power Supplycarlosjuniors888No ratings yet

- MC78XX/LM78XX/MC78XXA: 3-Terminal 1A Positive Voltage RegulatorDocument28 pagesMC78XX/LM78XX/MC78XXA: 3-Terminal 1A Positive Voltage Regulatorapi-19786583No ratings yet

- TYN 0510 - TYN 1010: FeaturesDocument4 pagesTYN 0510 - TYN 1010: FeaturesSofyan AndikaNo ratings yet

- Taiwan Semiconductor: Description FeaturesDocument7 pagesTaiwan Semiconductor: Description FeaturesjicoelhoNo ratings yet

- Low Capacitance TVS For LVDS Interfaces: Protection Products - Railclamp Description FeaturesDocument8 pagesLow Capacitance TVS For LVDS Interfaces: Protection Products - Railclamp Description FeaturesAnibal Tantalean SarmientoNo ratings yet

- Datasheet5641 ZenerDocument6 pagesDatasheet5641 ZenerDoppler ElectronicaNo ratings yet

- BR 211140Document7 pagesBR 211140Felipe SoffiattiNo ratings yet

- TVL ST23 04 Ad0Document9 pagesTVL ST23 04 Ad0coulsonpfilNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Analog Dialogue Volume 46, Number 1: Analog Dialogue, #5From EverandAnalog Dialogue Volume 46, Number 1: Analog Dialogue, #5Rating: 5 out of 5 stars5/5 (1)

- Digit ProblemDocument4 pagesDigit ProblemKimo KenoNo ratings yet

- Coalmine Monitoring SystemDocument65 pagesCoalmine Monitoring SystemTechnos_IncNo ratings yet

- General Chemistry 1: Quarter 2 - Module 4 Polymers & BiomoleculesDocument22 pagesGeneral Chemistry 1: Quarter 2 - Module 4 Polymers & BiomoleculesKaren de los ReyesNo ratings yet

- Hot Work Fabrics Just Got SaferDocument24 pagesHot Work Fabrics Just Got Saferjacc009No ratings yet

- Truss-Design 18mDocument6 pagesTruss-Design 18mARSENo ratings yet

- Integrity Management of Safety Critical Equipment and SystemsDocument10 pagesIntegrity Management of Safety Critical Equipment and SystemsLi QiNo ratings yet

- Test BenchDocument16 pagesTest BenchAdriana VeronicaNo ratings yet

- Tokyo Martis User Manual (En)Document32 pagesTokyo Martis User Manual (En)kyaw zin tun TunNo ratings yet

- Betag 2014Document7 pagesBetag 2014MelmakPolytronNo ratings yet

- DimpuDocument27 pagesDimpuDippu SihombingNo ratings yet

- Dialysis: Prepared byDocument31 pagesDialysis: Prepared byVimal PatelNo ratings yet

- Posture ClassDocument56 pagesPosture Classnarainder kumarNo ratings yet

- CRV Led Spec SheetDocument3 pagesCRV Led Spec SheetGabrielGrecoNo ratings yet

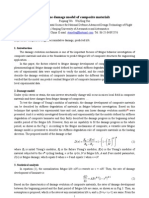

- A Fatigue Damage Model of Composite MaterialsDocument4 pagesA Fatigue Damage Model of Composite MaterialsPrathamesh BilgundeNo ratings yet

- Chapter 1 - Intro. To ForestryDocument40 pagesChapter 1 - Intro. To ForestryAngelica Sagayo DocayagNo ratings yet

- A High Proportion of Beta-Tocopherol In. 2019Document5 pagesA High Proportion of Beta-Tocopherol In. 2019Miguel Antonio CaicedoNo ratings yet

- What Is Price Skimming?: First MoverDocument9 pagesWhat Is Price Skimming?: First MoverDiya MukherjeeNo ratings yet

- Ingredients For The Dough: KachoriDocument3 pagesIngredients For The Dough: Kachoriprasad1995No ratings yet

- F1140 PDFDocument5 pagesF1140 PDFรอคนบนฟ้า ส่งใครมาให้ สักคน100% (1)

- Hampton Frames 2014 CatalogueDocument32 pagesHampton Frames 2014 CataloguehamptonframesNo ratings yet

- Forum Arduino CC T GRBL Lcdkeypad Shield 331250 6Document10 pagesForum Arduino CC T GRBL Lcdkeypad Shield 331250 6David duranNo ratings yet

- Formulation - of - Corrosion - Inhibitors-Yun Chen and Wenzhong Yang 23 PAGESDocument23 pagesFormulation - of - Corrosion - Inhibitors-Yun Chen and Wenzhong Yang 23 PAGESChoice Organo100% (4)

- HiitDocument41 pagesHiitpraveenNo ratings yet

- Despite', in Spite Of', Although', Though' and Even Though'Document4 pagesDespite', in Spite Of', Although', Though' and Even Though'pikorl4327No ratings yet

- Simulation and Study For Coherent Ofdm SystemDocument5 pagesSimulation and Study For Coherent Ofdm SystemTaha Al-abedNo ratings yet

- PARAS, Mark Heinrich B. - Exercise 3 - Lecture Biochemistry CHEM 40 BSN 1EDocument4 pagesPARAS, Mark Heinrich B. - Exercise 3 - Lecture Biochemistry CHEM 40 BSN 1EMark Heinrich B. ParasNo ratings yet