Professional Documents

Culture Documents

Truesemi-TSD5N65M C382376

Truesemi-TSD5N65M C382376

Uploaded by

carlos riveraOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Truesemi-TSD5N65M C382376

Truesemi-TSD5N65M C382376

Uploaded by

carlos riveraCopyright:

Available Formats

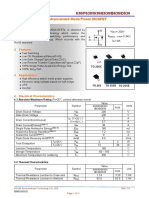

TSD5N65M/TSU5N65M

TSD5N65M/TSU5N65M

650V N-Channel MOSFET

General Description

Features

This Power MOSFET is produced using Truesemi‘s

advanced planar stripe DMOS technology. • 3.0A,650V,Max.RDS(on)=3.0 Ω @ VGS =10V

This advanced technology has been especially tailored to • Low gate charge(typical 16nC)

minimize on-state resistance, provide superior switching • High ruggedness

performance, and withstand high energy pulse in the

avalanche and commutation mode. These devices are well • Fast switching

suited for high efficiency switched mode power supplies, • 100% avalanche tested

active power factor correction based on half bridge • Improved dv/dt capability

topology.

Absolute Maximum Ratings TJ=25℃ unless otherwise specified

Symbol Parameter Value Units

VDSS Drain-Source Voltage 650 V

VGS Gate-Source Voltage ± 30 V

TC = 25℃ 3.0 A

ID Drain Current

TC = 100℃ 1.8 A

IDM Pulsed Drain Current (Note 1) 12 A

EAS Single Pulsed Avalanche Energy (Note 2) 210 mJ

EAR Repetitive Avalanche Energy (Note 1) 5.8 mJ

dv/dt Peak Diode Recovery dv/dt (Note 3) 4.5 V/ns

Power Dissipation (TC = 25℃) 58 W

PD

-Derate above 25℃ 0.46 W/℃

TJ, TSTG Operating and Storage Temperature Range -55 to +150 ℃

Maximum lead temperature for soldering purposes,

TL 300 ℃

1/8” from case for 5 seconds

* Drain current limited by maximum junction temperature.

Thermal Resistance Characteristics

Symbol Parameter Max Units

RθJC Thermal Resistance,Junction-to-Case 2.16 ℃/W

RθJA Thermal Resistance,Junction-to-Ambient* 50 ℃/W

RθJA Thermal Resistance,Junction-to-Ambient 110 ℃/W

© 2018 Truesemi Semiconductor Corporation Ver.C1 www.truesemi.com

TSD5N65M/TSU5N65M

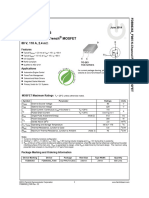

Electrical Characteristics TJ=25 ℃ unless otherwise specified

Symbol Parameter Test Conditions Min Typ Max Units

On Characteristics

VGS Gate Threshold Voltage VDS = VGS, ID = 250 uA㎂ 3.0 -- 5.0 V

Static Drain-Source

RDS(ON) VGS = 10 V, ID =1.5A -- 2.5 3.0 Ω

On-Resistance

gFS Forward Transconductance VDS=40V,ID=1.5A (Note 4) -- 4.7 -- S

Off Characteristics

BVDSS Drain-Source Breakdown Voltage VGS = 0 V, ID = 250 uA㎂ 650 -- -- V

△BVDSS Breakdown Voltage Temperature ID = 250 uA, Referenced to 25

-- 0.65 -- V/℃

/ △TJ Coefficient ℃

VDS = 650 V, VGS = 0 V -- -- 10 uA

IDSS Zero Gate Voltage Drain Current

VDS = 520 V, TJ = 125℃ -- -- 10 uA

IGSSF Gate-Body Leakage Current,Forward VGS = 30 V, VDS = 0 V -- -- 100 nA㎁

IGSSR Gate-Body Leakage Current,Reverse VGS =- 30 V, VDS = 0 V -- -- -100 nA㎁

Dynamic Characteristics

Ciss Input Capacitance -- 560 -- pF㎊

VDS = 25 V, VGS = 0 V,

Coss Output Capacitance -- 55 -- pF㎊

f = 1.0 MHz

Crss Reverse Transfer Capacitance -- 7 -- pF

Switching Characteristics

td(on) Turn-On Time -- 10 -- ns

VDS = 300 V, ID = 4.5A,

tr Turn-On Rise Time RG = 25 Ω -- 40 -- ns㎱

td(off) Turn-Off Delay Time (Note 4,5) -- 40 -- ns㎱

tf Turn-Off Fall Time -- 50 -- ns㎱

Qg Total Gate Charge -- 16 -- nC

VDS = 480 V, ID = 4.5A,

Qgs Gate-Source Charge VGS = 10 V -- 2.5 -- nC

Qgd Gate-Drain Charge (Note 4,5) -- 6.5 -- nC

Source-Drain Diode Maximum Ratings and Characteristics

IS Continuous Source-Drain Diode Forward Current -- -- 3.0

A

ISM Pulsed Source-Drain Diode Forward Current -- -- 12

VSD Source-Drain Diode Forward Voltage IS =3.0A, VGS = 0 V -- -- 1.4 V

trr Reverse Recovery Time IS =4.5A, VGS = 0 V -- 300 -- ns㎱

Qrr Reverse Recovery Charge diF/dt = 100 A/μs (Note 4) -- 2.0 -- uC

NOTES:

1. Repetitive Rating: Pulse width limited by maximum junction temperature

2. IAS=4.5A, VDD=50V, RG=25 Ω,Starting TJ=25 ℃

3. ISD≤4.5A, di/dt ≤ 200A/us, VDD ≤ BVDSS, Starting TJ = 25 ℃

4. Pulse Test: Pulse width ≤ 300us, Duty Cycle ≤ 2%

5. Essentially Independent of Operating Temperature Typical Characteristics

© 2018 Truesemi Semiconductor Corporation Ver.C1 www.truesemi.com

Typical Characteristics

TSD5N65M/TSU5N65M

Figure 1. On-Region Characteristics Figure 2. Transfer Characteristics

Figure 4. Body Diode Forward Voltage

Figure 3. On-Resistance Variation vs

Variation with Source Current

Drain Current and Gate Voltage

and Temperature

Figure 5. Capacitance Characteristics Figure 6. Gate Charge Characteristics

© 2018 Truesemi Semiconductor Corporation Ver.C1 www.truesemi.com

TSD5N65M/TSU5N65M

Typical Characteristics

Figure 7. Breakdown Voltage Variation Figure 8. On-Resistance Variation

vs Temperature vs Temperature

Figure 9. Maximum Safe Operating Area Figure 10. Maximum Drain Current

vs Case Temperature

Figure 11. Transient Thermal Response Curve

© 2018 Truesemi Semiconductor Corporation Ver.C1 www.truesemi.com

TSD5N65M/TSU5N65M

Fig 12. Gate Charge Test Circuit & Waveform

VGS

Same Type

50KΩ

as DUT Qg

12V 200nF

300nF 10V

VDS

VGS Qgs Qgd

DUT

3mA

Charge

Fig 13. Resistive Switching Test Circuit & Waveforms

RL VDS

VDS 90%

VDD

RG ( 0.5 rated VDS )

10%

Vin

10V DUT

td(on) tr td(off)

tf

t on t off

Fig 14. Unclamped Inductive Switching Test Circuit & Waveforms

L 1

VDS EAS = ---- LL IAS2

2

VDD

ID BVDSS

IAS

RG

ID (t)

10V DUT VDD VDS (t)

tp Time

© 2018 Truesemi Semiconductor Corporation Ver.C1 www.truesemi.com

TSD5N65M/TSU5N65M

Fig 15. Peak Diode Recovery dv/dt Test Circuit & Waveforms

DUT

+

VDS

IS

L

Driver

RG

Same Type

as DUT VDD

VGS • dv/dt controlled by RG

• IS controlled by pulse period

Gate Pulse Width

VGS D = --------------------------

Gate Pulse Period 10V

( Driver )

IFM , Body Diode Forward Current

IS

( DUT ) di/dt

IRM

Body Diode Reverse Current

VDS

( DUT ) Body Diode Recovery dv/dt

Vf VDD

Body Diode

Forward Voltage Drop

© 2018 Truesemi Semiconductor Corporation Ver.C1 www.truesemi.com

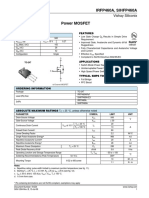

Package Dimension

TSD5N65M/TSU5N65M

© 2018 Truesemi Semiconductor Corporation Ver.C1 www.truesemi.com

Package Dimension

TSD5N65M/TSU5N65M

© 2018 Truesemi Semiconductor Corporation Ver.C1 www.truesemi.com

Package Dimension

TSD5N65M/TSU5N65M

© 2018 Truesemi Semiconductor Corporation Ver.C1 www.truesemi.com

Package Dimension

TSD5N65M/TSU5N65M

© 2018 Truesemi Semiconductor Corporation Ver.C1 www.truesemi.com

You might also like

- Syllabus EXTC Sem 7 Rev. (MU)Document31 pagesSyllabus EXTC Sem 7 Rev. (MU)Anurag RajNo ratings yet

- Features 10N65 650V N-Channel MOSFET: TO-220F PackageDocument7 pagesFeatures 10N65 650V N-Channel MOSFET: TO-220F PackageMindSet MarcosNo ratings yet

- SLW9N90C: 900V N-Channel MOSFETDocument7 pagesSLW9N90C: 900V N-Channel MOSFETJavier VelasquezNo ratings yet

- Unisonic Technologies Co., LTD: 15A, 700V N-CHANNEL Power MosfetDocument6 pagesUnisonic Technologies Co., LTD: 15A, 700V N-CHANNEL Power MosfetDavid alejandro VergaraNo ratings yet

- Transitor de CompuDocument7 pagesTransitor de CompuWilmenNo ratings yet

- SW630Document6 pagesSW630cops.elnicoNo ratings yet

- TSP12N60M / TSF12N60M TSP12N60M / TSF12N60M: 600V N-Channel MOSFETDocument7 pagesTSP12N60M / TSF12N60M TSP12N60M / TSF12N60M: 600V N-Channel MOSFETPablo Diego Cecere CasadoNo ratings yet

- Features 12N65 650V N-Channel MOSFET: TO-220F PackageDocument7 pagesFeatures 12N65 650V N-Channel MOSFET: TO-220F Packageing.angelocmNo ratings yet

- TSF65R300S1 TruesemiDocument9 pagesTSF65R300S1 Truesemimisael1001No ratings yet

- Error CodesDocument6 pagesError CodesNadin Villarroel TrollanoNo ratings yet

- ap65sl380diDocument8 pagesap65sl380diMarco Antonio RomeroNo ratings yet

- 100V N-Channel Mosfets: General DescriptionDocument5 pages100V N-Channel Mosfets: General DescriptionMariusNo ratings yet

- Datasheet F630Document11 pagesDatasheet F630Lâm Bá NhãNo ratings yet

- RTW90N20D/RTA90N20D 200V N-Channel MOSFET: Features General DescriptionDocument10 pagesRTW90N20D/RTA90N20D 200V N-Channel MOSFET: Features General DescriptionRaghunandan SubramanianNo ratings yet

- KIA KIA KIA: 1.descriptionDocument5 pagesKIA KIA KIA: 1.descriptionOscarVargasNo ratings yet

- Unisonic Technologies Co., LTD: 10A, 650V N-CHANNEL Power MosfetDocument6 pagesUnisonic Technologies Co., LTD: 10A, 650V N-CHANNEL Power MosfetJhonson Shut DownNo ratings yet

- Uufggf 5 UDocument7 pagesUufggf 5 UYousef KassimNo ratings yet

- FDP8443Document7 pagesFDP8443Semut criminalsNo ratings yet

- SVF8N70F SilanMicroelectronicsDocument7 pagesSVF8N70F SilanMicroelectronicsMike GhanemNo ratings yet

- DatasheetDocument10 pagesDatasheetMario Sandoval MoraNo ratings yet

- 2SK2611Document7 pages2SK2611mayurNo ratings yet

- TSF5N60MDocument7 pagesTSF5N60MMarko MarkovicNo ratings yet

- 10n65a 10n65afDocument6 pages10n65a 10n65afYeo LeoNo ratings yet

- SLP4N60C/SLF4N60C: 600V N-Channel MOSFETDocument7 pagesSLP4N60C/SLF4N60C: 600V N-Channel MOSFETmiler2011No ratings yet

- NCE8295A: Enhancement Mode Power MOSFETDocument7 pagesNCE8295A: Enhancement Mode Power MOSFETDarknezzNo ratings yet

- NCEP4090GUDocument6 pagesNCEP4090GUMar GaoNo ratings yet

- AP65SL190AI AdvancedPowerElectronicsDocument6 pagesAP65SL190AI AdvancedPowerElectronicsAkhmad Isnaeni RamdaniNo ratings yet

- Enhancement Mode Power MOSFET: NCE N-ChannelDocument7 pagesEnhancement Mode Power MOSFET: NCE N-ChannelErroz RosadiNo ratings yet

- B 812 Cfa 38Document8 pagesB 812 Cfa 38Sajid AliNo ratings yet

- KIA KIA KIA: 1.descriptionDocument5 pagesKIA KIA KIA: 1.descriptionzakreaNo ratings yet

- 100V N-Channel Mosfets: General DescriptionDocument5 pages100V N-Channel Mosfets: General DescriptionMariusNo ratings yet

- 100V N-Channel Mosfets: General DescriptionDocument5 pages100V N-Channel Mosfets: General DescriptionMariusNo ratings yet

- Advanced Power Electronics Corp.: AP0403GHDocument5 pagesAdvanced Power Electronics Corp.: AP0403GHIulius CezarNo ratings yet

- Irfr3505Pbf Irfu3505Pbf: FeaturesDocument11 pagesIrfr3505Pbf Irfu3505Pbf: FeaturesAzizullah AlizayNo ratings yet

- 400V N-Channel MOSFET: FTP06N40/FTA06N40Document11 pages400V N-Channel MOSFET: FTP06N40/FTA06N40Cube7 GeronimoNo ratings yet

- Datasheet - KNH8150ADocument8 pagesDatasheet - KNH8150AfrelinmNo ratings yet

- Fdb86363 - F085: N-Channel Powertrench MosfetDocument6 pagesFdb86363 - F085: N-Channel Powertrench MosfetNobreak ServiceNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument5 pagesAdvanced Power Electronics Corp.: DescriptionVladimir DoyminNo ratings yet

- Nce 8295 AkDocument7 pagesNce 8295 Akandre kressnerNo ratings yet

- IRF840Document8 pagesIRF840Apc CamNo ratings yet

- Irf840 PDFDocument8 pagesIrf840 PDFAnonymous AssOOhqigNo ratings yet

- 11N65S PingweiDocument8 pages11N65S PingweiBall SVNo ratings yet

- 100N10 EtcDocument5 pages100N10 EtcJm TechNo ratings yet

- RU6199R RuichipsDocument9 pagesRU6199R RuichipsAndres padillaNo ratings yet

- SW3205 Samwin: FeaturesDocument7 pagesSW3205 Samwin: FeaturesYousef KassimNo ratings yet

- ap65sl600ahDocument7 pagesap65sl600ahMarco Antonio RomeroNo ratings yet

- Irf 634 BDocument8 pagesIrf 634 BAhmed ShagidullinNo ratings yet

- IRFF110 JANTX2N6782 Hexfet Transistors JANTXV2N6782 THRU-HOLE (TO-205AF) REF:MIL-PRF-19500/556 100V, N-CHANNELDocument7 pagesIRFF110 JANTX2N6782 Hexfet Transistors JANTXV2N6782 THRU-HOLE (TO-205AF) REF:MIL-PRF-19500/556 100V, N-CHANNELJerson SebastianNo ratings yet

- 9 N 90 eDocument7 pages9 N 90 eMarcelo Lopes NunesNo ratings yet

- N-Channel Low QG Mosfet 30V, 100A, 3.3m: MOS-TECH Semiconductor Co.,LTDDocument9 pagesN-Channel Low QG Mosfet 30V, 100A, 3.3m: MOS-TECH Semiconductor Co.,LTDAnonymous p1ig0zX6p0No ratings yet

- Huf76633S3St - F085: N-Channel Logic Level Ultrafet Power MosfetDocument7 pagesHuf76633S3St - F085: N-Channel Logic Level Ultrafet Power MosfetJose cuelloNo ratings yet

- S2PF380N65R: N-Channel 650V Enhancement Mode Power MOSFETDocument8 pagesS2PF380N65R: N-Channel 650V Enhancement Mode Power MOSFETMaikel Borges IglesiasNo ratings yet

- STP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetDocument8 pagesSTP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetCarlos A AvilaNo ratings yet

- NCEP1520K NCEPowerSemiconductorDocument7 pagesNCEP1520K NCEPowerSemiconductorlucas sousaNo ratings yet

- Irl 2921 SDocument11 pagesIrl 2921 SDozer KamilNo ratings yet

- Advanced Power Electronics Corp.: AP2761I-ADocument4 pagesAdvanced Power Electronics Corp.: AP2761I-AM_YYYYNo ratings yet

- Datasheet RU190N10RDocument11 pagesDatasheet RU190N10Ralberto castañoNo ratings yet

- SVF 2 N 65Document7 pagesSVF 2 N 65alu5313No ratings yet

- FQP10N60-FQPF10N60: General Description Product SummaryDocument7 pagesFQP10N60-FQPF10N60: General Description Product SummaryVuksanov ZarkoNo ratings yet

- D5SB60Document6 pagesD5SB60Jahangir JinguNo ratings yet

- MAXELL Catalogo GeneralDocument48 pagesMAXELL Catalogo GeneralMedSparkNo ratings yet

- RRB Chennai SSE 2014 Question Papers and Answer KeyDocument19 pagesRRB Chennai SSE 2014 Question Papers and Answer KeyTonaNo ratings yet

- (English (Auto-Generated) ) How To Solve Diode Circuit Problems in Series and Parallel Using Ohm's Law and KVL (DownSub - Com)Document18 pages(English (Auto-Generated) ) How To Solve Diode Circuit Problems in Series and Parallel Using Ohm's Law and KVL (DownSub - Com)Jisoo KimNo ratings yet

- Wheatstone Bridge and The Diode: 1 ObjectDocument4 pagesWheatstone Bridge and The Diode: 1 ObjectathavanNo ratings yet

- Electronic Materials: Chapter 4: Semiconductor DevicesDocument25 pagesElectronic Materials: Chapter 4: Semiconductor Deviceschinh buiNo ratings yet

- ECE 027 - Module 4 Small Signal Amplifier - BJT AC AnalysisDocument40 pagesECE 027 - Module 4 Small Signal Amplifier - BJT AC AnalysisMiyuki NakiriNo ratings yet

- Electronics 6063 Y23 SyDocument32 pagesElectronics 6063 Y23 SykaboomzxcNo ratings yet

- CH11 ThyristorsDocument86 pagesCH11 Thyristorsmiathegirl9No ratings yet

- Description Appearance: 1 Watt Metal Case Zener DiodesDocument3 pagesDescription Appearance: 1 Watt Metal Case Zener DiodesDeepa DevarajNo ratings yet

- DatasheetDocument8 pagesDatasheetRegisk8 OliveiraNo ratings yet

- 1N5819 SMDDocument2 pages1N5819 SMDHla Swe OoNo ratings yet

- Electrical & Electronic ComponentsDocument242 pagesElectrical & Electronic ComponentsAkash AdakNo ratings yet

- Types of ModulatorDocument31 pagesTypes of ModulatorSamira TasnimNo ratings yet

- Control Relay Using IR SensorDocument5 pagesControl Relay Using IR Sensorsmartxdigital marketNo ratings yet

- Sx421 Automatic Voltage Regulator (Avr) : Specification, Installation and AdjustmentsDocument4 pagesSx421 Automatic Voltage Regulator (Avr) : Specification, Installation and AdjustmentsJose PirulliNo ratings yet

- Government Polytechnic, Pune: ET2107 - NODocument8 pagesGovernment Polytechnic, Pune: ET2107 - NOG012 Bhise AniketNo ratings yet

- Car Dome Light Off-DelayDocument8 pagesCar Dome Light Off-DelaymikcomiNo ratings yet

- PUE Question Paper Format - 100 MarksDocument3 pagesPUE Question Paper Format - 100 MarksnupurnehaNo ratings yet

- Green Life Charge: Kota KinabaluDocument29 pagesGreen Life Charge: Kota KinabaluAmirul NaimNo ratings yet

- Vishay IRFP460APBF Datasheet PDFDocument8 pagesVishay IRFP460APBF Datasheet PDFkamel keddarNo ratings yet

- Application of Schotkky DiodeDocument2 pagesApplication of Schotkky DiodeHema lathaNo ratings yet

- EE-252-Electronic Devices & Digital Electronics Laboratory Manual/ RecordDocument85 pagesEE-252-Electronic Devices & Digital Electronics Laboratory Manual/ RecordkishorebabNo ratings yet

- Syllabus: Electronic Circuit Design 1Document10 pagesSyllabus: Electronic Circuit Design 1Bảo Duy NguyễnNo ratings yet

- P-N Junction DiodeDocument19 pagesP-N Junction DiodeUjjWal MahAjanNo ratings yet

- Motorola Saa1042 0587f49ff7Document6 pagesMotorola Saa1042 0587f49ff7Kevin StrongNo ratings yet

- Module 2 - SLM - CSS - G8 - TCEW - 4WEEKSDocument28 pagesModule 2 - SLM - CSS - G8 - TCEW - 4WEEKSRonnel SingsonNo ratings yet

- AOD206/AOI206: General Description Product SummaryDocument6 pagesAOD206/AOI206: General Description Product SummaryAnacleto ChitalakumbiNo ratings yet

- Ultrafast Rectifier Module Vs-Ufb250fa60Document8 pagesUltrafast Rectifier Module Vs-Ufb250fa60Fay AgodoloNo ratings yet