Professional Documents

Culture Documents

Designing Silicon Carbide (Sic) Based DC Fast Charging System: Key Challenges, Design Considerations, and Building Validation

Designing Silicon Carbide (Sic) Based DC Fast Charging System: Key Challenges, Design Considerations, and Building Validation

Uploaded by

takaca40Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Designing Silicon Carbide (Sic) Based DC Fast Charging System: Key Challenges, Design Considerations, and Building Validation

Designing Silicon Carbide (Sic) Based DC Fast Charging System: Key Challenges, Design Considerations, and Building Validation

Uploaded by

takaca40Copyright:

Available Formats

Designing Silicon Carbide (SiC) based DC Fast Charging System:

Key Challenges, Design Considerations, and Building Validation

Session 2

Dual Active Bridge (DAB) Design and Control Architecture

Public Information © onsemi 2022

Content

• Past session :

− Session 1 (June 1): Project and 6-Pack Boost Active Front End AC-DC analyze

• Session 2 :

− Dual Active Bridge DC-DC converter

Component selection, in particular magnetic devices

Simulation approach

Simulation results

Outcomes

− AC-DC and DC-DC Control Architecture overview

• Next to come :

− Session 3 (June 15): Gate drivers, Auxiliary Supply and Thermal Approach

− Session 4 (June 29): Measurement Results

Public Information © onsemi 2022

Design Objectives

A brief Reminder…

Public Information © onsemi 2022

Complete System PFC + DC-DC Converter Specification

Voltage input rating Three-phase 400 Vac (EU), 480 Vac (US)

Max. input current 40 A

AC input Frequency 50/60 Hz

Power factor >0.99

Efficiency >96%

Output voltage 200 V to 1000 V

DC output Max. output power 25 kW

Max. output current 50 A

Output OVP, OCP, SC

Protections Input UVP, OVP, inrush current

Internal Desat (gate driver), thermal (NTC on power device)

Push buttons Yes

User Interface

GUI Yes.

Internal SPI, I2C

Communication buses

External Isolated CAN, USB, UART

Environmental Operating temperature 0°C to 40°C

Max. mechanical

PCB 450 x 300 x 280 mm (PFC and dc-dc stacked)

dimensions

Regulation Following guidelines described in EN55011 Class A Will not be tested

Standards

EV systems Following guidelines described in IEC 61851 Will not be tested

Public Information © onsemi 2022

Components Selection

First Step : Initial Approach

Public Information © onsemi 2022

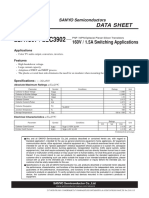

DC-DC Block Diagram : Components Selection Proposal

V V

+ +

DC in/out

°C

800V

31.5A DC in/out

1x current sense

°C

LEM CKSR50-NP A 1x current sense

LEM CKSR50-NP A 800V (optimized),

200-1000V (supported)

- A A -

Rshunt SiC SiC SiC SiC Rshunt

Aux. PSU Module Module Module Module

SECO- NCS213R Isol. Gate Drv. NCS213R

PWM1-6

HVDCDC1362-

40W15V

Shunt OPAMP ` DESAT

Source

Shunt OPAMP

NCD57000 Sink

NCS20034

OPAMP

Vcc 8x

8x

seco-te0716-gevb -5V/24V

12bit, SAR, ADC SECO-

°C NCD9801x LVDCDC3064-

4x 8x

SIC-GEVB

NCS20034 8x

NCS2032 NCID9211 Ethernet

OPAMP 2x OPAMP Gal. isolator CAN NCV7342

DESAT

9x

PWM1-6

` ` `

5V 5V ETH/

VCC AVCC

ADC SPI PWM GPIO FPGA controller (UCB) ADC PWM

CAN

6 Public Information © onsemi 2022

Bill of Material

Function Part Number

Power Module NXH006P120MNF2 X4

SiC Gate Driver NCD57000 X8

Voltage Amplifier NCS20034

Current Amplifier NCS213R

NCS2032

General Purpose Amplifier

NCS20034

Digital Isolator NCID9211

SAR ADC NCD9801x

Ethernet - CAN NCV7342

SECO-HVDCDC1362-40W15V

Aux HV PSU

with NCP1362

SECO-LVDCDC3064-SIC-GEVB

Aux LV PSU

with NCV3064MNTXG

Public Information © onsemi 2022

Dual Active Bridge Design Considerations

Public Information © onsemi 2022

Transformer Design

• Turn ratio : Given by the Output Voltage

𝑁𝑁𝑃𝑃𝑃𝑃𝑃𝑃𝑃𝑃 𝑉𝑉𝑃𝑃𝑃𝑃𝑃𝑃𝑃𝑃

Resonant Inductor = External Inductor − = (1) noted 𝑁𝑁𝑃𝑃𝑃𝑃𝑃𝑃𝑃𝑃 ∶ 𝑁𝑁𝑆𝑆𝑆𝑆𝑆𝑆

𝑁𝑁𝑆𝑆𝑆𝑆𝑆𝑆 𝑉𝑉𝑆𝑆𝑆𝑆𝑆𝑆

+ Transformer Leakage Inductor

− With VSec = 650V to 800V, VPrim = 800 V

• Resonant Inductor : Given by the

Output Power and the Phase Shift (𝜑𝜑)

𝑉𝑉𝑃𝑃𝑃𝑃𝑃𝑃𝑃𝑃 �𝑉𝑉𝑆𝑆𝑆𝑆𝑆𝑆 �sin 𝜑𝜑

− 𝐿𝐿𝑅𝑅𝑅𝑅𝑅𝑅 = (2)

2𝜋𝜋�𝑓𝑓𝑆𝑆𝑆𝑆𝑆𝑆 �𝑃𝑃𝑂𝑂𝑂𝑂𝑂𝑂

• Magnetizing Inductor :

2 𝜇𝜇0 �𝜇𝜇𝑟𝑟

− 𝐿𝐿𝑀𝑀𝑀𝑀𝑀𝑀 = 𝑁𝑁𝑃𝑃𝑃𝑃𝑃𝑃𝑃𝑃 � 𝐴𝐴𝐿𝐿 with 𝐴𝐴𝐿𝐿 = � 𝐴𝐴𝑒𝑒

𝑙𝑙𝑒𝑒 +𝜇𝜇𝑟𝑟 �𝑒𝑒

− It doesn’t depend on input or output…

Public Information © onsemi 2022

Resonant Inductor Selection

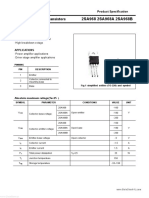

• We have the following operating points :

Point or Case Input Voltage Output Voltage Output Current Output Power

1 1000 V 25 A 25 kW

2 800 V 500 V 50 A 25 kW

3 200 V 50 A 10 kW

• Choosing 𝐿𝐿𝑅𝑅𝑅𝑅𝑅𝑅 = 22 𝜇𝜇𝜇𝜇 and using equation (2) we get :

Calculated

Point or Case

So, the maximum resonant inductor value Output Power

should to 22 µH to comply with the specification 1 57.9 kW

2 28.9 kW

3 12.6 kW

Public Information © onsemi 2022

Magnetizing Inductance Discussion

• Here, the magnetizing current or inductor does not participate to the energy

transfer. Magnetizing current can be seen as a parasitic element to minimize.

• To minimize magnetizing current, as the voltage applied to the inductor is given by

the input voltage, the magnetizing inductor should be the higher possible.

• For a fix size of core (𝐴𝐴𝑒𝑒 ; 𝑙𝑙𝑒𝑒 ), the solution is to increase the primary turn number.

• BUT, increasing primary turn number, increases the winding resistance or require

to use big wire cross section.

• Choosing a magnetizing current around or maximum 10% of the input current is a

good practice.

Public Information © onsemi 2022

Transformer Core Saturation Elimination with Active Flux Balancing

Or (Volt x Time) balancing due to mismatches or tolerances

• Passive approach :

• A low peak flux density

and large core gap transformer

Transformer efficiency drops

• Blocking capacitors in series

Bulky and expensive

High RMS current in capacitors

• Active approach using the DSP :

• Two control loops :

1. The first loop is to maintain the

average magnetizing current at

approximately zero level

2. The second loop is to keep the

average primary and secondary

currents close to zero

Public Information © onsemi 2022

Simulation Approach

Why and What ?

Public Information © onsemi 2022

Goals and Purpose

• Check Dual Active Bridge stage functionality before designing hardware

• Verify DC output voltages, currents and power at all operating points.

• Efficiency with the defined switching frequency (100 kHz)

• Estimation of power losses

• Gate drive requirements and gate resistors value

• Validate Resonant Inductor requirements/parameters (Current & Voltage)

• Transformer parameters selection

− Turn ratio optimization,

− Select reasonable Magnetizing Inductor,

− Obtain transformer parameters (Voltages & Currents)

− Determine Isolation requirements (Maximum Peak voltages Primary and Secondary)

Public Information © onsemi 2022

Input Values, Models Chosen and Parameters

• Input Voltage : 800 V (output of the Active FrontEnd)

• Output Voltage : 200 V to 1 kV

• Transformer turn ration : 1.0:1 , 1.2:1 , 1.4:1 with Magnetizing inductor = 720 µH

• Transformer Magnetizing Inductor impact : 150 µH, 300 µH and 720 µH

• Check Resonant Inductor effects with 22 µH and 18 µH

• Gate source and sink resistors (First pass 2 Ω)

• Driver model for NCD57001 using table for output impedance

• Flux Balancing control with Current Sensing and Sample and Hold included

• Verify Phase Shift control

Public Information © onsemi 2022

Expected Simulation Outputs

• Turn on and turn off speed (dv/dt)

• Select Transformer Turn ratio, Magnetizing Inductor and Resonant Inductor

• Check inductor and transformer current peak and shape, estimate losses

• Validate Flux Balancing operation

• Check input and output capacitors peak to peak current and shape,

estimate losses

• Evaluate switching behaviors and power needed to drive SiC modules

• Losses in SiC modules for thermal assembly validation

• Check overall Dual Active Bridge losses and performances

Public Information © onsemi 2022

Dual Active Bridge Simulation Results

Second Step : Verification

Public Information © onsemi 2022

Turn Ratio Impact on Magnetizing and Resonant Inductors

• Magnetizing Current • Resonant Inductor Voltage

Dual Active Bridge: Magnetizing peak current Dual Active Bridge: Inductor peak voltage

1.2:1, Lm 720µH, Ls 22µH, (P»S) 1.4:1, Lm 720µH, Ls 22µH, (P»S) 1.0:1, Lm 720µH, Ls 18µH, (P»S) 1.2:1, Lm 720µH, Ls 22µH, (P»S) 1.4:1, Lm 720µH, Ls 22µH, (P»S) 1.0:1, Lm 720µH, Ls 18µH, (P»S)

6 1000

900

5

800

4

Peak current [A]

Peak voltage [V]

700

600

2

500

1

400

0 300

200 300 400 500 600 700 800 900 1000 200 300 400 500 600 700 800 900 1000

Secondary side voltage [V] Secondary side voltage [V]

POUT = 25 kW (USEC ≥ 500 V), IOUT = 50 A (USEC < 500 V) Stefan Kosterec, 19. Jan 2021 POUT = 25 kW (USEC ≥ 500 V), IOUT = 50 A (USEC < 500 V) Stefan Kosterec, 19. Jan 2021

Public Information © onsemi 2022

Transformer Ratio Impact on Performances

• Total Losses • Overall Efficiency

Dual Active Bridge: Overall power loss Dual Active Bridge: Efficiency

1.2:1, Lm 720µH, Ls 22µH, (P»S) 1.4:1, Lm 720µH, Ls 22µH, (P»S) 1.0:1, Lm 720µH, Ls 18µH, (P»S) 1.2:1, Lm 720µH, Ls 22µH, (P»S) 1.4:1, Lm 720µH, Ls 22µH, (P»S) 1.0:1, Lm 720µH, Ls 18µH, (P»S)

900

100.0

800

99.5

700

99.0

600

Power loss [W]

Efficiency [%]

500 98.5

400

98.0

300

97.5

200

97.0

100

0 96.5

200 300 400 500 600 700 800 900 1000 200 300 400 500 600 700 800 900 1000

Secondary side voltage [V] Secondary side voltage [V]

POUT = 25 kW (USEC ≥ 500 V), IOUT = 50 A (USEC < 500 V) POUT = 25 kW (USEC ≥ 500 V), IOUT = 50 A (USEC < 500 V)

Core losses of resonant inductor and transformer are not included Stefan Kosterec, 19. Jan 2021 Core losses of resonant inductor and transformer are not included Stefan Kosterec, 19. Jan 2021

Public Information © onsemi 2022

Magnetizing Inductance value effects

• Total Losses • Overall efficiency

Dual Active Bridge: Overall power loss Dual Active Bridge: Efficiency

1.2:1, Lm 720µH, Ls 22µH, (P»S) 1.2:1, Lm 150µH, Ls 22µH, (P»S) 1.2:1, Lm 300µH, Ls 22µH, (P»S) 1.2:1, Lm 720µH, Ls 22µH, (P»S) 1.2:1, Lm 150µH, Ls 22µH, (P»S) 1.2:1, Lm 300µH, Ls 22µH, (P»S)

900

100.0

800

99.5

700

99.0

600

Power loss [W]

Efficiency [%]

500 98.5

400

98.0

300

97.5

200

97.0

100

0 96.5

200 300 400 500 600 700 800 900 1000 200 300 400 500 600 700 800 900 1000

POUT = 25 kW (USEC ≥ 500 V), IOUT = 50 A (USEC < 500 V) Secondary side voltage [V] POUT = 25 kW (USEC ≥ 500 V), IOUT = 50 A (USEC < 500 V) Secondary side voltage [V]

Core losses of resonant inductor and transformer are not included Stefan Kosterec, 19. Jan 2021 Core losses of resonant inductor and transformer are not included Stefan Kosterec, 19. Jan 2021

Public Information © onsemi 2022

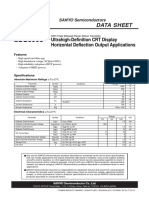

Magnetizing Inductance Selection

• Magnetizing Current

• Parameters Selection

Dual Active Bridge: Magnetizing peak current

1.2:1, Lm 720µH, Ls 22µH, (P»S) 1.2:1, Lm 150µH, Ls 22µH, (P»S) 1.2:1, Lm 300µH, Ls 22µH, (P»S) • For the turn ratio :

− 1.2:1 because it gives almost flat losses

20

18

for output voltage from 200 V to 900 V

16 And lower losses in the output voltage

14 range form 200 V to 600 V than 1.0:1

• Magnetizing Inductor :

Peak current [A]

12

10

− 150 µH to 300 µH

8

for smaller transformer size

6

4

• Resonant Inductor :

2

− Maximum 22 µH is validated

0

200 300 400 500 600 700 800 900 1000

Secondary side voltage [V]

POUT = 25 kW (USEC ≥ 500 V), IOUT = 50 A (USEC < 500 V) Stefan Kosterec, 19. Jan 2021

Public Information © onsemi 2022

Simulation Outcomes

What Can We Extract ?

Public Information © onsemi 2022

Simulations’ Outcomes and Adjustments

• Functionality : DAB works as expected. Flux Balancing prevents saturation

• Resonant Inductor selection : 18 µH Nominal 22 µH Maximum, with ESR < 12 mΩ

− Current 51 Arms / Max 85A Peak : Inductor saturation level is acceptable (<30%).

• Losses/Efficiency : Max 140W @ VOut=800V and above 97.5% for all VOut

• Turn-on / Turn-off : dV/dt is very high (up to 60 V/ns) …

− Increase Source and Sink gate resistance to get closer to 20 V/ns.

• Operating conditions :

− Maximum Maximum

Parameter ESR

Winding Voltage RMS Current

Primary < 18 mΩ 1000 V 51 Arms

Secondary < 8 mΩ 1000 V 62.5 Arms

− Total losses and Efficiency are inline with design objectives.

Public Information © onsemi 2022

Control High Level Architecture

For Active Front End and Dual Active Bridge

Public Information © onsemi 2022

PFC Control Overview

Filter Dead-Time

Compensation Correction

Power Control

Pulse Width

Modulation

Phase Locked

Loop

DQ to ABC

Transformation

with 3rd

Harmonic

Injection

Public Information © onsemi 2022

Phase Locked Loop

• Transform the rotating grid voltages and currents to corresponding steady values.

• Achieved by creating a rotating reference frame synchronized to the grid voltage.

• Allows the grid current to be split into

iD (active) and iQ (reactive) components.

Public Information © onsemi 2022

Power Control

• Control the active current flow (iD) to

reach the desired dc-link voltage.

• Control the output voltage of the

inverter to achieve the active current

flow desired by the dc-link voltage

control and the reactive current desired

by the reference.

Public Information © onsemi 2022

Cross Compensation

• The ac-line filter of the PFC topology

introduces a phase-shift between grid

and inverter output voltage.

• This phase-shift is accounted for by the

cross compensation.

To be clarify

with Daniel

Public Information © onsemi 2022

Dead-Time Correction

• A dead-time between on state of the

upper and lower switch of each half-

bridge comprising the inverter is

required to prevent shoot through.

• This dead-time changes the output of

the half-bridge depending on the

current.

• A correction term for each half-bridge

depending on its current is calculated

and the PWM output is adjusted

accordingly.

Public Information © onsemi 2022

DQ to ABC Transformation

• The steady dq values are transformed

back into rotating voltages to be output

by the inverter.

• Injection of a 3rd harmonic component

to the output voltage increases the

modulation factor.

Public Information © onsemi 2022

Pulse Width Modulation

• The ratio of inverter output voltage and

dc-link voltage is used to calculate the

duty cycle of the PWM module.

• This duty cycle is corrected by the

value computed during the dead-time

compensation.

Public Information © onsemi 2022

DAB Control Overview

Current

Control

With Soft-

Pulse Width

Start

Modulation

Current / Power

Limit

Voltage Flux

Control Compensatio

n

Public Information © onsemi 2022

Current / Power Limit

• Limit the output of the voltage

controller by either the current

reference or voltage reference.

• The smaller of the two is chosen.

• This results in

typical CC/CV

charging

characteristics Start CC CV

Public Information © onsemi 2022

Voltage Control

• Increase Current until either limit or

desired output voltage is reached.

• Identical to dc-link voltage control

of the Active FrontEnd (or PFC).

Public Information © onsemi 2022

Current Control with Soft-Start

• Control the phase-shift between No Soft-Start

primary and secondary side H-bridge

to achieve desired power flow.

• Soft-start prevents large resonant

currents during start-up by gradually

increasing the phase-shift With Soft-Start

Public Information © onsemi 2022

Pulse Width Modulation

• Create two carrier waves with a phase-

shift between them.

• Generate phase-shifted rectangular

voltages at the H-bridge outputs based

on the carrier waves

Public Information © onsemi 2022

Flux Compensation

No Flux Comp

• Inaccuracies in modulation, parasitic

influences, and operating point

changes lead to dc-currents on primary

and secondary side of transformer.

• The flux compensation reduces these

currents by slightly shifting the duty-

cycles of each H-bridge individually. With Flux Comp

Public Information © onsemi 2022

Conclusion

Public Information © onsemi 2022

Conclusion

• During this session, we have seen :

− We have analyzed the second part of the power stage : the Dual Active Bridge (DAB),

− Critical components’ (transformer and resonant inductor) effects were analyzed,

− Components selection was explained,

− Power stage simulation was shown,

− Control architecture for both stages were described.

• Next to come :

− Session 3 (June 15): Gate drivers, Auxiliary Supply and Thermal Approach

− Session 4 (June 29): Measurement Results

Public Information © onsemi 2022

Follow Us @onsemi

www.onsemi.com

You might also like

- Agilent Micro GC User InformationDocument160 pagesAgilent Micro GC User InformationRochim Bakti CahyonoNo ratings yet

- 2SB892 / 2SD1207: Data SheetDocument5 pages2SB892 / 2SD1207: Data SheetSamuel RodrigoNo ratings yet

- 2SA1469 / 2SC3746: Data SheetDocument4 pages2SA1469 / 2SC3746: Data SheetJavier Mendoza CastroNo ratings yet

- 2SA2169 / 2SC6017: High-Current Switching ApplicationsDocument5 pages2SA2169 / 2SC6017: High-Current Switching ApplicationsbambamtdoyNo ratings yet

- 2SB892/2SD1207: Large-Current Switching ApplicationsDocument5 pages2SB892/2SD1207: Large-Current Switching ApplicationsSandyNo ratings yet

- 2SB892/2SD1207: Large-Current Switching ApplicationsDocument4 pages2SB892/2SD1207: Large-Current Switching ApplicationsAbdul WahidNo ratings yet

- C4159 - Transistor Sin DamperDocument4 pagesC4159 - Transistor Sin DamperGerardo SarmientoNo ratings yet

- B764-Sanyo Semicon Device PDFDocument4 pagesB764-Sanyo Semicon Device PDFDiego LombeidaNo ratings yet

- Data Sheet: High-Voltage Switching ApplicationsDocument4 pagesData Sheet: High-Voltage Switching ApplicationsAnyun SangPemburuNo ratings yet

- KSA928A: PNP Epitaxial Silicon TransistorDocument4 pagesKSA928A: PNP Epitaxial Silicon Transistornanang c-kakakNo ratings yet

- 2SB892/2SD1207: Large-Current Switching ApplicationsDocument4 pages2SB892/2SD1207: Large-Current Switching ApplicationsFrancisco BandresNo ratings yet

- 2SB892/2SD1207: Large-Current Switching ApplicationsDocument4 pages2SB892/2SD1207: Large-Current Switching ApplicationsIrwantoirwanNo ratings yet

- DatasheetDocument4 pagesDatasheetIsmdark DarkNo ratings yet

- 2SB698/2SD734: 1W AF Output, Electronic Governor, DC-DC Converter ApplicationsDocument4 pages2SB698/2SD734: 1W AF Output, Electronic Governor, DC-DC Converter ApplicationsMauricio MaldonadoNo ratings yet

- Transitor 2SB647Document4 pagesTransitor 2SB647Louis CaraballoNo ratings yet

- 2SA1507 / 2SC3902: Data SheetDocument5 pages2SA1507 / 2SC3902: Data SheetJamgNo ratings yet

- 2CCS893001R0804 s803n c80Document4 pages2CCS893001R0804 s803n c80André Gogola VilarinhoNo ratings yet

- D1682 PDFDocument5 pagesD1682 PDFperro sNo ratings yet

- B1449 SanyoDocument5 pagesB1449 SanyogilvanNo ratings yet

- D863-Sanyo Semiconductor CorporationDocument4 pagesD863-Sanyo Semiconductor CorporationFrancisco Daniel ColimbaNo ratings yet

- 2SB817/2SD1047: 140V/12A AF 60W Output ApplicationsDocument4 pages2SB817/2SD1047: 140V/12A AF 60W Output ApplicationsEibar016No ratings yet

- 2SB817 - 2SD1047 PDFDocument4 pages2SB817 - 2SD1047 PDFisaiasvaNo ratings yet

- Transistor PNP B817 PDFDocument4 pagesTransistor PNP B817 PDFEstudiantes MacGregorNo ratings yet

- 2N4424 Silicon NPN Transistor DescriptionDocument5 pages2N4424 Silicon NPN Transistor DescriptionKarim KarimmNo ratings yet

- 2SC1815 Silicon NPN Transistor DescriptionDocument4 pages2SC1815 Silicon NPN Transistor DescriptionSamerNo ratings yet

- 2SC1815 Silicon NPN Transistor DescriptionDocument4 pages2SC1815 Silicon NPN Transistor DescriptionSamerNo ratings yet

- Unisonic Technologies Co., LTD: Audio Power AmplifierDocument4 pagesUnisonic Technologies Co., LTD: Audio Power Amplifierskazochnii.dolbenNo ratings yet

- Ae15b Ew-3076833Document8 pagesAe15b Ew-3076833skumar_945094No ratings yet

- 2 SD 1669Document4 pages2 SD 1669faraz jaanNo ratings yet

- S8550 маркировка 2TY JCSTDocument2 pagesS8550 маркировка 2TY JCSTZaegorNo ratings yet

- AIR Circuit Breaker: L.S.I.G CompactDocument2 pagesAIR Circuit Breaker: L.S.I.G CompactLUATNo ratings yet

- S1250-SE Data Sheet PDFDocument4 pagesS1250-SE Data Sheet PDFArun Senthil Nathan ViswanathanNo ratings yet

- Color TV Horizontal Deflection Output Applications: Data SheetDocument4 pagesColor TV Horizontal Deflection Output Applications: Data SheetJesus Wladimir RondonNo ratings yet

- PCS100 - 250 - 500 - 630 DatasheetDocument2 pagesPCS100 - 250 - 500 - 630 DatasheetKCB TechnologiesNo ratings yet

- PNP Silicon Elektronische Bauelemente: High Voltage PNP TransistorDocument3 pagesPNP Silicon Elektronische Bauelemente: High Voltage PNP TransistorNestor MartinNo ratings yet

- KSA928A PNP Epitaxial Silicon Transistor: FeaturesDocument6 pagesKSA928A PNP Epitaxial Silicon Transistor: FeaturessdfsdfsdNo ratings yet

- Prosurge Catalog SPV Series SPD For PV DCDocument2 pagesProsurge Catalog SPV Series SPD For PV DCElwanNo ratings yet

- Silicon PNP Power Transistors: 2SA1006 2SA1006A 2SA1006BDocument5 pagesSilicon PNP Power Transistors: 2SA1006 2SA1006A 2SA1006BMichael RamosNo ratings yet

- 2SB824Document5 pages2SB824enriquevazquez27No ratings yet

- 2 SD 1723Document4 pages2 SD 1723jose angel camara santosNo ratings yet

- Growatt 15000TL3-SL/ 20000TL3-SL/22000TL3-SL: Leading - Edge TechnologyDocument2 pagesGrowatt 15000TL3-SL/ 20000TL3-SL/22000TL3-SL: Leading - Edge TechnologyJohnny Alberto GaleanoNo ratings yet

- 2SB772SDocument3 pages2SB772SsdNo ratings yet

- Deye - SUN 5K SG01LP1 EU - DatasheetDocument2 pagesDeye - SUN 5K SG01LP1 EU - Datasheetwarick mNo ratings yet

- Dimensions - 700-HL Relays: Photo DescriptionDocument1 pageDimensions - 700-HL Relays: Photo DescriptionArif KhanNo ratings yet

- Mps 45a Darlington DriverDocument6 pagesMps 45a Darlington DriverporterfredNo ratings yet

- SDM120DB DatasheetDocument2 pagesSDM120DB DatasheetBalster van DuijnNo ratings yet

- ST330C16Document9 pagesST330C16Bruno NevesNo ratings yet

- 2SA968Document3 pages2SA968KhánhNo ratings yet

- RM-ST180 Jan 2021Document2 pagesRM-ST180 Jan 2021Jorge Rodriguez AlvaradoNo ratings yet

- JiangsuMJE2955 C78883Document3 pagesJiangsuMJE2955 C78883gabriel taberneroNo ratings yet

- PIN Connection Description: - Audio Power Amplifier - High Current ApplicationDocument4 pagesPIN Connection Description: - Audio Power Amplifier - High Current ApplicationJuan Angel AntaNo ratings yet

- KG105 enDocument2 pagesKG105 enramadhan kuNo ratings yet

- 2CCF019855R0001 s801s c4Document4 pages2CCF019855R0001 s801s c4Chandru MohanNo ratings yet

- KA2131 SamsungDocument4 pagesKA2131 SamsungTito PerezNo ratings yet

- 2SA1469/2SC3746: 60V/5A High-Speed Switching ApplicationsDocument3 pages2SA1469/2SC3746: 60V/5A High-Speed Switching ApplicationsJavier Mendoza CastroNo ratings yet

- Switching Applications (With Bias Resistance) : 2SA1519/2SC3913Document2 pagesSwitching Applications (With Bias Resistance) : 2SA1519/2SC3913vanmarteNo ratings yet

- Data Sheet: Ultrahigh-Definition CRT Display Horizontal Deflection Output ApplicationsDocument4 pagesData Sheet: Ultrahigh-Definition CRT Display Horizontal Deflection Output Applicationsphu chuNo ratings yet

- 2 Sa 1702Document4 pages2 Sa 1702mase fooNo ratings yet

- Ir2175 (S) & (PBF) : Linear Current Sensing IcDocument7 pagesIr2175 (S) & (PBF) : Linear Current Sensing IcDavid CoronadoNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- PLECS Model Quick Start Guide DS50002997ADocument37 pagesPLECS Model Quick Start Guide DS50002997Atakaca40No ratings yet

- The New Standard For Model Sharing and Collaboration: EbookDocument8 pagesThe New Standard For Model Sharing and Collaboration: Ebooktakaca40No ratings yet

- Getting To Know Vivado: Course WorkbookDocument54 pagesGetting To Know Vivado: Course Workbooktakaca40No ratings yet

- Designing Silicon Carbide (Sic) Based DC Fast Charging System: Key Challenges, Design Considerations, and Building ValidationDocument31 pagesDesigning Silicon Carbide (Sic) Based DC Fast Charging System: Key Challenges, Design Considerations, and Building Validationtakaca40No ratings yet

- Microzed Chronicles: Device Trees: Search All Content BlogDocument7 pagesMicrozed Chronicles: Device Trees: Search All Content Blogtakaca40No ratings yet

- Getting To Know Vivado: Workshop SeriesDocument4 pagesGetting To Know Vivado: Workshop Seriestakaca40No ratings yet

- Working With Vivado P2Document59 pagesWorking With Vivado P2takaca40No ratings yet

- Getting To Know Vivado: Course WorkbookDocument53 pagesGetting To Know Vivado: Course Workbooktakaca40No ratings yet

- Edge AIDocument156 pagesEdge AItakaca4067% (3)

- Dspic Control Board: For Industrial ApplicationsDocument5 pagesDspic Control Board: For Industrial Applicationstakaca40No ratings yet

- Using Python and Sockets: System Power Supply ProgrammingDocument6 pagesUsing Python and Sockets: System Power Supply Programmingtakaca40No ratings yet

- Kickd Pic32 Ubl ManualDocument18 pagesKickd Pic32 Ubl Manualtakaca40No ratings yet

- Proyectos Con 18f2550 y c18Document63 pagesProyectos Con 18f2550 y c18Garra Crema StoneNo ratings yet

- Training Manual ProvisionalDocument524 pagesTraining Manual ProvisionalArriola Sergio50% (2)

- Problem - Solution Essay PracticeDocument12 pagesProblem - Solution Essay PracticeHà NgânNo ratings yet

- UOP 3-16-7 - Storage Tanks AtmosphericDocument9 pagesUOP 3-16-7 - Storage Tanks Atmosphericjev_vdNo ratings yet

- Company Profile ElgiDocument4 pagesCompany Profile Elgiashish2783No ratings yet

- WCL Chandrapur FinalDocument30 pagesWCL Chandrapur FinalVikram SinghNo ratings yet

- MEC-A4-125B EnglishDocument2 pagesMEC-A4-125B Englishdragos manoleNo ratings yet

- Scion GC Series: The Gas Chromatographerhs Choice For SeparationsDocument12 pagesScion GC Series: The Gas Chromatographerhs Choice For SeparationsLABSSSSSNo ratings yet

- Antennacraft ST2 Scanner Antenna ManualDocument2 pagesAntennacraft ST2 Scanner Antenna ManualdonsterthemonsterNo ratings yet

- Fire Extinguisher Location and Placement: Fact SheetDocument2 pagesFire Extinguisher Location and Placement: Fact SheetEli NaguitNo ratings yet

- Daikin Room Air Conditioner ManualDocument30 pagesDaikin Room Air Conditioner ManualsmithworkNo ratings yet

- Maperod C I Maperod GDocument4 pagesMaperod C I Maperod GdraganugNo ratings yet

- Energy Audit My QuestionsDocument8 pagesEnergy Audit My QuestionsSahathullah AhamedNo ratings yet

- VonRoll Geschaeftsbericht 2017 ENDocument116 pagesVonRoll Geschaeftsbericht 2017 ENraul_beronNo ratings yet

- JEE-Adv Grand Test Question Paper (P 1) - 14-05-2014Document24 pagesJEE-Adv Grand Test Question Paper (P 1) - 14-05-2014Ranjan PrasadNo ratings yet

- Diamond - EnglishDocument24 pagesDiamond - EnglishTopcom Toki-VokiNo ratings yet

- 9065PD9501 Developments in Motor Protection 1996Document12 pages9065PD9501 Developments in Motor Protection 1996shockthemonkeyNo ratings yet

- Eikonal EquationDocument23 pagesEikonal Equationfitriah wulandariNo ratings yet

- Load Flow Studies - Lecture Notes 2Document29 pagesLoad Flow Studies - Lecture Notes 2Snr Berel Shepherd100% (1)

- Procedure (Ams 2750e)Document2 pagesProcedure (Ams 2750e)SIVAKUMAR NATARAJANNo ratings yet

- Meningkatkan Nilai Jual Proyek InfrastrukturDocument54 pagesMeningkatkan Nilai Jual Proyek InfrastruktureddyhusinNo ratings yet

- Product Data Sheet: Earth-Leakage Relay RH86M With Manual Reset - 0.03..10 A - 0.5 S - 220-240 VDocument2 pagesProduct Data Sheet: Earth-Leakage Relay RH86M With Manual Reset - 0.03..10 A - 0.5 S - 220-240 VAnggiet ZoaNo ratings yet

- Truma Camping World Int GBDocument91 pagesTruma Camping World Int GBIngrid LewisNo ratings yet

- Sprinkler DesignDocument10 pagesSprinkler Designsk lukoNo ratings yet

- A4-P 13.0 enDocument13 pagesA4-P 13.0 enAtiq Ur RehmanNo ratings yet

- Heat Transfer Design Methods // John J. Mcketta JRDocument5 pagesHeat Transfer Design Methods // John J. Mcketta JRRizky Irfattah SNo ratings yet

- E-Bike PPT Review 3Document29 pagesE-Bike PPT Review 3karthick shivaNo ratings yet

- 855HM Instruction Sheet 10001245826 Rev 1Document4 pages855HM Instruction Sheet 10001245826 Rev 1luis.chuquimiaNo ratings yet

- Hydraulic Roller PressDocument8 pagesHydraulic Roller Pressusmanny100% (1)

- AR 50 SP Cod. 401: Technical Speci CationsDocument3 pagesAR 50 SP Cod. 401: Technical Speci CationsHIDROIL PERUNo ratings yet