Professional Documents

Culture Documents

Sisngle Phase Rectifier

Sisngle Phase Rectifier

Uploaded by

mücahitOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Sisngle Phase Rectifier

Sisngle Phase Rectifier

Uploaded by

mücahitCopyright:

Available Formats

IJSRD - International Journal for Scientific Research & Development| Vol.

8, Issue 2, 2020 | ISSN (online): 2321-0613

Analysis of Control Strategy of Active Front End Converter for R-Load

Vibha B. Patel1 Karan R. Thawani2

1

Sakalchand Patel University, Visanagar, Gujarat, India 2Hitachi Hirel Power Electronics Pvt Ltd., India

Abstract— This paper represents the simulation and analysis Today, the AFE systems can be used as an interesting

of a front-end converter. The term Active Front End Inverter solution to realize AC drives. The AFE’s main advantages

refers to the power converter system consisting of the line- are the four quadrants operation mode and the full control in

side converter with active switches such as IGBTs, the dc- regenerative braking. Moreover, AFEs guarantee high

link capacitor bank, and the load-side inverter. Active front power quality giving very good performance in terms of

end converter (AFE or FEC) converts the AC to DC or DC Power Factor (PF) and Total Harmonic Distortion (THD) of

to AC. The basic objective of AFE is to regulate the DC the supply currents and supply voltages on the ac side

output voltage and make the line side power factor unity. [4][5][6]. The two main objectives of the AFE are the

The main advantage of this converter is to eliminate the regulation of the dc output voltage and the compensation for

lower order harmonics or to reduce the total harmonic undesired harmonics on the line current [4] [7].

distortion (THD) caused by a large nonlinear load. And it is

done by using the PWM technique. Sinusoidal pulse width II. POWER CIRCUIT OF ACTIVE FRONT END CONVERTER

modulation (SPWM) is a popular technique used for the

control of output voltage. By changing the modulation

index, both the frequency and magnitude of the output

voltage can be controlled. The modulation index increases

as the fundamental line voltage increases. Thus, by changing

the modulation index we can able to change the voltage.

Keywords: total harmonic distortion (THD), PWM

technique, Sinusoidal pulse width modulation (SPWM),

AFC system

I. INTRODUCTION

Front end converters are becoming an interesting solution

for power factor correction and low frequency current

harmonic elimination in static power conversion systems.

The term Front End Converter refers to the power converter

system consisting of the line-side converter with active

switches such as IGBTs, the dc-link capacitor bank, and the

load-side inverter. The line-side converter normally

functions as a rectifier. But, during regeneration it can also Fig. 2.1: Power Circuit of Active Front End Converter

be operated as an inverter, feeding power back to the line. The Power circuit is mainly divided into the following parts:

The line-side converter is popularly referred to as a PWM 1) Single-Phase Step-Down Transformer

rectifier in the literature. This is due to the fact that, with 2) Pre-charge resistor and contactor

active switches, the rectifier can be switched using a suitable 3) IGBT PWM Rectifier

pulse width modulation technique. The PWM rectifier 4) DC Link or DC Bus

basically operates as a boost chopper with ac voltage at the A. Single-Phase Step-Down Transformer

input, but dc voltage at the output. The intermediate dc-link It is used to step down the grid voltage with the

voltage should be higher than the peak of the supply voltage transformation ratio, V1/V2= 26.69. It is also used as a

[1]. This is required to avoid saturation of the PWM booster to step up the DC Voltage. Hence no other boosting

controller due to insufficient dc-link voltage, resulting in inductor is required.

line side harmonics.

The required dc-link voltage needs to be B. Pre-charge Resistor and Contactor

maintained constant during rectifier as well as inverter The capacitor acts as a short circuit at the moment instant

operation of the line side converter. The ripple in dc-link when applying DC voltage, hence it draws a very large

voltage can be reduced using an appropriately sized amount of current from the grid which may result in the

capacitor bank [2][3]. The active front-end inverter topology damage of the power semiconductor device and the

for a motor drive application. capacitor itself. Hence pre-charge resistor is used to limit

For a constant dc-link voltage, the IGBTs in the the starting current drawn from the DC link capacitors and

line-side converter are switched to produce at input to smoothly charge the DC bus. It is then bypassed by the

terminals. The line-side PWM voltages, generated in this contactor when the sufficient DC link voltage is achieved.

way, control the line currents to the desired value. When the

dc-link voltage drops below the reference value, the feed- C. IGBT Based PWM Rectifier

back diodes carry the capacitor charging currents, and bring PWM Based IGBT rectifier is used to boost up the DC link

the dc-link voltage back to reference value. Voltage to the 1800V. It also provides a unity power factor

and reduces the THD in the input current.

All rights reserved by www.ijsrd.com 63

Analysis of Control Strategy of Active Front End Converter for R-Load

(IJSRD/Vol. 8/Issue 2/2020/015)

D. DC Link or DC Bus into the DC quantity by transforming this vector into the dq-

DC link capacitor is placed in parallel with the load to rotating reference frame.

minimize the effects of voltage variations as the load Since we know that when the frequency and phase

changes. The DC-link capacitor also provides a low- of the d-rotating reference frame is aligned with the alpha

impedance path for ripple currents generated by power component, then the Vd = Peak amplitude of the alpha

switching circuits. component and Vq = 0. Hence, this condition is used to

control the speed of the dq-rotating reference frame in such

III. CONTROL CIRCUIT OF ACTIVE FRONT END CONVERTER a way that Vq becomes zero. The actual Vq is compared

with the Vq(reference) i.e. 0. The difference between the

The Control Method is mainly divided into the following actual Vq and Vq(reference) is called the error which is then

parts: applied to the PI controller. The aim of the PI controller is to

1) Start-up logic reduce this error and generate the omega in such a way that

2) Phase Lock Loop this error becomes zero.

3) SPWM Control Loop This omega is then integrated to generate the theta

A. Start-up logic which is then fed back to the dq the rotating reference frame

for the closed loop control of the theta.

The pre-charge resistor is used to limit the starting current

drawn from the DC link capacitors and to smoothly charge C. SPWM Control

the DC bus. In the start-up control circuit, DC link voltage is

compared with 1160 VDC. When the soft-start finishes and

DC link voltage crosses the 1160V, then START=1 and pre-

charge resistor is then bypassed by the contactor.

PWM Start Logic: It takes around 0.2 seconds to

smoothly charge the DC bus through pre-charge resistor and

PWM are started with a delay of 0.4 seconds. Hence by that

time, DC link is built up through IGBT body diodes.

Hence when START=1 and the delay of 0.4 seconds is

achieved, then the PWM flag is setup and the PWM control

loop is started.

B. Phase Lock Loop

To maintain the input power factor to unity, the input grid

voltage phase and frequency must be known. Hence Phase

Lock Loop is used to generate a Theta (in radians) in such a

way that this theta is the same as the theta of the input grid

voltage.

Fig. 3.2: SPWM Control Circuit for open loop

For now, the control circuit is implemented with a fixed

modulation index of 0.61 which means open loop control of

dc-link voltage. This control loop generates the gating

signals for the power semiconducting devices. Theta

obtained from PLL is used to generate the unity sine wave

which is then multiplied with the fixed modulation index of

0.61 to generate the reference sine wave for Phase lag 1.

This sine wave is then inverted which becomes the reference

sine wave for phase lag 2. This both sine waves are then

compared with the high frequency carrier wave for the

generation of gating signals. When the amplitude of the

reference sine wave 1 is greater than the carrier wave, the

Fig. 3.1: Control Circuit of PLL IGBT1 is turn on and invert logic is applied for the IGBT2.

First, The Vgrid is scaled down by the gain of Similarly, when the amplitude of the reference sine wave 2

25000*1.412. Then it is applied as an alpha component to is greater than the carrier wave, the IGBT3 is turn on and

the Alpha-beta stationary reference frame. Since we have invert logic is applied for the IGBT4.

only one phasor as an input, this alpha component is delayed

by 90° to generated the beta component of the Alpha-beta

stationary reference frame. These vectors are then converted

All rights reserved by www.ijsrd.com 64

Analysis of Control Strategy of Active Front End Converter for R-Load

(IJSRD/Vol. 8/Issue 2/2020/015)

IV. SIMULATION RESULTS

Fig. 3.3: DC Link Voltage Control Loop

This loop is started when the sufficient DC is built

up through the pre-charge circuit and the PWM delay flag is Fig. 5.1: Controlled Vd Generated from PLL

set to high. This loop maintains the Output DC Voltage to

the Vdc(reference) considering the allowable ripple voltage.

Here, the actual DC Voltage is compared with the

Vdc(reference) i.e. 1800V. The difference between the

actual DC Voltage and Vdc(reference) is called the error in

the DC voltage with reference to Vdc(reference). This error

signal is applied to the PI controller. The aim of the PI

controller is to reduce this error in the DC Voltage and

produce the equivalent current signal.

Fig. 5.2: Controlled Vq Generated from PLL

Fig. 5.3: Controlled Theta Generated from PLL

Fig. 3.4: SPWM Control Circuit for close loop

The input signal to this control loop is the error in

the actual DC voltage to achieve the required VDC and to

maintain the power factor to the unity. This control loop

generates the gating signals for the power semiconducting

devices. Theta obtained from PLL is used to generate the

unity sine wave which is then multiplied with the output of

the PI controller to generate the reference sine wave for

Phase lag 1. This sine wave is then inverted which becomes

the reference sine wave for phase lag 2. This both sine

waves are then compared with the high frequency carrier

wave for the generation of gating signals. When the

amplitude of the reference sine wave 1 is greater than the

carrier wave, the IGBT1 is turn on and invert logic is

applied for the IGBT2. Similarly, when the amplitude of the

reference sine wave 2 is greater than the carrier wave, the Fig. 5.4: Comparison of Sine Wave Generated from

IGBT3 is turn on and invert logic is applied for the IGBT4. Theta(PLL) and Theta(REF)

All rights reserved by www.ijsrd.com 65

Analysis of Control Strategy of Active Front End Converter for R-Load

(IJSRD/Vol. 8/Issue 2/2020/015)

Fig. 5.8: Input Grid Voltage & Current Waveform at Steady

State

Fig. 5.5: Output DC Voltage Waveforms with SPWM

Control

Fig. 5.9: Output DC Voltage Waveforms with SPWM

Control for Close loop

Here, we can see the different results of the open

loop and close loop proposed circuit with their analysis at

different modulation index.

V. CONCLUSION

Closed loop AFC system is more reliable than open loop

AFC system because it automatically adjusts the modulation

Fig. 5.6: Input Grid Voltage Waveform

index as load changes. Hence, we get the desired DC-link

voltage from 0 to 100% rated load. Open loop means there

is no feedback of DC-link voltage. By adjusting the

modulation index, we get our desired DC-link voltage and it

is for fixed defined load only. If the load will change, DC-

link voltage will be changed because there is no feedback

loop and there is no closed loop control of the DC-link

voltage. Closed loop means there is the feedback of DC-link

voltage and by controlling the DC-link voltage (Maintaining

the DC-link voltage at the desired reference value in all load

conditions), modulation index is automatically adjusted as

load changes.

Fig. 5.7: Input Grid Current Waveform during Pre-charge

REFERENCES

Time

[1] Grahame Holmes D., Thomas A. L., “Pulse Width

Modulation for Power Converters – Principles and

practice”, IEEE Press Series on Power Engineering,

ISBN: 0-471-20814-0

All rights reserved by www.ijsrd.com 66

Analysis of Control Strategy of Active Front End Converter for R-Load

(IJSRD/Vol. 8/Issue 2/2020/015)

[2] A. Ndokaj* and A. Di Napoli* *Roma Tre University,

Dept. of Ind. and Mecc. Engeneering, (Italy)

“Converter Simultaneously as Active Front End and as

Active Filter” 552978-1-4673-4430-2/13/$31.00 ©2013

IEEE

[3] A. Ndokaj* and A. Di Napoli* *Roma Tre University,

Dept. of Ind. and Mecc. Engeneering, (Italy) “Active

Front End in Presence of Voltage Notches”, 978-1-

4799-8704-7/15/$31.00 ©2015 IEEE

[4] L. Di Donna, F. Liccardo*, P. Marino*,C. Schiano*, M.

Triggianese* * Seconda Università degli Studi di

Napoli / Dipartimento di Ingegneria dell’Informazione,

Aversa (CE), Italy “Single-Phase Synchronous Active

Front-End for High Power Applications”, IEEE ISIE

2005, June 20-23, 2005, Dubrovnik, Croatia

[5] G. Carpinelli, P. Marino, A. Testa, F. Vasca,

“Optimizing The Industrial System Utility Interface by

Means of AC/DC Boost Converters”, in Proc.

AFRICON 1996

[6] Castaldo, D. Gallo, P. Marino, N. Visciano,

“Probabilistic Criteria for Reactive Power

Compensation in Presence of an Active Front-End” in

Proc. PMAPS 2002

[7] F. Liccardo, Student Member, IEEE, P. Marino, and C.

Schiano “High-performance Single-phase High-power

Active Front-End”

All rights reserved by www.ijsrd.com 67

You might also like

- SVPWM Thesis Prepared by DeekshitDocument81 pagesSVPWM Thesis Prepared by Deekshitchunduri_rambabuNo ratings yet

- J'14 - Analysis, Design and Performance of A Soft-Switching Single-Phase InverterDocument12 pagesJ'14 - Analysis, Design and Performance of A Soft-Switching Single-Phase Inverter閒雲野鶴No ratings yet

- Iceets 2013 6533563Document9 pagesIceets 2013 6533563Steni MoaiNo ratings yet

- Analysis of Predictive Control For Active Power Factor CorrectioDocument6 pagesAnalysis of Predictive Control For Active Power Factor Correctioezloy80No ratings yet

- LM25005, LM25010: Buck Regulator Topologies For Wide Input/Output Voltage DifferentialsDocument10 pagesLM25005, LM25010: Buck Regulator Topologies For Wide Input/Output Voltage DifferentialsBejoy ThomasNo ratings yet

- Nan Kalayar HlaingDocument5 pagesNan Kalayar HlaingThet TinNo ratings yet

- Carrier Based Sinusodial PWM Scheme For The Nine Switch ConverterDocument6 pagesCarrier Based Sinusodial PWM Scheme For The Nine Switch ConverterShankar MukalNo ratings yet

- E3sconf Posei2021 02021Document4 pagesE3sconf Posei2021 02021WilliamNo ratings yet

- Unit-2-Converter and HVDC System ControlDocument14 pagesUnit-2-Converter and HVDC System ControlT shivaprasad100% (1)

- 1999apr08 Icd PD Tac2Document11 pages1999apr08 Icd PD Tac2King GervinhoNo ratings yet

- Application of DC/DC Buck Power Converter in DC Motor For Speed Controlling Using PI ControllerDocument5 pagesApplication of DC/DC Buck Power Converter in DC Motor For Speed Controlling Using PI ControllerShreeji ExportsNo ratings yet

- Buck Boost ConverterDocument5 pagesBuck Boost ConverterZhang EnjuneNo ratings yet

- Design of A Synchronous Rectified Switching Regulator Chip For CPU Power SupplyDocument4 pagesDesign of A Synchronous Rectified Switching Regulator Chip For CPU Power SupplysrdjanNo ratings yet

- A Novel Switch Mode DC-AC Inverter With Nonlinear Robust Control (IEEE-TIE)Document7 pagesA Novel Switch Mode DC-AC Inverter With Nonlinear Robust Control (IEEE-TIE)Al Bajad MamadNo ratings yet

- Zeta Converter PidDocument7 pagesZeta Converter Pidvenkateswarlu chamalaNo ratings yet

- Reduction of Harmonic Distortions in BLDC Motor Power Supply Using SEPIC ConverterDocument6 pagesReduction of Harmonic Distortions in BLDC Motor Power Supply Using SEPIC ConverterRahardian TristantoNo ratings yet

- Unit 2 - NewDocument61 pagesUnit 2 - NewMonster AmanNo ratings yet

- Unit-2-Converter and HVDC System ControlDocument13 pagesUnit-2-Converter and HVDC System Controlravikumar_ranganNo ratings yet

- 1.1 Introduction To Buck ConverterDocument44 pages1.1 Introduction To Buck Converterapi-19810277No ratings yet

- Power Electronics Chapter 2-2: Applications of Semiconductor DevicesDocument18 pagesPower Electronics Chapter 2-2: Applications of Semiconductor DevicestesfuNo ratings yet

- SEPIC AC-DC Converter For Aircraft Application: Bassim M.H. JassimDocument5 pagesSEPIC AC-DC Converter For Aircraft Application: Bassim M.H. JassimsabinebachNo ratings yet

- 06533563Document8 pages06533563MadhavanIceNo ratings yet

- 10 1109@pesc 1997 616727 PDFDocument7 pages10 1109@pesc 1997 616727 PDFjeos20132013No ratings yet

- University of Engineering & Technology LahoreDocument43 pagesUniversity of Engineering & Technology LahoreKantesh KumarNo ratings yet

- Power Factor Improvement of The System: Abhishek Kumar, Manisha Kushwaha, Ratnesh Shukla, Vishal Sharma, NaimuddinDocument3 pagesPower Factor Improvement of The System: Abhishek Kumar, Manisha Kushwaha, Ratnesh Shukla, Vishal Sharma, Naimuddinanil kasotNo ratings yet

- A Novel Soft-Switching Single-Phase AC-DC-AC Converter Using New ZVS-PWM StrategyDocument2 pagesA Novel Soft-Switching Single-Phase AC-DC-AC Converter Using New ZVS-PWM Strategyskumar_61719No ratings yet

- Design and Performance Analysis of 400Hz Static Frequency ConverterDocument3 pagesDesign and Performance Analysis of 400Hz Static Frequency ConverterEditor IJTSRDNo ratings yet

- Ilovepdf MergedDocument119 pagesIlovepdf MergedkushalNo ratings yet

- Heavy Load Light Load Conversion ReportDocument41 pagesHeavy Load Light Load Conversion ReportSanjivee SachinNo ratings yet

- Transformer Based Resonant DC Inverter For Brushless DC Motor Drive SystemDocument7 pagesTransformer Based Resonant DC Inverter For Brushless DC Motor Drive SystemStudents Xerox ChidambaramNo ratings yet

- Shyam Course ProjectDocument6 pagesShyam Course ProjectBhukya Reethvik RathodNo ratings yet

- Power Electronics Interface For PV SysteDocument7 pagesPower Electronics Interface For PV SysteSreepadam PadamNo ratings yet

- DC - AC ConvertorsDocument3 pagesDC - AC Convertorskarthick LNo ratings yet

- A High-Efficiency QR Flyback DC-DC Converter WithDocument21 pagesA High-Efficiency QR Flyback DC-DC Converter WithRakesh SandarativjuNo ratings yet

- A Feedback Linearizing Control Scheme For ADocument8 pagesA Feedback Linearizing Control Scheme For AFatih BurakNo ratings yet

- Inverter Distributed: Controller Generation SystemsDocument7 pagesInverter Distributed: Controller Generation SystemsJohnNo ratings yet

- Implementation of PSR in Flyback ConvertersDocument9 pagesImplementation of PSR in Flyback ConvertersNehaoua FaresNo ratings yet

- Design and Simulation of Triggering Circ PDFDocument4 pagesDesign and Simulation of Triggering Circ PDFYimy GarciaNo ratings yet

- High-Power Density Design of A Soft-Switching High-Power Bidirectional DC-DC ConverterDocument9 pagesHigh-Power Density Design of A Soft-Switching High-Power Bidirectional DC-DC Convertermurthy237No ratings yet

- Analysis of Chopper Fed D.C. Drive With PWM & Hysteresis Current Control SchemeDocument8 pagesAnalysis of Chopper Fed D.C. Drive With PWM & Hysteresis Current Control SchemeS Bharadwaj ReddyNo ratings yet

- Modeling and Simulation of Bidirectional Ac-Dc Power ConverterDocument4 pagesModeling and Simulation of Bidirectional Ac-Dc Power ConverterKalyan Reddy AnuguNo ratings yet

- Closed Loop Buck & Boost Converter Mathematical Modeling, Analysis and Simulation Using MATLABDocument9 pagesClosed Loop Buck & Boost Converter Mathematical Modeling, Analysis and Simulation Using MATLAB7031 GauravNo ratings yet

- Applying To Control Overcurrents at Unbalanced Faults of Forced-Commutated Vscs Used As Static Var CompensatorsDocument6 pagesApplying To Control Overcurrents at Unbalanced Faults of Forced-Commutated Vscs Used As Static Var CompensatorsJULFANRI SIRAITNo ratings yet

- An Experimental Prototype of Buck Converter Fed Series DC Motor Implementing Speed and Current ControlsDocument4 pagesAn Experimental Prototype of Buck Converter Fed Series DC Motor Implementing Speed and Current ControlsdevchandarNo ratings yet

- Performance of Difference PFC Converter For Improved Converter Efficiency: A ReviewDocument6 pagesPerformance of Difference PFC Converter For Improved Converter Efficiency: A ReviewJohn PetersNo ratings yet

- Design and Application For PV Generation System Using A Soft-Switching Boost Converter With SARCDocument13 pagesDesign and Application For PV Generation System Using A Soft-Switching Boost Converter With SARCIJERDNo ratings yet

- Cost Effective AC-DC Buck-Boost Converter For Single Phase Upf Load With Optimum Dynamic PerformanceDocument7 pagesCost Effective AC-DC Buck-Boost Converter For Single Phase Upf Load With Optimum Dynamic Performanceplay storeNo ratings yet

- Simulation and Prototype Implementation of Phase Shift Full Bridge DC DC ConverterDocument4 pagesSimulation and Prototype Implementation of Phase Shift Full Bridge DC DC ConverterjimmyNo ratings yet

- Design of A Power Converter Based On UC3842 For Blade Electric VehicleDocument6 pagesDesign of A Power Converter Based On UC3842 For Blade Electric VehicleHossam SobhyNo ratings yet

- High Efficiency Power Conversion Using A Matrix Converter: Jun-Ichi Itoh Akihiro Odaka Ikuya SatoDocument0 pagesHigh Efficiency Power Conversion Using A Matrix Converter: Jun-Ichi Itoh Akihiro Odaka Ikuya Satomenilanjan89nLNo ratings yet

- Buck RegulatorDocument6 pagesBuck RegulatorBhukya Reethvik RathodNo ratings yet

- Q 7) Explain The Basic Principle of Control in HVDCTDocument12 pagesQ 7) Explain The Basic Principle of Control in HVDCTrasashpujNo ratings yet

- Final ReviewDocument19 pagesFinal ReviewSanyam JainNo ratings yet

- Buck Boost Converter ReportDocument5 pagesBuck Boost Converter ReportMehedi HasanNo ratings yet

- Analysis and Construction of Push Pull Converter - Noor Rulmuna Bt. Mohd Sarmin - TK7872.C8.N66 2006Document27 pagesAnalysis and Construction of Push Pull Converter - Noor Rulmuna Bt. Mohd Sarmin - TK7872.C8.N66 2006Rizwan FaizNo ratings yet

- A Single-Phase Isolated Z-Source Inverter: Swetadri Ghosh, Koustuv Sarkar, Dipten Maiti, Sujit K. BiswasDocument4 pagesA Single-Phase Isolated Z-Source Inverter: Swetadri Ghosh, Koustuv Sarkar, Dipten Maiti, Sujit K. BiswassaiNo ratings yet

- Slup 075Document12 pagesSlup 075Gowtham SanampalliNo ratings yet

- Microchip CLC DescriptionDocument12 pagesMicrochip CLC DescriptionKamlesh YadavNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- SVM Algorithm of Three-Level NPC Inverter: Shanmei Cheng and Yajun Liu Bing WuDocument5 pagesSVM Algorithm of Three-Level NPC Inverter: Shanmei Cheng and Yajun Liu Bing WumücahitNo ratings yet

- Multilevel Grid-Connected Inverter Performance Under Different Modulation StrategiesDocument8 pagesMultilevel Grid-Connected Inverter Performance Under Different Modulation StrategiesmücahitNo ratings yet

- PWM Techniques & AC DrivesDocument9 pagesPWM Techniques & AC DrivesmücahitNo ratings yet

- DC Link Capacitor Voltage Balancing in Three Level Neutral Point Clamped InverterDocument5 pagesDC Link Capacitor Voltage Balancing in Three Level Neutral Point Clamped InvertermücahitNo ratings yet

- Journal Jpe 17-1 2098064263Document12 pagesJournal Jpe 17-1 2098064263mücahitNo ratings yet

- Journal Jpe 19-2 948324673Document9 pagesJournal Jpe 19-2 948324673mücahitNo ratings yet

- Transformer-Less Single-Phase Four-Level InverterDocument10 pagesTransformer-Less Single-Phase Four-Level InvertermücahitNo ratings yet

- Journal Jpe 13-5 343243127Document11 pagesJournal Jpe 13-5 343243127mücahitNo ratings yet

- The Peak Current Control of Permanent Magnet Brushless DC Machine With Asymmetric Dual-Three PhasesDocument7 pagesThe Peak Current Control of Permanent Magnet Brushless DC Machine With Asymmetric Dual-Three PhasesmücahitNo ratings yet

- Fusible Tipo KearneyDocument8 pagesFusible Tipo KearneyjuxagoNo ratings yet

- AC Pro II Trip UnitDocument60 pagesAC Pro II Trip UnitThe SignNo ratings yet

- Power Consumption of RefrigeratorsDocument10 pagesPower Consumption of RefrigeratorsAhmed HsabryNo ratings yet

- Nova-M Prefabricated Metal Transformer Substation: Main CharacteristicsDocument1 pageNova-M Prefabricated Metal Transformer Substation: Main CharacteristicsAnonymous 1AAjd0No ratings yet

- Restoring Power With Confidence: 14kW, 17kW, & 20kW Standby GeneratorsDocument2 pagesRestoring Power With Confidence: 14kW, 17kW, & 20kW Standby GeneratorsitcmiguelNo ratings yet

- Cigre AUS 2011 HVDC & GridAccess Tutorial Re PDFDocument111 pagesCigre AUS 2011 HVDC & GridAccess Tutorial Re PDFmhd986No ratings yet

- SM6-36 SM62D336DG6X000001Document2 pagesSM6-36 SM62D336DG6X000001Marko Maky ZivkovicNo ratings yet

- Uninterrupted Power Uninterrupted Service: Netpro-33HDocument4 pagesUninterrupted Power Uninterrupted Service: Netpro-33HLbar SidiyaNo ratings yet

- GSR 54 (E)Document3 pagesGSR 54 (E)jiguparmar1516No ratings yet

- AC DC ConverterDocument21 pagesAC DC ConverterHải Nguyễn CôngNo ratings yet

- Electric Machinery ProblemsDocument2 pagesElectric Machinery ProblemsRogzJrBernzNo ratings yet

- GA Electrical Boxes VFDDocument14 pagesGA Electrical Boxes VFDPornyutNo ratings yet

- Power AnalysisDocument14 pagesPower AnalysisVimala ElumalaiNo ratings yet

- Printed by SYSUSER: Dial Toll Free 1912 For Bill & Supply ComplaintsDocument1 pagePrinted by SYSUSER: Dial Toll Free 1912 For Bill & Supply ComplaintsSuhelNo ratings yet

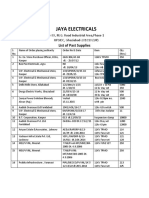

- Jaya Electricals AB Switch Drop Out Fuse Set Isolator SMC Box CT PTDocument2 pagesJaya Electricals AB Switch Drop Out Fuse Set Isolator SMC Box CT PTSharafat AliNo ratings yet

- Seven Level InverterDocument41 pagesSeven Level InverterAYONA THOMASNo ratings yet

- Datasheet MultiGrid 3000VA enDocument2 pagesDatasheet MultiGrid 3000VA enJason CarrNo ratings yet

- Nexus 1500 ManualDocument238 pagesNexus 1500 Manualpb21No ratings yet

- Experiment No. 5 Overcurrent and Undercurrent Relay: ObjectiveDocument4 pagesExperiment No. 5 Overcurrent and Undercurrent Relay: ObjectiveMian Tauseef100% (1)

- CDG 1131Document4 pagesCDG 1131AnilNo ratings yet

- PDFDocument33 pagesPDFTechno madNo ratings yet

- Reference DAPPER PDFDocument124 pagesReference DAPPER PDFangel lozadaNo ratings yet

- Building 7Document1 pageBuilding 7Arshad AlamNo ratings yet

- E 7068 B0 Airmeex De65e0Document5 pagesE 7068 B0 Airmeex De65e0Mehdi HassouneNo ratings yet

- Danfoss VLT5000 Users Manual01Document192 pagesDanfoss VLT5000 Users Manual01krisNo ratings yet

- 1 - Power Electronics CatalogueDocument83 pages1 - Power Electronics CataloguerockNo ratings yet

- Catalog SIPROTEC Compact 3.01Document210 pagesCatalog SIPROTEC Compact 3.01janarthananNo ratings yet

- Guide To Low Voltage System Design and SelectivityDocument40 pagesGuide To Low Voltage System Design and SelectivityShung Tak ChanNo ratings yet

- 1SFA898115R7000 pstx370 600 70 SoftstarterDocument3 pages1SFA898115R7000 pstx370 600 70 SoftstarterChitranjan KumarNo ratings yet

- Electric Machines EEE241 LAB Report#3: Name Registration Number Teacher Date of SubmissionDocument7 pagesElectric Machines EEE241 LAB Report#3: Name Registration Number Teacher Date of Submissionbilal ahmedNo ratings yet