Professional Documents

Culture Documents

0 ratings0% found this document useful (0 votes)

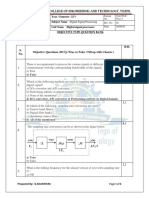

3 viewsDspa Mid 1 Paper

Dspa Mid 1 Paper

Uploaded by

Panku RangareeThis document contains a mid-term exam for a Digital Signal Processor and Architecture course. It has two parts: Part A contains 5 multiple choice questions worth 5 marks each and Part B contains 10 multiple choice questions worth 0.5 marks each. The exam assesses 5 course outcomes related to understanding digital signal processing systems and techniques, distinguishing features of general processors and DSP processors, and analyzing interfaces between devices and DSP processors.

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

You might also like

- Saueressig T. Business As Unusual With SAP... 2022Document569 pagesSaueressig T. Business As Unusual With SAP... 2022Srinivasan MeshramNo ratings yet

- Flysmart+ For Ipad Applications V5.0: Installation Guide - RevbDocument22 pagesFlysmart+ For Ipad Applications V5.0: Installation Guide - RevbrameauNo ratings yet

- Clapswitchpbl 2Document22 pagesClapswitchpbl 2Panku RangareeNo ratings yet

- Lab 2 - Working With Data StorageDocument15 pagesLab 2 - Working With Data StorageMangesh AbnaveNo ratings yet

- Clat2 Set-B Answer KeyDocument7 pagesClat2 Set-B Answer KeyVikram ChaudharyNo ratings yet

- CT2 QP SetBDocument5 pagesCT2 QP SetBsansheela2014No ratings yet

- MEL G642-Compre Solution - 2 2016-17Document9 pagesMEL G642-Compre Solution - 2 2016-17Gaurav PatilNo ratings yet

- 15A05502 Computer NetworksDocument2 pages15A05502 Computer NetworksKiran Kumar BoddepalliNo ratings yet

- Third Internal Assessment Question PaperDocument1 pageThird Internal Assessment Question Papersyed1188No ratings yet

- Iiiy VS U3 Ee8591 DSP 2020 2021Document1 pageIiiy VS U3 Ee8591 DSP 2020 2021syed1188No ratings yet

- Dspa Question BankDocument2 pagesDspa Question BankPanku RangareeNo ratings yet

- Thapar Institute of Engineering & Technology, Patiala: End Semester Examination (May 2019)Document4 pagesThapar Institute of Engineering & Technology, Patiala: End Semester Examination (May 2019)Forza HorizonNo ratings yet

- Ct3 Set B Adc Answer KeyDocument17 pagesCt3 Set B Adc Answer Keypa2195No ratings yet

- Digital Signal Processing LabDocument6 pagesDigital Signal Processing LabTHABO KEITH DUBENo ratings yet

- MP Mid TermDocument4 pagesMP Mid TermHassan AamerNo ratings yet

- DSP Question Paper April 2012Document2 pagesDSP Question Paper April 2012Famida Begam100% (1)

- DSP Lab Manual - FinalDocument72 pagesDSP Lab Manual - FinalSwetNo ratings yet

- Embedded Micro Controller Test SolutionDocument9 pagesEmbedded Micro Controller Test SolutionalikaastridNo ratings yet

- EETP DSS W1 Job Aid PDFDocument6 pagesEETP DSS W1 Job Aid PDFAnkita BajpaiNo ratings yet

- 1997 TCASII I. Galton Spectral Shaping of Circuit Errors in Digital To Analog ConvertersDocument10 pages1997 TCASII I. Galton Spectral Shaping of Circuit Errors in Digital To Analog Converterskijiji userNo ratings yet

- 3upplement: International Telecommunication UnionDocument11 pages3upplement: International Telecommunication Unionmohit_bhavsar2aratiNo ratings yet

- OS Set 3Document2 pagesOS Set 3sriranganathan120No ratings yet

- Ecomms s07 MidtermDocument6 pagesEcomms s07 MidtermJos2No ratings yet

- QuestionsDocument5 pagesQuestionsgirishdsk2002No ratings yet

- LLL I Parallel Image Processing: Dr. Christos Bouganis o OugaDocument41 pagesLLL I Parallel Image Processing: Dr. Christos Bouganis o Ougasj030694No ratings yet

- Clat2-Set A QPDocument2 pagesClat2-Set A QPVikram ChaudharyNo ratings yet

- OFDM Write UpDocument6 pagesOFDM Write Up20112075No ratings yet

- ECL333 - Ktu QbankDocument7 pagesECL333 - Ktu QbankRoshith KNo ratings yet

- Multiplexer/Decoder Implementation of Logic Functions: 1. ObjectivesDocument5 pagesMultiplexer/Decoder Implementation of Logic Functions: 1. ObjectivesjhangmNo ratings yet

- Verilog LabDocument70 pagesVerilog Labhkes rcrNo ratings yet

- (System) Verilog Tutorial: Aleksandar MilenkovićDocument56 pages(System) Verilog Tutorial: Aleksandar MilenkovićAbhinav TallapallyNo ratings yet

- Dae31203 Lab3 Sem2sesi22-23Document14 pagesDae31203 Lab3 Sem2sesi22-23Arief Musta'in Bin Mohammad Ilyas SahuriNo ratings yet

- Cao Previous QNDocument9 pagesCao Previous QNanusha deviNo ratings yet

- ECT 206 Computer Organization and Microcontroller-SyllabusDocument8 pagesECT 206 Computer Organization and Microcontroller-SyllabusVilayil jestinNo ratings yet

- Debouncer v1 0Document5 pagesDebouncer v1 0Carlos MendozaNo ratings yet

- Cda3101 f13 Exam3 AnswerkeyDocument7 pagesCda3101 f13 Exam3 Answerkeydgsfg safdafNo ratings yet

- Electronics Individual DocumentDocument13 pagesElectronics Individual DocumentkennethNo ratings yet

- CLAT-2-Answer Key-SET-BDocument8 pagesCLAT-2-Answer Key-SET-BVikram ChaudharyNo ratings yet

- Compiler DesignDocument23 pagesCompiler Design21bcs003No ratings yet

- HDL Lab Manual: Anandanagar, Bangalore-24Document81 pagesHDL Lab Manual: Anandanagar, Bangalore-24Abinet ArbaNo ratings yet

- DSP Objective Unit 5Document6 pagesDSP Objective Unit 5arpit pNo ratings yet

- Ilovepdf MergedDocument160 pagesIlovepdf Mergedarpit pNo ratings yet

- E-Assignment: German-Malaysian InstituteDocument8 pagesE-Assignment: German-Malaysian InstituteYeshi UchihaNo ratings yet

- Software Design of Digital Receiver Using FPGADocument5 pagesSoftware Design of Digital Receiver Using FPGAAnonymous kw8Yrp0R5rNo ratings yet

- Designing Fir Filters With Actel Fpgas: Application NoteDocument12 pagesDesigning Fir Filters With Actel Fpgas: Application Notehiennhan1810No ratings yet

- 2019 Enel3ds - Exam - MainDocument15 pages2019 Enel3ds - Exam - MainNOMPUMELELO MTHETHWANo ratings yet

- Link Budget Analysis Guide: November 21, 2014Document19 pagesLink Budget Analysis Guide: November 21, 2014Анатолий МаловNo ratings yet

- Indian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Document4 pagesIndian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Utkarsh PatelNo ratings yet

- CLAT3 - Key - Set A (Updated)Document8 pagesCLAT3 - Key - Set A (Updated)Swarali UtekarNo ratings yet

- 2010 Embedded Computer System: CS/M.Tech/ME (IT) /SEM-2/PGEIT-201/2010Document3 pages2010 Embedded Computer System: CS/M.Tech/ME (IT) /SEM-2/PGEIT-201/2010Sanjib BhaktaNo ratings yet

- CAO IAT 2 QP 2019 Set 2Document2 pagesCAO IAT 2 QP 2019 Set 2formyphdNo ratings yet

- Test 2 - January 2021Document3 pagesTest 2 - January 2021muhammad iqbalNo ratings yet

- 1395 DSPProcessorsand ArchitecturesDocument6 pages1395 DSPProcessorsand ArchitecturesSudheer BabuNo ratings yet

- DSP Processor and ArchitectureDocument45 pagesDSP Processor and ArchitectureAlemayehu AsmareNo ratings yet

- Chapter1: Introduction To VerilogDocument15 pagesChapter1: Introduction To Verilogarunguptha_gsNo ratings yet

- 15A05502 Computer NetworksDocument1 page15A05502 Computer NetworksJaya SankarNo ratings yet

- B.Tech III Year I Semester (R15) Supplementary Examinations June 2018Document1 pageB.Tech III Year I Semester (R15) Supplementary Examinations June 2018PoornimaNo ratings yet

- B.Tech II Year II Semester (R15) Regular Examinations May/June 2017Document2 pagesB.Tech II Year II Semester (R15) Regular Examinations May/June 2017Abson MulengaNo ratings yet

- JOB AID-1 (W1 S1) : Digital Switching Systems (DSS) Job Aid Job AidDocument6 pagesJOB AID-1 (W1 S1) : Digital Switching Systems (DSS) Job Aid Job AidAlishaAliNo ratings yet

- SP Manual 2023-24Document98 pagesSP Manual 2023-24Manjunath ReddyNo ratings yet

- Digital Signal Processing Lab Record R20 (III ECE)Document78 pagesDigital Signal Processing Lab Record R20 (III ECE)goudNo ratings yet

- Final Exam Su2017Document9 pagesFinal Exam Su2017Juan SantosNo ratings yet

- Basic Digital Signal Processing: Butterworths Basic SeriesFrom EverandBasic Digital Signal Processing: Butterworths Basic SeriesRating: 5 out of 5 stars5/5 (1)

- Digital Differential Analysers: International Series of Monographs on Electronics and InstrumentationFrom EverandDigital Differential Analysers: International Series of Monographs on Electronics and InstrumentationNo ratings yet

- M Tech PublicationsDocument5 pagesM Tech PublicationsPanku RangareeNo ratings yet

- B.Tech III-I TTDocument4 pagesB.Tech III-I TTPanku RangareeNo ratings yet

- Sample Doc Mini ProjectDocument61 pagesSample Doc Mini ProjectPanku RangareeNo ratings yet

- 10 - Overfitting and UnderfittingDocument22 pages10 - Overfitting and UnderfittingPanku RangareeNo ratings yet

- IJRTI2209058 SharvaniDocument7 pagesIJRTI2209058 SharvaniPanku RangareeNo ratings yet

- Dspa Question BankDocument2 pagesDspa Question BankPanku RangareeNo ratings yet

- Machine Learning: Chapter 3. Decision Tree LearningDocument29 pagesMachine Learning: Chapter 3. Decision Tree LearningPanku RangareeNo ratings yet

- Time Table-2022-23Document4 pagesTime Table-2022-23Panku RangareeNo ratings yet

- System Verilog ImpDocument59 pagesSystem Verilog ImpPanku RangareeNo ratings yet

- CS276A Text Retrieval and MiningDocument48 pagesCS276A Text Retrieval and MiningPanku RangareeNo ratings yet

- Rashtrasant Tukadoji Maharaj Nagpur University: Direction No. 27 of 2021Document29 pagesRashtrasant Tukadoji Maharaj Nagpur University: Direction No. 27 of 2021Panku RangareeNo ratings yet

- Joics - 4964-1Document6 pagesJoics - 4964-1Panku RangareeNo ratings yet

- Vaagdevi College of Engineering: Autonomous B.Tech. Electronics & Communication Engineering Course StructureDocument5 pagesVaagdevi College of Engineering: Autonomous B.Tech. Electronics & Communication Engineering Course StructurePanku RangareeNo ratings yet

- DSP MCQ PaperDocument4 pagesDSP MCQ PaperPanku RangareeNo ratings yet

- 1Document12 pages1Panku RangareeNo ratings yet

- VLSI FDP Brochure - Phase3Document2 pagesVLSI FDP Brochure - Phase3Panku RangareeNo ratings yet

- IIC Activities During LockdownDocument4 pagesIIC Activities During LockdownPanku RangareeNo ratings yet

- Labview RMDocument92 pagesLabview RMPanku RangareeNo ratings yet

- CMOS MSD Question BankDocument1 pageCMOS MSD Question BankPanku RangareeNo ratings yet

- R18 B.Tech ECEDocument153 pagesR18 B.Tech ECEPanku RangareeNo ratings yet

- FplanDocument108 pagesFplanPanku RangareeNo ratings yet

- M.Tech-VLSISD - R18 - SyllabusDocument57 pagesM.Tech-VLSISD - R18 - SyllabusPanku RangareeNo ratings yet

- Iot, Industrial Iot, Industry 4.0Document1 pageIot, Industrial Iot, Industry 4.0Panku RangareeNo ratings yet

- FPGA PresentationDocument57 pagesFPGA PresentationPanku RangareeNo ratings yet

- Benefits of Area ConstraintsDocument18 pagesBenefits of Area ConstraintsPanku RangareeNo ratings yet

- Network Protocols and ServicesDocument4 pagesNetwork Protocols and ServicesMay Ann Agcang SabelloNo ratings yet

- Tutorials - DD-WRT WikiDocument3 pagesTutorials - DD-WRT WikiombidasarNo ratings yet

- PumpsDocument9 pagesPumpsmanoj1994kumar461No ratings yet

- Benefits of Creating A Gmail IDDocument4 pagesBenefits of Creating A Gmail IDSujit GulhaneNo ratings yet

- Date Codes Unmasked ESADocument30 pagesDate Codes Unmasked ESAlovrata4550No ratings yet

- Fluorolog-3 User Manual - Part Number 5500081014HDocument344 pagesFluorolog-3 User Manual - Part Number 5500081014HRichard BedellNo ratings yet

- Clock Tower - PSX - by RombieDocument57 pagesClock Tower - PSX - by RombieDanilo CassioNo ratings yet

- Debian Package ManagementDocument21 pagesDebian Package ManagementMilad NorouziNo ratings yet

- IEC Separable Connectors 36 KV, 630A: Front T-Body / Coupling (Rear) T-Body ConnectorDocument5 pagesIEC Separable Connectors 36 KV, 630A: Front T-Body / Coupling (Rear) T-Body ConnectorDiego AlvesNo ratings yet

- UI Developer (HTML&CSS) PDFDocument2 pagesUI Developer (HTML&CSS) PDFhamedjixNo ratings yet

- Sis 2.0Document5 pagesSis 2.0Valmaq Prestação Serviço Lda100% (1)

- 1008TX-POE+ Unmanaged SwitchDocument3 pages1008TX-POE+ Unmanaged SwitchPham HoaNo ratings yet

- How To Draw ER DiagramDocument22 pagesHow To Draw ER DiagramNidhi SinghNo ratings yet

- Lesson 3 - Divisibility Rules For 4, 8, 12 and 11Document12 pagesLesson 3 - Divisibility Rules For 4, 8, 12 and 11ranulfo mayolNo ratings yet

- Garmin Foretrex 401 ManualDocument12 pagesGarmin Foretrex 401 Manualt.w.c.No ratings yet

- FF0291 01 Free Mind Map Powerpoint Diagram 16x9Document6 pagesFF0291 01 Free Mind Map Powerpoint Diagram 16x9licantNo ratings yet

- Dokumen - Tips - Syrus Installation and Configuration Manual v1Document53 pagesDokumen - Tips - Syrus Installation and Configuration Manual v1registroNo ratings yet

- Customer Satisfaction Evaluation For Online Food SDocument14 pagesCustomer Satisfaction Evaluation For Online Food SLianne JuneNo ratings yet

- Shadab New ResumeDocument2 pagesShadab New Resumeshadab AliNo ratings yet

- Customizing For Hedge Management: Hedging ClassificationDocument13 pagesCustomizing For Hedge Management: Hedging ClassificationDillip Kumar mallickNo ratings yet

- Medal of Honor Heroes 2 Cheat Codes For Sony PSP PDFDocument4 pagesMedal of Honor Heroes 2 Cheat Codes For Sony PSP PDFMuhamad RosyidNo ratings yet

- Instant Download Econ Macro 5th Edition Mceachern Solutions Manual PDF Full ChapterDocument12 pagesInstant Download Econ Macro 5th Edition Mceachern Solutions Manual PDF Full Chaptercinderyburhcfc03100% (11)

- Accounting and Finance For ManagersDocument8 pagesAccounting and Finance For ManagerssrisaravNo ratings yet

- Products and Combos ListDocument11 pagesProducts and Combos Listamresh05062007No ratings yet

- Cyberbullying Detection System On TwitterDocument11 pagesCyberbullying Detection System On Twitterbibek singhNo ratings yet

- Lf77j01a00 10enDocument2 pagesLf77j01a00 10enAlvaro Quinteros CabreraNo ratings yet

- Experiment-3 DBMSDocument10 pagesExperiment-3 DBMSNANDHAKUMAR V MNo ratings yet

Dspa Mid 1 Paper

Dspa Mid 1 Paper

Uploaded by

Panku Rangaree0 ratings0% found this document useful (0 votes)

3 views6 pagesThis document contains a mid-term exam for a Digital Signal Processor and Architecture course. It has two parts: Part A contains 5 multiple choice questions worth 5 marks each and Part B contains 10 multiple choice questions worth 0.5 marks each. The exam assesses 5 course outcomes related to understanding digital signal processing systems and techniques, distinguishing features of general processors and DSP processors, and analyzing interfaces between devices and DSP processors.

Original Description:

Original Title

dspa mid 1 paper

Copyright

© © All Rights Reserved

Available Formats

DOC, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document contains a mid-term exam for a Digital Signal Processor and Architecture course. It has two parts: Part A contains 5 multiple choice questions worth 5 marks each and Part B contains 10 multiple choice questions worth 0.5 marks each. The exam assesses 5 course outcomes related to understanding digital signal processing systems and techniques, distinguishing features of general processors and DSP processors, and analyzing interfaces between devices and DSP processors.

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

Download as doc, pdf, or txt

0 ratings0% found this document useful (0 votes)

3 views6 pagesDspa Mid 1 Paper

Dspa Mid 1 Paper

Uploaded by

Panku RangareeThis document contains a mid-term exam for a Digital Signal Processor and Architecture course. It has two parts: Part A contains 5 multiple choice questions worth 5 marks each and Part B contains 10 multiple choice questions worth 0.5 marks each. The exam assesses 5 course outcomes related to understanding digital signal processing systems and techniques, distinguishing features of general processors and DSP processors, and analyzing interfaces between devices and DSP processors.

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

Download as doc, pdf, or txt

You are on page 1of 6

VAAGDEVI COLLGE OF ENGINEERING

AUTONOMOUS

P.O.BOLLIKUNTA , WARANGAL – 506 005

B. TECH VII SEMESTER I - MID EXAMINATIONS SEPTEMBER - 2023

Digital Signal Processor & Architecture (B20EC56)

Electronics and Communication Engineering

Time: 1 ½ Hours SET-I Max. Marks : 20

Date:12/09/2023 Session:AN

Note: This question Paper Contains two parts. Part A & B

Course Outcomes for Assessment in this Test:

Cos Course Outcome

Understand the DFT, FFT, DSP system and Explain the DSP computational building blocks and

1

addressing capabilities.

2 Distinguish between the architectural features of General purpose processors and DSP processors.

3 Discuss and understand the TMS320C54xx Processor.

4 Understand the Analog devices family of DSP devices .

5 Analyze the interface of various devices to DSP Processors

PART – A (3 X5 = 15 Marks)

Mapping

ANSWER ANY THREE OF FOLLOWING QUESTIONS Marks Bloom’s Taxonomy Levels

Cos

Draw and explain the block diagram of a Digital

1. 5 1 L1

Signal-Processing system.

Find 4 point DFT of a sequence x(n) =

2. 5 1 L3

{1,0,1,0}using radix 2 DITFFT algorithm.

Explain in brief about errors in A/D conversion

3. 5 2 L3

process.

Briefly discuss about the floating point and

4. 5 2 L2

block floating point formats

Explain the significance of Fast Transform

5. 5 3 L2

techniques. What are the advantages over DFT?

PART – B (10 X 1/2 = 5 Marks)

Marks

CHOOSE THE CORRECT ANSWER

In general, a digital system designer has better control of tolerances in a digital signal 1/2

processing system than an analog system designer who is designing an equivalent

1. analog system.

a) True

b) False

The selection of the sampling rate Fs=1/T, where T is the sampling interval, not only 1/2

determines the highest frequency (Fs/2) that is preserved in the analog signal but also

2. serves as a scale factor that influences the design specifications for digital filters.

a) True

b) False

What is the configuration of system for digital processing of an analog signal? 1/2

a) Analog signal|| Pre-filter -> D/A Converter -> Digital Processor -> A/D Converter -

> Post-filter

b) Analog signal|| Pre-filter -> A/D Converter -> Digital Processor -> D/A Converter

3.

-> Post-filter

c) Analog signal|| Post-filter -> D/A Converter -> Digital Processor -> A/D Converter

-> Pre-filter

d) None of the mentioned

4. 1/2

The signal given by the equation is known as __________

a) Energy signal

b) Power signal

c) Work done signal

d) None of the mentioned

The discrete time function defined as u(n)=n for n≥0;u(n)=0 for n<0 is an 1/2

_____________

a) Unit sample signal

5.

b) Unit step signal

c) Unit ramp signal

d) None of the mentioned

FILL IN THE BLANKS Marks

The quality of output signal from A/D converter is measured in terms of 1/2

6.

___________

7. Which bit coder is required to code a signal with 16 levels? 1/2

1/2

8. The process of converting discrete-time continuous valued signal into discrete-time

discrete valued (digital) signal is known as ____________

9. DTFT stands for _____________ 1/2

10. DF-I filters are ____________filters 1/2

Assessment Summary

Cos Remember Understand Apply Analyze Evaluate Create Total

1 5 -- 10 -- -- -- 15

2 -- 10 -- -- -- -- 10

3 -- -- -- -- -- -- --

4 -- -- -- -- -- -- --

5 -- -- -- -- -- -- --

VAAGDEVI COLLGE OF ENGINEERING

AUTONOMOUS

P.O.BOLLIKUNTA , WARANGAL – 506 005

B. TECH VII SEMESTER I - MID EXAMINATIONS SEPTEMBER - 2023

Digital Signal Processor & Architecture (B20EC56)

Electronics and Communication Engineering

Time: 1 ½ Hours SET-II Max. Marks : 20

Date:12/09/2023 Session:AN

Note: This question Paper Contains two parts. Part A & B

Course Outcomes for Assessment in this Test:

Cos Course Outcome

Understand the DFT, FFT, DSP system and Explain the DSP computational building blocks and

1

addressing capabilities.

2 Distinguish between the architectural features of General purpose processors and DSP processors.

3 Discuss and understand the TMS320C54xx Processor.

4 Understand the Analog devices family of DSP devices .

5 Analyze the interface of various devices to DSP Processors

PART – A (3 X5 = 15 Marks)

Mapping

ANSWER ANY THREE OF FOLLOWING QUESTIONS Marks Bloom’s Taxonomy Levels

Cos

Explain the block diagram of DSP? Give the

1. 5 1 L2

applications of DSP.

What are the different number formats that are

2. used to represent signals and coefficients in 5 1 L2

DSP systems? Explain any one of them.

Find DFT of a sequence x(n) = { 1,1,1,1} using

3. 5 2 L1

DITFFT

What is the difference between FIR and IIR

4. 5 2 L2

filters. Discuss DF-I structure

Explain the significance of Fast Transform

5. 5 3 L3

techniques. What are the advantages over DFT?

PART – B (10 X 1/2 = 5 Marks)

Marks

CHOOSE THE CORRECT ANSWER

If ‘F’ is the frequency of the analog signal, then what is the minimum sampling rate 1/2

required to avoid aliasing?

a) F

1.

b) 2F

c) 3F

d) 4F

What is the nyquist rate of the signal x(t)=3cos(50*pi*t)+10sin(300*pi*t)- 1/2

cos(100*pi*t)?

a) 50Hz

2.

b) 100Hz

c) 200Hz

d) 300Hz

The quality of output signal from A/D converter is measured in terms of

___________

a) Quantization error

3.

b) Quantization to signal noise ratio

c) Signal to quantization noise ratio

1/2

d) Conversion constant

4. What are the main characteristics of Anti aliasing filter? 1/2

a) Ensures that bandwidth of signal to be sampled is limited to frequency range

b) To limit the additive noise spectrum and other interference, which corrupts the

signal

c) All of the mentioned

d) None of the mentioned

Which bit coder is required to code a signal with 16 levels? 1/2

a) 8 bit

5. b) 4 bit

c) 2 bit

d) 1 bit

FILL IN THE BLANKS Marks

According to Nyquist, Sampling rate should be greater than equal to _______of maximum 1/2

6.

frequency component available in signal

7. DTFT stands for _____________ 1/2

8. FFT is _____________than DFT 1/2

9. IIR systems are _____________system 1/2

10. FIR systems are ______________system 1/2

Assessment Summary

Cos Remember Understand Apply Analyze Evaluate Create Total

1 5 5 -- -- -- -- 10

2 -- 10 5 -- -- -- 15

3 -- -- -- -- -- -- --

4 -- -- -- -- -- -- --

5 -- -- -- -- -- -- --

VAAGDEVI COLLGE OF ENGINEERING

AUTONOMOUS

P.O.BOLLIKUNTA , WARANGAL – 506 005

B. TECH VII SEMESTER I - MID EXAMINATIONS SEPTEMBER - 2023

Digital Signal Processor & Architecture (B20EC56)

Electronics and Communication Engineering

Time: 1 ½ Hours SET-III Max. Marks : 20

Date:12/09/2023 Session:AN

Note: This question Paper Contains two parts. Part A & B

Course Outcomes for Assessment in this Test:

Cos Course Outcome

Understand the DFT, FFT, DSP system and Explain the DSP computational building blocks and

1

addressing capabilities.

2 Distinguish between the architectural features of General purpose processors and DSP processors.

3 Discuss and understand the TMS320C54xx Processor.

4 Understand the Analog devices family of DSP devices .

5 Analyze the interface of various devices to DSP Processors

PART – A (3 X5 = 15 Marks)

Mapping

ANSWER ANY THREE OF FOLLOWING QUESTIONS Marks Bloom’s Taxonomy Levels

Cos

What are the Advantages Of Digital Signal

1. 5 1 L1

Processing Over Analog Signal Processing

2. Differentiate between FIR and IIR filters design 5 1 L2

Explain in brief about errors in A/D conversion

3. 5 2 L3

process.

Find 4 point DFT of a sequence x(n) =

4. 5 2 L2

{1,1,1,0}using radix 2 DITFFT algorithm.

Explain the significance of Fast Transform

5. 5 3 L3

techniques. What are the advantages over DFT?

PART – B (10 X 1/2 = 5 Marks)

Marks

CHOOSE THE CORRECT ANSWER

_________theorem is used for efficient communication in dsp system 1/2

1.

i)parseval ii)convolution iii)sampling iv) central limit

1. Which of the following should be done in order to convert a continuous-time signal

to a discrete-time signal?

a) Sampling

b) Differentiating 1/2

2. c) Integrating

d) None of the mentioned

2. The process of converting discrete-time continuous valued signal into discrete-time

discrete valued (digital) signal is known as ____________ 1/2

a) Sampling

3. b) Quantization

c) Coding

d) None of the mentioned

3. The difference between the unquantized x(n) and quantized xq(n) is known as 1/2

___________

a) Quantization coefficient

4.

b) Quantization ratio

c) Quantization factor

d) Quantization error

5. The relation between analog frequency ‘F’ and digital frequency ‘f’ is? 1/2

a) F=f*T(where T is sampling period)

5. b) f=F*T

c) No relation

d) None of the mentioned

FILL IN THE BLANKS Marks

6. The twiddle factor is given by______________ 1/2

7. DTFT stands for _____________ 1/2

8. FFT is _____________than DFT 1/2

According to Nyquist, Sampling rate should be greater than equal to _______of maximum 1/2

9.

frequency component available in signal

10. FFT is using ________________property for fast calculations. 1/2

Assessment Summary

Cos Remember Understand Apply Analyze Evaluate Create Total

1 5 -- 10 -- -- -- 15

2 -- 10 -- -- -- -- 10

3 -- -- -- -- -- -- --

4 -- -- -- -- -- -- --

5 -- -- -- -- -- -- --

You might also like

- Saueressig T. Business As Unusual With SAP... 2022Document569 pagesSaueressig T. Business As Unusual With SAP... 2022Srinivasan MeshramNo ratings yet

- Flysmart+ For Ipad Applications V5.0: Installation Guide - RevbDocument22 pagesFlysmart+ For Ipad Applications V5.0: Installation Guide - RevbrameauNo ratings yet

- Clapswitchpbl 2Document22 pagesClapswitchpbl 2Panku RangareeNo ratings yet

- Lab 2 - Working With Data StorageDocument15 pagesLab 2 - Working With Data StorageMangesh AbnaveNo ratings yet

- Clat2 Set-B Answer KeyDocument7 pagesClat2 Set-B Answer KeyVikram ChaudharyNo ratings yet

- CT2 QP SetBDocument5 pagesCT2 QP SetBsansheela2014No ratings yet

- MEL G642-Compre Solution - 2 2016-17Document9 pagesMEL G642-Compre Solution - 2 2016-17Gaurav PatilNo ratings yet

- 15A05502 Computer NetworksDocument2 pages15A05502 Computer NetworksKiran Kumar BoddepalliNo ratings yet

- Third Internal Assessment Question PaperDocument1 pageThird Internal Assessment Question Papersyed1188No ratings yet

- Iiiy VS U3 Ee8591 DSP 2020 2021Document1 pageIiiy VS U3 Ee8591 DSP 2020 2021syed1188No ratings yet

- Dspa Question BankDocument2 pagesDspa Question BankPanku RangareeNo ratings yet

- Thapar Institute of Engineering & Technology, Patiala: End Semester Examination (May 2019)Document4 pagesThapar Institute of Engineering & Technology, Patiala: End Semester Examination (May 2019)Forza HorizonNo ratings yet

- Ct3 Set B Adc Answer KeyDocument17 pagesCt3 Set B Adc Answer Keypa2195No ratings yet

- Digital Signal Processing LabDocument6 pagesDigital Signal Processing LabTHABO KEITH DUBENo ratings yet

- MP Mid TermDocument4 pagesMP Mid TermHassan AamerNo ratings yet

- DSP Question Paper April 2012Document2 pagesDSP Question Paper April 2012Famida Begam100% (1)

- DSP Lab Manual - FinalDocument72 pagesDSP Lab Manual - FinalSwetNo ratings yet

- Embedded Micro Controller Test SolutionDocument9 pagesEmbedded Micro Controller Test SolutionalikaastridNo ratings yet

- EETP DSS W1 Job Aid PDFDocument6 pagesEETP DSS W1 Job Aid PDFAnkita BajpaiNo ratings yet

- 1997 TCASII I. Galton Spectral Shaping of Circuit Errors in Digital To Analog ConvertersDocument10 pages1997 TCASII I. Galton Spectral Shaping of Circuit Errors in Digital To Analog Converterskijiji userNo ratings yet

- 3upplement: International Telecommunication UnionDocument11 pages3upplement: International Telecommunication Unionmohit_bhavsar2aratiNo ratings yet

- OS Set 3Document2 pagesOS Set 3sriranganathan120No ratings yet

- Ecomms s07 MidtermDocument6 pagesEcomms s07 MidtermJos2No ratings yet

- QuestionsDocument5 pagesQuestionsgirishdsk2002No ratings yet

- LLL I Parallel Image Processing: Dr. Christos Bouganis o OugaDocument41 pagesLLL I Parallel Image Processing: Dr. Christos Bouganis o Ougasj030694No ratings yet

- Clat2-Set A QPDocument2 pagesClat2-Set A QPVikram ChaudharyNo ratings yet

- OFDM Write UpDocument6 pagesOFDM Write Up20112075No ratings yet

- ECL333 - Ktu QbankDocument7 pagesECL333 - Ktu QbankRoshith KNo ratings yet

- Multiplexer/Decoder Implementation of Logic Functions: 1. ObjectivesDocument5 pagesMultiplexer/Decoder Implementation of Logic Functions: 1. ObjectivesjhangmNo ratings yet

- Verilog LabDocument70 pagesVerilog Labhkes rcrNo ratings yet

- (System) Verilog Tutorial: Aleksandar MilenkovićDocument56 pages(System) Verilog Tutorial: Aleksandar MilenkovićAbhinav TallapallyNo ratings yet

- Dae31203 Lab3 Sem2sesi22-23Document14 pagesDae31203 Lab3 Sem2sesi22-23Arief Musta'in Bin Mohammad Ilyas SahuriNo ratings yet

- Cao Previous QNDocument9 pagesCao Previous QNanusha deviNo ratings yet

- ECT 206 Computer Organization and Microcontroller-SyllabusDocument8 pagesECT 206 Computer Organization and Microcontroller-SyllabusVilayil jestinNo ratings yet

- Debouncer v1 0Document5 pagesDebouncer v1 0Carlos MendozaNo ratings yet

- Cda3101 f13 Exam3 AnswerkeyDocument7 pagesCda3101 f13 Exam3 Answerkeydgsfg safdafNo ratings yet

- Electronics Individual DocumentDocument13 pagesElectronics Individual DocumentkennethNo ratings yet

- CLAT-2-Answer Key-SET-BDocument8 pagesCLAT-2-Answer Key-SET-BVikram ChaudharyNo ratings yet

- Compiler DesignDocument23 pagesCompiler Design21bcs003No ratings yet

- HDL Lab Manual: Anandanagar, Bangalore-24Document81 pagesHDL Lab Manual: Anandanagar, Bangalore-24Abinet ArbaNo ratings yet

- DSP Objective Unit 5Document6 pagesDSP Objective Unit 5arpit pNo ratings yet

- Ilovepdf MergedDocument160 pagesIlovepdf Mergedarpit pNo ratings yet

- E-Assignment: German-Malaysian InstituteDocument8 pagesE-Assignment: German-Malaysian InstituteYeshi UchihaNo ratings yet

- Software Design of Digital Receiver Using FPGADocument5 pagesSoftware Design of Digital Receiver Using FPGAAnonymous kw8Yrp0R5rNo ratings yet

- Designing Fir Filters With Actel Fpgas: Application NoteDocument12 pagesDesigning Fir Filters With Actel Fpgas: Application Notehiennhan1810No ratings yet

- 2019 Enel3ds - Exam - MainDocument15 pages2019 Enel3ds - Exam - MainNOMPUMELELO MTHETHWANo ratings yet

- Link Budget Analysis Guide: November 21, 2014Document19 pagesLink Budget Analysis Guide: November 21, 2014Анатолий МаловNo ratings yet

- Indian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Document4 pagesIndian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Utkarsh PatelNo ratings yet

- CLAT3 - Key - Set A (Updated)Document8 pagesCLAT3 - Key - Set A (Updated)Swarali UtekarNo ratings yet

- 2010 Embedded Computer System: CS/M.Tech/ME (IT) /SEM-2/PGEIT-201/2010Document3 pages2010 Embedded Computer System: CS/M.Tech/ME (IT) /SEM-2/PGEIT-201/2010Sanjib BhaktaNo ratings yet

- CAO IAT 2 QP 2019 Set 2Document2 pagesCAO IAT 2 QP 2019 Set 2formyphdNo ratings yet

- Test 2 - January 2021Document3 pagesTest 2 - January 2021muhammad iqbalNo ratings yet

- 1395 DSPProcessorsand ArchitecturesDocument6 pages1395 DSPProcessorsand ArchitecturesSudheer BabuNo ratings yet

- DSP Processor and ArchitectureDocument45 pagesDSP Processor and ArchitectureAlemayehu AsmareNo ratings yet

- Chapter1: Introduction To VerilogDocument15 pagesChapter1: Introduction To Verilogarunguptha_gsNo ratings yet

- 15A05502 Computer NetworksDocument1 page15A05502 Computer NetworksJaya SankarNo ratings yet

- B.Tech III Year I Semester (R15) Supplementary Examinations June 2018Document1 pageB.Tech III Year I Semester (R15) Supplementary Examinations June 2018PoornimaNo ratings yet

- B.Tech II Year II Semester (R15) Regular Examinations May/June 2017Document2 pagesB.Tech II Year II Semester (R15) Regular Examinations May/June 2017Abson MulengaNo ratings yet

- JOB AID-1 (W1 S1) : Digital Switching Systems (DSS) Job Aid Job AidDocument6 pagesJOB AID-1 (W1 S1) : Digital Switching Systems (DSS) Job Aid Job AidAlishaAliNo ratings yet

- SP Manual 2023-24Document98 pagesSP Manual 2023-24Manjunath ReddyNo ratings yet

- Digital Signal Processing Lab Record R20 (III ECE)Document78 pagesDigital Signal Processing Lab Record R20 (III ECE)goudNo ratings yet

- Final Exam Su2017Document9 pagesFinal Exam Su2017Juan SantosNo ratings yet

- Basic Digital Signal Processing: Butterworths Basic SeriesFrom EverandBasic Digital Signal Processing: Butterworths Basic SeriesRating: 5 out of 5 stars5/5 (1)

- Digital Differential Analysers: International Series of Monographs on Electronics and InstrumentationFrom EverandDigital Differential Analysers: International Series of Monographs on Electronics and InstrumentationNo ratings yet

- M Tech PublicationsDocument5 pagesM Tech PublicationsPanku RangareeNo ratings yet

- B.Tech III-I TTDocument4 pagesB.Tech III-I TTPanku RangareeNo ratings yet

- Sample Doc Mini ProjectDocument61 pagesSample Doc Mini ProjectPanku RangareeNo ratings yet

- 10 - Overfitting and UnderfittingDocument22 pages10 - Overfitting and UnderfittingPanku RangareeNo ratings yet

- IJRTI2209058 SharvaniDocument7 pagesIJRTI2209058 SharvaniPanku RangareeNo ratings yet

- Dspa Question BankDocument2 pagesDspa Question BankPanku RangareeNo ratings yet

- Machine Learning: Chapter 3. Decision Tree LearningDocument29 pagesMachine Learning: Chapter 3. Decision Tree LearningPanku RangareeNo ratings yet

- Time Table-2022-23Document4 pagesTime Table-2022-23Panku RangareeNo ratings yet

- System Verilog ImpDocument59 pagesSystem Verilog ImpPanku RangareeNo ratings yet

- CS276A Text Retrieval and MiningDocument48 pagesCS276A Text Retrieval and MiningPanku RangareeNo ratings yet

- Rashtrasant Tukadoji Maharaj Nagpur University: Direction No. 27 of 2021Document29 pagesRashtrasant Tukadoji Maharaj Nagpur University: Direction No. 27 of 2021Panku RangareeNo ratings yet

- Joics - 4964-1Document6 pagesJoics - 4964-1Panku RangareeNo ratings yet

- Vaagdevi College of Engineering: Autonomous B.Tech. Electronics & Communication Engineering Course StructureDocument5 pagesVaagdevi College of Engineering: Autonomous B.Tech. Electronics & Communication Engineering Course StructurePanku RangareeNo ratings yet

- DSP MCQ PaperDocument4 pagesDSP MCQ PaperPanku RangareeNo ratings yet

- 1Document12 pages1Panku RangareeNo ratings yet

- VLSI FDP Brochure - Phase3Document2 pagesVLSI FDP Brochure - Phase3Panku RangareeNo ratings yet

- IIC Activities During LockdownDocument4 pagesIIC Activities During LockdownPanku RangareeNo ratings yet

- Labview RMDocument92 pagesLabview RMPanku RangareeNo ratings yet

- CMOS MSD Question BankDocument1 pageCMOS MSD Question BankPanku RangareeNo ratings yet

- R18 B.Tech ECEDocument153 pagesR18 B.Tech ECEPanku RangareeNo ratings yet

- FplanDocument108 pagesFplanPanku RangareeNo ratings yet

- M.Tech-VLSISD - R18 - SyllabusDocument57 pagesM.Tech-VLSISD - R18 - SyllabusPanku RangareeNo ratings yet

- Iot, Industrial Iot, Industry 4.0Document1 pageIot, Industrial Iot, Industry 4.0Panku RangareeNo ratings yet

- FPGA PresentationDocument57 pagesFPGA PresentationPanku RangareeNo ratings yet

- Benefits of Area ConstraintsDocument18 pagesBenefits of Area ConstraintsPanku RangareeNo ratings yet

- Network Protocols and ServicesDocument4 pagesNetwork Protocols and ServicesMay Ann Agcang SabelloNo ratings yet

- Tutorials - DD-WRT WikiDocument3 pagesTutorials - DD-WRT WikiombidasarNo ratings yet

- PumpsDocument9 pagesPumpsmanoj1994kumar461No ratings yet

- Benefits of Creating A Gmail IDDocument4 pagesBenefits of Creating A Gmail IDSujit GulhaneNo ratings yet

- Date Codes Unmasked ESADocument30 pagesDate Codes Unmasked ESAlovrata4550No ratings yet

- Fluorolog-3 User Manual - Part Number 5500081014HDocument344 pagesFluorolog-3 User Manual - Part Number 5500081014HRichard BedellNo ratings yet

- Clock Tower - PSX - by RombieDocument57 pagesClock Tower - PSX - by RombieDanilo CassioNo ratings yet

- Debian Package ManagementDocument21 pagesDebian Package ManagementMilad NorouziNo ratings yet

- IEC Separable Connectors 36 KV, 630A: Front T-Body / Coupling (Rear) T-Body ConnectorDocument5 pagesIEC Separable Connectors 36 KV, 630A: Front T-Body / Coupling (Rear) T-Body ConnectorDiego AlvesNo ratings yet

- UI Developer (HTML&CSS) PDFDocument2 pagesUI Developer (HTML&CSS) PDFhamedjixNo ratings yet

- Sis 2.0Document5 pagesSis 2.0Valmaq Prestação Serviço Lda100% (1)

- 1008TX-POE+ Unmanaged SwitchDocument3 pages1008TX-POE+ Unmanaged SwitchPham HoaNo ratings yet

- How To Draw ER DiagramDocument22 pagesHow To Draw ER DiagramNidhi SinghNo ratings yet

- Lesson 3 - Divisibility Rules For 4, 8, 12 and 11Document12 pagesLesson 3 - Divisibility Rules For 4, 8, 12 and 11ranulfo mayolNo ratings yet

- Garmin Foretrex 401 ManualDocument12 pagesGarmin Foretrex 401 Manualt.w.c.No ratings yet

- FF0291 01 Free Mind Map Powerpoint Diagram 16x9Document6 pagesFF0291 01 Free Mind Map Powerpoint Diagram 16x9licantNo ratings yet

- Dokumen - Tips - Syrus Installation and Configuration Manual v1Document53 pagesDokumen - Tips - Syrus Installation and Configuration Manual v1registroNo ratings yet

- Customer Satisfaction Evaluation For Online Food SDocument14 pagesCustomer Satisfaction Evaluation For Online Food SLianne JuneNo ratings yet

- Shadab New ResumeDocument2 pagesShadab New Resumeshadab AliNo ratings yet

- Customizing For Hedge Management: Hedging ClassificationDocument13 pagesCustomizing For Hedge Management: Hedging ClassificationDillip Kumar mallickNo ratings yet

- Medal of Honor Heroes 2 Cheat Codes For Sony PSP PDFDocument4 pagesMedal of Honor Heroes 2 Cheat Codes For Sony PSP PDFMuhamad RosyidNo ratings yet

- Instant Download Econ Macro 5th Edition Mceachern Solutions Manual PDF Full ChapterDocument12 pagesInstant Download Econ Macro 5th Edition Mceachern Solutions Manual PDF Full Chaptercinderyburhcfc03100% (11)

- Accounting and Finance For ManagersDocument8 pagesAccounting and Finance For ManagerssrisaravNo ratings yet

- Products and Combos ListDocument11 pagesProducts and Combos Listamresh05062007No ratings yet

- Cyberbullying Detection System On TwitterDocument11 pagesCyberbullying Detection System On Twitterbibek singhNo ratings yet

- Lf77j01a00 10enDocument2 pagesLf77j01a00 10enAlvaro Quinteros CabreraNo ratings yet

- Experiment-3 DBMSDocument10 pagesExperiment-3 DBMSNANDHAKUMAR V MNo ratings yet