Professional Documents

Culture Documents

ncp81152 D

ncp81152 D

Uploaded by

Nikhil khadeOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ncp81152 D

ncp81152 D

Uploaded by

Nikhil khadeCopyright:

Available Formats

NCP81152

Synchronous Buck Dual

MOSFET Driver

The NCP81152 is a high−performance dual MOSFET gate driver

optimized to drive the gates of both high−side and low−side power

MOSFETs in a synchronous buck converter. Two drivers are

co−packaged into a 2.5 mm x 3.5 mm QFN16 package that greatly www.onsemi.com

reduces the footprint compared to two discrete drivers. Adaptive

anti−cross−conduction circuitry and power saving operation provides

a low−switching−loss and high−efficiency solution for notebook

systems. The under−voltage lockout function guarantees the outputs 1

are low when the supply voltage is low. QFN16

MN SUFFIX

Features CASE 485AW

• Adaptive Anti−Cross−Conduction Circuit

• Integrated Bootstrap Diode

MARKING DIAGRAM

• Zero Cross Detection

• Floating Top Driver Accommodates Boost Voltages up to 35 V 81152

ALYWG

• Output Disable Control Turns Off Both MOSFETs G

• Under−voltage Lockout

81152 = Specific Device Code

• Power Saving Operation Under Light Load Conditions A = Assembly Location

• Thermally Enhanced Package L = Wafer Lot

Y = Year

• These are Pb−Free Devices W = Work Week

G = Pb−Free Package

Typical Applications

(Note: Microdot may be in either location)

• Vcore Power for Notebook Systems

• Power Systems for DDR and Graphics

PIN CONNECTIONS

DRVH1

BST1

1 16

PWM1 SW1

EN1 GND1

FLAG

VCC1 DRVL1

BST2 DRVH2

PWM2 SW2

EN2 GND2

VCC2

DRVL2

(Top View)

ORDERING INFORMATION

Device Package Shipping†

NCP81152MNTWG QFN16 3000 / Tape &

(Pb−Free) Reel

†For information on tape and reel specifications,

including part orientation and tape sizes, please

refer to our Tape and Reel Packaging Specifications

Brochure, BRD8011/D.

© Semiconductor Components Industries, LLC, 2015 1 Publication Order Number:

January, 2015 − Rev. 2 NCP81152/D

Downloaded from Arrow.com.

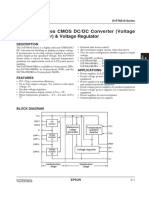

NCP81152

VCC1 BST1

DRVH1

PWM1 Logic

SW1

Anti−Cross

Conduction

VCC1

DRVL1

EN1 Zero

Cross

Detection

UVLO

VCC2 BST2

DRVH2

PWM2 Logic

SW2

Anti−Cross

Conduction

VCC2

DRVL2

EN2 Zero

Cross

Detection

UVLO

Figure 1. Block Diagram

www.onsemi.com

2

Downloaded from Arrow.com.

NCP81152

Table 1. PIN DESCRIPTIONS

Pin No. Symbol Description

1, 5 BST1, BST2 Floating bootstrap supply pin for high−side gate driver. Connect the bootstrap capacitor between this pin

and the SW pin.

2, 6 PWM1, PWM2 Control input. The PWM signal has three states:

PWM = High enables the high−side FET;

PWM = Mid enables zero cross detection;

PWM = Low enables the low−side FET.

3, 7 EN1, EN2 Logic input. Three−state logic input:

EN = High enables the driver;

EN = Mid goes into diode braking mode (both high−side and low−side gate drive signals are low);

EN = Low disables the driver.

4, 8 VCC1, VCC2 Power supply input. Connect a bypass capacitor (0.1 mF) from this pin to ground.

9, 13 DRVL1, DRVL2 Low−side gate drive output. Connect to the gate of the low−side MOSFET.

10, 14 GND1, GND2 Bias and reference ground. All signals are referenced to this node.

11, 15 SW1, SW2 Switch node. Connect this pin to the source of the high−side MOSFET and drain of the low−side MOSFET.

12, 16 DRVH1, DRVH2 High−side gate drive output. Connect to the gate of the high−side MOSFET.

17 FLAG Thermal flag. There is no electrical connection to the IC. Connect to ground plane.

Table 2. ABSOLUTE MAXIMUM RATINGS

Pin Symbol Pin Name VMAX VMIN

VCC1, VCC2 Main Supply Voltage Input 6.5 V −0.3 V

BST1, BST2 Bootstrap Supply Voltage 35 V wrt/ GND −0.3 V wrt/SW

40 V ≤ 50 ns wrt/ GND

6.5 V wrt/ SW

SW1, SW2 Switching Node 35 V −5 V

(Bootstrap Supply Return) 40 V ≤ 50 ns −10 V (200 ns)

DRVH1, DRVH2 High Side Driver Output BST+0.3 V −0.3 V wrt/SW

−2 V (<200 ns) wrt/SW

DRVL1, DRVL2 Low Side Driver Output VCC+0.3 V −0.3 V DC

−5 V (<200 ns)

PWM1, PWM2 DRVH and DRVL Control Input 6.5 V −0.3 V

EN1, EN2 Enable Pin 6.5 V −0.3 V

GND1, GND2 Ground 0V 0V

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality

should not be assumed, damage may occur and reliability may be affected.

*All signals referenced to AGND unless noted otherwise.

Table 3. THERMAL INFORMATION

Parameter Symbol Value Unit

Thermal Characteristic (Note 1) RqJA 29 °C/W

Operating Junction Temperature Range TJ −40 to +150 °C

Operating Ambient Temperature Range TA −40 to +100 °C

Maximum Storage Temperature Range TSTG −55 to +150 °C

Moisture Sensitivity Level − QFN Package MSL 1

*The maximum package power dissipation must be observed.

1. 1 in2 Cu., 1 oz. thickness.

www.onsemi.com

3

Downloaded from Arrow.com.

NCP81152

Table 4. NCP81152 DRIVER ELECTRICAL CHARACTERISTICS

Unless otherwise stated: −40°C < TA < +100°C; VCC = 4.5 V ~ 5.5 V; BST−SW = 4.5 V ~ 5.5 V; BST = 4.5 V ~ 30 V; SWN = 0 V ~ 21 V.

Parameter Test Conditions Min Typ Max Units

SUPPLY VOLTAGE

VCC1, VCC2 Operation Voltage 4.5 5.5 V

UNDERVOLTAGE LOCKOUT (VCC1, VCC2)

Start Threshold 3.8 4.35 4.5 V

Hysteresis 150 200 250 mV

SUPPLY CURRENT

Normal Mode ICC1 + ICC2 + IBST1 + IBST2 9.4 mA

EN1, EN2 = 5 V,

PWM1 & PWM2 oscillating at 100 kHz,

CLOAD = 3 nF

Shutdown Mode ICC1 + ICC2 + IBST1 + IBST2 22 40 mA

EN1, EN2 = Gnd

Standby Current 1 ICC1 + ICC2 + IBST1 + IBST2 1.8 mA

EN1, EN2 = Logic High,

PWM1, PWM2 = Logic Low,

No loading on DRVH1/2 & DRVL1/2

Standby Current 2 ICC1 + ICC2 + IBST1 + IBST2 2.2 mA

EN1, EN2 = Logic High,

PWM1, PWM2 = Logic High,

No loading on DRVH1/2 & DRVL1/2

BOOTSTRAP DIODE

Forward Voltage VCC = 5 V, forward bias current = 2 mA 0.1 0.4 0.6 V

PWM INPUT

Input High 3.4 V

Mid−State 1.3 2.45 V

Input Low 0.7 V

ZCD blanking timer 350 ns

HIGH SIDE DRIVER (DRVH1, DRVH2)

Output Resistance, Sourcing Current BST − SW = 5 V 0.9 1.7 W

Output Resistance, Sinking Current BST − SW = 5 V 0.7 1.7 W

Rise Time, trDRVH VCC = 5 V, 3 nF load, BST − SW = 5 V 16 25 ns

Fall Time, tfDRVH VCC = 5 V, 3 nF load, BST − SW = 5 V 11 18 ns

Turn−Off Propagation Delay, tpdlDRVH CLOAD = 3 nF 10 30 ns

Turn−On Propagation Delay, tpdhDRVH CLOAD = 3 nF 10 40 ns

SW Pull−Down Resistance SW to PGND 45 kW

DRVH Pull−Down Resistance DRVH to SW, VBST−VSW = 0 V 45 kW

LOW SIDE DRIVER (DRVL1, DRVL2)

Output Resistance, Sourcing Current 0.9 1.7 W

Output Resistance, Sinking Current 0.4 0.8 W

Rise Time, trDRVH CLOAD = 3 nF 16 25 ns

Fall Time, tfDRVH CLOAD = 3 nF 11 15 ns

Turn−Off Propagation Delay, tpdlDRVH CLOAD = 3 nF 10 30 ns

Turn−On Propagation Delay, tpdhDRVH CLOAD = 3 nF 5 25 ns

DRVL Pull−Down Resistance DRVL to PGND, VCC = PGND 45 kW

www.onsemi.com

4

Downloaded from Arrow.com.

NCP81152

Table 4. NCP81152 DRIVER ELECTRICAL CHARACTERISTICS

Unless otherwise stated: −40°C < TA < +100°C; VCC = 4.5 V ~ 5.5 V; BST−SW = 4.5 V ~ 5.5 V; BST = 4.5 V ~ 30 V; SWN = 0 V ~ 21 V.

Parameter Test Conditions Min Typ Max Units

ENABLE INPUT (EN1, EN2)

Input High 3.3 V

Mid−State 1.35 1.8 V

Input Low 0.6 V

Normal Mode Bias Current −1 1 mA

Propagation Delay Time 20 40 ns

SWITCH NODE (SW1, SW2)

SW Leakage Current 20 mA

Zero Cross Detection Threshold Voltage SW to −20 mV, ramp slowly until BG goes off −6 mV

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

Table 5. PWM/EN TRUTH TABLE

PWM INPUT ZCD DRVL DRVH

PWM High ZCD Reset Low High

PWM Mid Positive current through the inductor High Low

PWM Mid Zero or negative current through the inductor Low Low

PWM Low ZCD Reset High Low

Enable at Mid X Low Low

PWM

tpdlDRVL tfDRVL

DRVL

90% 90%

1V 10% 10%

tpdlDRVH tfDRVH trDRVL

tpdhDRVH trDRVH

90% 90%

10% 1V 10%

DRVH−

SW

tpdhDRVL

Figure 2. Timing Diagram

www.onsemi.com

5

Downloaded from Arrow.com.

NCP81152

PWM

DRVH−SW

DRVL

IL

Figure 3. Logic Diagram

www.onsemi.com

6

Downloaded from Arrow.com.

NCP81152

Application Information

The NCP81152 is a high−performance dual MOSFET voltage supply for the low−side driver is internally

gate driver optimized to drive the gates of both high−side connected to the VCC and GND pins.

and low−side power MOSFETs in a synchronous buck

converter. Two drivers are co−packaged into a 2.5 mm x 3.5 High−Side Driver

mm QFN16 package that greatly reduces the footprint The high−side driver is designed to drive a floating

compared to two discrete drivers. low−RDS(on) N−channel MOSFET. The gate voltage for the

high−side driver is developed by a bootstrap circuit

Undervoltage Lockout referenced to the SW pin.

DRVH and DRVL are low until VCC reaches the VCC The bootstrap circuit is comprised of the integrated diode

UVLO threshold, typically 4.35 V. When VCC reaches this and an external bootstrap capacitor. When the NCP81152 is

threshold, the PWM signal controls the states of DRVH and starting up, the SW pin is held at ground, allowing the

DRVL. There is a 200 mV hysteresis on VCC UVLO. There bootstrap capacitor to charge up to VCC through the

are pull−down resistors on DRVH, DRVL and SW that bootstrap diode. When the PWM input is driven high, the

prevent the gates of the MOSFETs from accumulating high−side driver turns on the high−side MOSFET using the

enough charge to turn on when the driver is powered off. stored charge of the bootstrap capacitor. As the high−side

MOSFET turns on, the SW pin rises. When the high−side

Three−State EN Signal MOSFET fully turns on, SW settles to VIN and BST settles

Placing EN into a logic−high or logic−low turns the driver to VIN + VCC (excluding parasitic ringing).

on and off, respectively, as long as VCC is greater than the

UVLO threshold. The EN threshold limits are specified in Bootstrap Circuit

the electrical characteristics table in this datasheet. Setting The bootstrap circuit relies on an external charge storage

the EN voltage to a mid−state level pulls both DRVH and capacitor (CBST) and an integrated diode to provide current

DRVL low. to the high−side driver. A multi−layer ceramic capacitor

Setting EN to the mid−state level can be used for body (MLCC) with a value greater than 100 nF should be used for

diode braking to quickly reduce the inductor current. By CBST.

turning the LS FET off and having the current conduct

through the LS FET body diode, the voltage at the switch Thermal Considerations

node is at a greater negative potential compared to having As power in the NCP81152 increases, it may be necessary

the LS FET on. This greater negative potential on switch to provide thermal relief. The maximum power dissipation

node allows there to be a greater voltage across the output supported by the device depends upon board design and

inductor, since the opposite terminal of the inductor is layout. Mounting pad configuration on the PCB, the board

connected to the converter output voltage. The larger material, and the ambient temperature affect the rate of

voltage across the inductor causes there to be a greater junction temperature rise for the part. When the NCP81152

inductor current slew rate, allowing the current to decrease has good thermal conductivity through the PCB, the

at a faster rate. junction temperature is relatively low with high power

applications. The maximum dissipation the NCP81152 can

PWM Input and Zero Cross Detect (ZCD) handle is given by:

The PWM input, along with EN and ZCD, controls the

state of DRVH and DRVL. When PWM is set high, DRVH

ƪTJ(MAX) * TAƫ

P D(MAX) + (eq. 1)

is set high after the adaptive non−overlap delay. When PWM R qJA

is set low, DRVL is set high after the adaptive non−overlap Since TJ is not recommended to exceed 150°C, the

delay. NCP81152, soldered on to a 645 mm2 copper area, using

When PWM is set to the mid−state, DRVH is set low, and 1 oz. copper and FR4, can dissipate up to 4.3 W when the

after the adaptive non−overlap delay, DRVL is set high. ambient temperature (TA) is 25°C. The power dissipated by

DRVL remains high until the ZCD blanking time expires. the NCP81152 can be calculated from the following

When the timer expires, the voltage on the SW pin is equation:

monitored for zero cross detection (whether it has crossed

(eq. 2)

the ZCD threshold voltage). After zero cross is detected,

DRVL is set low. P D [ VCC @ ƪ(n HS @ Qg HS ) n LS @ Qg LS) @ f ) I standbyƫ

Low−Side Driver Where nHS and nLS are the number of high−side and

The low−side driver is designed to drive a low−side FETs, respectively, QgHS and QgLS are the gate

ground−referenced low−RDS(on) N−channel MOSFET. The charges of the high−side and low−side FETs, respectively

and f is the switching frequency of the converter.

www.onsemi.com

7

Downloaded from Arrow.com.

MECHANICAL CASE OUTLINE

PACKAGE DIMENSIONS

QFN16, 2.5x3.5, 0.5P

CASE 485AW−01

1 ISSUE O

DATE 11 DEC 2008

SCALE 2:1

NOTES:

D A 1. DIMENSIONING AND TOLERANCING PER

B L L ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

ÉÉÉ

3. DIMENSIONS b APPLIES TO PLATED

PIN ONE TERMINAL AND IS MEASURED BETWEEN

L1

ÉÉÉ

REFERENCE 0.15 AND 0.30 MM FROM TERMINAL.

4. COPLANARITY APPLIES TO THE EXPOSED

ÉÉÉ

DETAIL A PAD AS WELL AS THE TERMINALS.

ALTERNATE TERMINAL MILLIMETERS

CONSTRUCTIONS

E DIM MIN MAX

A 0.80 1.00

ÇÇÇ

A1 0.00 0.05

A3 0.20 REF

ÇÇÇ

ÉÉÉ

EXPOSED Cu MOLD CMPD b 0.20 0.30

2X 0.15 C D 2.50 BSC

ÉÉÉ

D2 0.85 1.15

E 3.50 BSC

2X 0.15 C E2 1.85 2.15

TOP VIEW DETAIL B e 0.50 BSC

ALTERNATE K 0.20 ---

A CONSTRUCTIONS L 0.35 0.45

DETAIL B

0.10 C (A3) L1 --- 0.15

A1 GENERIC MARKING

16X 0.08 C

DIAGRAM*

NOTE 4

SEATING XXXX

SIDE VIEW C PLANE ALYWG

G

0.15 C A B

XXXX = Specific Device Code

D2 A = Assembly Location

16X L K L = Wafer Lot

8

Y = Year

10 0.15 C A B

DETAIL A

W = Work Week

G = Pb−Free Package

E2 (Note: Microdot may be in either location)

*This information is generic. Please refer to

16X b device data sheet for actual part marking.

2 0.10 C A B Pb−Free indicator, “G” or microdot “ G”,

15 may or may not be present.

1

0.05 C NOTE 3

e SOLDERING FOOTPRINT*

e/2

3.80

BOTTOM VIEW 2.10

0.50

PITCH

2.80 1.10

1

PACKAGE

16X 16X OUTLINE

0.60 0.30

DIMENSIONS: MILLIMETERS

*For additional information on our Pb−Free strategy and soldering

details, please download the ON Semiconductor Soldering and

Mounting Techniques Reference Manual, SOLDERRM/D.

Electronic versions are uncontrolled except when accessed directly from the Document Repository.

DOCUMENT NUMBER: 98AON36347E Printed versions are uncontrolled except when stamped “CONTROLLED COPY” in red.

DESCRIPTION: QFN16, 2.5X3.5, 0.5P PAGE 1 OF 1

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.

ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding

the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically

disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the

rights of others.

© Semiconductor Components Industries, LLC, 2019 www.onsemi.com

Downloaded from Arrow.com.

onsemi, , and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba “onsemi” or its affiliates

and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property.

A listing of onsemi’s product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent−Marking.pdf. onsemi reserves the right to make changes at any time to any

products or information herein, without notice. The information herein is provided “as−is” and onsemi makes no warranty, representation or guarantee regarding the accuracy of the

information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use

of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products

and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information

provided by onsemi. “Typical” parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may

vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. onsemi does not convey any license

under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems

or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should

Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates,

and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death

associated with such unintended or unauthorized use, even if such claim alleges that onsemi was negligent regarding the design or manufacture of the part. onsemi is an Equal

Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS: ONLINE SUPPORT: www.onsemi.com/support

Technical Library: www.onsemi.com/design/resources/technical−documentation For additional information, please contact your local Sales Representative at

onsemi Website: www.onsemi.com www.onsemi.com/support/sales

Downloaded from Arrow.com.

You might also like

- TWR 850 - WXR 840Document10 pagesTWR 850 - WXR 840Jacob Jack YoshaNo ratings yet

- NCP81152 ONSemiconductorDocument8 pagesNCP81152 ONSemiconductorwej10358No ratings yet

- ncp5901 r2 OnDocument10 pagesncp5901 r2 OnakashNo ratings yet

- +VCCGT Vegas 15341Document8 pages+VCCGT Vegas 15341Eric ArcherNo ratings yet

- NCP5901 VR12 Compatible Synchronous Buck MOSFET Drivers: Soic 8 NB D Suffix CASE 751 Dfn8 MN Suffix Case 506aaDocument9 pagesNCP5901 VR12 Compatible Synchronous Buck MOSFET Drivers: Soic 8 NB D Suffix CASE 751 Dfn8 MN Suffix Case 506aaDeilyn RivasNo ratings yet

- NCP 81258Document10 pagesNCP 81258Loc Nguyen HuyNo ratings yet

- NCP81253 5 V MOSFET Driver Compatible With Single-Phase IMVP8 ControllersDocument11 pagesNCP81253 5 V MOSFET Driver Compatible With Single-Phase IMVP8 ControllersTom TomNo ratings yet

- NCP81253 5 V MOSFET Driver Compatible With Single-Phase IMVP8 ControllersDocument10 pagesNCP81253 5 V MOSFET Driver Compatible With Single-Phase IMVP8 ControllersBlue StacksNo ratings yet

- NCP5212A, NCP5212T Single Synchronous Step-Down Controller: QFN16 Case 485apDocument19 pagesNCP5212A, NCP5212T Single Synchronous Step-Down Controller: QFN16 Case 485apokeinfoNo ratings yet

- R1283x SERIES: 2ch DC/DC For CCD & OLEDDocument26 pagesR1283x SERIES: 2ch DC/DC For CCD & OLEDarnaud.herbertNo ratings yet

- ADP3110A ONSemiconductorDocument8 pagesADP3110A ONSemiconductorinfosolutionNo ratings yet

- R1283K001CDocument26 pagesR1283K001CdinhdtdNo ratings yet

- NCV8871 Automotive Grade Non-Synchronous Boost Controller: SOIC 8 D Suffix CASE 751Document12 pagesNCV8871 Automotive Grade Non-Synchronous Boost Controller: SOIC 8 D Suffix CASE 751Albaro LedesmaNo ratings yet

- Ne5521 Sa5521 2Document11 pagesNe5521 Sa5521 2José AdelinoNo ratings yet

- bd7905bfs (6CH Power Driver For CD-ROM, DVD-ROMDocument18 pagesbd7905bfs (6CH Power Driver For CD-ROM, DVD-ROMVeiko CastañedaNo ratings yet

- Ic - NCP1631Document24 pagesIc - NCP1631Alexandre SoaresNo ratings yet

- ncv8141d2tg - 1119029 - Regulador - Modulo Direccion ChinacamionetaDocument14 pagesncv8141d2tg - 1119029 - Regulador - Modulo Direccion ChinacamionetaChristiam OrtegaNo ratings yet

- NCP3488 MOSFET Driver With Dual Outputs For Synchronous Buck ConvertersDocument7 pagesNCP3488 MOSFET Driver With Dual Outputs For Synchronous Buck ConvertersRoidysNo ratings yet

- ISL6227CAZDocument26 pagesISL6227CAZEdson HenriqueNo ratings yet

- mc33385vw 80fd951059Document18 pagesmc33385vw 80fd951059MansurjanNo ratings yet

- DatasheetDocument21 pagesDatasheetGEAR OficialNo ratings yet

- Ur4205c Smartpower Enabled Non Flickering Apfc Controller For Led Lighting Data SheetDocument10 pagesUr4205c Smartpower Enabled Non Flickering Apfc Controller For Led Lighting Data Sheetkilowatt СкворцовNo ratings yet

- NCP 81174Document18 pagesNCP 81174techgamebr85No ratings yet

- Onsm S A0013302101 1Document16 pagesOnsm S A0013302101 1123No ratings yet

- ncv8518 - Regulador Voltaje Chevrolet Sonic BCMDocument12 pagesncv8518 - Regulador Voltaje Chevrolet Sonic BCMChristiam OrtegaNo ratings yet

- 546a2 Usb Power MagnagementDocument1 page546a2 Usb Power MagnagementJavierNo ratings yet

- Data Sheet: Smartpower Enabled Combo Controller For High PF Led LightingDocument11 pagesData Sheet: Smartpower Enabled Combo Controller For High PF Led LightingIbrain MoranNo ratings yet

- NE/SA/SE5521 LVDT Signal Conditioner: Description Pin ConfigurationsDocument5 pagesNE/SA/SE5521 LVDT Signal Conditioner: Description Pin ConfigurationsAriel SanusiNo ratings yet

- SA571NDocument11 pagesSA571NCHARILAOS MOULIERISNo ratings yet

- TLE7209 R InfineonDocument16 pagesTLE7209 R Infineonmobil benerNo ratings yet

- Dual Differential Comparators: Features DescriptionDocument29 pagesDual Differential Comparators: Features Descriptionalllim88No ratings yet

- A3995 - PWM Motor DriveDocument9 pagesA3995 - PWM Motor DriveLucas CardosoNo ratings yet

- RF LDMOS Wideband Integrated Power Amplifier: MMRF2004NBR1Document19 pagesRF LDMOS Wideband Integrated Power Amplifier: MMRF2004NBR1bulli babuNo ratings yet

- NCP51810 DDocument20 pagesNCP51810 DArun Rajkumar K PNo ratings yet

- NCP6922C ONSemiconductorDocument42 pagesNCP6922C ONSemiconductorjotikapc2No ratings yet

- 3A Bus Termination Regulator: Features DescriptionDocument14 pages3A Bus Termination Regulator: Features DescriptionZak zsNo ratings yet

- DG401, DG403, DG405: Vishay SiliconixDocument15 pagesDG401, DG403, DG405: Vishay SiliconixytnateNo ratings yet

- JK FF Mc74hc112 DDocument8 pagesJK FF Mc74hc112 DKHÔI PHẠM ĐĂNGNo ratings yet

- Cdcvf25081 (Ck081 Ic) - IfxDocument18 pagesCdcvf25081 (Ck081 Ic) - IfxDwp BhaskaranNo ratings yet

- NCP1582, NCP1582A, NCP1583 Low Voltage Synchronous Buck ControllersDocument16 pagesNCP1582, NCP1582A, NCP1583 Low Voltage Synchronous Buck ControllersDaiverJuarezNo ratings yet

- Dual Operational Amplifiers: Features DescriptionDocument34 pagesDual Operational Amplifiers: Features DescriptionMario Sernaque RumicheNo ratings yet

- NCP662, NCV662, NCP663, NCV663 100 Ma CMOS Low Iq Low-Dropout Voltage RegulatorDocument10 pagesNCP662, NCV662, NCP663, NCV663 100 Ma CMOS Low Iq Low-Dropout Voltage RegulatorTaufiq Adhi MNo ratings yet

- Green-Mode PWM Controller: General Description FeaturesDocument10 pagesGreen-Mode PWM Controller: General Description FeaturesValdir DerlannNo ratings yet

- bd9285f eDocument39 pagesbd9285f eUncle PaneNo ratings yet

- Dual, High-Efficiency, Step-Down Controller With Accurate Current LimitDocument27 pagesDual, High-Efficiency, Step-Down Controller With Accurate Current LimitEdson HenriqueNo ratings yet

- CS3361 Alternator Voltage Regulator FET Driver: FeaturesDocument8 pagesCS3361 Alternator Voltage Regulator FET Driver: FeaturesQUYENNo ratings yet

- cs3361-FET DriverDocument10 pagescs3361-FET DriverSiam_SquareNo ratings yet

- 35V Voltage Resistance 1A LDO Regulator: DatasheetDocument20 pages35V Voltage Resistance 1A LDO Regulator: DatasheetDaniela GarciaNo ratings yet

- 1608b-pqbj Fuente MonoDocument24 pages1608b-pqbj Fuente MonohernanNo ratings yet

- TPS5125Document21 pagesTPS5125Shaun Dwyer Van HeerdenNo ratings yet

- Off-Line Quasi-Resonant Switching Regulators: STR-Y6763, STR-Y6765, and STR-Y6766Document13 pagesOff-Line Quasi-Resonant Switching Regulators: STR-Y6763, STR-Y6765, and STR-Y6766Renato Luther escalanteNo ratings yet

- Ne5521 PDFDocument9 pagesNe5521 PDFCarlos TibussiNo ratings yet

- RF LDMOS Wideband Integrated Power Amplifier: MHV5IC1810NR2Document17 pagesRF LDMOS Wideband Integrated Power Amplifier: MHV5IC1810NR2mohsengsmNo ratings yet

- Datasheet PDFDocument13 pagesDatasheet PDFkandi abdNo ratings yet

- NC7WZ04 D-1812077Document12 pagesNC7WZ04 D-1812077Michał PestrakiewiczNo ratings yet

- S1F76610 Series CMOS DC/DC Converter (Voltage Doubler / Tripler) & Voltage RegulatorDocument14 pagesS1F76610 Series CMOS DC/DC Converter (Voltage Doubler / Tripler) & Voltage RegulatorAndyNo ratings yet

- Infineon Infineon Power Cookbook Zynq UltraScale March 2017rev0.1 ATI v01 - 00 EN PDFDocument13 pagesInfineon Infineon Power Cookbook Zynq UltraScale March 2017rev0.1 ATI v01 - 00 EN PDFanhxcoNo ratings yet

- MC14541B DDocument9 pagesMC14541B DabrkNo ratings yet

- 300ma Dual LDO Regulator With POR: General Description FeaturesDocument12 pages300ma Dual LDO Regulator With POR: General Description FeaturesTitán SotoNo ratings yet

- WS3620-LED Coor Const LAMP - WinsemiDocument7 pagesWS3620-LED Coor Const LAMP - WinsemivmsaNo ratings yet

- Spaulding Lighting Phoenix Spec Sheet 6-79Document2 pagesSpaulding Lighting Phoenix Spec Sheet 6-79Alan MastersNo ratings yet

- JUE-85 Inmarsat C For GMDSSDocument6 pagesJUE-85 Inmarsat C For GMDSSDuta MariusNo ratings yet

- Saida A3 P06623 Manual Central Agility (Unificado) Rev0Document2 pagesSaida A3 P06623 Manual Central Agility (Unificado) Rev0CleberMorelloNo ratings yet

- APsystems Microinverter QT2 For North America Datasheet - Rev1.5 - 2023!06!25Document2 pagesAPsystems Microinverter QT2 For North America Datasheet - Rev1.5 - 2023!06!25Firoz KhanNo ratings yet

- Technical Information Course: Ethsmfb12 10th of Octobre 2011 Gas Natural Fenosa Office HV-Test Set WRV1.5/680Document8 pagesTechnical Information Course: Ethsmfb12 10th of Octobre 2011 Gas Natural Fenosa Office HV-Test Set WRV1.5/680Freddy Escorza100% (1)

- Power Tranducer LSMT2Document10 pagesPower Tranducer LSMT2daniNo ratings yet

- VLSI-Latest Titles: S.No Project Code Project NameDocument10 pagesVLSI-Latest Titles: S.No Project Code Project NameRatnakarVarunNo ratings yet

- Doctor Start 330 230V 12-24VDocument2 pagesDoctor Start 330 230V 12-24VVăn ĐạtNo ratings yet

- KTN-70A OME Rev01 PDFDocument66 pagesKTN-70A OME Rev01 PDFZakaria ChowdhuryNo ratings yet

- WINSEM2018-19 ECE4009 ETH TT631 VL2018195006523 Reference Material I Propagation ModelsDocument27 pagesWINSEM2018-19 ECE4009 ETH TT631 VL2018195006523 Reference Material I Propagation ModelsAarav BhatiaNo ratings yet

- Lecture 2 PDFDocument22 pagesLecture 2 PDFhskakNo ratings yet

- Soal TEORI COC GMDSS Set 22Document9 pagesSoal TEORI COC GMDSS Set 22ANISANo ratings yet

- Digiflex KMTDocument58 pagesDigiflex KMTsarafciger12350% (2)

- Lab 1 TemplateDocument7 pagesLab 1 TemplateAzmienz HierzanzNo ratings yet

- Transfer-Function Measurement With Sweeps PDFDocument52 pagesTransfer-Function Measurement With Sweeps PDFHector Herrera ChavezNo ratings yet

- Unit-V Detection of Radar Signals in NoiseDocument13 pagesUnit-V Detection of Radar Signals in NoiseChennam VaishnaviNo ratings yet

- iMP-550 Eng Lish ManualDocument25 pagesiMP-550 Eng Lish ManualellagitmanNo ratings yet

- E17-S02 - 0 Panel & Switchracks in Hazardous & Non Hazardous AreaDocument10 pagesE17-S02 - 0 Panel & Switchracks in Hazardous & Non Hazardous AreaMuhammad IrfanNo ratings yet

- Isl 83202Document12 pagesIsl 83202prithivirajNo ratings yet

- Sdz6V2Cg: Small Signal Zener DiodeDocument5 pagesSdz6V2Cg: Small Signal Zener DiodeSero StivNo ratings yet

- 10 FM ReceiverDocument9 pages10 FM ReceiverMohamed shabanaNo ratings yet

- Detailed Lesson Plan in Electronics I. ObjectivesDocument5 pagesDetailed Lesson Plan in Electronics I. ObjectivesValen Karl ButayNo ratings yet

- Study of Model Predictive Control Using Ni LabviewDocument10 pagesStudy of Model Predictive Control Using Ni LabviewBrankko Jhonathan Torres SaavedraNo ratings yet

- Manual Eclipse Combustion VeriFlame SingleMonitoring SystemDocument42 pagesManual Eclipse Combustion VeriFlame SingleMonitoring Systemshion2794No ratings yet

- Vol 48 N 2Document24 pagesVol 48 N 2losmilzoNo ratings yet

- Economic Solution For Data Acquisition in A Formula SAE Race CarDocument6 pagesEconomic Solution For Data Acquisition in A Formula SAE Race CarmclarenrulzNo ratings yet

- ESX-200 EXT-200 ECX-200 IME Rev-J v1.31Document48 pagesESX-200 EXT-200 ECX-200 IME Rev-J v1.31Hikmat RahimovNo ratings yet

- Pioneer Deh 3250ub 3290ubDocument23 pagesPioneer Deh 3250ub 3290ubMartin Soko100% (2)

- P7tf-Is16 Os16 Os08 I o Relay Terminals DatasheetDocument9 pagesP7tf-Is16 Os16 Os08 I o Relay Terminals DatasheetcoronaqcNo ratings yet