Professional Documents

Culture Documents

Notes Module2 (FET Part) Basic Electronics 22BBEE203

Notes Module2 (FET Part) Basic Electronics 22BBEE203

Uploaded by

Hani MOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Notes Module2 (FET Part) Basic Electronics 22BBEE203

Notes Module2 (FET Part) Basic Electronics 22BBEE203

Uploaded by

Hani MCopyright:

Available Formats

Basic Electronics_Module-2 FET

FET

Introduction:

A transistor is a semiconductor device that controls current with the application of a

small electrical signal.

Transistors may be roughly grouped into two major families: bipolar and field effect.

BJT utilize a small current to control a large current. But, FET utilizing a small

voltage to control current.

FETs are unipolar rather than bipolar devices. That is, the main current through them

is comprised either of electrons through an N-type semiconductor (N-channel FET) or

holes through a P-type semiconductor (P channel FET).

In a JFET, the controlled current passes from Source to Drain or from Drain to Source

as the case may be. The controlling voltage is applied between the Gate and Source.

Current flowing through this channel widely depends on the input voltage applied to

its Gate terminal.

FETs generally of two types: 1) JFET (Junction Field Effect Transistors) and

2) MOSFET (Metal Oxide Semiconductor Field Effect Transistors).

Junction Field Effect Transistors:

JFET is a voltage controlled three terminal uni-polar semiconductor device. The three

terminals namely, Source (S), Gate (G) and Drain (D).

As the voltage applied to the Gate with respect to the Source (VGS), controls

the current flowing between the Drain and the Source terminals. See fig. JFETs can be

classified into two types (i) n-channel JFET and (ii) p-channel JFET, depending on

whether the current flow is due to electrons or holes, respectively.

Components of FET:

1. Channel: This is the area in which majority charge carriers flow. When the majority

charge carriers are entered in FET, then with the help of this channel only they flow

from source to drain.

Prepared By Nagayya S Hiremath Asst.Prof ECE dept, SVIT Page 1

Basic Electronics_Module-2 FET

2. Source: Source is the terminal through which the majority charge carriers

are introduced in the FET.

3. Drain: Drain is the collecting terminal in which the majority charge carriers enter and

thus contribute in the conduction procedure.

4. Gate: Gate terminal is formed by diffusion of a type of semiconductor with

another type of semiconductor. It basically creates high impurity region which

controls the flow of carrier from source to drain.

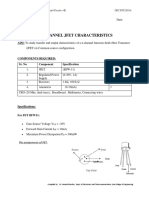

Fig: 2.1 Constructional details of a) N-channel JFET b) P-channel JFET

Working of N-channel JFET:

Case I: No voltage is applied to the device (VDS = 0 and VGS = 0).

At this state, the device will be idle and no current flows through it (IDS = 0).

Case-II: When VDS is applied and VGS = 0

As shown in fig.2.2 (a), the two PN junctions at the sides of the N channel establish depletion

layers. The electrons will flow from Source to Drain through a channel between the depletion

layers. The size of the depletion layers determines the width of the channel and hence current

IDS, conduction through the bar.

Prepared By Nagayya S Hiremath Asst.Prof ECE dept, SVIT Page 2

Basic Electronics_Module-2 FET

Case-III: When VDS is applied and VGS = - ve

The depletion region width increases, which results in reduces the width of

conducting channel, thereby increasing the resistance of n-type bar. Consequently, the

current from Source to Drain is decreased.

If more (-VGS ) is applied, further reduces the channel width until no current

flows through the channel. At this - voltage at which the JFET channel is called as

pinched off voltage, VP.

At this state, the IDS current is restricted only by the channel-resistance. However, once

the pinch-off occurs (VDS = VP), the current IDS saturates at a particular level IDSS.

Fig 2.2 (a) and (b)

Fig 2.3: Circuit diagram of N-channel JFET

Prepared By Nagayya S Hiremath Asst.Prof ECE dept, SVIT Page 3

Basic Electronics_Module-2 FET

Output characteristics (Drain) V-I curves of JFET:

The characteristics curves of a JFET shown in the fig.2.4, reveals four different regions of

operation are given as:

Ohmic Region: When VGS = 0 the depletion region of the channel is very small and the

JFET acts like a voltage controlled resistor.

Cut-off Region: This is also known as the pinch-off region was the Gate voltage, VGS is

sufficient to cause the JFET to act as an open circuit as the channel resistance is at

maximum.

Saturation or Active Region: The JFET becomes a good conductor and is controlled by the

Gate-Source voltage, (VGS) while the Drain-Source voltage, (VDS) has little or no effect.

Breakdown Region: The voltage between the Drain and the Source, (VDS) is high enough to

causes the JFET’s resistive channel to breakdown and pass uncontrolled maximum current.

The characteristics curves for a P-channel junction field effect transistor are the same as

those above, except that the Drain current ID decreases with an increasing positive Gate-

Source voltage, VGS.

Fig 2.4 (a) JFET with VGS=0V and a variable VDS (VDD) (b) The drain Characteristics

curve for VGS=0 showing pinch off voltage

The Drain current IDS is zero when VGS = VP. For normal operation, VGS is biased to be

somewhere between VP and 0. Then we can calculate the Drain current, ID for any given

bias point in the saturation or active region as follows:

Prepared By Nagayya S Hiremath Asst.Prof ECE dept, SVIT Page 4

Basic Electronics_Module-2 FET

1. Drain current in the Active region:

Drain current (ID) at the active region can be calculated as follows: ID lies between (pinch-

off) zero to IDSS.

2. Drain-Source Channel Resistance RDS:

Similarly, if we know drain source voltage Vds and drain current Id, we can calculate the

drain-source channel resistance.

Where: gm is the “trans conductance gain” since the JFET is a voltage controlled device and

which represents the rate of change of the ID with respect to the change in VGS.

3. Amplification Factor: (µ)

It is given by

Transfer characteristics of JFET:

The transfer characteristics can be determined by observing different values of ID with variation

in VGS provided that the VDS should be constant as shown in the fig.2.5.

Notice that the bottom end of the transfer characteristic curve is at a point on the VGS axis

equal to VGS(off), and the top end of the curve is at a point on the ID axis equal to IDSS.

This curve shows that

i) ID = 0; when VGS = VGS(off)

ii) ID = IDSS when VGS = 0

iii) The transfer characteristic curve is expressed approximately

Prepared By Nagayya S Hiremath Asst.Prof ECE dept, SVIT Page 5

Basic Electronics_Module-2 FET

Hence, JFETs are often referred to as square-law devices.

Fig 2.5 Transfer and Drain characteristics

Comparison of BJT and FET:

BJT JFET

Bipolar junction transistor Unipolar junction transistor

Input impedance is very less Input impedance is very large

Current control device, preferred for low Voltage controlled device, preferred for

current applications low voltage applications

More noisy Less noisy

Frequency variations effect its performance High frequency response

Prepared By Nagayya S Hiremath Asst.Prof ECE dept, SVIT Page 6

Basic Electronics_Module-2 FET

Temperature dependent device Better heat stability

Cheaper than FET Costly than BJT

Bigger in size than FET Smaller in size than BJT

More gain Less gain

High output impedance because of high gain Low output impedance because of less

gain

High voltage gain Low voltage gain

Low current gain High current gain

Switching time is medium Switching time is fast

Consumes more power Consumes less power

Metal Oxide Semiconductor Field Effect transistor (MOSFET):

The MOSFET, different from the JFET, has no pn junction structure; instead, the

gate of the MOSFET is insulated from the channel by a silicon dioxide (SiO2) layer

shown in the fig.2.6.

The MOSFET is widely used for switching and amplifying electronic signals. Also,

it is a core of ICs and it can be designed and fabricated in a single chip because of

smaller silicon chip area.

The two basic types of MOSFETs

1. Enhancement MOSFET (E-MOSFET) and

2. Depletion MOSFET (D-MOSFET). Of the two types, the enhancement MOSFET is

more widely used.

Prepared By Nagayya S Hiremath Asst.Prof ECE dept, SVIT Page 7

Basic Electronics_Module-2 FET

Fig.2.6 MOSFET circuit symbols

The depletion mode MOSFETs are generally ON at (VGS = 0V). The conductivity of the

channel in depletion MOSFETs is less compared to the enhancement type of MOSFETs. See

fig. 2.7.

Prepared By Nagayya S Hiremath Asst.Prof ECE dept, SVIT Page 8

Basic Electronics_Module-2 FET

Case I:

When there is no Gate voltage (VGS = 0), as in fig. 2.7, maximum current flows (ID =

IS = IDSS).

Case II:

When VGS = -ve with respect to the substrate, the Gate repels some of the electrons

out of the N-channel.

This creates a depletion region in the channel, as illustrated in fig.2.8, and, therefore,

increases the channel resistance and reduces the Drain current, ID. The more negative

the gate, the less the Drain current.

In this mode of operation, the device is referred to as a depletion-mode

MOSFET. Here too much negative Gate voltage can pinch-off the channel. Then

device is said to be OFF.

Case III:

When VGS = +ve, Gate attracts the negative charge carriers from the P substrate to the

N- channel and thus reduces the channel resistance and increases the drain current,

ID. The more positive the Gate is made, the more Drain current flows. In this mode of

operation, the device is referred to as an enhancement-mode MOSFET. This is

depicted in the fig. 2.9.

Fig.2.9 MOSFET in depletion mode with gate voltage positive

Prepared By Nagayya S Hiremath Asst.Prof ECE dept, SVIT Page 9

Basic Electronics_Module-2 FET

Transfer and Drain characteristic of depletion MOSFET is shown in the fig.2.10.

Fig. 2.10 Transfer characteristic and Drain characteristic of depletion MOSFET

Enhancement Mode:

The construction of an enhancement-type MOSFET is quite similar to that of the depletion-

type MOSFET, except for the absence of an N-channel between the drain and source

terminals.

The minimum value of VGS is required to form the induced N-channel, that turns the E-

MOSFET ON is called threshold voltage [VGS (th)]. For VGS below VGS (th), the drain current

ID = 0.

(i) When VGS = 0 V, VDS = +ve: There is no channel induced between Source and Drain.

The p- substrate has only a few thermally produced free electrons (minority carriers) so that

drain current is almost zero. For this reason, E MOSFET is normally OFF when VGS = 0V.

(ii) When VGS = VGS(th) = + ve, and VDS = + ve: The free electrons developed next to the

SiO2 layer and induced an N channel, as shown in the fig.2.11. Now a Drain current ID starts

flowing. E-MOSFET is turned ON. Beyond VGS (th), if the value of VGS is increased, the

induced N channel becomes wider, resulting large ID. If the value of VGS decreases not less

than VGS (th), the channel becomes narrower and ID will decrease.

Prepared By Nagayya S Hiremath Asst.Prof ECE dept, SVIT Page 10

Basic Electronics_Module-2 FET

Fig. 2.11 MOSFET in enhancement mode with gate voltage positive

Since the conductivity of the channel is enhanced by the positive bias on the Gate, so this

device is also called the enhancement MOSFET or E- MOSFET.

Characteristics of E-MOSFET:

Drain Characteristics curve: fig.2.12 (b), have almost vertical and almost horizontal parts.

The vertical components of the curves correspond to the ohmic region, and the horizontal

components correspond to the saturation region (constant current). Note the following

worthy points:

∙ ID depends on different values of VGS (from 0V to + VGS (max)).

∙ When VGS = 0, even for large increase in VDS, ID = 0. This is said to be cut-off region.

(MOSFET off state).

Prepared By Nagayya S Hiremath Asst.Prof ECE dept, SVIT Page 11

Basic Electronics_Module-2 FET

Transfer Characteristics curve:

i. When VGS < VGS(th), then ID =0. This is because under this state, the channel will not be

connecting between the drain and the source terminals. This is called as cut-off region.

(MOSFET off state). The transfer curves of MOSFET is shown in the fig.2.13.

ii. When VGS > VGS(th),. then ID flows through the device, initially (Ohmic region) and then

saturates to a value (saturation region). That means, ID is controlled by the Gate voltage,

VGS.

iii. ID can be obtained by analytical expression:

I

D= k (VGS VGS(th))2

Fig.2.13 Transfer characteristic of E - MOSFET

Prepared By Nagayya S Hiremath Asst.Prof ECE dept, SVIT Page 12

You might also like

- Module 2Document51 pagesModule 2eswarsenthil2004No ratings yet

- Module 4 FET MOSFETDocument23 pagesModule 4 FET MOSFETsenthilnathanNo ratings yet

- Jfet MosfetDocument25 pagesJfet Mosfethrishabhraj710No ratings yet

- Lecture Notes For Semiconductor Devices and Circuits: JFET and MOSFETDocument25 pagesLecture Notes For Semiconductor Devices and Circuits: JFET and MOSFETdevashri gaurkedeNo ratings yet

- Chapter 7 FET TransistorsDocument118 pagesChapter 7 FET TransistorsosamaNo ratings yet

- Chapter ForDocument17 pagesChapter Forbelacheweshetu222No ratings yet

- Electronics Chapter 4Document16 pagesElectronics Chapter 4YidnekachewNo ratings yet

- Electronics Ii: BY Professor Omotosho T. Victor & DR Akinwumi SayoDocument46 pagesElectronics Ii: BY Professor Omotosho T. Victor & DR Akinwumi SayoOmotosho Temidayo VictorNo ratings yet

- Ece-Research Work 1Document10 pagesEce-Research Work 1Peale ObiedoNo ratings yet

- Electronics Hons C3 FET Field Effect TransistorDocument21 pagesElectronics Hons C3 FET Field Effect TransistorGawrav BaishyaNo ratings yet

- Unit 5 - Electronic Devices - WWW - Rgpvnotes.inDocument17 pagesUnit 5 - Electronic Devices - WWW - Rgpvnotes.inprakharNo ratings yet

- Unit IIIDocument20 pagesUnit IIIionightbotNo ratings yet

- Analog and Digital Electronics (Subject Code: 17CS32) Lecturer NotesDocument59 pagesAnalog and Digital Electronics (Subject Code: 17CS32) Lecturer NotesKarthik v BhatNo ratings yet

- J-FET (Junction Field Effect Transistor)Document28 pagesJ-FET (Junction Field Effect Transistor)Jobins GeorgeNo ratings yet

- Ee 211 Chapter 3Document19 pagesEe 211 Chapter 3RickNo ratings yet

- Field Effect Transisters (FET)Document22 pagesField Effect Transisters (FET)Raja PosupoNo ratings yet

- Field Effect TransistorDocument26 pagesField Effect TransistorsalahuddinNo ratings yet

- MODULE 1 - FET - WatermarkDocument16 pagesMODULE 1 - FET - WatermarkAnupama MohananNo ratings yet

- Module-2 Fets:: Importance of Fets (Motivation)Document22 pagesModule-2 Fets:: Importance of Fets (Motivation)rajuNo ratings yet

- Chapter 4Document16 pagesChapter 4firomsaguteta12No ratings yet

- NPN Transistor TemplateDocument4 pagesNPN Transistor Templateuser.rony302No ratings yet

- Chapter 4 Ele IDocument16 pagesChapter 4 Ele Ibiruk satnawNo ratings yet

- Lecture-1: Notes by Dr. Prem Pal SinghDocument28 pagesLecture-1: Notes by Dr. Prem Pal SinghPrempalSinghNo ratings yet

- Field Effect TransistorsDocument5 pagesField Effect TransistorsMaryam ShahzadiNo ratings yet

- Assignment FET 2Document3 pagesAssignment FET 2shobanraj1995No ratings yet

- EE386 FET - Field Effect TransistorsDocument7 pagesEE386 FET - Field Effect TransistorsKeshara WeerasingheNo ratings yet

- Analog & Digital Electronics: Course No: Ph-218 Lec-26: Field Effect Transistors (Fets)Document7 pagesAnalog & Digital Electronics: Course No: Ph-218 Lec-26: Field Effect Transistors (Fets)Keerthi NalliboyinaNo ratings yet

- EDC Unit-4Document23 pagesEDC Unit-4laxmanabcdNo ratings yet

- Field Effect Transistors (FET) : Comparison Between BJT and FETDocument9 pagesField Effect Transistors (FET) : Comparison Between BJT and FETpranavraikar1No ratings yet

- Unit 2Document69 pagesUnit 2KISHAN SHUKLANo ratings yet

- Unit III Jfet - MosfetDocument20 pagesUnit III Jfet - Mosfet1akshat341No ratings yet

- Draw Input and Output Characteristics of A JFET (BFW10) PDFDocument7 pagesDraw Input and Output Characteristics of A JFET (BFW10) PDFKirti ChandraNo ratings yet

- On Mosfets (Prepared) 1Document75 pagesOn Mosfets (Prepared) 1Ankit RajNo ratings yet

- DEE20023 Chapter 4 JUNCTION FIELD EFFECT TRANSISTOR SESI II 20222023Document51 pagesDEE20023 Chapter 4 JUNCTION FIELD EFFECT TRANSISTOR SESI II 20222023Muhd ZarifNo ratings yet

- JfetDocument19 pagesJfetEEE M.AASTHIKANo ratings yet

- Field Effect Transistor (FET)Document4 pagesField Effect Transistor (FET)Chalez Zengeretsi100% (1)

- Observations: Experimental ValuesDocument7 pagesObservations: Experimental ValuesShibeshwar MandalNo ratings yet

- BE 4 UnitDocument15 pagesBE 4 Unit08sunnyjaganNo ratings yet

- Field Effect Transistors: Field Effect Transistor Is A Semiconductor Device Which Depends On Electric Field For ItsDocument34 pagesField Effect Transistors: Field Effect Transistor Is A Semiconductor Device Which Depends On Electric Field For ItsSivagami AmmuNo ratings yet

- EDC-II Unit-3 Field Effect Transistor & MOSFET TheoryDocument34 pagesEDC-II Unit-3 Field Effect Transistor & MOSFET TheorysamarthNo ratings yet

- Bee CHPT5 2Document7 pagesBee CHPT5 2khan adilNo ratings yet

- 1-5 Coen309-1Document19 pages1-5 Coen309-1mahmoud sadiqNo ratings yet

- ElectronicsDocument22 pagesElectronicsVARSHITH REDDY JNo ratings yet

- Expt - 11: JFET CharacteristicsDocument8 pagesExpt - 11: JFET CharacteristicssamarthNo ratings yet

- JFET and MOSFET CharacteristicsDocument56 pagesJFET and MOSFET CharacteristicsHarry Chandhu100% (1)

- EEE111+ (Exp+7) +Study+of+Switching+CharacteristicsDocument5 pagesEEE111+ (Exp+7) +Study+of+Switching+CharacteristicsFaria SharifNo ratings yet

- Topik 4 - Field Effect Transistors (Fet)Document39 pagesTopik 4 - Field Effect Transistors (Fet)faizah100% (1)

- Erno BorbelyJFETs The New Frontier Part 1and 2Document11 pagesErno BorbelyJFETs The New Frontier Part 1and 2eligeotroNo ratings yet

- Exp7 Mosfet ConfigurationDocument14 pagesExp7 Mosfet ConfigurationAyeshaNo ratings yet

- ECE 027 - Module 5 Field Effect TransistorDocument102 pagesECE 027 - Module 5 Field Effect TransistorMiyuki NakiriNo ratings yet

- Expt 13 - JFET-CharaceristicsDocument8 pagesExpt 13 - JFET-CharaceristicssamarthNo ratings yet

- FETs 11Document55 pagesFETs 11بلسم محمود شاكرNo ratings yet

- Department OF Electronics and Communication Engineering: Lab Instructions For Carrying Out PracticalDocument7 pagesDepartment OF Electronics and Communication Engineering: Lab Instructions For Carrying Out PracticalRishi Raj KanojiaNo ratings yet

- Edc - Unit 5Document37 pagesEdc - Unit 5GANGADHARA SAIPRASANNANo ratings yet

- Field-Effect Transistors: TypesDocument24 pagesField-Effect Transistors: TypesKhuram Shahzad KhalidNo ratings yet

- Controlled Devices FET, BJT, IGBTDocument51 pagesControlled Devices FET, BJT, IGBTHolloGramNo ratings yet

- Construction and Working of A JFETDocument6 pagesConstruction and Working of A JFETSatish Mali100% (1)

- Lecture 2.1.5Document27 pagesLecture 2.1.5Shubham JadhavNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Laser MCQDocument10 pagesLaser MCQFaisal ShahzadNo ratings yet

- Da 1Document2 pagesDa 1benpm320% (1)

- 3 - Unit-2 - LED, Solar Cell, PIN Photo Diode, Avalanche Photo DiodeDocument59 pages3 - Unit-2 - LED, Solar Cell, PIN Photo Diode, Avalanche Photo Diodepooja.amanchiNo ratings yet

- Atomic Structure MCQS: 1 Year N0tes Chemistry NewDocument11 pagesAtomic Structure MCQS: 1 Year N0tes Chemistry NewHaider Jalal100% (10)

- 40 TOP SEMICONDUCTOR THEORY Questions and Answers PDF - MCQs SEMICONDUCTOR THEORY Questions PDFDocument11 pages40 TOP SEMICONDUCTOR THEORY Questions and Answers PDF - MCQs SEMICONDUCTOR THEORY Questions PDFtulasiraoNo ratings yet

- PP Ch6 3rdedDocument82 pagesPP Ch6 3rdedaying mugiwaraNo ratings yet

- Mosfet eDocument3 pagesMosfet eAgnathavasiNo ratings yet

- FHM, May 2011Document5 pagesFHM, May 2011emediageNo ratings yet

- APS 08 Graphene Tutorial KimDocument33 pagesAPS 08 Graphene Tutorial KimChoudhary Lakshya100% (1)

- Introduction To Decoherence TheoryDocument57 pagesIntroduction To Decoherence Theoryahsbon100% (1)

- Valence Bond TheoryDocument3 pagesValence Bond TheorytechzonesNo ratings yet

- Organic Chemistry Worked ExamplesDocument10 pagesOrganic Chemistry Worked ExamplesJohnssii VonRuerich WindsorNo ratings yet

- Edcp - 1Document19 pagesEdcp - 1Raja AdnanNo ratings yet

- Introduction To LaserDocument29 pagesIntroduction To Laserkaushik4208100% (6)

- MosfetDocument30 pagesMosfetsakibNo ratings yet

- Theory of 3 Folds 5 Dimensional UniverseDocument6 pagesTheory of 3 Folds 5 Dimensional UniverseIJARP PublicationsNo ratings yet

- 13Document12 pages13MEOW41No ratings yet

- Wightman AxiomsDocument4 pagesWightman AxiomsShivank MehraNo ratings yet

- Quiz 3 MPHY104 Electronics-I Unit - IIIDocument11 pagesQuiz 3 MPHY104 Electronics-I Unit - IIIAloke VermaNo ratings yet

- D G Kanhere, Center For Simulation and Modeling Pune UniversityDocument74 pagesD G Kanhere, Center For Simulation and Modeling Pune UniversitySelvakapoorNo ratings yet

- Atomic Structure ReviewDocument7 pagesAtomic Structure ReviewKinal PatelNo ratings yet

- Unit 14 Semicondutor Answer KeyDocument14 pagesUnit 14 Semicondutor Answer KeyN NEELAKANDANNo ratings yet

- Chem 373 - Lecture 28: Heteronuclear Diatomic MoleculesDocument28 pagesChem 373 - Lecture 28: Heteronuclear Diatomic MoleculesNuansak3No ratings yet

- Introduction To Condensed Matter PhysicsDocument263 pagesIntroduction To Condensed Matter PhysicsPhysicist91No ratings yet

- DRRG Equipmentlist 29032022 RDocument49 pagesDRRG Equipmentlist 29032022 RjayapalNo ratings yet

- Preib Enrichment Quantum Numbers Edit3Document2 pagesPreib Enrichment Quantum Numbers Edit3api-270154205No ratings yet

- 5.PV - IV CharacteristicsDocument17 pages5.PV - IV CharacteristicsErmias NigussieNo ratings yet

- Operators: Operators and Quantum MechanicsDocument5 pagesOperators: Operators and Quantum MechanicsAniketRaikwarNo ratings yet

- VLSI Class Lecturer-3Document20 pagesVLSI Class Lecturer-3Rubel RiadNo ratings yet

- Waveguide FabricationDocument24 pagesWaveguide FabricationANo ratings yet