Professional Documents

Culture Documents

Problem - Sheet - 5

Problem - Sheet - 5

Uploaded by

Shubhanshu ChauhanOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Problem - Sheet - 5

Problem - Sheet - 5

Uploaded by

Shubhanshu ChauhanCopyright:

Available Formats

Problem Sheet - 5

1. Determine the decimal numbers represented by the following binary numbers: (i) 1110012 (ii) 1010012 (iii) 111111102 (iv) 11001002 (v) 1101.00112 (vi) 1010.10102 (vii) 0.111002 2. Determine the binary numbers represented by the following decimal numbers: (i) 3710 (ii) 25510 (iii) 1510 (iv) 26.2510 (v) 11.7510 (vi) 0.110 3. Convert the following numbers from decimal to octal and then to binary. Compare the binary numbers obtained with the binary numbers obtained directly from the decimal numbers: (i) 37510 (ii) 24910 (iii) 27.12510 4. Find the decimal numbers represented by the following BCD codes: (i) 10000110 (ii) 00110001 (iii) 01010011 (iv) 100101110100 (iv) 0001100001100000.0111 5. Convert the following hexadecimal numbers to decimal: (i) E516 (ii) B2F816 6. Convert the decimal numbers in Problem 3 to hexadecimal and then to binary. Compare the binary numbers obtained with the binary numbers obtained directly from the decimal numbers. 7. Convert the binary numbers in Problem 4 to hexadecimal and then to decimal. Compare the decimal numbers obtained with the decimal numbers obtained directly from the binary numbers. 8. Encode the following decimal numbers in BCD codes: (i) 4610 (ii) 327.8910 (iii) 20.30510 9. Perform the following subtraction using 1s and 2s complement method: (i) 112 102 (ii) 1002 112 (iii) 10102 1112 (iv) 11012 10102 (vi) 101112 111112 (v) 10012 - 11102

10. Add the following BCD numbers: (i) 1000 + 0110 (ii) 0111 + 0101 (iii) 1001 + 1000 (iv) 1001 + 0111 (iv) 00100101 + 00100111 (v) 01010001 + 01011000 (vi) 10011000 + 10010111 (vii) 010101100001 + 011100001000 11. Prove the following using Boolean algebraic theorem; (i) + + = + (ii) + + = + + + + = + + (iii)

12. For an open-collector TTL NOT gate, the specifications are: VOH = 2.4V, VOL = 0.4V, IOH = 250A, IOL = 16mA, IIH = 40A, IIL = -1.6mA Calculate the value of RC required for the open collector gate. Assume VCC = 5V and a fan-out of 8.

13. A

The voltage waveform shown in above figure is applied at the input of 2-input AND, OR, NAND, NOR and XOR gates. Determine the output waveform in each case. 14. Minimize the four variable logic function: f(A, B, C, D) = + + + + + +

15. Minimize following logic functions and realize using NAND/NOR gates: (a) f1 (A, B, C, D) = m(1, 3, 5, 8, 9, 11, 15) + d(2, 13) (b) f2 (A, B, C, D) = M(1, 2, 3, 8, 9, 10, 11, 14). d(7, 15)

16. For a full adder, determine the propagation delay time for Sum output (Sn) and carry output (Cn), assuming the propagation delay time of gates as; EX-OR 20ns AND 10ns OR 10ns and presence of data inputs An, Bn and carry-in Cn-1 simultaneously. 17. Show how two four-bit parallel adders can be connected to form an eight-bit parallel adder. Show outputs for P7P6P5P4P3P2P1P0 = 10111001 and Q7Q6Q5Q4Q3Q2Q1Q0 = 10011110 18. Convert the following binary codes to gray codes using XOR gates; (a) 01012 (b) 001112 (c) 1010112

You might also like

- Problems: Cameron HulseDocument3 pagesProblems: Cameron HulseCameron Hulse100% (1)

- Questions DE-1Document9 pagesQuestions DE-1Riddhesh PatilNo ratings yet

- DLD Da1Document38 pagesDLD Da1Navin Rs0% (1)

- Bolum 1 CozumlerDocument53 pagesBolum 1 Cozumlerrks123No ratings yet

- Ece213 MCQDocument34 pagesEce213 MCQJahnavi JanuNo ratings yet

- Tutorial Sheet3Document1 pageTutorial Sheet3Dhiren GoyalNo ratings yet

- Rajagiri School of Engineering and Technology: Rajagiri Valley, Kakkanad. Third SemesterDocument37 pagesRajagiri School of Engineering and Technology: Rajagiri Valley, Kakkanad. Third SemesterAmrita VenkitaramaniNo ratings yet

- DLD BankDocument16 pagesDLD BankHarshad ThiteNo ratings yet

- Define ComputersDocument1 pageDefine Computerspadmanaban_cseNo ratings yet

- Graded: Number in This Section Is Expressed in 2's Complement FormDocument3 pagesGraded: Number in This Section Is Expressed in 2's Complement FormPaul The HumanNo ratings yet

- Ec312 - Digital Electronics Tutorial Sheet - 1Document1 pageEc312 - Digital Electronics Tutorial Sheet - 1varun89goelNo ratings yet

- Module 1 Number System and Codes Question Bank Feb 2018 PDFDocument3 pagesModule 1 Number System and Codes Question Bank Feb 2018 PDFsanjit0907_982377739No ratings yet

- ECE-223, Solutions For Assignment #1: Chapter 1, Digital Design, M. Mano, 3 EditionDocument3 pagesECE-223, Solutions For Assignment #1: Chapter 1, Digital Design, M. Mano, 3 EditionGajula SureshNo ratings yet

- ECE-223, Solutions For Assignment #1: Chapter 1, Digital Design, M. Mano, 3 EditionDocument3 pagesECE-223, Solutions For Assignment #1: Chapter 1, Digital Design, M. Mano, 3 EditionGajula SureshNo ratings yet

- ECE-223, Solutions For Assignment #1: Chapter 1, Digital Design, M. Mano, 3 EditionDocument3 pagesECE-223, Solutions For Assignment #1: Chapter 1, Digital Design, M. Mano, 3 EditionRonit WadhwaNo ratings yet

- ECE-223, Solutions For Assignment #1: Chapter 1, Digital Design, M. Mano, 3 EditionDocument3 pagesECE-223, Solutions For Assignment #1: Chapter 1, Digital Design, M. Mano, 3 EditionRonit WadhwaNo ratings yet

- Tutorial 1 Digital Number SystemsDocument2 pagesTutorial 1 Digital Number SystemsMrmouzinhoNo ratings yet

- Assignment 2Document3 pagesAssignment 2Syed Abdullah Hasan ChishtiNo ratings yet

- Worksheet 1Document2 pagesWorksheet 1prasad govardanaNo ratings yet

- VL2021220504591 DaDocument2 pagesVL2021220504591 DaDattu GollapinniNo ratings yet

- Assignment-1: Digital Electronics: CT 304-N Semester: 3 (CE/CSE/IT)Document2 pagesAssignment-1: Digital Electronics: CT 304-N Semester: 3 (CE/CSE/IT)Liyanshu patelNo ratings yet

- CS-304 IMP Midterm-1Document4 pagesCS-304 IMP Midterm-1Garam khoonNo ratings yet

- Ecl202 1Document3 pagesEcl202 1shreykumartyagiNo ratings yet

- SGM1 Binary NumbersDocument7 pagesSGM1 Binary NumbersDylan CosepNo ratings yet

- Tutorial 9Document4 pagesTutorial 9thaanusshNo ratings yet

- TCMT N12-2 C1 51900708 DangHoangNamDocument3 pagesTCMT N12-2 C1 51900708 DangHoangNamHoàng NamNo ratings yet

- Tutorial Part 1Document29 pagesTutorial Part 1Noor Zilawati SabtuNo ratings yet

- CSC159 Ch2 Numbering SystemDocument23 pagesCSC159 Ch2 Numbering SystemBebekNo ratings yet

- DCD Assignment QuestionsDocument5 pagesDCD Assignment QuestionsSYAMALANo ratings yet

- Digital Design-Digital Electronics Question BankDocument1 pageDigital Design-Digital Electronics Question BankPaweceNo ratings yet

- Digital Electronics QB 2015-RDocument8 pagesDigital Electronics QB 2015-RKeerthe VaasanNo ratings yet

- TD Serie GlobalDocument6 pagesTD Serie Globalbarr.youcef.magNo ratings yet

- Number SystemDocument6 pagesNumber SystemJoerel NicolasNo ratings yet

- CS2202 DPSD 2 MarksDocument78 pagesCS2202 DPSD 2 MarksVenkat RamananNo ratings yet

- BCA T 113 Digital Electronics Question BankDocument9 pagesBCA T 113 Digital Electronics Question BankAhana MalhotraNo ratings yet

- 2nd Tutorial SerieDocument2 pages2nd Tutorial Seriechorfiroumaissa16No ratings yet

- Tutorial 1 - AnswersDocument1 pageTutorial 1 - AnswersMuhammad IrfanNo ratings yet

- Lab 1 - DLDDocument7 pagesLab 1 - DLDTarviha FatimaNo ratings yet

- DE Assignment No 01Document3 pagesDE Assignment No 01zarachoudhry325No ratings yet

- Problems 1 (Chapter1&2)Document6 pagesProblems 1 (Chapter1&2)Thịnh NguyễnNo ratings yet

- Assignment 1Document2 pagesAssignment 1hardip1No ratings yet

- Electronics For Computing QuestionsDocument30 pagesElectronics For Computing QuestionsKaka MwenyaNo ratings yet

- Tutorial 1Document2 pagesTutorial 1Ratnam KrishnasamyNo ratings yet

- Digital Logics QBDocument9 pagesDigital Logics QBZaid MohammedNo ratings yet

- DLD Question BankDocument5 pagesDLD Question BankHarshad ThiteNo ratings yet

- Tutorial Sheet-1Document2 pagesTutorial Sheet-1vivek patelNo ratings yet

- Selected Answers and Hints For Problem Set 1Document2 pagesSelected Answers and Hints For Problem Set 1vigneshwar RNo ratings yet

- DIGITAL ELECTRONICS - MicroProcessor 2016-17Document4 pagesDIGITAL ELECTRONICS - MicroProcessor 2016-17Prateek singhNo ratings yet

- Repaso 1Document5 pagesRepaso 1Hector GasgaNo ratings yet

- Zzanswer For January 2012-Inb10403Document6 pagesZzanswer For January 2012-Inb10403Aafz ZaafNo ratings yet

- Digital Electronics 1Document8 pagesDigital Electronics 1Tapas BanerjeeNo ratings yet

- Tutorial 1 Co Solutions Tit 402Document14 pagesTutorial 1 Co Solutions Tit 402swatagodaNo ratings yet

- Assingnment# 1Document8 pagesAssingnment# 1Tayyab AbbasNo ratings yet

- CO Unit 1-1Document17 pagesCO Unit 1-1Aravinder Reddy SuramNo ratings yet

- Question Bank AssignmentDocument3 pagesQuestion Bank AssignmentPavankumar MangavalliNo ratings yet

- Modeling and Simulation of Logistics Flows 3: Discrete and Continuous Flows in 2D/3DFrom EverandModeling and Simulation of Logistics Flows 3: Discrete and Continuous Flows in 2D/3DNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Supersymmetry and Generic BSM Models in PYTHIA 8: Nishita Desai, Peter Z. SkandsDocument20 pagesSupersymmetry and Generic BSM Models in PYTHIA 8: Nishita Desai, Peter Z. SkandsShubhanshu ChauhanNo ratings yet

- Competitions: Photography Workshop CS 101 1000 - 1300 1400 - 1700Document4 pagesCompetitions: Photography Workshop CS 101 1000 - 1300 1400 - 1700Shubhanshu ChauhanNo ratings yet

- Phy Mid Sem-TtDocument1 pagePhy Mid Sem-TtShubhanshu ChauhanNo ratings yet

- Particle Magnetic FieldDocument7 pagesParticle Magnetic FieldShubhanshu ChauhanNo ratings yet

- Aoc Le58d3140Document74 pagesAoc Le58d3140Rodney bravaNo ratings yet

- Accelerometer (PROJ REPORT)Document22 pagesAccelerometer (PROJ REPORT)Priya SharmaNo ratings yet

- CKP DiagramDocument6 pagesCKP DiagramAlainbravopaez100% (2)

- Portable GeneratorDocument2 pagesPortable Generatorramsi17No ratings yet

- Protective DevicesDocument4 pagesProtective DevicesKantharaj ChinnappaNo ratings yet

- FSWP UserManual en 12Document662 pagesFSWP UserManual en 12wesNo ratings yet

- PID Tutorial: Step Cloop RedDocument8 pagesPID Tutorial: Step Cloop RedTran SangNo ratings yet

- Lighting Compliance Documentation: Mandatory Provisions ChecklistDocument4 pagesLighting Compliance Documentation: Mandatory Provisions ChecklistBilly CondorNo ratings yet

- LF450Document10 pagesLF450Micheal Chan100% (1)

- Radio Measurements On Radio 4415 B2 B25 Equipment With FCC ID TA8AKRC161636 and IC: 287AB-AS161636Document62 pagesRadio Measurements On Radio 4415 B2 B25 Equipment With FCC ID TA8AKRC161636 and IC: 287AB-AS161636Cleyton Archbold BarkerNo ratings yet

- How To Build FM Transmitter CircuitDocument1 pageHow To Build FM Transmitter Circuitzerihun demereNo ratings yet

- Overhead Robo For Safty & CommunicationDocument2 pagesOverhead Robo For Safty & CommunicationSanjayNo ratings yet

- Lucas Generator and Control Box TestsDocument28 pagesLucas Generator and Control Box TestsAnonymous aOXD9JuqdNo ratings yet

- 12V - 15-21V Car Inverter For NotebookDocument3 pages12V - 15-21V Car Inverter For Notebookmohamed lamine elbiskriNo ratings yet

- Statement of PurposeDocument1 pageStatement of Purposesujeet.jha.311No ratings yet

- SW274 IG enDocument16 pagesSW274 IG enThi KháchNo ratings yet

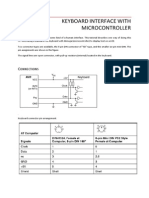

- ps2 Keyboard Interfacing With MicrocontrollerDocument9 pagesps2 Keyboard Interfacing With MicrocontrollerLeslie WrightNo ratings yet

- SecquizDocument3 pagesSecquizdeezm579No ratings yet

- Gates Institute of Technology:: Gooty Digital Circuits and Systems 2 Marks With AnswersDocument20 pagesGates Institute of Technology:: Gooty Digital Circuits and Systems 2 Marks With AnswersNaveen YallapuNo ratings yet

- Electricity and Magnetism Handouts 1Document5 pagesElectricity and Magnetism Handouts 1Homo CiderNo ratings yet

- Sigma-5 To Sigma-7 Transition GuideDocument50 pagesSigma-5 To Sigma-7 Transition GuideKiên NguyễnNo ratings yet

- Title Page, Toc, and PrefaceoldDocument12 pagesTitle Page, Toc, and Prefaceoldarehanliaqat8125No ratings yet

- Wiring CompatibilityDocument8 pagesWiring Compatibilityiba ogbaNo ratings yet

- Quotation-Electrical Items-Exon Machines PVT LTDDocument7 pagesQuotation-Electrical Items-Exon Machines PVT LTDSharafat AliNo ratings yet

- Grid Code-Chapter10Document36 pagesGrid Code-Chapter10Xavier Aldrin Abanilla AustriaNo ratings yet

- Anti-Corrosives & Surface Modulars: Lenses & DiffusersDocument15 pagesAnti-Corrosives & Surface Modulars: Lenses & DiffusersLightingmaniaNo ratings yet

- MPM281 Pressure SensorDocument4 pagesMPM281 Pressure SensorPetr -No ratings yet

- SM 34Document14 pagesSM 34Luis Oswaldo Roa PerezNo ratings yet

- Sked of LoadsDocument11 pagesSked of LoadsJon Cuntapay NonatoNo ratings yet

- DP7645III User's ManualDocument6 pagesDP7645III User's ManualMuh Qadri TappiNo ratings yet