Professional Documents

Culture Documents

Vishu's Notes CAO Unit 10,11,12

Vishu's Notes CAO Unit 10,11,12

Uploaded by

vishal903010 ratings0% found this document useful (0 votes)

4 views18 pagesOriginal Title

Vishu’s Notes CAO Unit 10,11,12

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

Download as pdf

0 ratings0% found this document useful (0 votes)

4 views18 pagesVishu's Notes CAO Unit 10,11,12

Vishu's Notes CAO Unit 10,11,12

Uploaded by

vishal90301Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

Download as pdf

You are on page 1of 18

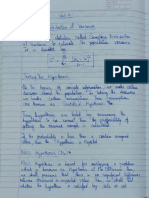

| Umit -lo

laglution &_ dabrractron

spuakon Le ote

ve

(ana (48) + (A+B)

(ea) +)

(-A)+ (+8)

(A+ 8)

(r a)-( B)

(P)-(-8) + (A+B)

-p)- (+8) — (048)

Cn--#

Hard wom Tmnplrunto 0°

— Mimbtrs oS om sergigers 4,8

Ag, Bs be ip fap iros wold

— parolee om +o perform A418

~ Wonp 4 osotor to check AYB a Bthum, cubhacbivn ofcurt Cake one

gations oluaret OrDy tht A inet 0, wet

Hinwien_ovuftow taka (ous o/'- quar orion | divics by

x i {chiding tn 88 4) ,

; eee ovdfow FF ‘= OVE [eucban hee

Hamebling '- O Propraremss't Wanuibbly 0h pve fe

TV dvr uy Com bromeh 9.0 Aulaoubins th hel of,

msaek Lith a pucodiry Hoe dota.

Inofdn combusurs, WU ords tiers Ata bid the voripulls Haus Coll aiviey

Orowwnd :~ provi indomnps rug uit

Wore Ys mubauE ~Givt Orrbe Tag LMIDZp they

aul evan te ovoid divi ovtifiu i1¥0 vy Wookiry Sport ary, O°)

HoueluvOt AY 9:- pale Oars

E

Lecture Notes in Computer Architecture and Organization i

a 4

a 9 4 9

Figure 10-10 4-bi by }-bit array euultiplier.

——____—_—_————— ——

eee

Oth a/9of:-

a a,

eee me d petior kp ub tractive opera 42,

di AB, “nip pe “hy parol HE Mosnce ty

= gn matteo ploa tue mollis Mom ae om cam be

B ay gubyrouktd cantporsctscigoctn OMB) Og

ce pag ade

ra

dikernuved por

jada pun b rgnadlate aE cae of yee rraktad

= tori b then Bs

NO nae oD ie BuaD

Gu ore “lyfe ed

ithecoolestprofessor

Cerne

Lecture Notes in Computer Architecture and Organization

Chapter 11 i

Input-Output Organization

Peripheral Devices

Peripheral devices = input/output devices connected to a computer

‘American Standard Code for Information Interchange (ASCII)

© 7-bit codes

© 94 printable characters + 34 non-printable characters = 128

Memory-mapped input/output

Memory and input/output devices share the same address space

Asynchronous Data Transfer

(2) Block diagram

Data ‘Valid data ——>|

Strobe

(b) Timing diagram

Figure 11-3 Source initiated strobe for data transfer.

Data bus

eer eee |

(2) Block diagram

|

:

Data ‘Valid data 4

|

ee

(6) Timing diagram

Figure 11-4 Destination-initiated strobe for data transfer.

‘Hthecoolestprofessor

: indeqact blw CPU & UP Rot &

Re CORVODLOS) a1 ete

t

Data & Ay nduonet prams}

Addi = Cod format -

a - oy Sep ucts:

i Grr of opuokrt

BA

es eee

ae Ng f

Conwroh h

Cenkintabiatin) Wee

tear wk :

Nolaka H1° i

; ieee — wornman Jf, ‘adds

i Pi, ca

= da Insrrehions -

—ycs

rapped

—> hs) c .

at — Gas ai a nay |

he aoe —all

To IIs

To "0

one Naan tes

Keg} egal 7a

Nayythor0 4s Comysiui carrion Ltafett'-

BH eit ge a,

=o ihe oe" Cerf

Bee 4

hq ee ae

= [a] fen Se Rye

ives,

Spiga

Das vad

\ ;

\ /

(oy Tammy dex

Dec tes

[eat | een

a

Ready for Se

(@) Bat Gaga

Beaty for dae

neg

Des vad

Vaid do

Desa bes

(0) Teming Sagas

w

Lecture Notes in Computer Architecture and Organization

Asynchronous Serial Data Transfer

1, When a character is not being sent, the line is kept in the ks

2, The initiation of a character transmission is detected from y, "8%

which is always 0. “ath,

3. The character bits always follow the start bit,

4 After the last bit of the character is transmitted, a stop bit ig

when the line returns to the I-state for at least one bit tine detec

Baud rate is a measure of data transmitted in unit time

Baud rate may be expressed in bits per second

Input-Output Interface

Transmitter

Receiver

Modem

Brg LUctry vid S|

Modes of Input-Output ans ee ae cag

Programmed input/output selon rtlay Chainthy

Interrupt-initiated input/output Puallel Prigc %

Direct memory access (DMA)

© Burst mode

* Cycle stealing mode

Input-Output Processor (10P)

Supports multiple modes of input/output

sthecoolestprofess™

Memory Mamagerauat tipterm (ee antl & wsog

deen pes :

Main

Memory! hve ee

pranft COS L_ « speeol

‘ra bent ered

cache! MUL program rainy! Lb,

canny, L proyracis “acetal al

dase ross =paabielt prrogrante afr

————__»

———* —___ ,» —

19.2 Mane Meer —— gan S

C seme ceomoluctor Gia Rom) REN

SRAM | Sao

T Pata toed HU pour cupply —— — Jexo ral Useeords

~ fp Hope brewuuters ee ors

~ hte stad yn Joxm y voltage — stored tn pom Of currins

— No

fuermory Mapping fike CONN)

*

=e =a chouackuti be access actin

Aumiliony Macy: tN ee leapaciey] cot

= putes wth novtry pacts requ asektine $0 pos'hin tee astm

pack to a Cocatimn & tromju tim. Aeeletrhne > tram AM

tes if computer Architecture and Organization

no!

ry

on gram computer, Memory stores program and data

wer ced-PPO eae

ng actually @ collection of memory units of different types

y

jer OF

Hierarchy

wer cpu

acer Rung

speed

Volatility

Cost per

byte

Figure 12-1 Memory hierarchy in s computer system.

Main Memory

Random Access Memory (RAM)

* 0s

User programs

Multiprogramming

Multitasking / timesharing

ftthecoolestprofessor

Lecture Notes in Computer Architecture and Organization

Read Only Memory (Rom)

° BIOS

Bootstrap loader

RAM and ROM share the memory space

Cache Memory

Associative memory / Content addressable memory

Hit ratio = hits / (hits + misses)

Hit ratio is 2PProximately 0.9

Writing into Cache memory

o Wri e-through

° Write-back

Secondary Memory

Hard disk

rock 1

Paging

fit...

irtual Memory : :

Ge lly implemented using paging ae

eae imber of pages >> number o} eae

¥ Ristersthicis p > number of bi

.

#thecoolestprofessor

Lecture Notes in Computer Architecture and Organization

@ Use a valid-invalid bit in Page table

page fault

"Page replacement

_ Page replacement algorithms

© FIFO

LRU

Locality of References

Locality of references in code

Locality of references in data

Segmentation

Types of segments

* Code

* Data

Stack

‘Segment registers in 8086

.

Baga

fithecoolestprofessor

39

t :

ecture Notes in Computer Architecture and Organization 40

pS

= x pane eX

Magni? Oisies plawu—rswfae Sh es — teeter pate

7 aa C (40x,

— mctel/ plastic coated wre rHagnassed.

Weakowal

Tracks sak

pead/wrbe — B/W beak on bole Ge

siete ead Dah pot siopick Jot wed ap

Blu bead

Loretto it ofp ® olen

; Os a each frau.

— Dik Hat spudly ltt numb cask gun Spratt

a X a J a

va. alae, easy Po Store fame We. Of bite tm Be eT ane, i

x : used dex A S28 inches

Hod obit

Pana abe Shs oie (neare heute )

=strip 7 Hashe woakd with o magrsh'e cae yd +

Ritr arurroliol ws uta Shots on te fae

cated

: late. tyuuted in betwen 49 Spi,

a whit read [2 reef recone «

fithecoolestprofessor

emits

meeused by conten

ere pe acardd )

ane oe

_ one aniresor tole

Arqunwne Inbitg (words t? tlk. wt)

Ne tmast ry eatlhe & pot

Rey f 1d mate found In

momar bn] ciate

aA | wore of I eset aunmplith ei! ST

Mb

A | 3a MI

lp

=1] (Aj Fy A, Ft ky) SD)

CAR) ae

hack por at Wet of

Sf nee

vl kc

come ta.

vegitle, uel attive® machye Le '.

Maal Tee

ee

bn aed

; ann VOLUs or alard storage

“ont es

bens, tubroutinss, tbe Loeb,

re a

i Sale new

Ales Soa i ape oS a hae as

Waetbss

eT a

Bi Si ct na a cee

i i

Cocke HiE- wre pound — Mik: mot found,

Kit Rawion = Hult )

Bial CPU fawn oo

Cathe Accel Vinee 2+ Time requiied 1 atpus data prom cae. ’

Kus foualey °- Time apuuiot M fetch cate Jrom wi

an : ; , y ;

CK Yrs root Min > Cadudicceyee Mn Pew

(Seana wu in cache

fut)

my Ace Tine? ~ HU fae ¥ Cagis +(I-

Aeus

Karls of cache we

YP k

oe k

8 ye

posts Hate oe oe 4 Couhe)

ELIS ata

mr

CPU ner motnboad

—_____» ———____,. Se

Cathe Mapping i Mow data iy boughs pom main wrsuety [> Ade

O Ayo ceateve '— fastest, y aado elotive otra sores bok addon & Conor

+. CPU cdots Acide int & pat

@ boa eee es addum cold

ach Srnttg | ind Lane] 414 132/436 ;

Stored as

Te eache oe iff]

cru block ki Com be Peade 1

Fporedmd fo (mprove Wt ral.

Tol eae) mo Check Fig Il

Hit Rae ) ae 3 ,)

ae

O Ack Anoctockive Sack unral De Adata wee

some index hus of tag no

13a 4 [ue qed / e882 = 1YSF

TH IZL= [UZ6

Ppladmunk = FIFO, LeU Cae

meee

when dur ae

sniotuaber :- each apy oe

valtol bet ait <0 0 +

set

oS ,

vcd tk Caches watt throwfh cee

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5823)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (898)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (823)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (403)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Vishal GuptaDocument1 pageVishal Guptavishal90301No ratings yet

- Vishu's Notes CAO Unit 5,6,8,9Document40 pagesVishu's Notes CAO Unit 5,6,8,9vishal90301No ratings yet

- Stats Unit 4Document22 pagesStats Unit 4vishal90301No ratings yet

- Content Curation TaskDocument6 pagesContent Curation Taskvishal90301No ratings yet

- Event Management (College)Document8 pagesEvent Management (College)vishal90301No ratings yet

- Practicalfile DbmsDocument23 pagesPracticalfile Dbmsvishal90301No ratings yet