Professional Documents

Culture Documents

ElectronicsI Part III

ElectronicsI Part III

Uploaded by

Chỉnh Nguyễn ThếCopyright:

Available Formats

You might also like

- 23-3-20 - JFET and MOSFET (B25-27)Document45 pages23-3-20 - JFET and MOSFET (B25-27)Shubhankar KunduNo ratings yet

- Field Effect Transistor (FET) : Fajar BudimanDocument42 pagesField Effect Transistor (FET) : Fajar BudimanMohammadFakhriAliNo ratings yet

- Field Effect Transistor & MOSFETDocument40 pagesField Effect Transistor & MOSFETchandrakant chaudhariNo ratings yet

- Unit 2Document69 pagesUnit 2KISHAN SHUKLANo ratings yet

- CHAPTER 4 (I) : Field Effect Transistor (FET)Document27 pagesCHAPTER 4 (I) : Field Effect Transistor (FET)samsung 6000No ratings yet

- JFETs - MOSFETSDocument33 pagesJFETs - MOSFETSpratikdash9938No ratings yet

- Field Effect Transistors: Dr. SK WijayasekaraDocument18 pagesField Effect Transistors: Dr. SK Wijayasekarasaumya irugalbandaraNo ratings yet

- JFET TouhidDocument32 pagesJFET TouhidA.K.M.TOUHIDUR RAHMANNo ratings yet

- 1 Self-BiasDocument6 pages1 Self-BiasSaurav ChourasiaNo ratings yet

- 1 Self-BiasDocument6 pages1 Self-BiasSaurav ChourasiaNo ratings yet

- Field-Effect TransistorsDocument50 pagesField-Effect TransistorsMUHAMMAD SMITHNo ratings yet

- ch6 2Document31 pagesch6 2avishek aviNo ratings yet

- 15EC101 - Basic Electronics Engineering-All UnitsDocument366 pages15EC101 - Basic Electronics Engineering-All UnitssubhaNo ratings yet

- JFETs - MOSFETSDocument43 pagesJFETs - MOSFETSmarrilaharikrishnaNo ratings yet

- Basic Ele Module-2Document21 pagesBasic Ele Module-2Rachana MedehalNo ratings yet

- Electronic Devices and Circuit Theory: Field-Effect TransistorsDocument34 pagesElectronic Devices and Circuit Theory: Field-Effect TransistorsNasser AlmofariNo ratings yet

- A.Electronics Chapter 4Document30 pagesA.Electronics Chapter 4enatiye2015No ratings yet

- Chapter 4Document16 pagesChapter 4firomsaguteta12No ratings yet

- MOSFETDocument17 pagesMOSFETShafiul Huda ErazNo ratings yet

- Field-Effect Transistors - Part 1: Reference Book: Electronic Devices and Circuit Theory (11 Edition) Robert F. BoylestadDocument27 pagesField-Effect Transistors - Part 1: Reference Book: Electronic Devices and Circuit Theory (11 Edition) Robert F. BoylestadKazi TanvirNo ratings yet

- Lecture 4 - FETDocument32 pagesLecture 4 - FETNimsiri AbhayasingheNo ratings yet

- Introduction To FET's: ELEC 121 Author UnknownDocument36 pagesIntroduction To FET's: ELEC 121 Author UnknownM Junaid Sultan100% (1)

- Mosfet Part 2Document19 pagesMosfet Part 2MUHAMMAD KHAIRUL ANUAR BIN JUHARI A22EE0178No ratings yet

- Introduction To FET's: ELEC 121 Author UnknownDocument36 pagesIntroduction To FET's: ELEC 121 Author UnknownNaseeb AghaNo ratings yet

- Electronics Chapter 4Document16 pagesElectronics Chapter 4YidnekachewNo ratings yet

- L5 Week6 FET Intro Chap6 RJDocument48 pagesL5 Week6 FET Intro Chap6 RJAmir MustakimNo ratings yet

- Chapter ForDocument17 pagesChapter Forbelacheweshetu222No ratings yet

- Electronic II-1Document10 pagesElectronic II-1Isaac DanielNo ratings yet

- Junction Field Effect Transistor: Electronic Devices & CircuitsDocument10 pagesJunction Field Effect Transistor: Electronic Devices & CircuitsMuhammad IbadNo ratings yet

- Field Effect TransistorsDocument50 pagesField Effect TransistorsA.K.M.TOUHIDUR RAHMANNo ratings yet

- Module 2Document51 pagesModule 2eswarsenthil2004No ratings yet

- Lec 03Document15 pagesLec 03Pratibha RajNo ratings yet

- Analog & Digital Electronics: Course No: Ph-218 Lec-26: Metal Oxide Field Effect Transistors (Mosfets)Document16 pagesAnalog & Digital Electronics: Course No: Ph-218 Lec-26: Metal Oxide Field Effect Transistors (Mosfets)Udai SinghNo ratings yet

- ��هندسة الكترونيات (1) - الأسبوع الثاني عاشر�Document27 pages��هندسة الكترونيات (1) - الأسبوع الثاني عاشر�Yehia ElrifyNo ratings yet

- B.E. FETs and Other Components NotesDocument12 pagesB.E. FETs and Other Components NotesLaxman SalianNo ratings yet

- Chap6 Part1 PDFDocument19 pagesChap6 Part1 PDFOmar Ahmed AbuLeilaNo ratings yet

- Expt 13 - JFET-CharaceristicsDocument8 pagesExpt 13 - JFET-CharaceristicssamarthNo ratings yet

- Expt - 11: JFET CharacteristicsDocument8 pagesExpt - 11: JFET CharacteristicssamarthNo ratings yet

- Field Effect Transistors PDFDocument102 pagesField Effect Transistors PDFanjanaNo ratings yet

- Center For Advanced Studies in Engineering, Islamabad Electronics LabDocument9 pagesCenter For Advanced Studies in Engineering, Islamabad Electronics LabHussain HadiNo ratings yet

- Chap3a - FET (v1.2)Document70 pagesChap3a - FET (v1.2)Al AidenNo ratings yet

- Chapter 7 8 9 FETDocument97 pagesChapter 7 8 9 FETnndung.2k5No ratings yet

- Chapter 4 Ele IDocument16 pagesChapter 4 Ele Ibiruk satnawNo ratings yet

- My Lec MOSFET All F MineDocument25 pagesMy Lec MOSFET All F MineArun JagaNo ratings yet

- Lab5 JFET Characteristics and ApplicationDocument9 pagesLab5 JFET Characteristics and ApplicationMohmmad AlkhaldiNo ratings yet

- AnalogEl 2 FETDocument38 pagesAnalogEl 2 FETAlbert GenceNo ratings yet

- Field Effect TransistorsDocument59 pagesField Effect TransistorsRan QuitNo ratings yet

- Lecture 2.3: FET IntroductionDocument3 pagesLecture 2.3: FET IntroductionAids Sumalde0% (1)

- Vishwas BeeeDocument17 pagesVishwas BeeeyashNo ratings yet

- Exp 5Document5 pagesExp 5MohammedZahidNo ratings yet

- Chapter 5Document10 pagesChapter 5migmakeNo ratings yet

- Notes Module2 (FET Part) Basic Electronics 22BBEE203Document12 pagesNotes Module2 (FET Part) Basic Electronics 22BBEE203Hani MNo ratings yet

- @3 FET FundamentalsDocument210 pages@3 FET Fundamentalschâu nguyễn ngọcNo ratings yet

- Jfet NRP Lecture 2Document97 pagesJfet NRP Lecture 2Nitin PrajapatiNo ratings yet

- Mosfet (Iii) - I-V CharacteristicsDocument11 pagesMosfet (Iii) - I-V Characteristics許博凱No ratings yet

- ElectronicsDocument22 pagesElectronicsVARSHITH REDDY JNo ratings yet

- Feynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterFrom EverandFeynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterNo ratings yet

- Wireless LAN MAC ProtocolsDocument11 pagesWireless LAN MAC ProtocolsChỉnh Nguyễn ThếNo ratings yet

- PowerApps Connectors Reference (PDFDrive)Document2,622 pagesPowerApps Connectors Reference (PDFDrive)Chỉnh Nguyễn Thế100% (1)

- IPv6Security Appendix Devices OverviewDocument2 pagesIPv6Security Appendix Devices OverviewChỉnh Nguyễn ThếNo ratings yet

- IPv6Security CourseIntroDocument1 pageIPv6Security CourseIntroChỉnh Nguyễn ThếNo ratings yet

- Ipv6 Security Training Course: Exercise BookletDocument28 pagesIpv6 Security Training Course: Exercise BookletChỉnh Nguyễn ThếNo ratings yet

- IPv6Security CourseIntroDocument1 pageIPv6Security CourseIntroChỉnh Nguyễn ThếNo ratings yet

- IPv6Security CourseIntroDocument1 pageIPv6Security CourseIntroChỉnh Nguyễn ThếNo ratings yet

- Ipv6 Security Training Course: ReferencesDocument11 pagesIpv6 Security Training Course: ReferencesChỉnh Nguyễn ThếNo ratings yet

- Diodes BJT and FetDocument52 pagesDiodes BJT and FetMadeleine NavarreteNo ratings yet

- FinFET TEchnologiesDocument2 pagesFinFET TEchnologiessurya tejaNo ratings yet

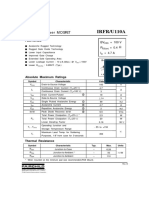

- IRFR/U110A: Advanced Power MOSFETDocument7 pagesIRFR/U110A: Advanced Power MOSFETAbel RodriguezNo ratings yet

- BLHeli Supported Atmel ESCsDocument34 pagesBLHeli Supported Atmel ESCsFly HighNo ratings yet

- Irjet V3i7474 PDFDocument4 pagesIrjet V3i7474 PDFSergiu HălăucăNo ratings yet

- Experiment-1 Aim: VDD=5V VT,n=0.8V VT,p=-0.8V (W/L) p=2.5 (W/L) n=1 Technology=1μ1Document5 pagesExperiment-1 Aim: VDD=5V VT,n=0.8V VT,p=-0.8V (W/L) p=2.5 (W/L) n=1 Technology=1μ1Timir PatelNo ratings yet

- 2SA1357Document2 pages2SA1357Kike VillasurNo ratings yet

- Multisim Act, 3,4,5,6,7 On Electronic Devices Sir MirandaDocument20 pagesMultisim Act, 3,4,5,6,7 On Electronic Devices Sir MirandaKimberly CarreonNo ratings yet

- Soft-Error-Aware Read-Stability-Enhanced Low-Power 12T SRAM With Multi-Node Upset Recoverability For Aerospace ApplicationsDocument11 pagesSoft-Error-Aware Read-Stability-Enhanced Low-Power 12T SRAM With Multi-Node Upset Recoverability For Aerospace ApplicationsZhongpeng LiangNo ratings yet

- ANALOGUE CAT 1 AnswersDocument10 pagesANALOGUE CAT 1 Answersamanda christineNo ratings yet

- Ee 366 Chap 1 3Document10 pagesEe 366 Chap 1 3Michael Adu-boahenNo ratings yet

- Semiconductor Memories: VLSI Design (18EC72)Document11 pagesSemiconductor Memories: VLSI Design (18EC72)PraveenNo ratings yet

- NPN Silicon Epitaxial Planar Transistor: Semtech Electronics LTDDocument2 pagesNPN Silicon Epitaxial Planar Transistor: Semtech Electronics LTDalexjcc10No ratings yet

- DatasheetDocument1 pageDatasheetStuxnetNo ratings yet

- MCQ'S of Digital Vlsi DesignDocument12 pagesMCQ'S of Digital Vlsi Designnayna bhosaleNo ratings yet

- Assignment 1Document2 pagesAssignment 1LJYLowNo ratings yet

- Basic VLSI Design Unit-3Document50 pagesBasic VLSI Design Unit-3N.RAMAKUMARNo ratings yet

- Semiconductor Physics MCQ'SDocument9 pagesSemiconductor Physics MCQ'SGuruKPONo ratings yet

- A Review Paper On CNTFET Technology and Circuit Designing Using CNTFETDocument3 pagesA Review Paper On CNTFET Technology and Circuit Designing Using CNTFETGopi Reddy RanabothuNo ratings yet

- Delta Electronics, IncDocument8 pagesDelta Electronics, IncSasha NaumchenkoNo ratings yet

- Analytical Modeling of Tunneling Field Effect Transistor (TFET)Document22 pagesAnalytical Modeling of Tunneling Field Effect Transistor (TFET)Girdhar Gopal GautamNo ratings yet

- Depletion-Mode: Further Information: andDocument3 pagesDepletion-Mode: Further Information: andshohobiNo ratings yet

- s9013 Tranzistor DatasheetDocument1 pages9013 Tranzistor DatasheetJeno TrutaNo ratings yet

- TransistorsDocument5 pagesTransistorsSyed Fawad AdilNo ratings yet

- DVLSI Lab EXPT1 ManualDocument8 pagesDVLSI Lab EXPT1 ManualApoorvaNo ratings yet

- Electronics Module 3Document18 pagesElectronics Module 3tirsollantada100% (1)

- What Is PNP Transistor - Construction, Working & ApplicationsDocument34 pagesWhat Is PNP Transistor - Construction, Working & ApplicationsgezahegnNo ratings yet

- Silicon NPN Power Transistors: Inchange Semiconductor Product SpecificationDocument4 pagesSilicon NPN Power Transistors: Inchange Semiconductor Product SpecificationNazo FsNo ratings yet

- Bicmos Inverter UploadDocument3 pagesBicmos Inverter UploadHasanAlBannaBhuiyanNo ratings yet

- LDMOSDocument6 pagesLDMOShaseebNo ratings yet

ElectronicsI Part III

ElectronicsI Part III

Uploaded by

Chỉnh Nguyễn ThếOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ElectronicsI Part III

ElectronicsI Part III

Uploaded by

Chỉnh Nguyễn ThếCopyright:

Available Formats

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Philadelphia University

Faculty of Engineering

Communication and Electronics Engineering

Field-Effect Transistor

Introduction

FETs (Field-Effect Transistors) are much like BJTs (Bipolar Junction Transistors).

Similarities:

• Amplifiers

• Switching devices

• Impedance matching circuits

Differences:

FETs are voltage controlled devices whereas BJTs are current controlled devices.

FETs also have higher input impedance, but BJTs have higher gains.

FETs are less sensitive to temperature variations and because of there

construction they are more easily integrated on ICs.

FETs are also generally more static sensitive than BJTs.

In the BJT-the prefix bi-revealing that the conduction level is a function of two

charge carriers, electrons and holes. The FET is unipolar device depending on

either electrons or holes conduction.

FET Types

• JFET–– Junction Field-Effect Transistor

• MOSFET –– Metal-Oxide Field-Effect Transistor

D-MOSFET –– Depletion MOSFET

E-MOSFET –– Enhancement MOSFET

JFET

JFET Construction

There are two types of JFETs:

• n-channel (The n-channel is more widely used.)

• p-channel

There are three terminals:

• Drain (D)

• Source (S) are connected to the n-channel

Lecturer: Dr. Omar Daoud ١

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

• Gate (G) is connected to the p-type material

Basic Operation of a JFET

JFET operation can be compared to a water

spigot.

The source of water pressure is the accumulation

of electrons at the negative pole of the drain-source

voltage.

The drain of water is the electron deficiency (or

holes) at the positive pole of the applied voltage.

The control (gate) of flow of water is the gate

voltage that controls the width of the n-channel

and, therefore, the flow of charges from source to

drain.

JFET Operating Characteristics

Three things happen when VGS = 0 and VDS is

increased from 0 to a more positive voltage

• The depletion region between p-gate and n-

channel increases as electrons from n-

channel combine with holes from p-gate.

• Increasing the depletion region, decreases

the size of the n-channel which increases the

resistance of the n-channel.

• Even though the n-channel resistance is

increasing, the current (ID) from source to

drain through the n-channel is increasing.

This is because VDS is increasing.

If VGS = 0 and VDS is further increased to a more positive

voltage, then the depletion zone gets so large that it pinches

off the n-channel.

This suggests that the current in the n-channel (ID) would

drop to 0A, but it does just the opposite–as VDS increases,

so does ID.

Lecturer: Dr. Omar Daoud ٢

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

At the pinch-off point:

• Any further increase in VGS does not

produce any increase in ID. VGS at pinch-

off is denoted as Vp.

• ID is at saturation or maximum. It is

referred to as IDSS.

• The ohmic value of the channel is

maximum.

As VGS becomes more negative, the depletion

region increases.

• The JFET experiences pinch-off at a lower

voltage (Vp).

• ID decreases (ID < IDSS) even though

VDS is increased.

• Eventually ID reaches 0A. VGS at this

point is called Vp or VGS(off)..

Also note that at high levels of

VDS the JFET reaches a

breakdown situation. ID increases

uncontrollably if VDS > VDSmax.

The region to the left of the

pinch-off point is called the

ohmic region.

The JFET can be used as a

variable resistor, where VGS

controls the drain-source

resistance (rd). As VGS becomes

more negative, the resistance (rd)

increases.

ro

rd 2

VGS

1

VP

Where ro is the resistance with VGS=0 and rd the resistance at a particular level of VGS.

Lecturer: Dr. Omar Daoud ٣

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

The transfer characteristic of input-to-output is not as straightforward in a JFET as it is

in a BJT. In a BJT, indicates the relationship between IB (input) and IC (output).

In a JFET, the relationship of VGS (input) and ID (output) is a little more complicated:

2

ID I VGS

DSS 1 V

P

Summary:

Lecturer: Dr. Omar Daoud ٤

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

JFET Transfer (Characteristics) Curve

This graph shows the value of

ID for a given value of VGS.

Using IDSS and Vp (VGS(off))

values found in a

specification sheet, the

transfer curve can be plotted

according to these three

steps:

Step 1 2

V

Solving for VGS = 0V, I D I DSS 1 GS I D I DSS

VP

Step 2

Solving for VGS = Vp (VGS(off)) ID = 0A

Step 3

Solving for VGS = 0V to Vp

Fig. 6.18 Transfer curve for Example 6.1. Fig. 7.17 Example 7.3.

Lecturer: Dr. Omar Daoud ٥

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Exmple 6.1:

MOSFET

MOSFETs have characteristics similar to JFETs

and additional characteristics that make then very

useful.

There are two types of MOSFETs:

• Depletion-Type

• Enhancement-Type

The drain (D) and source (S) connect to the to n-

doped regions. These n-doped regions are

connected via an n-channel. This n-channel is

connected to the gate (G) via a thin insulating layer

of SiO2.

The n-doped material lies on a p-doped substrate that may have an additional terminal

connection called substrate (SS).

A depletion-type MOSFET

can operate in two modes:

• Depletion mode

• Enhancement mode

Depletion Mode:

The characteristics are similar

to a JFET.

• When VGS = 0V, ID = IDSS

• When VGS < 0V, ID < IDSS

Fig. 5.25 Drain and transfer characteristics for an n-channel depletion-type

MOSFET.

Lecturer: Dr. Omar Daoud ٦

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

• The formula used to plot the transfer curve still applies:

2

V

I D I DSS 1 GS

VP

Fig. 5.24 n-Channel depletion-type MOSFET

with VGS = 0 V and applied voltage VDD.

Enhancement Mode:

• VGS > 0V

• ID increases above IDSS

• The formula used to plot the transfer curve still applies:

2

V

I D I DSS 1 GS

VP

Enhancement-Type MOSFET Construction

• The drain (D) and source (S) connect to the n-

doped regions. These n-doped regions are

connected via an n-channel

• The gate (G) connects to the p-doped substrate

via a thin insulating layer of SiO2

Lecturer: Dr. Omar Daoud ٧

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

• There is no channel

• The n-doped material lies on a p-doped substrate that may have an additional

terminal connection called the substrate (SS)

The enhancement-type MOSFET only operates in the enhancement mode.

• VGS is always

positive

• As VGS increases,

ID increases

• As VGS is kept

constant and VDS is

increased, then ID

saturates (IDSS) and

the saturation level,

VDSsat is reached

Lecturer: Dr. Omar Daoud ٨

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Field-Effect Transistor Amplifiers

Transconductance

The relationship of VGS(input) to ID(output) is

called transconductance. Transconductance is

denoted gm and given by:

ΔI D 2I VGS

gm DSS 1

ΔV GS VP VP

Where VGS =0V 2I

g m0 DSS

VP

V

g m g m0 1 GS

VP

Where

VGS ID V ID

1 g m g m0 1 GS g m0

VP I DSS VP I DSS

The prefix trans- in the terminology applied to gm reveals that it establishes a

relationship between an output and input quantity. The root word conductance was

chosen because it is determined by a voltage-to-current ratio similar to the ratio that

defines the conductance of a resistor.

FET Impedance

1

Z o rd

y os

where:

VDS

rd V constant

I D GS

yos= admittance equivalent circuit parameter

listed on FET specification sheets. FET AC Equivalent Circuit

FET Biasing

Lecturer: Dr. Omar Daoud ٩

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

JFET Common-Source (CS) Fixed-Bias Configuration

The input is on the gate and the output is on the drain. There is a 180 phase shift

between input and output

Zi R G

Z o R D || rd

Zo R D

rd 10R D

Vo

Av g m (rd || R D )

Vi

V

A v o g m R D

Vi rd 10R D

Lecturer: Dr. Omar Daoud ١٠

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Example 7.1:

Lecturer: Dr. Omar Daoud ١١

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Solution:

Lecturer: Dr. Omar Daoud ١٢

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Cont. Example 7.1:

Solution:

JFET Common-Source (CS) Self-Bias Configuration

It eliminates the need for two dc supplies. The controlling VGS is now determined by the

voltage across a resistor Rs.

Lecturer: Dr. Omar Daoud ١٣

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Bypassed RS:

Unbypassed RS:

Fig. 8.18 Self-bias JFET configuration including the effects of RS with rd = ∞ Ω.

Lecturer: Dr. Omar Daoud ١٤

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Example 7.2:

Lecturer: Dr. Omar Daoud ١٥

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Solution:

Cont. Example 7.2.:

Lecturer: Dr. Omar Daoud ١٦

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Solution:

Common Source Voltage Divider Bias Configuration

Lecturer: Dr. Omar Daoud ١٧

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Lecturer: Dr. Omar Daoud ١٨

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Example 7.5:

Solution:

Fig. 7.25 Example 7.5.

Fig. 7.26 Determining the Q-point for the network of Fig. 7.25.

Lecturer: Dr. Omar Daoud ١٩

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Example 7.6:

Lecturer: Dr. Omar Daoud ٢٠

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Solution:

Lecturer: Dr. Omar Daoud ٢١

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Source Follower (Common-Drain) Configuration

In a common-drain amplifier configuration, the input is on the gate, but the output is

from the source. There is no phase shift between input and output.

Zi R G

1

Z o rd || R S ||

gm

1

Z o R S || rd 10R S

gm

Vo g m (rd || R S )

Av

Vi 1 g m (rd || R S )

V gmRS

Av o r 10

Vi 1 g m R S d

Fig. 8.29 Network to be analyzed in Example 8.9.

Lecturer: Dr. Omar Daoud ٢٢

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Lecturer: Dr. Omar Daoud ٢٣

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Example 8.9:

Solution:

Lecturer: Dr. Omar Daoud ٢٤

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

JFET Common-Gate Configuration

The input is on the source and the output is on the drain. There is no phase shift between

input and output.

r RD

Z i R S || d

1 g m rd

1

Z i R S || r 10R

gm d D

Z o R D || rd

Zo R D rd 10

RD

g m R D

Vo rd

Av

Vi RD

1

rd

Av gmR D rd 10R D

Lecturer: Dr. Omar Daoud ٢٥

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Example 8.10:

Solution:

Lecturer: Dr. Omar Daoud ٢٦

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Fig. 8.33 Network for Example 8.10.

Lecturer: Dr. Omar Daoud ٢٧

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Design Example 1:

Lecturer: Dr. Omar Daoud ٢٨

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Design Example 2:

Lecturer: Dr. Omar Daoud ٢٩

Module: Electronics I Module Number: 610/650221-222

Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky

Design Example 3:

Lecturer: Dr. Omar Daoud ٣٠

You might also like

- 23-3-20 - JFET and MOSFET (B25-27)Document45 pages23-3-20 - JFET and MOSFET (B25-27)Shubhankar KunduNo ratings yet

- Field Effect Transistor (FET) : Fajar BudimanDocument42 pagesField Effect Transistor (FET) : Fajar BudimanMohammadFakhriAliNo ratings yet

- Field Effect Transistor & MOSFETDocument40 pagesField Effect Transistor & MOSFETchandrakant chaudhariNo ratings yet

- Unit 2Document69 pagesUnit 2KISHAN SHUKLANo ratings yet

- CHAPTER 4 (I) : Field Effect Transistor (FET)Document27 pagesCHAPTER 4 (I) : Field Effect Transistor (FET)samsung 6000No ratings yet

- JFETs - MOSFETSDocument33 pagesJFETs - MOSFETSpratikdash9938No ratings yet

- Field Effect Transistors: Dr. SK WijayasekaraDocument18 pagesField Effect Transistors: Dr. SK Wijayasekarasaumya irugalbandaraNo ratings yet

- JFET TouhidDocument32 pagesJFET TouhidA.K.M.TOUHIDUR RAHMANNo ratings yet

- 1 Self-BiasDocument6 pages1 Self-BiasSaurav ChourasiaNo ratings yet

- 1 Self-BiasDocument6 pages1 Self-BiasSaurav ChourasiaNo ratings yet

- Field-Effect TransistorsDocument50 pagesField-Effect TransistorsMUHAMMAD SMITHNo ratings yet

- ch6 2Document31 pagesch6 2avishek aviNo ratings yet

- 15EC101 - Basic Electronics Engineering-All UnitsDocument366 pages15EC101 - Basic Electronics Engineering-All UnitssubhaNo ratings yet

- JFETs - MOSFETSDocument43 pagesJFETs - MOSFETSmarrilaharikrishnaNo ratings yet

- Basic Ele Module-2Document21 pagesBasic Ele Module-2Rachana MedehalNo ratings yet

- Electronic Devices and Circuit Theory: Field-Effect TransistorsDocument34 pagesElectronic Devices and Circuit Theory: Field-Effect TransistorsNasser AlmofariNo ratings yet

- A.Electronics Chapter 4Document30 pagesA.Electronics Chapter 4enatiye2015No ratings yet

- Chapter 4Document16 pagesChapter 4firomsaguteta12No ratings yet

- MOSFETDocument17 pagesMOSFETShafiul Huda ErazNo ratings yet

- Field-Effect Transistors - Part 1: Reference Book: Electronic Devices and Circuit Theory (11 Edition) Robert F. BoylestadDocument27 pagesField-Effect Transistors - Part 1: Reference Book: Electronic Devices and Circuit Theory (11 Edition) Robert F. BoylestadKazi TanvirNo ratings yet

- Lecture 4 - FETDocument32 pagesLecture 4 - FETNimsiri AbhayasingheNo ratings yet

- Introduction To FET's: ELEC 121 Author UnknownDocument36 pagesIntroduction To FET's: ELEC 121 Author UnknownM Junaid Sultan100% (1)

- Mosfet Part 2Document19 pagesMosfet Part 2MUHAMMAD KHAIRUL ANUAR BIN JUHARI A22EE0178No ratings yet

- Introduction To FET's: ELEC 121 Author UnknownDocument36 pagesIntroduction To FET's: ELEC 121 Author UnknownNaseeb AghaNo ratings yet

- Electronics Chapter 4Document16 pagesElectronics Chapter 4YidnekachewNo ratings yet

- L5 Week6 FET Intro Chap6 RJDocument48 pagesL5 Week6 FET Intro Chap6 RJAmir MustakimNo ratings yet

- Chapter ForDocument17 pagesChapter Forbelacheweshetu222No ratings yet

- Electronic II-1Document10 pagesElectronic II-1Isaac DanielNo ratings yet

- Junction Field Effect Transistor: Electronic Devices & CircuitsDocument10 pagesJunction Field Effect Transistor: Electronic Devices & CircuitsMuhammad IbadNo ratings yet

- Field Effect TransistorsDocument50 pagesField Effect TransistorsA.K.M.TOUHIDUR RAHMANNo ratings yet

- Module 2Document51 pagesModule 2eswarsenthil2004No ratings yet

- Lec 03Document15 pagesLec 03Pratibha RajNo ratings yet

- Analog & Digital Electronics: Course No: Ph-218 Lec-26: Metal Oxide Field Effect Transistors (Mosfets)Document16 pagesAnalog & Digital Electronics: Course No: Ph-218 Lec-26: Metal Oxide Field Effect Transistors (Mosfets)Udai SinghNo ratings yet

- ��هندسة الكترونيات (1) - الأسبوع الثاني عاشر�Document27 pages��هندسة الكترونيات (1) - الأسبوع الثاني عاشر�Yehia ElrifyNo ratings yet

- B.E. FETs and Other Components NotesDocument12 pagesB.E. FETs and Other Components NotesLaxman SalianNo ratings yet

- Chap6 Part1 PDFDocument19 pagesChap6 Part1 PDFOmar Ahmed AbuLeilaNo ratings yet

- Expt 13 - JFET-CharaceristicsDocument8 pagesExpt 13 - JFET-CharaceristicssamarthNo ratings yet

- Expt - 11: JFET CharacteristicsDocument8 pagesExpt - 11: JFET CharacteristicssamarthNo ratings yet

- Field Effect Transistors PDFDocument102 pagesField Effect Transistors PDFanjanaNo ratings yet

- Center For Advanced Studies in Engineering, Islamabad Electronics LabDocument9 pagesCenter For Advanced Studies in Engineering, Islamabad Electronics LabHussain HadiNo ratings yet

- Chap3a - FET (v1.2)Document70 pagesChap3a - FET (v1.2)Al AidenNo ratings yet

- Chapter 7 8 9 FETDocument97 pagesChapter 7 8 9 FETnndung.2k5No ratings yet

- Chapter 4 Ele IDocument16 pagesChapter 4 Ele Ibiruk satnawNo ratings yet

- My Lec MOSFET All F MineDocument25 pagesMy Lec MOSFET All F MineArun JagaNo ratings yet

- Lab5 JFET Characteristics and ApplicationDocument9 pagesLab5 JFET Characteristics and ApplicationMohmmad AlkhaldiNo ratings yet

- AnalogEl 2 FETDocument38 pagesAnalogEl 2 FETAlbert GenceNo ratings yet

- Field Effect TransistorsDocument59 pagesField Effect TransistorsRan QuitNo ratings yet

- Lecture 2.3: FET IntroductionDocument3 pagesLecture 2.3: FET IntroductionAids Sumalde0% (1)

- Vishwas BeeeDocument17 pagesVishwas BeeeyashNo ratings yet

- Exp 5Document5 pagesExp 5MohammedZahidNo ratings yet

- Chapter 5Document10 pagesChapter 5migmakeNo ratings yet

- Notes Module2 (FET Part) Basic Electronics 22BBEE203Document12 pagesNotes Module2 (FET Part) Basic Electronics 22BBEE203Hani MNo ratings yet

- @3 FET FundamentalsDocument210 pages@3 FET Fundamentalschâu nguyễn ngọcNo ratings yet

- Jfet NRP Lecture 2Document97 pagesJfet NRP Lecture 2Nitin PrajapatiNo ratings yet

- Mosfet (Iii) - I-V CharacteristicsDocument11 pagesMosfet (Iii) - I-V Characteristics許博凱No ratings yet

- ElectronicsDocument22 pagesElectronicsVARSHITH REDDY JNo ratings yet

- Feynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterFrom EverandFeynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterNo ratings yet

- Wireless LAN MAC ProtocolsDocument11 pagesWireless LAN MAC ProtocolsChỉnh Nguyễn ThếNo ratings yet

- PowerApps Connectors Reference (PDFDrive)Document2,622 pagesPowerApps Connectors Reference (PDFDrive)Chỉnh Nguyễn Thế100% (1)

- IPv6Security Appendix Devices OverviewDocument2 pagesIPv6Security Appendix Devices OverviewChỉnh Nguyễn ThếNo ratings yet

- IPv6Security CourseIntroDocument1 pageIPv6Security CourseIntroChỉnh Nguyễn ThếNo ratings yet

- Ipv6 Security Training Course: Exercise BookletDocument28 pagesIpv6 Security Training Course: Exercise BookletChỉnh Nguyễn ThếNo ratings yet

- IPv6Security CourseIntroDocument1 pageIPv6Security CourseIntroChỉnh Nguyễn ThếNo ratings yet

- IPv6Security CourseIntroDocument1 pageIPv6Security CourseIntroChỉnh Nguyễn ThếNo ratings yet

- Ipv6 Security Training Course: ReferencesDocument11 pagesIpv6 Security Training Course: ReferencesChỉnh Nguyễn ThếNo ratings yet

- Diodes BJT and FetDocument52 pagesDiodes BJT and FetMadeleine NavarreteNo ratings yet

- FinFET TEchnologiesDocument2 pagesFinFET TEchnologiessurya tejaNo ratings yet

- IRFR/U110A: Advanced Power MOSFETDocument7 pagesIRFR/U110A: Advanced Power MOSFETAbel RodriguezNo ratings yet

- BLHeli Supported Atmel ESCsDocument34 pagesBLHeli Supported Atmel ESCsFly HighNo ratings yet

- Irjet V3i7474 PDFDocument4 pagesIrjet V3i7474 PDFSergiu HălăucăNo ratings yet

- Experiment-1 Aim: VDD=5V VT,n=0.8V VT,p=-0.8V (W/L) p=2.5 (W/L) n=1 Technology=1μ1Document5 pagesExperiment-1 Aim: VDD=5V VT,n=0.8V VT,p=-0.8V (W/L) p=2.5 (W/L) n=1 Technology=1μ1Timir PatelNo ratings yet

- 2SA1357Document2 pages2SA1357Kike VillasurNo ratings yet

- Multisim Act, 3,4,5,6,7 On Electronic Devices Sir MirandaDocument20 pagesMultisim Act, 3,4,5,6,7 On Electronic Devices Sir MirandaKimberly CarreonNo ratings yet

- Soft-Error-Aware Read-Stability-Enhanced Low-Power 12T SRAM With Multi-Node Upset Recoverability For Aerospace ApplicationsDocument11 pagesSoft-Error-Aware Read-Stability-Enhanced Low-Power 12T SRAM With Multi-Node Upset Recoverability For Aerospace ApplicationsZhongpeng LiangNo ratings yet

- ANALOGUE CAT 1 AnswersDocument10 pagesANALOGUE CAT 1 Answersamanda christineNo ratings yet

- Ee 366 Chap 1 3Document10 pagesEe 366 Chap 1 3Michael Adu-boahenNo ratings yet

- Semiconductor Memories: VLSI Design (18EC72)Document11 pagesSemiconductor Memories: VLSI Design (18EC72)PraveenNo ratings yet

- NPN Silicon Epitaxial Planar Transistor: Semtech Electronics LTDDocument2 pagesNPN Silicon Epitaxial Planar Transistor: Semtech Electronics LTDalexjcc10No ratings yet

- DatasheetDocument1 pageDatasheetStuxnetNo ratings yet

- MCQ'S of Digital Vlsi DesignDocument12 pagesMCQ'S of Digital Vlsi Designnayna bhosaleNo ratings yet

- Assignment 1Document2 pagesAssignment 1LJYLowNo ratings yet

- Basic VLSI Design Unit-3Document50 pagesBasic VLSI Design Unit-3N.RAMAKUMARNo ratings yet

- Semiconductor Physics MCQ'SDocument9 pagesSemiconductor Physics MCQ'SGuruKPONo ratings yet

- A Review Paper On CNTFET Technology and Circuit Designing Using CNTFETDocument3 pagesA Review Paper On CNTFET Technology and Circuit Designing Using CNTFETGopi Reddy RanabothuNo ratings yet

- Delta Electronics, IncDocument8 pagesDelta Electronics, IncSasha NaumchenkoNo ratings yet

- Analytical Modeling of Tunneling Field Effect Transistor (TFET)Document22 pagesAnalytical Modeling of Tunneling Field Effect Transistor (TFET)Girdhar Gopal GautamNo ratings yet

- Depletion-Mode: Further Information: andDocument3 pagesDepletion-Mode: Further Information: andshohobiNo ratings yet

- s9013 Tranzistor DatasheetDocument1 pages9013 Tranzistor DatasheetJeno TrutaNo ratings yet

- TransistorsDocument5 pagesTransistorsSyed Fawad AdilNo ratings yet

- DVLSI Lab EXPT1 ManualDocument8 pagesDVLSI Lab EXPT1 ManualApoorvaNo ratings yet

- Electronics Module 3Document18 pagesElectronics Module 3tirsollantada100% (1)

- What Is PNP Transistor - Construction, Working & ApplicationsDocument34 pagesWhat Is PNP Transistor - Construction, Working & ApplicationsgezahegnNo ratings yet

- Silicon NPN Power Transistors: Inchange Semiconductor Product SpecificationDocument4 pagesSilicon NPN Power Transistors: Inchange Semiconductor Product SpecificationNazo FsNo ratings yet

- Bicmos Inverter UploadDocument3 pagesBicmos Inverter UploadHasanAlBannaBhuiyanNo ratings yet

- LDMOSDocument6 pagesLDMOShaseebNo ratings yet