Professional Documents

Culture Documents

Fdp050an06a0 241446

Fdp050an06a0 241446

Uploaded by

ElvisOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Fdp050an06a0 241446

Fdp050an06a0 241446

Uploaded by

ElvisCopyright:

Available Formats

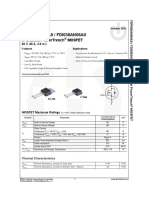

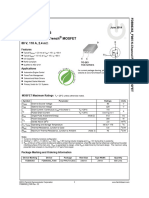

FDP050AN06A0 / FDB050AN06A0 — N-Channel PowerTrench® MOSFET

October 2013

FDP050AN06A0 / FDB050AN06A0

N-Channel PowerTrench® MOSFET

60 V, 80 A, 5 mΩ

Features Applications

• RDS(on) = 4.3 mΩ ( Typ.) @ VGS = 10 V, ID = 80 A • Synchronous Rectification for ATX / Server / Telecom PSU

• QG(tot) = 61 nC ( Typ.) @ VGS = 10 V • Battery Protection Circuit

• Low Miller Charge • Motor drives and Uninterruptible Power Supplies

• Low Qrr Body Diode

• UIS Capability (Single Pulse and Repetitive Pulse)

Formerly developmental type 82575

G

GD G

S TO-220 S D2-PAK

MOSFET Maximum Ratings TC = 25°C unless otherwise noted

Symbol FDP050AN06A0 Unit

Parameter

FDB050AN06A0

V DSS Drain to Source Voltage 60 V

VGS Gate to Source Voltage ±20 V

Drain Current

Continuous (TC < 135oC, VGS = 10V) 80 A

ID

Continuous (TA = 25oC, VGS = 10V, R θJA = 43oC/W) 18 A

Pulsed Figure 4 A

EAS Single Pulse Avalanche Energy (Note 1) 470 mJ

Power dissipation 245 W

PD

Derate above 25oC 1.63 W/oC

o

TJ, TSTG Operating and Storage Temperature -55 to 175 C

Thermal Characteristics

RθJC oC/W

Thermal Resistance Junction to Case, Max. TO-220, D2-PAK 0.61

62 o

RθJA Thermal Resistance Junction to Ambient, Max. TO-220, D2-PAK (Note 2) C/W

o

RθJA Thermal Resistance Junction to Ambient D2-PAK, Max. 1in2 copper pad area 43 C/W

©2003 Fairchild Semiconductor Corporation 1 www.fairchildsemi.com

FDP050AN06A0 / FDB050AN06A0 Rev. C2

FDP050AN06A0 / FDB050AN06A0 — N-Channel PowerTrench® MOSFET

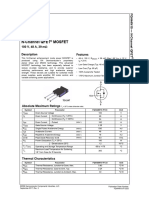

Package Marking and Ordering Information

Device Marking Device Package Reel Size Tape Width Quantity

FDB050AN06A0 FDB050AN06A0 D2-PAK 330 mm 24 mm 800 units

FDP050AN06A0 FDP050AN06A0 TO-220 Tube N/A 50 units

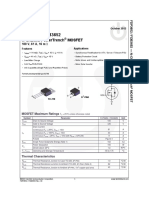

Electrical Characteristics TC = 25°C unless otherwise noted

Symbol Parameter Test Conditions Min Typ Max Unit

Off Characteristics

B VDSS Drain to Source Breakdown Voltage ID = 250µA, VGS = 0V 60 - - V

V DS = 50V - - 1

IDSS Zero Gate Voltage Drain Current µA

VGS = 0V TC = 150oC - - 250

IGSS Gate to Source Leakage Current VGS = ±20V - - ±100 nA

On Characteristics

VGS(TH) Gate to Source Threshold Voltage VGS = VDS, ID = 250µA 2 - 4 V

ID = 80A, VGS = 10V - 0.0043 0.005

ID = 40A, VGS = 6V - 0.007 0.011

rDS(ON) Drain to Source On Resistance Ω

ID = 80A, VGS = 10V,

- 0.0085 0.010

TJ = 175oC

Dynamic Characteristics

CISS Input Capacitance - 3900 - pF

V DS = 25V, VGS = 0V,

COSS Output Capacitance - 750 - pF

f = 1MHz

CRSS Reverse Transfer Capacitance - 270 - pF

Qg(TOT) Total Gate Charge at 10V VGS = 0V to 10V 61 80 nC

Qg(TH) Threshold Gate Charge VGS = 0V to 2V VDD = 30V - 8 11 nC

Qgs Gate to Source Gate Charge ID = 80A - 24 - nC

Qgs2 Gate Charge Threshold to Plateau Ig = 1.0mA - 16 - nC

Qgd Gate to Drain “Miller” Charge - 15 - nC

Switching Characteristics (VGS = 10V)

tON Turn-On Time - - 264 ns

td(ON) Turn-On Delay Time - 16 - ns

tr Rise Time V DD = 30V, ID = 80A - 160 - ns

td(OFF) Turn-Off Delay Time V GS = 10V, RGS = 4.3Ω - 28 - ns

tf Fall Time - 29 - ns

tOFF Turn-Off Time - - 86 ns

Drain-Source Diode Characteristics

ISD = 80A - - 1.25 V

V SD Source to Drain Diode Voltage

ISD = 40A - - 1.0 V

trr Reverse Recovery Time ISD = 75A, dISD/dt = 100A/µs - - 34 ns

QRR Reverse Recovered Charge ISD = 75A, dISD/dt = 100A/µs - - 25 nC

Notes:

1: Starting TJ = 25°C, L = 229µH, IAS = 64A.

2: Pulse width = 100s.

©2003 Fairchild Semiconductor Corporation 2 www.fairchildsemi.com

FDP050AN06A0 / FDB050AN06A0 Rev. C2

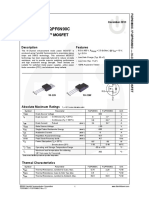

FDP050AN06A0 / FDB050AN06A0 — N-Channel PowerTrench® MOSFET

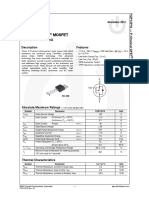

Typical Characteristics TC = 25°C unless otherwise noted

1.2 160

CURRENT LIMITED

BY PACKAGE

1.0

POWER DISSIPATION MULTIPLIER

ID, DRAIN CURRENT (A)

120

0.8

0.6 80

0.4

40

0.2

0 0

0 25 50 75 100 125 150 175 25 50 75 100 125 150 175

TC , CASE TEMPERATURE (o C) TC, CASE TEMPERATURE (oC)

Figure 1. Normalized Power Dissipation vs Figure 2. Maximum Continuous Drain Current vs

Ambient Temperature Case Temperature

2

DUTY CYCLE - DESCENDING ORDER

1 0.5

0.2

0.1

0.05

THERMAL IMPEDANCE

ZθJC, NORMALIZED

0.02

0.01

PDM

0.1

t1

t2

NOTES:

DUTY FACTOR: D = t1/t2

SINGLE PULSE PEAK TJ = PDM x ZθJC x RθJC + TC

0.01

10-5 10-4 10-3 10-2 10-1 100 101

t , RECTANGULAR PULSE DURATION (s)

Figure 3. Normalized Maximum Transient Thermal Impedance

2000

TC = 25oC

FOR TEMPERATURES

1000 ABOVE 25oC DERATE PEAK

IDM, PEAK CURRENT (A)

CURRENT AS FOLLOWS:

I = I25 175 - TC

VGS = 10V

150

TRANSCONDUCTANCE

MAY LIMIT CURRENT

IN THIS REGION

100

50

10-5 10-4 10-3 10-2 10-1 100 101

t, PULSE WIDTH (s)

Figure 4. Peak Current Capability

©2003 Fairchild Semiconductor Corporation 3 www.fairchildsemi.com

FDP050AN06A0 / FDB050AN06A0 Rev. C2

FDP050AN06A0 / FDB050AN06A0 — N-Channel PowerTrench® MOSFET

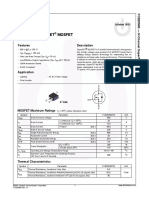

Typical Characteristics TC = 25°C unless otherwise noted

1000 500

If R = 0

10µs tAV = (L)(I AS)/(1.3*RATED BVDSS - VDD)

If R ≠ 0

IAS, AVALANCHE CURRENT (A)

100µs tAV = (L/R)ln[(IAS*R)/(1.3*RATED BVDSS - VDD) +1]

100 100

ID, DRAIN CURRENT (A)

1ms

OPERATION IN THIS STARTING TJ = 25oC

AREA MAY BE 10ms

10

LIMITED BY rDS(ON)

10

DC

1

SINGLE PULSE STARTING TJ = 150 oC

TJ = MAX RATED

TC = 25oC

0.1 1

1 10 100 0.01 0.1 1 10 100

VDS, DRAIN TO SOURCE VOLTAGE (V) tAV, TIME IN AVALANCHE (ms)

Figure 5. Forward Bias Safe Operating Area NOTE: Refer to Fairchild Application Notes AN7514 and AN7515

Figure 6. Unclamped Inductive Switching

Capability

160 160

PULSE DURATION = 80µs

DUTY CYCLE = 0.5% MAX VGS = 7V

VDD = 15V VGS = 10V VGS = 6V

120 120

ID, DRAIN CURRENT (A)

ID, DRAIN CURRENT (A)

80 80

TJ = 175oC

TJ = 25o C VGS = 5V

40 40

TC = 25oC

TJ = -55oC PULSE DURATION = 80µs

DUTY CYCLE = 0.5% MAX

0 0

0 0.5 1.0 1.5

4.0 4.5 5.0 5.5 6.0

VGS , GATE TO SOURCE VOLTAGE (V) VDS , DRAIN TO SOURCE VOLTAGE (V)

Figure 7. Transfer Characteristics Figure 8. Saturation Characteristics

8 2.0

PULSE DURATION = 80µs

DRAIN TO SOURCE ON RESISTANCE(mΩ)

PULSE DURATION = 80µs

DUTY CYCLE = 0.5% MAX VGS = 6V DUTY CYCLE = 0.5% MAX

NORMALIZED DRAIN TO SOURCE

7

ON RESISTANCE

1.5

1.0

5

VGS = 10V

VGS = 10V, ID =80A

4

0.5

0 20 40 60 80

-80 -40 0 40 80 120 160 200

ID, DRAIN CURRENT (A) TJ, JUNCTION TEMPERATURE (oC)

Figure 9. Drain to Source On Resistance vs Drain Figure 10. Normalized Drain to Source On

Current Resistance vs Junction Temperature

©2003 Fairchild Semiconductor Corporation 4 www.fairchildsemi.com

FDP050AN06A0 / FDB050AN06A0 Rev. C2

FDP050AN06A0 / FDB050AN06A0 — N-Channel PowerTrench® MOSFET

Typical Characteristics TC = 25°C unless otherwise noted

1.4 1.15

VGS = VDS, ID = 250µA ID = 250µA

NORMALIZED DRAIN TO SOURCE

1.2 1.10

THRESHOLD VOLTAGE

BREAKDOWN VOLTAGE

NORMALIZED GATE

1.0 1.05

0.8 1.00

0.6 0.95

0.4

0.90

-80 -40 0 40 80 120 160 200

-80 -40 0 40 80 120 160 200

TJ, JUNCTION TEMPERATURE (oC) TJ , JUNCTION TEMPERATURE (oC)

Figure 11. Normalized Gate Threshold Voltage vs Figure 12. Normalized Drain to Source

Junction Temperature Breakdown Voltage vs Junction Temperature

10000 10

VDD = 30V

CISS = CGS + CGD

VGS , GATE TO SOURCE VOLTAGE (V)

8

C, CAPACITANCE (pF)

COSS ≅ CDS + CGD

6

1000

CRSS = CGD

4

WAVEFORMS IN

2 DESCENDING ORDER:

ID = 80A

VGS = 0V, f = 1MHz ID = 18A

100 0

0.1 1 10 60 0 10 20 30 40 50 60 70

VDS , DRAIN TO SOURCE VOLTAGE (V) Qg, GATE CHARGE (nC)

Figure 13. Capacitance vs Drain to Source Figure 14. Gate Charge Waveforms for Constant

Voltage Gate Current

©2003 Fairchild Semiconductor Corporation 5 www.fairchildsemi.com

FDP050AN06A0 / FDB050AN06A0 Rev. C2

FDP050AN06A0 / FDB050AN06A0 — N-Channel PowerTrench® MOSFET

Test Circuits and Waveforms

VDS

BVDSS

L tP

VDS

VARY tP TO OBTAIN IAS

+

VDD

REQUIRED PEAK IAS RG

VDD

VGS -

DUT

tP

0V IAS

0.01Ω 0

tAV

Figure 15. Unclamped Energy Test Circuit Figure 16. Unclamped Energy Waveforms

VDS

VDD Qg(TOT)

L VDS

VGS

VGS = 10V

VGS +

VDD Qgs2

-

DUT

VGS = 2V

Ig(REF)

0

Qg(TH)

Qgs Qgd

Ig(REF)

0

Figure 17. Gate Charge Test Circuit Figure 18. Gate Charge Waveforms

VDS tON tOFF

td(ON) td(OFF)

RL tr tf

VDS

90% 90%

+

VGS

VDD

10% 10%

- 0

DUT 90%

RGS

VGS 50% 50%

PULSE WIDTH

VGS 10%

0

Figure 19. Switching Time Test Circuit Figure 20. Switching Time Waveforms

©2003 Fairchild Semiconductor Corporation 6 www.fairchildsemi.com

FDP050AN06A0 / FDB050AN06A0 Rev. C2

FDP050AN06A0 / FDB050AN06A0 — N-Channel PowerTrench® MOSFET

Thermal Resistance vs. Mounting Pad Area

The maximum rated junction temperature, TJM , and the 80

thermal resistance of the heat dissipating path determines RθJA = 26.51+ 19.84/(0.262+Area) EQ.2

the maximum allowable device power dissipation, PDM , in an

application. Therefore the application’s ambient RθJA = 26.51+ 128/(1.69+Area) EQ.3

temperature, TA (oC), and thermal resistance RθJA (oC/W)

60

must be reviewed to ensure that TJM is never exceeded.

RθJA (o C/W)

Equation 1 mathematically represents the relationship and

serves as the basis for establishing the rating of the part.

(T –T )

JM A (EQ. 1) 40

P D M = -----------------------------

R θ JA

In using surface mount devices such as the TO-263

package, the environment in which it is applied will have a 20

significant influence on the part’s current and maximum 0.1 1 10

power dissipation ratings. Precise determination of P DM is (0.645) (6.45) (64.5)

complex and influenced by many factors: AREA, TOP COPPER AREA in2 (cm2 )

Figure 21. Thermal Resistance vs Mounting

1. Mounting pad area onto which the device is attached and Pad Area

whether there is copper on one side or both sides of the

board.

2. The number of copper layers and the thickness of the

board.

3. The use of external heat sinks.

4. The use of thermal vias.

5. Air flow and board orientation.

6. For non steady state applications, the pulse width, the

duty cycle and the transient thermal response of the part,

the board and the environment they are in.

Fairchild provides thermal information to assist the

designer’s preliminary application evaluation. Figure 21

defines the RθJA for the device as a function of the top

copper (component side) area. This is for a horizontally

positioned FR-4 board with 1oz copper after 1000 seconds

of steady state power with no air flow. This graph provides

the necessary information for calculation of the steady state

junction temperature or power dissipation. Pulse

applications can be evaluated using the Fairchild device

Spice thermal model or manually utilizing the normalized

maximum transient thermal impedance curve.

Thermal resistances corresponding to other copper areas

can be obtained from Figure 21 or by calculation using

Equation 2 or 3. Equation 2 is used for copper area defined

in inches square and equation 3 is for area in centimeters

square. The area, in square inches or square centimeters is

the top copper area including the gate and source pads.

R

19.84

= 26.51 + -------------------------------------

θ JA (EQ. 2)

( 0.262 + Area )

Area in Inches Squared

R

128

= 26.51 + ----------------------------------

θ JA (EQ. 3)

( 1.69 + Area )

Area in Centimeters Squared

©2003 Fairchild Semiconductor Corporation 7 www.fairchildsemi.com

FDP050AN06A0 / FDB050AN06A0 Rev. C2

FDP050AN06A0 / FDB050AN06A0 — N-Channel PowerTrench® MOSFET

PSPICE Electrical Model

.SUBCKT FDB050AN06A0 2 1 3 ; rev February 2003

Ca 12 8 1.5e-9

Cb 15 14 1.5e-9 LDRAIN

Cin 6 8 3.75e-9 DPLCAP 5 DRAIN

2

10

Dbody 7 5 DbodyMOD RLDRAIN

RSLC1

Dbreak 5 11 DbreakMOD DBREAK

51

Dplcap 10 5 DplcapMOD RSLC2

+

5

51 ESLC 11

Ebreak 11 7 17 18 64.8 -

Eds 14 8 5 8 1 50 +

-

Egs 13 8 6 8 1 RDRAIN 17 DBODY

6 EBREAK 18

Esg 6 10 6 8 1 ESG 8

EVTHRES -

Evthres 6 21 19 8 1 + 16

+ 19 - 21

Evtemp 20 6 18 22 1 LGATE EVTEMP MWEAK

8

GATE RGATE + 18 - 6

It 8 17 1 1 22 MMED

9 20

RLGATE MSTRO

Lgate 1 9 4.7e-9 LSOURCE

CIN SOURCE

Ldrain 2 5 1.0e-9 8 7 3

Lsource 3 7 4.03e-9

RSOURCE

RLSOURCE

RLgate 1 9 47 S1A S2A

RLdrain 2 5 10 12 RBREAK

13 14 15

17 18

RLsource 3 7 40 8 13

S1B S2B RVTEMP

Mmed 16 6 8 8 MmedMOD 13 CB 19

Mstro 16 6 8 8 MstroMOD CA

14 IT -

+ +

Mweak 16 21 8 8 MweakMOD 6 5 VBAT

EGS EDS +

8 8

Rbreak 17 18 RbreakMOD 1 - - 8

Rdrain 50 16 RdrainMOD 1.1e-3 22

Rgate 9 20 1.3 RVTHRES

RSLC1 5 51 RSLCMOD 1e-6

RSLC2 5 50 1e3

Rsource 8 7 RsourceMOD 2.1e-3

Rvthres 22 8 RvthresMOD 1

Rvtemp 18 19 RvtempMOD 1

S1a 6 12 13 8 S1AMOD

S1b 13 12 13 8 S1BMOD

S2a 6 15 14 13 S2AMOD

S2b 13 15 14 13 S2BMOD

Vbat 22 19 DC 1

ESLC 51 50 VALUE={(V(5,51)/ABS(V(5,51)))*(PWR(V(5,51)/(1e-6*250),10))}

.MODEL DbodyMOD D (IS=1.3E-11 N=1.04 RS=1.76e-3 TRS1=2.7e-3 TRS2=2e-7

+ CJO=2.7e-9 M=5.4e-1 TT=1e-10 XTI=3.9)

.MODEL DbreakMOD D (RS=8e-1 TRS1=5e-4 TRS2=-8.9e-6)

.MODEL DplcapMOD D (CJO=1.3e-9 IS=1e-30 N=10 M=0.45)

.MODEL MmedMOD NMOS (VTO=3.7 KP=9 IS=1e-30 N=10 TOX=1 L=1u W=1u RG=1.3)

.MODEL MstroMOD NMOS (VTO=4.29 KP=155 IS=1e-30 N=10 TOX=1 L=1u W=1u)

.MODEL MweakMOD NMOS (VTO=3.05 KP=0.03 IS=1e-30 N=10 TOX=1 L=1u W=1u RG=13 RS=0.1)

.MODEL RbreakMOD RES (TC1=9.3e-4 TC2=-5.5e-7)

.MODEL RdrainMOD RES (TC1=1.3e-2 TC2=4e-5)

.MODEL RSLCMOD RES (TC1=1e-3 TC2=1e-5)

.MODEL RsourceMOD RES (TC1=1e-3 TC2=1e-6)

.MODEL RvthresMOD RES (TC1=-5.8e-3 TC2=-1.4e-5)

.MODEL RvtempMOD RES (TC1=-2.8e-3 TC2=1e-6)

.MODEL S1AMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-4 VOFF=-2)

.MODEL S1BMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-2 VOFF=-4)

.MODEL S2AMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-1.5 VOFF=0.5)

.MODEL S2BMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=0.5 VOFF=-1.5)

.ENDS

Note: For further discussion of the PSPICE model, consult A New PSPICE Sub-Circuit for the Power MOSFET Featuring Global

Temperature Options; IEEE Power Electronics Specialist Conference Records, 1991, written by William J. Hepp and C. Frank

Wheatley.

©2003 Fairchild Semiconductor Corporation 8 www.fairchildsemi.com

FDP050AN06A0 / FDB050AN06A0 Rev. C2

FDP050AN06A0 / FDB050AN06A0 — N-Channel PowerTrench® MOSFET

SABER Electrical Model

rev February 2003

template FDB050AN06A0 n2,n1,n3

electrical n2,n1,n3

{

var i iscl

dp..model dbodymod = (isl=1.3e-11,nl=1.04,rs=1.76e-3,trs1=2.7e-3,trs2=2e-7,cjo=2.7e-9,m=5.4e-1,tt=1e-10,xti=3.9)

dp..model dbreakmod = (rs=8e-1,trs1=5e-4,trs2=-8.9e-6)

dp..model dplcapmod = (cjo=1.3e-9,isl=10e-30,nl=10,m=0.45)

m..model mmedmod = (type=_n,vto=3.7,kp=9,is=1e-30, tox=1)

m..model mstrongmod = (type=_n,vto=4.29,kp=155,is=1e-30, tox=1)

m..model mweakmod = (type=_n,vto=3.05,kp=0.03,is=1e-30, tox=1,rs=0.1)

LDRAIN

sw_vcsp..model s1amod = (ron=1e-5,roff=0.1,von=-4,voff=-2) DPLCAP 5 DRAIN

sw_vcsp..model s1bmod = (ron=1e-5,roff=0.1,von=-2,voff=-4) 2

sw_vcsp..model s2amod = (ron=1e-5,roff=0.1,von=-1.5,voff=0.5) 10

RLDRAIN

sw_vcsp..model s2bmod = (ron=1e-5,roff=0.1,von=0.5,voff=-1.5) RSLC1

c.ca n12 n8 = 1.5e-9 51

RSLC2

c.cb n15 n14 = 1.5e-9

c.cin n6 n8 = 3.75e-9 ISCL

50 DBREAK

dp.dbody n7 n5 = model=dbodymod -

6 RDRAIN

dp.dbreak n5 n11 = model=dbreakmod ESG 11

8 DBODY

dp.dplcap n10 n5 = model=dplcapmod + EVTHRES 16

+ 19 - 21

LGATE EVTEMP MWEAK

spe.ebreak n11 n7 n17 n18 = 64.8 8

GATE RGATE + 18 - 6

spe.eds n14 n8 n5 n8 = 1 1 MMED EBREAK

9 22 +

spe.egs n13 n8 n6 n8 = 1 20

MSTRO

RLGATE 17

spe.esg n6 n10 n6 n8 = 1 18 LSOURCE

spe.evthres n6 n21 n19 n8 = 1 CIN - SOURCE

8 7

spe.evtemp n20 n6 n18 n22 = 1 3

RSOURCE

RLSOURCE

i.it n8 n17 = 1

S1A S2A

12 RBREAK

13 14 15

l.lgate n1 n9 = 4.7e-9 17 18

8 13

l.ldrain n2 n5 = 1.0e-9

l.lsource n3 n7 = 4.03e-9 S1B S2B RVTEMP

13 CB 19

CA

14 IT -

res.rlgate n1 n9 = 47 + +

res.rldrain n2 n5 = 10 6 5 VBAT

EGS 8 EDS 8 +

res.rlsource n3 n7 = 40

- - 8

22

m.mmed n16 n6 n8 n8 = model=mmedmod, l=1u, w=1u RVTHRES

m.mstrong n16 n6 n8 n8 = model=mstrongmod, l=1u, w=1u

m.mweak n16 n21 n8 n8 = model=mweakmod, l=1u, w=1u

res.rbreak n17 n18 = 1, tc1=9.3e-4,tc2=-5.5e-7

res.rdrain n50 n16 = 1.1e-3, tc1=1.3e-2,tc2=4e-5

res.rgate n9 n20 = 1.3

res.rslc1 n5 n51 = 1e-6, tc1=1e-3,tc2=1e-5

res.rslc2 n5 n50 = 1e3

res.rsource n8 n7 = 2.1e-3, tc1=1e-3,tc2=1e-6

res.rvthres n22 n8 = 1, tc1=-5.8e-3,tc2=-1.4e-5

res.rvtemp n18 n19 = 1, tc1=-2.8e-3,tc2=1e-6

sw_vcsp.s1a n6 n12 n13 n8 = model=s1amod

sw_vcsp.s1b n13 n12 n13 n8 = model=s1bmod

sw_vcsp.s2a n6 n15 n14 n13 = model=s2amod

sw_vcsp.s2b n13 n15 n14 n13 = model=s2bmod

v.vbat n22 n19 = dc=1

equations {

i (n51->n50) +=iscl

iscl: v(n51,n50) = ((v(n5,n51)/(1e-9+abs(v(n5,n51))))*((abs(v(n5,n51)*1e6/250))** 10))

}

}

©2003 Fairchild Semiconductor Corporation 9 www.fairchildsemi.com

FDP050AN06A0 / FDB050AN06A0 Rev. C2

FDP050AN06A0 / FDB050AN06A0 — N-Channel PowerTrench® MOSFET

SPICE Thermal Model

th JUNCTION

REV 23 February 2003

FDB050AN06A0T

CTHERM1 TH 6 5e-3

CTHERM2 6 5 1.3e-2

CTHERM3 5 4 1.4e-2 RTHERM1 CTHERM1

CTHERM4 4 3 1.9e-2

CTHERM5 3 2 4.7e-2

CTHERM6 2 TL 9e-2

6

RTHERM1 TH 6 1e-2

RTHERM2 6 5 3.1e-2

RTHERM3 5 4 4.5e-2

RTHERM2 CTHERM2

RTHERM4 4 3 1.2e-1

RTHERM5 3 2 1.3e-1

RTHERM6 2 TL 1.52e-1

5

SABER Thermal Model

SABER thermal model FDB050AN06A0T

template thermal_model th tl RTHERM3 CTHERM3

thermal_c th, tl

{

ctherm.ctherm1 th 6 =5e-3

4

ctherm.ctherm2 6 5 =1.3e-2

ctherm.ctherm3 5 4 =1.4e-2

ctherm.ctherm4 4 3 =1.9e-2

ctherm.ctherm5 3 2 =4.7e-2 RTHERM4 CTHERM4

ctherm.ctherm6 2 tl =9e-2

rtherm.rtherm1 th 6 =1e-2

rtherm.rtherm2 6 5 =3.1e-2 3

rtherm.rtherm3 5 4 =4.5e-2

rtherm.rtherm4 4 3 =1.2e-1

rtherm.rtherm5 3 2 =1.3e-1

RTHERM5 CTHERM5

rtherm.rtherm6 2 tl =1.52e-1

}

RTHERM6 CTHERM6

tl CASE

©2003 Fairchild Semiconductor Corporation 10 www.fairchildsemi.com

FDP050AN06A0 / FDB050AN06A0 Rev. C2

FDP050AN06A0 / FDB050AN06A0 — N-Channel PowerTrench® MOSFET

Mechanical Dimensions

TO-220 3L

Figure 22. TO-220, Molded, 3Lead, Jedec Variation AB

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specif-

ically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/package/packageDetails.html?id=PN_TT220-003

Dimension in Millimeters

©2003 Fairchild Semiconductor Corporation 11 www.fairchildsemi.com

FDP050AN06A0 / FDB050AN06A0 Rev. C2

FDP050AN06A0 / FDB050AN06A0 — N-Channel PowerTrench® MOSFET

Mechanical Dimensions

TO-263 2L (D2PAK)

Figure 23. 2LD, TO263, Surface Mount

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specif-

ically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/package/packageDetails.html?id=PN_TT263-002

Dimension in Millimeters

©2003 Fairchild Semiconductor Corporation 12 www.fairchildsemi.com

FDP050AN06A0 / FDB050AN06A0 Rev. C2

FDP050AN06A0 / FDB050AN06A0 — N-Channel PowerTrench® MOSFET

TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not

intended to be an exhaustive list of all such trademarks.

AccuPower™ F-PFS™ Sync-Lock™

AX-CAP®* FRFET® ® tm

®*

SM ®

BitSiC™ Global Power Resource PowerTrench

Build it Now™ GreenBridge™ PowerXS™

TinyBoost®

CorePLUS™ Green FPS™ Programmable Active Droop™

® TinyBuck®

CorePOWER™ Green FPS™ e-Series™ QFET

TinyCalc™

CROSSVOLT™ Gmax™ QS™

TinyLogic®

CTL™ GTO™ Quiet Series™

TINYOPTO™

Current Transfer Logic™ IntelliMAX™ RapidConfigure™

TinyPower™

DEUXPEED® ISOPLANAR™ ™ TinyPWM™

Dual Cool™ Marking Small Speakers Sound Louder

TinyWire™

EcoSPARK® and Better™ Saving our world, 1mW/W/kW at a time™

TranSiC™

EfficentMax™ MegaBuck™ SignalWise™

TriFault Detect™

ESBC™ MICROCOUPLER™ SmartMax™

TRUECURRENT®*

® MicroFET™ SMART START™

SerDes™

MicroPak™ Solutions for Your Success™

Fairchild® MicroPak2™ SPM®

Fairchild Semiconductor® MillerDrive™ STEALTH™

MotionMax™ SuperFET® UHC®

FACT Quiet Series™

mWSaver ® SuperSOT™-3 Ultra FRFET™

FACT®

OptoHiT™ SuperSOT™-6 UniFET™

FAST®

OPTOLOGIC® SuperSOT™-8 VCX™

FastvCore™

OPTOPLANAR® SupreMOS® VisualMax™

FETBench™

SyncFET™ VoltagePlus™

FPS™

XS™

*Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE

RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY

PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY

THEREIN, WHICH COVERS THESE PRODUCTS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE

EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used here in:

1. Life support devices or systems are devices or systems which, (a) are 2. A critical component in any component of a life support, device, or

intended for surgical implant into the body or (b) support or sustain life, system whose failure to perform can be reasonably expected to cause

and (c) whose failure to perform when properly used in accordance with the failure of the life support device or system, or to affect its safety or

instructions for use provided in the labeling, can be reasonably effectiveness.

expected to result in a significant injury of the user.

ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation’s Anti-Counterfeiting Policy. Fairchild’s Anti-Counterfeiting Policy is also stated on our external website,

www.Fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufactures of semiconductor products are experiencing counterfeiting of their

parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed

application, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the

proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild

Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild

Distributors are genuine parts, have full traceability, meet Fairchild’s quality standards for handing and storage and provide access to Fairchild’s full range of

up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address and

warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is

committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Datasheet contains the design specifications for product development. Specifications

Advance Information Formative / In Design

may change in any manner without notice.

Datasheet contains preliminary data; supplementary data will be published at a later

Preliminary First Production date. Fairchild Semiconductor reserves the right to make changes at any time without

notice to improve design.

Datasheet contains final specifications. Fairchild Semiconductor reserves the right to

No Identification Needed Full Production

make changes at any time without notice to improve the design.

Datasheet contains specifications on a product that is discontinued by Fairchild

Obsolete Not In Production

Semiconductor. The datasheet is for reference information only.

Rev. I66

©2003 Fairchild Semiconductor Corporation 13 www.fairchildsemi.com

FDP050AN06A0 / FDB050AN06A0 Rev. C2

Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Fairchild Semiconductor:

FDP050AN06A0

You might also like

- MOS MemoryDocument53 pagesMOS Memoryskh_1987100% (1)

- Fdp038An06A0 / Fdi038An06A0: N-Channel Powertrench MosfetDocument12 pagesFdp038An06A0 / Fdi038An06A0: N-Channel Powertrench Mosfetdani pedroNo ratings yet

- Fdp3652 / Fdb3652: N-Channel Powertrench MosfetDocument14 pagesFdp3652 / Fdb3652: N-Channel Powertrench Mosfethalil ibrahim soysalNo ratings yet

- FDP 5800Document8 pagesFDP 5800Khalid JakirNo ratings yet

- Fdb2532 - F085: N-Channel Powertrench Mosfet 150V, 79A, 16MDocument11 pagesFdb2532 - F085: N-Channel Powertrench Mosfet 150V, 79A, 16MSukandar TeaNo ratings yet

- Aot4n60 Aotf4n60 Aotf4n60lDocument9 pagesAot4n60 Aotf4n60 Aotf4n60lCamilo JuniorNo ratings yet

- IRFB4610 IRFS4610 IRFSL4610: V 100V R Typ. 11m Max. 14m I 73ADocument11 pagesIRFB4610 IRFS4610 IRFSL4610: V 100V R Typ. 11m Max. 14m I 73ATomi OzzyNo ratings yet

- AOT12N50/AOB12N50/AOTF12N50: General Description Product SummaryDocument6 pagesAOT12N50/AOB12N50/AOTF12N50: General Description Product SummaryEdson Guimarães SobrinhoNo ratings yet

- FDP20N50 184794Document11 pagesFDP20N50 184794Paulo NogueiraNo ratings yet

- FDP8443Document7 pagesFDP8443Semut criminalsNo ratings yet

- MDF7N60BDocument8 pagesMDF7N60BFreddyNo ratings yet

- Irfb 4115 PBFDocument7 pagesIrfb 4115 PBFEdi ChanNo ratings yet

- FQPF6N90CDocument8 pagesFQPF6N90CMoises de Oliveira BastosNo ratings yet

- FDPA Programing1231Document10 pagesFDPA Programing1231Engr. Syed Ghulam Mustafa ShahNo ratings yet

- Fta02n60c FTP02N60CDocument9 pagesFta02n60c FTP02N60Csquirrel1969No ratings yet

- FQP10N60-FQPF10N60: General Description Product SummaryDocument7 pagesFQP10N60-FQPF10N60: General Description Product SummaryVuksanov ZarkoNo ratings yet

- Tmp10n60a Tmpf10n60a PDFDocument7 pagesTmp10n60a Tmpf10n60a PDFUncle PaneNo ratings yet

- FTP04N60D Fta04n60dDocument9 pagesFTP04N60D Fta04n60dgigiNo ratings yet

- FQP12P10: P-Channel QFET MosfetDocument8 pagesFQP12P10: P-Channel QFET MosfetCrdz LouisNo ratings yet

- FDP20N50FDocument10 pagesFDP20N50Ftplink.gtzrojasNo ratings yet

- Fdp3651U N-Channel Powertrench Mosfet: 100V, 80A, 15M Features ApplicationsDocument6 pagesFdp3651U N-Channel Powertrench Mosfet: 100V, 80A, 15M Features ApplicationsAli R.MNo ratings yet

- Unisonic Technologies Co., LTD: 15A, 600V N-CHANNEL Power MosfetDocument6 pagesUnisonic Technologies Co., LTD: 15A, 600V N-CHANNEL Power MosfetCode Main ProjectNo ratings yet

- N-Channel Low QG Mosfet 30V, 100A, 3.3m: MOS-TECH Semiconductor Co.,LTDDocument9 pagesN-Channel Low QG Mosfet 30V, 100A, 3.3m: MOS-TECH Semiconductor Co.,LTDAnonymous p1ig0zX6p0No ratings yet

- AOT20N60/AOTF20N60: General Description Product SummaryDocument6 pagesAOT20N60/AOTF20N60: General Description Product SummaryKrasimir MalamovNo ratings yet

- FQPF8N60C-tv Mosfet OriginalDocument9 pagesFQPF8N60C-tv Mosfet OriginalFerhat QweNo ratings yet

- HY27UF084G2B HynixSemiconductorDocument7 pagesHY27UF084G2B HynixSemiconductorDrew AlbaneseNo ratings yet

- MDF13N50: N-Channel MOSFET 500V, 13.0 A, 0.5Document6 pagesMDF13N50: N-Channel MOSFET 500V, 13.0 A, 0.5Moroșan CristiNo ratings yet

- FQP10N20C / FQPF10N20C: N-Channel QFET MosfetDocument10 pagesFQP10N20C / FQPF10N20C: N-Channel QFET MosfethenriquegonferNo ratings yet

- Rev.D Nov.-2016: 描述 / DescriptionsDocument6 pagesRev.D Nov.-2016: 描述 / Descriptionsfuad64No ratings yet

- Fcb20N60: N-Channel Superfet MosfetDocument9 pagesFcb20N60: N-Channel Superfet MosfetEo GpNo ratings yet

- FQD7P06: P-Channel QFET MosfetDocument9 pagesFQD7P06: P-Channel QFET MosfetIsela LopezNo ratings yet

- MDF9N50F MagnaChipDocument6 pagesMDF9N50F MagnaChipchokNo ratings yet

- Unisonic Technologies Co., LTD: 800V N-Channel Power MosfetDocument6 pagesUnisonic Technologies Co., LTD: 800V N-Channel Power MosfetEisenhower Garcia LealNo ratings yet

- Fdb86363 - F085: N-Channel Powertrench MosfetDocument6 pagesFdb86363 - F085: N-Channel Powertrench MosfetNobreak ServiceNo ratings yet

- AP3N1R8MT-L Datasheet PackageDocument8 pagesAP3N1R8MT-L Datasheet Packageviktor ivanovNo ratings yet

- FDD8880Document11 pagesFDD8880DannyNo ratings yet

- Fds8880 N-Channel Powertrench: MosfetDocument12 pagesFds8880 N-Channel Powertrench: MosfetDavid J. Pinto ApazaNo ratings yet

- Fcp190N60 / Fcpf190N60: N-Channel Superfet Ii MosfetDocument10 pagesFcp190N60 / Fcpf190N60: N-Channel Superfet Ii Mosfetarness22No ratings yet

- Data SheetDocument8 pagesData SheetSuyash SuyashNo ratings yet

- AP9T15GHDocument4 pagesAP9T15GHJose M PeresNo ratings yet

- Ap4n2r1mt V1Document6 pagesAp4n2r1mt V1Mar GaoNo ratings yet

- MDF10N60G 1Document6 pagesMDF10N60G 1samvick103No ratings yet

- B 812 Cfa 38Document8 pagesB 812 Cfa 38Sajid AliNo ratings yet

- ITA08N60ADocument9 pagesITA08N60AAljosha TurzaNo ratings yet

- SLP4N60C/SLF4N60C: 600V N-Channel MOSFETDocument7 pagesSLP4N60C/SLF4N60C: 600V N-Channel MOSFETmiler2011No ratings yet

- FDPF035N06B FairchildSemiconductorDocument10 pagesFDPF035N06B FairchildSemiconductorALWHBANY Learn TermuxNo ratings yet

- Fdd9407L - F085: N-Channel Logic Level Powertrench MosfetDocument7 pagesFdd9407L - F085: N-Channel Logic Level Powertrench Mosfetonis1 onis1No ratings yet

- Irfb4115Gpbf: V 150V R Typ. 9.3M Max. 11M I 104ADocument8 pagesIrfb4115Gpbf: V 150V R Typ. 9.3M Max. 11M I 104AHuutinh LeNo ratings yet

- Irf 634 BDocument8 pagesIrf 634 BAhmed ShagidullinNo ratings yet

- Mosfet FQP50N06 60V - 50a PDFDocument8 pagesMosfet FQP50N06 60V - 50a PDFGiraldoCarpioRamosNo ratings yet

- AP0503GMT-HF DatasheetDocument4 pagesAP0503GMT-HF DatasheetAisya NurcahyaNo ratings yet

- FQPF7N80C FQPF7N80CDocument12 pagesFQPF7N80C FQPF7N80Cmadeline cruzata downerNo ratings yet

- N-Channel Powertrench Mosfet: 30V, 8.5A, 23M General Descriptions FeaturesDocument6 pagesN-Channel Powertrench Mosfet: 30V, 8.5A, 23M General Descriptions FeaturesjokophpNo ratings yet

- 3N80Document6 pages3N80hectorsevillaNo ratings yet

- Irfp 3206 PBFDocument8 pagesIrfp 3206 PBFroberto-741945No ratings yet

- Unisonic Technologies Co., LTD: 15A, 300V N-CHANNEL Power MosfetDocument6 pagesUnisonic Technologies Co., LTD: 15A, 300V N-CHANNEL Power MosfetaboaltaemrrNo ratings yet

- 6N90C Mosfet N PDFDocument10 pages6N90C Mosfet N PDFHưng HQNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- FSFR1800Document17 pagesFSFR1800sontuyet82No ratings yet

- K2718 Toshiba SemiconductorDocument6 pagesK2718 Toshiba SemiconductorWathsalaNo ratings yet

- Gate Analog CrktsDocument232 pagesGate Analog Crktsmanoj kumarNo ratings yet

- Logic Family Introduction and OverviewDocument96 pagesLogic Family Introduction and OverviewNikhil DattaNo ratings yet

- PWM DC Motor Controller Using MOSFETs and IR2110 HDocument3 pagesPWM DC Motor Controller Using MOSFETs and IR2110 HdragoblaztrNo ratings yet

- Week 7 Chapter 3 FET Small Signal AnalysisDocument64 pagesWeek 7 Chapter 3 FET Small Signal AnalysisA.K.M.TOUHIDUR RAHMANNo ratings yet

- SCT3030AL: 650V V R (Typ.) 30mDocument14 pagesSCT3030AL: 650V V R (Typ.) 30mSas Pro EletronicaNo ratings yet

- CalculationsDocument15 pagesCalculationsnho_OsakaNo ratings yet

- 2SK2926 (L), 2SK2926 (S) : Silicon N Channel MOS FET High Speed Power SwitchingDocument9 pages2SK2926 (L), 2SK2926 (S) : Silicon N Channel MOS FET High Speed Power SwitchingNgoc AnNo ratings yet

- Syllabus PH 5118 & 5218Document5 pagesSyllabus PH 5118 & 5218Findx proNo ratings yet

- Irfz34, Sihfz34: Features Product SummaryDocument7 pagesIrfz34, Sihfz34: Features Product SummarySamia TouffaNo ratings yet

- Obe Curriculum For The Course: RGPV (Diploma Wing) BhopalDocument23 pagesObe Curriculum For The Course: RGPV (Diploma Wing) BhopalArpita VajpayeeNo ratings yet

- Fairchild Channel F Instructions PDFDocument2 pagesFairchild Channel F Instructions PDFDanNo ratings yet

- Spintronics ReportDocument27 pagesSpintronics Reportshailendra100% (5)

- MP3394 r1.07 PDFDocument17 pagesMP3394 r1.07 PDFAnonymous biMSzTyszNo ratings yet

- LS3954A LS3954 LS3955 LS3956 LS3958: Linear Integrated SystemsDocument3 pagesLS3954A LS3954 LS3955 LS3956 LS3958: Linear Integrated SystemsJCMNo ratings yet

- Mosfet Type On Laptop MotherboardDocument6 pagesMosfet Type On Laptop MotherboardCrissy CrysNo ratings yet

- EE313 MOS Digital Integrated Circuit DesignDocument30 pagesEE313 MOS Digital Integrated Circuit DesignFernando Sánchez HernándezNo ratings yet

- EC8252 Question BankDocument11 pagesEC8252 Question BankPalaniappan Muthu TNo ratings yet

- BS170Document14 pagesBS170AndresNo ratings yet

- Data SheetDocument7 pagesData SheetGökhan SağdıçNo ratings yet

- Sic Power Devices in Power Electronics: An OverviewDocument8 pagesSic Power Devices in Power Electronics: An OverviewLuís SmithNo ratings yet

- IRFB20N50K: Smps Mosfet V R Typ. IDocument8 pagesIRFB20N50K: Smps Mosfet V R Typ. IFarides PitreNo ratings yet

- UNIT 3-2marks-FET PDFDocument9 pagesUNIT 3-2marks-FET PDFpriyanka236No ratings yet

- High Gain Amplifier With Enhanced Cascoded CompensationDocument8 pagesHigh Gain Amplifier With Enhanced Cascoded CompensationAMSA84No ratings yet

- A Transistor Ladder Voltage-Controlled Filter Implemented On A Field Programmable Analog ArrayDocument8 pagesA Transistor Ladder Voltage-Controlled Filter Implemented On A Field Programmable Analog Arrayfidel.certucheNo ratings yet

- Application Note en 20230209 AKX00063Document12 pagesApplication Note en 20230209 AKX00063Bhakti MatsyapalNo ratings yet