Professional Documents

Culture Documents

DR - 44defect Reduction by Nitrogen Purge of Wafer Carriers

DR - 44defect Reduction by Nitrogen Purge of Wafer Carriers

Uploaded by

Mukti Ali SadikinOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DR - 44defect Reduction by Nitrogen Purge of Wafer Carriers

DR - 44defect Reduction by Nitrogen Purge of Wafer Carriers

Uploaded by

Mukti Ali SadikinCopyright:

Available Formats

Defect Reduction by Nitrogen Purge of Wafer

Carriers

R. van Roijen1, P. Joshi1, D. Bailey2, S. Conti1, W. Brennan1, P. Findeis1

1 2

Microelectronics Division PDF Solutions

IBM Richardson, TX 75082

Hopewell Junction, NY, USA dane.bailey@pdf.com

rvanroij@us.ibm.com

Abstract—Nitrogen purge of wafer carriers is driving defect during processing and humidity can affect wafers. The

density reduction at critical process steps. We discuss the susceptibility to such contaminants will depend on the state of

mechanism of defect creation and how nitrogen purge improves the wafer surface at a given time.

defect density. We report on experimental split data from in line

inspection and the impact at electrical test. The effect on volume In addition to the fact that the FOUP can not keep all types

manufacturing is demonstrated. of contaminants away from the wafer, it can also have a

detrimental impact, compared to an environment where wafers

Keywords—Semiconductor processing; Contamination are exposed to the larger cleanroom. As we describe below, so-

called condensation defects are prevalent on wafers processed

I. INTRODUCTION with mini-environments. However, such defects are generally

not observed on wafers processed without mini-environments.

The need for defect reduction at present and future

technology nodes requires that we look for fundamentally new

methods to avoid contamination. The use of mini- III. SIGE EPITAXY

environments, which achieve better defect class than the Epitaxial growth of SiGe on silicon is used for strain

surrounding cleanroom, is critical for modern semiconductor engineering in CMOS logic, amongst others. Epitaxial SiGe in

manufacturing[1]. However, the mini-environment has the source/drain region of pFET devices increases the device

limitations: gases permeating the shell and other contaminants on current at given off current by as much as 20% [5,6].

can still come in contact with wafers[2].

Epitaxial growth will only be successful if the silicon

Nitrogen purge of wafer carriers can mitigate some of these surface is sufficiently clean and a number of authors have

disadvantages and eliminate defects caused by oxidation and described methods to achieve this[7]. One common result of

other mechanisms[3,4]. We demonstrate the improvement in insufficient surface cleaning is the so-called blocked growth

defect density and we show that certain queue time restrictions, defect (BG), where SiGe is completely absent in certain areas.

driven by formation of oxide over time, can be relaxed. An example of this defect is shown in cross section in fig. 1.

II. THE WAFER CARRIER

The Front Opening Unified Pod (FOUP) is widely used in

the Semiconductor industry. Its primary objective is to

effectively improve the cleanroom class for wafers inside,

compared to the level of the production floor. In our case the

wafers inside a FOUP are in a class 1 environment, while the

cleanroom outside is class 100. Thus the FOUP has made the

contamination level suitable for manufacturing at advanced

technology nodes, while keeping cost at acceptable levels.

The success of the mini-environment can be attributed to its

ability to keep dust, mainly generated by the presence of

humans, away from the wafer. However, dust is not the only

source of defects during fabrication. It is known volatile Fig. 1. A cross section of a BG defect. The two areas to each side of the

organic compounds (VOC), by products of chemicals used central gate structure (circled) are missing SiGe on the thin silicon layer. This

we call blocked growth.

978-1-4673-5007-5/13/$31.00 ©2013 IEEE 338 ASMC 2013

One contributing cause of BG defects was found to be epitaxy is 8 hours or less, since it is known there is an

condensation defects. Typically the silicon surface is cleaned increased risk of defects if we exceed 8 hours.

before epitaxial growth in some wet etch process, in our case

using dilute HF. When inspecting wafers after this clean step In the experiment we split a lot and ran three different

and before they entered the furnace, we found droplet shaped conditions: normal processing without purge with

defects on the surface. We also confirmed that BG defects were approximately 1 hour between clean and epitaxy; normal

found after epitaxy in the same location where the processing, but with a 30 hour wait before epitaxy; and

condensation was seen before[8]. The density of these defects processing with 30 hour wait before epitaxy, where the wafers

was often such that significant yield degradation occurred. By are kept in a FOUP with nitrogen purge. These conditions are

making changes to the clean process the defect density was expected to generate a significant difference in the number of

greatly reduced, but we still had to operate with a queue time defects.

restriction between clean and furnace to limit the BG defect

density.

Attempts to determine the composition of condensation

defects were not successful, but most likely they are small

droplets consisting mostly of water. A striking observation is

that such defects are not typically found where wafers are

exposed to the open cleanroom, presumably since water and

other remaining liquids quickly evaporate in the absence of a

sealed pod[9].

IV. EXPERIMENTAL

For some time nitrogen purge has been proposed as a way

to mitigate certain sources of defects, especially those that are

caused by oxygen or water [3,4,10,11]. Promising results have

also been reported using other methods to remove air and

molecular contaminants [12]. We use otherwise conventional

FOUPs with an inlet and outlet opening in the bottom and have

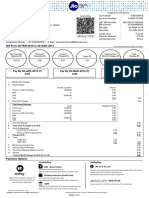

fitted stockers with the ability to flow nitrogen or other gases Fig. 3. Defect density D for three cases: POR (regular processing), queue

time violation in a normal FOUP without purge and queue time violation with

through the openings (fig. 2). nitrogen purge.

Since there is good reason to suspect that oxygen and/or

water play a large role in the formation of the defects for SiGe V. RESULTS

growth described above, we have applied nitrogen purge to

FOUPs for the processing steps before SiGe epitaxy. To test The result clearly confirmed the benefit of nitrogen purge

the hypothesis that the nitrogen reduces the occurrence of for avoiding growth defects. While the regularly processed

growth defects we could monitor a large sample of wafers wafers, which saw a standard mini-environment during the 30

during regular processing, but a simpler way is to compare hour wait, had a high density of growth defects, as expected,

cases where we intentionally violate the queue time restriction. the wafers which had spend 30 hours in a nitrogen purge had a

In the presence of air the queue time between preclean and defect level comparable to the wafers which did not violate the

queue time restriction. Fig. 3 shows the defect density for the

three cases: queue time violation in a nitrogen purge

environment (third bar) has a level comparable to the process

of record (POR, first bar), but the equivalent queue time

violation in the regular environment has a high defect density

(second bar).

The wafers used in the queue time experiment above

contained an array of electrical defectivity structures which

allow for the measurement of open and short failures on key

conductive layers. (eg. Active, Gate, Metal, etc). From such

electrical structures, a failure rate can be determined based on

the number of fails and the critical area of all similar structures

on a wafer[13]. The wafers in these experiments were

processed up to the first metal level and then electrically tested.

The electrical test results confirmed the in-line inspection

data. As shown in fig. 4, the most significant impact on the

results was observed for PFET active open fails. This is

Fig. 2. Photograph of the bottom of a FOUP with inlet and outlet for gas expected since a BG defect in the PFET active region would

purge. In our case the gas is nitrogen, but other gases can also be used. The likely cause an electrical failure due to the absence of SiGe

ports are fited with filters.

339 ASMC 2013

growth. The queue time violation in normal atmosphere,

which had a high defect density, also has a significantly higher

fail rate than POR. However, the comparable queue time

violation with nitrogen purge produced fail rates comparable to

POR.

Fig. 6. Average density of BG defects before (POR) and after (N2 purge)

application of nitrogen purge FOUP for the SiGe epitaxy process. The total

sample size is nearly 200 wafers inspected

VI. IMPACT ON PRODUCTION WAFERS

After changing the POR SiGe epitaxy process to take place

in purged FOUPs we continued to monitor defect levels using

Fig. 4. Open fail rate of p-type Active area for three cases: POR, queue time inline inspection. Though the level of BG defects was

violation in a conventional FOUP and queue time violation with nitrogen considered acceptable before this change, we did find the

purge. defect density decreased significantly with nitrogen purge, as

shown in fig. 6. Since the BG defect leads to a high probability

Another process step known to be at risk for defects of of fail at test, this is a yield benefit. The second benefit of

molecular origin is reactive ion etching (RIE). In this case there purge is the relaxation of the queue time limit. It results in

is no known queue time limitation, but the process gases used increased throughput and a reduction of rework.

have components such as fluorine and bromine which can

linger and react to cause damage to the wafer. We have applied VII. SUMMARY

nitrogen purge during lithography and etch for the definition of

gate structures. In this case we did not observe a significant The mini-environment has been very successful at

change of defect density at inline inspection, but we did find a improving the cleanroom class at recent technology nodes, but

clear reduction of electrical open defects for gate contacts at we are increasingly experiencing defects due to exposure to

electrical test. The response of defect density for electrical oxygen, water vapor and other molecular contaminants within

opens is shown in fig. 5. the mini-environment. We have applied nitrogen purge of

FOUPs in a production line and demonstrated that defect

density is reduced and queue time sensitivity can be eliminated

at the epitaxial growth of SiGe.

ACKNOWLEDGMENT

The authors would like to thank R. Miller, S. Kaldor and S.

Sankaran of IBM Microelectronics for their support of this

work.

REFERENCES

[1] J. Schliesser and P. Staudt-Fischbach, “Minienvironments and thermal

effects”, in Proc. IEEE/SEMI Advanced Semiconductor Manufacturing

Conference, pp. 432-439, 1999.

[2] Sung In Moon and C. W. Extrand, “Humidity Rise after Purge in

Micro-Environments”, in Proc. IEEE/SEMI Advanced Semiconductor

Manufacturing Conference, pp. 308-310, 2012.

[3] Frickinger, J.; Bugler, J.; Zielonka, G.; Pfitzner, L.; Ryssel, H.;

Fig. 5. Normalized density of electrical open defects for POR processing and Hollemann, S.; Schneider, H., “Reducing airborne molecular

with application of nitrogen purge FOUP for the gate etch process on a split contamination by efficient purging of FOUPs for 300-mm wafers-the

lot, as determined at electrical test. influence of materials properties” IEEE Transactions on Semiconductor

Manufacturing, Vol. 13 , pp. 427 – 433, 2000.

340 ASMC 2013

[4] Tokunaga, K.; Koiwa, A.; Suzuki, N.; Takeda, K.; Makabe, K.; [9] S. Keil, private communication (2011).

Nishihara, S.; Koike, A., “FOUP mini-environment contamination [10] Jiaxiang Nie; Yun Kang; Ruipeng Yang; Na Su; Weiye He; Sheng Liu;

control optimizing nitrogen purging” 2003 IEEE International Xiangtao Kong, “Investigation and reduction of metal voids post-CMP

Symposium on Semiconductor Manufacturing, pp. 463 – 466, 2003 in dual damascene process”, 9th Int. Conf on Solid-State and Integrated-

[5] W.H. Lee et al, “High Performance 65 nm SOI Technology with Circuit Technology, 2008.

Enhanced Transistor Strain and Advanced-Low-K BEOL”, Electron [11] B.H.J Tseng, M. D You, and S. C. Hsin, “Characterization and control

Devices Meeting, 2005 IEDM Technical Digest. IEEE International of microcontamination for advanced technology nodes and 300-mm

Publication Date: 5-5 Dec. 2005, pp. 59-63. wafer processing: overview and challenges”, IEEE Transactions on

[6] R. van Roijen et al. “Control of etch and deposition for embedded Device and Materials Reliability, Vol. 5 (2005), pp. 623 - 630

SiGe,” IEEE/SEMI Advanced Semiconductor Manufacturing [12] A. Favre et al, “Yield enhancement through new solutions for queue

Conference, ASMC 2010, pp. 133-136. time containment”, International Symposium on Semiconductor

[7] K. Umezawa et al, “Advanced Surface Cleanness Evaluation Technique Manufacturing (ISSM), (2008) , pp. 255 – 257.

Using Epitaxial Silicon Germanium (SiGe) Process beyond 32nm [13] B. T. Murphy, “Cost-size optima of monolithic integrated circuits”,

Node”, International Symposium on Semiconductor Manufacturing, Proceedings of the IEEE, Volume: 52 , Issue: 12 (1964), pp. 1537-1545.

(2007) pp. 1-4.

[8] R. van Roijen et al, “The Impact of the Environment on Wafer Defect

Density”, IEEE Transactions on Semiconductor Manufacturing, Issue

99, 2012

341 ASMC 2013

You might also like

- ZF Cruisecommand User ManualDocument240 pagesZF Cruisecommand User ManualSoesanto Tirtoprodjo100% (3)

- My - Bill - 26th February - 25th March - 7006338926 PDFDocument4 pagesMy - Bill - 26th February - 25th March - 7006338926 PDFRahila SofiNo ratings yet

- 2013 Nissan Sentra LanDocument128 pages2013 Nissan Sentra LanFSR1407100% (1)

- Line Follower Robot PDFDocument5 pagesLine Follower Robot PDFNameet JainNo ratings yet

- Bubble Free Resin For Infusion ProcessDocument8 pagesBubble Free Resin For Infusion ProcessVenkat GiriNo ratings yet

- Geopolymer Sewer Pipe.: October 2019Document7 pagesGeopolymer Sewer Pipe.: October 2019BRAHIMI ABDELGHANINo ratings yet

- Geopolymer Sewer Pipe.: October 2019Document7 pagesGeopolymer Sewer Pipe.: October 2019BRAHIMI ABDELGHANINo ratings yet

- Process Robustness and Defect Formation Mechanisms in Unidirectional SemipregDocument15 pagesProcess Robustness and Defect Formation Mechanisms in Unidirectional SemipregYiğit IlgazNo ratings yet

- Ipc2022-86892 Pig Sweep Nanoparticles Transform PipelineDocument5 pagesIpc2022-86892 Pig Sweep Nanoparticles Transform PipelineOswaldo MontenegroNo ratings yet

- 34 Ozone BleachingDocument12 pages34 Ozone Bleachingsushil kumar100% (1)

- WEAR TypesDocument2 pagesWEAR TypesRăzvan IordacheNo ratings yet

- MBR - Industrial WW AE 02Document12 pagesMBR - Industrial WW AE 02transilvanpopNo ratings yet

- Dust Suppression of Phosphate Rock: Storage, Conveyance and ShippingDocument7 pagesDust Suppression of Phosphate Rock: Storage, Conveyance and ShippingJavier Alejandro RodriguezNo ratings yet

- Cau Let 1998Document7 pagesCau Let 1998Jake LasontoNo ratings yet

- The Corrosion Resistance of Geopolymer Concrete Sewer Pipe.: October 2019Document7 pagesThe Corrosion Resistance of Geopolymer Concrete Sewer Pipe.: October 2019Shaik HussainNo ratings yet

- Risk Analysis of Oil and Gas Pipelines Subjected To CO2 Corrosion - ESREL2007Document10 pagesRisk Analysis of Oil and Gas Pipelines Subjected To CO2 Corrosion - ESREL2007ManeeshSinghNo ratings yet

- TappiDocument15 pagesTappiLye YpNo ratings yet

- Survey of The Fouling Characteristics Between Attached and Suspended Growth Microorganisms in Submerged Membrane BioreactorDocument11 pagesSurvey of The Fouling Characteristics Between Attached and Suspended Growth Microorganisms in Submerged Membrane BioreactorsagbvnNo ratings yet

- A Novel Polymer To Create A New Approach of Hole Cleaning. Iptc-20122-AbstractDocument10 pagesA Novel Polymer To Create A New Approach of Hole Cleaning. Iptc-20122-Abstractمحمد مريف حسن الربعي (Mohammed M H Al Rubaii)No ratings yet

- SPE 90836 Well-Completion Techniques and Methodologies For Maintaining Underbalanced Conditions Throughout Initial and Subsequent Well InterventionsDocument15 pagesSPE 90836 Well-Completion Techniques and Methodologies For Maintaining Underbalanced Conditions Throughout Initial and Subsequent Well Interventionskoroko SinseiNo ratings yet

- Towards A Methodology For Top Seal Efficacy AssessmentDocument6 pagesTowards A Methodology For Top Seal Efficacy Assessment是sherry吖No ratings yet

- 1 s2.0 S0011916409010108 MainDocument6 pages1 s2.0 S0011916409010108 Mainmrsuriyaa63No ratings yet

- Energies 04 01728 PDFDocument20 pagesEnergies 04 01728 PDFAoru SamuelNo ratings yet

- Mitigation of Soil-Side Corrosion On Storage Tank Bottoms in The Absence or Deficient CP SystemDocument14 pagesMitigation of Soil-Side Corrosion On Storage Tank Bottoms in The Absence or Deficient CP SystemfailureanalystNo ratings yet

- Application of Tip Screen-Out Fracturing TechniqueDocument11 pagesApplication of Tip Screen-Out Fracturing TechniqueZhiyong Huang100% (1)

- Membrance CleaningDocument23 pagesMembrance CleaningsaaroomaniNo ratings yet

- A Comparative Study of A Front Opening Unified Pod F 2022 International JouDocument11 pagesA Comparative Study of A Front Opening Unified Pod F 2022 International JouAsmamaw FirewNo ratings yet

- Cstic 2016 7463995Document3 pagesCstic 2016 7463995Bonn QianNo ratings yet

- Stefan On I 2020Document11 pagesStefan On I 2020chau_riberNo ratings yet

- Analysis of The Resin Transfer Molding RTM ProcessDocument7 pagesAnalysis of The Resin Transfer Molding RTM ProcesshafiNo ratings yet

- Test of Membrane Aerated Biofilm ReactorsDocument10 pagesTest of Membrane Aerated Biofilm ReactorsGeorge DobreNo ratings yet

- Resumo - Filipe Costa.67968Document10 pagesResumo - Filipe Costa.67968lqmanalyafy1No ratings yet

- Critical Evaluation of Date Palm Sheath Fibre CharDocument17 pagesCritical Evaluation of Date Palm Sheath Fibre CharEvan AzerNo ratings yet

- Frothing at The Lip - Stability in Your Flotation Cell: Author: Jason HeathDocument3 pagesFrothing at The Lip - Stability in Your Flotation Cell: Author: Jason HeathPili Torres OrregoNo ratings yet

- Froth CrowdingDocument3 pagesFroth CrowdingPili Torres OrregoNo ratings yet

- Frothing at The Lip - Stability in Your Flotation Cell: Author: Jason HeathDocument3 pagesFrothing at The Lip - Stability in Your Flotation Cell: Author: Jason HeathPili Torres OrregoNo ratings yet

- Removal of Hydrogen Sulfide From Biogas Using Dry Desulfurization SystemsDocument4 pagesRemoval of Hydrogen Sulfide From Biogas Using Dry Desulfurization Systemsandy131078No ratings yet

- CompilationDocument17 pagesCompilationAnonymous 1VhXp1No ratings yet

- Spe 100476Document6 pagesSpe 100476HSEQ AZUL ENERGYNo ratings yet

- Construction and Building Materials: Shihui Shen, Maria Burton, Bertram Jobson, Liv HaselbachDocument10 pagesConstruction and Building Materials: Shihui Shen, Maria Burton, Bertram Jobson, Liv HaselbachBranimirNo ratings yet

- Texto 1. Inglés 2Document1 pageTexto 1. Inglés 2Gabriel LopezNo ratings yet

- 1 s2.0 S2949929123000050 MainDocument11 pages1 s2.0 S2949929123000050 Maincaptain.binkhaterNo ratings yet

- Solar RRL - 2022 - Jay - Reduction in Indium Usage For Silicon Heterojunction Solar Cells in A Short Term IndustrialDocument7 pagesSolar RRL - 2022 - Jay - Reduction in Indium Usage For Silicon Heterojunction Solar Cells in A Short Term Industrialsupriya raiNo ratings yet

- 25.000 M3 AAT de Çamurun Ozonla Azaltımı-Fabiyi2008Document11 pages25.000 M3 AAT de Çamurun Ozonla Azaltımı-Fabiyi2008yusuf yeniceNo ratings yet

- Identification of Controlling Factors For The Initiation of Corrosion of Fresh Concrete Sewers (09-05-18)Document11 pagesIdentification of Controlling Factors For The Initiation of Corrosion of Fresh Concrete Sewers (09-05-18)Marcos Damião Resende LeiteNo ratings yet

- 19 Numerical PDFDocument14 pages19 Numerical PDFIJAERS JOURNALNo ratings yet

- Johnson2004 IFASDocument24 pagesJohnson2004 IFASLouay MansourNo ratings yet

- Comparison of The Processing of Epoxy Resins in Pultrusion With Open Bath Impregnation and Closed-Injection PultrusionDocument11 pagesComparison of The Processing of Epoxy Resins in Pultrusion With Open Bath Impregnation and Closed-Injection PultrusionfahadNo ratings yet

- BoilerDocument7 pagesBoilerXie ShjNo ratings yet

- 1 s2.0 S1385894724016930 MainDocument12 pages1 s2.0 S1385894724016930 MainWassachol SumarasinghaNo ratings yet

- Chemical Engineering and Processing: Process Intensi FicationDocument9 pagesChemical Engineering and Processing: Process Intensi FicationCamilo Botero ZapataNo ratings yet

- Tan 2017Document37 pagesTan 2017NAROUTO ITADORINo ratings yet

- Mitigation CorrossionDocument6 pagesMitigation CorrossionhadzicklNo ratings yet

- Week 7 - Reading 1 - MBRs in Wastewater Treatment (2010)Document10 pagesWeek 7 - Reading 1 - MBRs in Wastewater Treatment (2010)Weixuan ZhangNo ratings yet

- Cleaning Biofouled Membranes EarlyDocument11 pagesCleaning Biofouled Membranes EarlyNaim HossainNo ratings yet

- Coatings: Wear Characterization of Chromium PVD Coatings On Polymeric Substrate For Automotive Optical ComponentsDocument20 pagesCoatings: Wear Characterization of Chromium PVD Coatings On Polymeric Substrate For Automotive Optical ComponentsVũ Nguyễn TuấnNo ratings yet

- Performance Evaluation of Insulator Creepage Extender at Heavy MagnetiteDocument9 pagesPerformance Evaluation of Insulator Creepage Extender at Heavy Magnetiteboedak korporatNo ratings yet

- IPTC 10924 Analyzing Microbial Improved Oil Recovery Processes From Core FloodsDocument8 pagesIPTC 10924 Analyzing Microbial Improved Oil Recovery Processes From Core FloodsSajad FalahNo ratings yet

- Visco-Elastic CoatingsDocument7 pagesVisco-Elastic CoatingsXiaohua ChenNo ratings yet

- 1pollutant Inhibition in An Extreme UltravioletDocument12 pages1pollutant Inhibition in An Extreme UltravioletleehoomelqxNo ratings yet

- Copper Doped ZnODocument12 pagesCopper Doped ZnOkarthik tvkNo ratings yet

- Lifetime Assessment of NH - Plants: Approach For Lifetime ExtensionDocument12 pagesLifetime Assessment of NH - Plants: Approach For Lifetime Extensionvaratharajan g rNo ratings yet

- SATR-J - 6801 - Rev 0 PDFDocument6 pagesSATR-J - 6801 - Rev 0 PDFAdel KlkNo ratings yet

- Advances in UHV Transmission and DistributionDocument24 pagesAdvances in UHV Transmission and DistributionsalehknNo ratings yet

- Dissertation OledDocument8 pagesDissertation OledWhereToBuyPapersCanada100% (1)

- Lab 3Document3 pagesLab 3Mdarshad AlamNo ratings yet

- BUK71/794R1-40BT: 1. Product ProfileDocument15 pagesBUK71/794R1-40BT: 1. Product ProfileAlex RojaxNo ratings yet

- Journal of Luminescence: Monika Mall, Lokendra KumarDocument6 pagesJournal of Luminescence: Monika Mall, Lokendra KumarAzie AzuraNo ratings yet

- 4 Amps N-Channel MOSFET: 600voltsDocument5 pages4 Amps N-Channel MOSFET: 600voltsOliveira OliveiraNo ratings yet

- DPT CTRL Datasheet-5.0Document2 pagesDPT CTRL Datasheet-5.0Alejandro CorsiNo ratings yet

- Fast, Compact and Versatile Industrial RobotDocument2 pagesFast, Compact and Versatile Industrial RobotAlexandru ZdbNo ratings yet

- Frenic VG1Document52 pagesFrenic VG1cold storageNo ratings yet

- CMAX DM30 43 V53 - Mimo2 PDFDocument3 pagesCMAX DM30 43 V53 - Mimo2 PDFOrLand ChxNo ratings yet

- Voice Data Video CrosswalkDocument11 pagesVoice Data Video CrosswalkJulio SibrianNo ratings yet

- NCPA Tata Theatre DataDocument1 pageNCPA Tata Theatre DatashantanusubramaniamNo ratings yet

- EMBER LED - vSHINE LED FAÇADE LIGHTDocument7 pagesEMBER LED - vSHINE LED FAÇADE LIGHTjrobins1228No ratings yet

- TT 400, Applications Manual - ENDocument70 pagesTT 400, Applications Manual - ENanil kumarNo ratings yet

- Experiment - 12: Power Angle Curve of Syncronous MachineDocument3 pagesExperiment - 12: Power Angle Curve of Syncronous MachinesanjuNo ratings yet

- CZC7 Automatic Charger: Operating InstructionDocument10 pagesCZC7 Automatic Charger: Operating InstructionJavier VillelaNo ratings yet

- What FeedersDocument6 pagesWhat FeedersArtursNo ratings yet

- Electric CircuitsDocument107 pagesElectric CircuitsKristine Cris VenusNo ratings yet

- Speed Control of DC Motor Using Conventional and Adaptive PID ControllersDocument8 pagesSpeed Control of DC Motor Using Conventional and Adaptive PID Controllerstaddese bekeleNo ratings yet

- How To Install A Home Security SystemDocument4 pagesHow To Install A Home Security SystemluvavaleNo ratings yet

- Automotive Electronics Product Information Accelerometers For Satellite Sensor With PAS3-protocolDocument2 pagesAutomotive Electronics Product Information Accelerometers For Satellite Sensor With PAS3-protocolNegrea MihaiNo ratings yet

- H4262S - HP-UX Performance and TuningDocument4 pagesH4262S - HP-UX Performance and Tuningvel4yogaNo ratings yet

- L9 Rooted AndroidDocument6 pagesL9 Rooted AndroidKhasbullahHudaNo ratings yet

- Expertfea Com Catalog June 2014Document291 pagesExpertfea Com Catalog June 2014Prakash Kancharla100% (3)

- Matrix Multiplication Using SIMD TechnologiesDocument13 pagesMatrix Multiplication Using SIMD TechnologiesGurpreet SinghNo ratings yet