Professional Documents

Culture Documents

223 EE3117 DIC Lab4 Eng Updated 11202023 Ver2

223 EE3117 DIC Lab4 Eng Updated 11202023 Ver2

Uploaded by

DUY VĂN BÁOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

223 EE3117 DIC Lab4 Eng Updated 11202023 Ver2

223 EE3117 DIC Lab4 Eng Updated 11202023 Ver2

Uploaded by

DUY VĂN BÁCopyright:

Available Formats

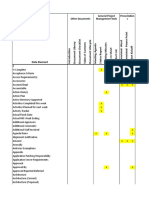

LABORATORY 4 – ARITHMETIC LOGIC UNIT & REGISTER FILE

LABORATORY 4

ARITHMETIC LOGIC UNIT & REGISTER FILE

OBJECTIVES

No. Objectives Requirements

Implement a simple Arithmetic Logic Unit – Write HDL code to

1

ALU – performing eight functions. implement the system.

Re-used logic components

2 Implement Register File – RF. from previous lab to build up

this system.

EXPERIMENT 1

Objective: Known how to implement an ALU.

Requirements:

Write Verilog/System Verilog HDL code to implement ALU block with 8-bit input

data performing eight functions with 4-bit Flags output (N, Z, C, V).

Propose a suitable circuit design for an ALU performing operations shown in

Table 1 and simulate it.

ALU_op_i[2:0] Function

0 0 0 Add, A+B

0 0 1 Subtract, A-B

0 1 0 Logical shift left

0 1 1 Logical shift right

1 0 0 AND

1 0 1 OR

1 1 0 NOT

1 1 1 Forwarding input, A

Table 1 ALU operations.

Department of Electronics Page | 1

Digital IC Design Laboratory

LABORATORY 4 – ARITHMETIC LOGIC UNIT & REGISTER FILE

Figure 1 Block diagram of 8-bit ALU.

Signal Description

A_i[7:0] Input operand A

B_i[7:0] Input operand B

ALU_op_i[2:0] 2-bit control signal which specifies which

function to perform.

ALU_RESULT_o[7:0] Output of ALU

ALU_FLAGS_o[3:0] Extra outputs indicating information

about the ALU output.

Table 2 ALU specification.

Instructions:

An Arithmetic Logic Unit (ALU) integrates various mathematical and logical

operations into a unified unit. In this part, students examine a sample of a basic ALU

(block diagram) featuring four functions with output flags. Additionally, labs introduce

the concept of shifters and rotators, covering not only their definitions but also several

types of commonly utilized shifters.

First, a typical ALU might perform addition, subtraction, AND, and OR

operations. ALU forms the heart of most computer systems. For instance, figure 2(a)

shows a symbol for an N-bit ALU with N-bit inputs and outputs.

ALUControl[1:0] Function

0 0 Add

0 1 Subtract

1 0 AND

1 1 OR

Table 3 Operations of simple ALU.

Department of Electronics Page | 2

Digital IC Design Laboratory

LABORATORY 4 – ARITHMETIC LOGIC UNIT & REGISTER FILE

ALU receives a 2-bit control signal ALUControl that specifies which function to

perform. Control signals will generally be shown in blue to distinguish them from the

data. Table 3 lists typical functions that ALU can perform.

(a) (b)

(c) (d)

Figure 2 (a) ALU symbol (b) N-bit ALU (c) Carry Propagate Adder (d) Subtractor:

symbol, and implementation.

Figure 2(b) shows an implementation of the ALU which contains:

o An N-bit adder and N 2-input AND, and OR gates.

o Inverters and a multiplexer to invert input B when ALUControl[0] is

asserted.

o A 4:1 multiplexer chooses the desired function based on ALUControl.

According to table 2 presenting operations ALU N-bit in Figure 2(b):

o If ALUControl[1:0] = 00, the output multiplexer chooses A + B.

o If ALUControl[1:0] = 01, the ALU computes A − B.

+1=− in two’s complement arithmetic. Because

ALUControl[0] is 1, the adder receives inputs A and asserted carry

in, causing it to perform subtraction: + +1 = − .

o If ALUControl[1:0] = 10, the ALU computes A AND B.

o If ALUControl[1:0] = 11, the ALU performs A OR B.

Department of Electronics Page | 3

Digital IC Design Laboratory

LABORATORY 4 – ARITHMETIC LOGIC UNIT & REGISTER FILE

(a) (b)

Figure 3 (a) ALU symbol with output flags (b) N-bit ALU with output flags.

Some ALUs produce extra outputs, called flags, that indicate information about

the ALU output. Figure 3(a) shows the ALU symbol with a 4-bit Flags output. As

shown in the schematic of this ALU in Figure 3(b), the Flags output is composed of the

N, Z, C, and V flags that indicate, respectively, that the ALU output, Result, is negative

or zero or that the adder produced a carry out or overflowed. Recall that the most

significant bit of a two’s complement number is 1 if it is negative and 0 otherwise.

o The N (Negative) flag is connected to the most significant bit of the ALU

output.

o The Z (Zero) flag is asserted when all of the bits of Result are 0, as

detected by the N-bit NOR gate in Figure 3(b).

o The C (Carry out) flag is asserted when the adder produces a carry out

and the ALU is performing addition or subtraction (indicated by ALUControl[1] = 0).

o Overflow detection, as shown on the left side of Figure 2(b), occurs when

the addition of two same signed numbers produces a result with the opposite sign.

V (oVerflow) is asserted when all three of the following conditions

are true:

(1) the ALU is performing addition or subtraction

(ALUControl[1] = 0).

(2) A and Sum have opposite signs, as detected by the XOR

gate.

(3) overflow is possible.

That is, as detected by the XNOR gate,

Department of Electronics Page | 4

Digital IC Design Laboratory

LABORATORY 4 – ARITHMETIC LOGIC UNIT & REGISTER FILE

Either A and B have the same sign and the adder is

performing addition (ALUControl[0] = 0) or

A and B have opposite signs and the adder is per forming

subtraction (ALUControl[0] = 1).

The 3-input AND gate detects when all three conditions are true

and asserts V.

Shifters and rotators move bits and multiply or divide by powers of 2. As the

name implies, a shifter shifts a binary number left or right by a specified number of

positions. Several kinds of commonly used shifters exist:

o Logical shifter – shifts the number to the left or right and fills empty

spots with 0’s.

Example: 11001 >> 2 = 00110; 11001 << 2 = 00100

o Arithmetic shifter – is the same as a logical shifter, but on right shifts

fills the most significant bits with a copy of the old most significant bit. This is useful for

multiplying and dividing signed numbers. Arithmetic shift left is the same as logical

shift left.

Note that, the operators <<, >>, and >>> typically indicate shift left, logical shift right,

and arithmetic shift right, respectively.

Example: 11001 >>> 2 = 11110; 11001 << 2 = 00100

o Rotator – rotates a number in a circle such that empty spots are filled

with bits shifted off the other end. ROR and ROL indicate rotate right, and rotate left,

respectively.

Example: 11001 ROR 2 = 01110; 11001 ROL 2 = 00111

An N-bit shifter can be built from N N:1 multiplexers. The input is shifted by 0 to

(N −1) bits, depending on the value of the log _ select lines. Figure 3 shows the

symbol and hardware of 4-bit shifters. Depending on the value of the 2-bit shift amount

shamt[1:0], the output Y receives the input A shifted by 0 to 3 bits. For all shifters,

when shamt[1:0] = 00, Y = A.

In addition, there are two features of left shift and arithmetic right shift that you

may pay attention to:

o A left shift is a special case of multiplication. A left shift by bits

multiplies the number by 2 .

Example: 000011B << 4 = 110000B is equivalent to 3 × 2 = 48 .

o An arithmetic right shift is a special case of division. An arithmetic right

shift by bits divides the number by 2 .

Department of Electronics Page | 5

Digital IC Design Laboratory

LABORATORY 4 – ARITHMETIC LOGIC UNIT & REGISTER FILE

Example: 11100D >>> 2 = 11111D is equivalent to = −1 .

(a) (b) (c)

Figure 4 4-bit shifters: (a) shift left, (b) logical shift right, (c) arithmetic shift right.

In this experiment, students should create two bit wide buses for input, internal

nodes and output. To add a bus, click the Wire (wide) icon or Schematic Editor L >

Create > Wire (wide) or Shift + W. Draw the bus as you would draw any normal

(narrow) wire.

Department of Electronics Page | 6

Digital IC Design Laboratory

LABORATORY 4 – ARITHMETIC LOGIC UNIT & REGISTER FILE

Figure 5 Instruction to create wide wire.

After creating the bus, the bus must be named. The same command to add wire

names for narrow wires is used, however the syntax for naming the bus is slightly

different.

Bus name is in the form Name<a:b>, where a and b denotes the range of bits of

the bus. In addition, it is possible to add several names to different buses at one time. To

do this, make sure the Bus Expansion button is off and simply type the names of the

buses separated by a space in the Names field. The names will be added in order when

you click on the various nets.

Figure 6 Create Wire Name window.

To draw or tap wires to and from the buses, draw wires from the buses and name

them correspondingly to their bits. To name the individual bit lines, type in the bus

Department of Electronics Page | 7

Digital IC Design Laboratory

LABORATORY 4 – ARITHMETIC LOGIC UNIT & REGISTER FILE

name (e.g. A<7:0> or <7:0>) and turn on Bus Expansion in the Add Wire Name

window. The Bus Expansion button is used to extract individual bit names from the bus.

When you start placing the names on the wires, you will notice that the first name will

be A<7> (or <7>), the next will be A<6> (or <6>), and so on.

Check: Students must show in your report these results.

The waveform to prove your design in HDL correctly, and students should show

all the cases of flags. Besides, the result of RTL viewer is obligatory to present.

Students show the waveforms of simulation results performed on your ALU by

verifying the outputs of the final ALU with three different patterns. For each pattern,

the results are verified for all eight components.

(Note: students can use any addition algorithm such as: Ripple Carry Adder, Carry

Look-Ahead…)

A[7:0] B[7:0] ALU_op_i ALU_RESULT_o[7:0] Function

0000_0000 0101_0101 000 ADD

0000_0000 0101_0101 001 SUB

0000_0000 0101_0101 010 SLL

0000_0000 0101_0101 011 SRL

0000_0000 0101_0101 100 AND

0000_0000 0101_0101 101 OR

0000_0000 0101_0101 110 NOT

0000_0000 0101_0101 111 Forward A

Table 4 First Test Vector Truth Table.

A[7:0] B[7:0] ALU_op_i ALU_RESULT_o[7:0] Function

1111_1111 0110_0110 000 ADD

1111_1111 0110_0110 001 SUB

1111_1111 0110_0110 010 SLL

1111_1111 0110_0110 011 SRL

1111_1111 0110_0110 100 AND

1111_1111 0110_0110 101 OR

1111_1111 0110_0110 110 NOT

1111_1111 0110_0110 111 Forward A

Table 5 Second Test Vector Truth Table.

Department of Electronics Page | 8

Digital IC Design Laboratory

LABORATORY 4 – ARITHMETIC LOGIC UNIT & REGISTER FILE

A[7:0] B[7:0] ALU_op_i ALU_RESULT_o[7:0] Function

0010_1010 1001_1111 000 ADD

0010_1010 1001_1111 001 SUB

0010_1010 1001_1111 010 SLL

0010_1010 1001_1111 011 SRL

0010_1010 1001_1111 100 AND

0010_1010 1001_1111 101 OR

0010_1010 1001_1111 110 NOT

0010_1010 1001_1111 111 Forward A

Table 6 Second Test Vector Truth Table.

EXPERIMENT 2

Objective: Known how to implement Register File – RF.

Requirements:

Write VHDL/Verilog/System Verilog HDL code to implement Register File

including eight 8-bit registers.

Propose a suitable circuit for your design and simulate it.

Instructions:

A typical datapath has multiple registers. The construction of a bus system with

a large number of registers requires different techniques. A set of registers having

common operations performed on them may be organized into a register file. The

register file (RF) contains all the registers and provides two read ports and one write

port. The RF always provides the contents of the registers corresponding to the read

register inputs on the outputs.

In general, a register file is denoted as 2 × , where is the number of register

address bits and is the number of bits per register. In this experiment, students will

implement 2 × 3 register file. The block diagram of register file, Register File

specifications, and register file architecture are introduced in Figure 7, Table 7, and

Figure 8, respectively.

Besides, the register file architecture shown in Figure 8 is not obligatory to follow,

students can feel free to modify or propose your design, however, please present it

Department of Electronics Page | 9

Digital IC Design Laboratory

LABORATORY 4 – ARITHMETIC LOGIC UNIT & REGISTER FILE

similar to Figure 7, Table 7, and Figure 8.

Figure 7 Block diagram of Register File.

Signal Description

CLK_i Positive clock

RST_ni Low negative reset

RD_ADDR1_i[2:0] The first address to be read from.

RD_ADDR2_i[2:0] The second address to be read from.

WRT_DEST_i[2:0] Address supposed to be written into the

register file.

WRT_DATA_i[7:0] Data supposed to be written into the

register file.

WRT_EN_i 1: write to the Register File

0: read the Register File

RD_DATA1_o The read data from first address.

RD_DATA2_o The read data from second address.

Table 7 Register File specifications.

Department of Electronics Page | 10

Digital IC Design Laboratory

LABORATORY 4 – ARITHMETIC LOGIC UNIT & REGISTER FILE

Figure 8 Implementation of 8 × 8 Register File.

There are some points that students need to take care of:

o The structure of registers in the register file is PIPO.

Figure 9 The registers structure.

o Reads and writes are always completed in one cycle.

A read can be done any time (i.e. combinational).

A write is performed at the rising clock edge.

If WRT_EN_i = 1 the write address and data must be stable at the clock edge.

Check:

The waveform to prove your design in HDL correctly, and the result of RTL

viewer is obligatory to present.

Students will show the waveforms of simulation results performed on your RF in

circuit design.

Department of Electronics Page | 11

Digital IC Design Laboratory

LABORATORY 4 – ARITHMETIC LOGIC UNIT & REGISTER FILE

---------------------------------------------------------------------------------------------

ONE MORE THING…

After completing this lab, please answer the following questions.

How much time did you spend completing this lab?

Is there any problem when you do? Please let me know.

Department of Electronics Page | 12

Digital IC Design Laboratory

You might also like

- Mental Health and Healthy Lifestyle Workplace Policy and ProgramDocument7 pagesMental Health and Healthy Lifestyle Workplace Policy and ProgramDarryl Robles100% (5)

- 8 Bit ALU Design in Modelsim Using Verilog With Code and Test BenchDocument17 pages8 Bit ALU Design in Modelsim Using Verilog With Code and Test BenchArslan Javaid67% (3)

- Ramniranjan Jhunjhunwala College of Arts, Science and Commerce (Autonomous)Document1 pageRamniranjan Jhunjhunwala College of Arts, Science and Commerce (Autonomous)Angelina JoyNo ratings yet

- Exclusive - OR-GATE, HALF ADDER, FULL Adder: Experiment 2Document6 pagesExclusive - OR-GATE, HALF ADDER, FULL Adder: Experiment 2noputNo ratings yet

- Logic Gates Programming in PLCDocument19 pagesLogic Gates Programming in PLCRahul Sharma100% (6)

- CH 05Document6 pagesCH 05Saif BaneesNo ratings yet

- ALS-R User's Manual: Amplified Spontaneous Emission Light SourceDocument16 pagesALS-R User's Manual: Amplified Spontaneous Emission Light SourceAnonymous 60esBJZIjNo ratings yet

- ALUDocument7 pagesALUmonsour888No ratings yet

- DLCA - Practical No 5Document8 pagesDLCA - Practical No 504 Tushar BhadrikeNo ratings yet

- Digital Design LaboratoryDocument10 pagesDigital Design Laboratorykarths22No ratings yet

- Lab 1Document9 pagesLab 1Chinmayi AvasaralaNo ratings yet

- Federal Democratic Republic of Ethiopia Ministry of Defense Defense University, College of EngineeringDocument12 pagesFederal Democratic Republic of Ethiopia Ministry of Defense Defense University, College of EngineeringmelkamzerNo ratings yet

- Half AdderDocument10 pagesHalf AdderSanjayNo ratings yet

- Lab - ALUDocument3 pagesLab - ALUERICK BERNARDO TEQUIZ MERCHANNo ratings yet

- CEG2136 15lab3Document17 pagesCEG2136 15lab3Mat MorashNo ratings yet

- Digital System Design (EE005-3.5-3) : Individual Assignment ReportDocument27 pagesDigital System Design (EE005-3.5-3) : Individual Assignment ReportBalaji ArunNo ratings yet

- Design of An Arithmetic and Logic Unit Based On Reversible Logic GatesDocument8 pagesDesign of An Arithmetic and Logic Unit Based On Reversible Logic GateslambanaveenNo ratings yet

- Alu PDFDocument4 pagesAlu PDFAravindhan SaravananNo ratings yet

- Module IV LOCDocument21 pagesModule IV LOCrahulNo ratings yet

- Exp No. 3: Design of 8-Bit Arithmetic Logic Unit (ALU)Document5 pagesExp No. 3: Design of 8-Bit Arithmetic Logic Unit (ALU)DaniaNo ratings yet

- DLD Lab 01Document8 pagesDLD Lab 01MeerMuhammad AnsariNo ratings yet

- Digital Electronics LabDocument34 pagesDigital Electronics LabJuno Hera Magallanes Huyan100% (1)

- LAB 5 - Implementing An ALU GoalsDocument9 pagesLAB 5 - Implementing An ALU GoalsJoey WangNo ratings yet

- LAB 5 - Implementing An ALU: GoalsDocument9 pagesLAB 5 - Implementing An ALU: GoalsBlmjdb AbdelhafidNo ratings yet

- F4HCJAQJ3YPYHHNDocument44 pagesF4HCJAQJ3YPYHHNFerekkanNo ratings yet

- S07 273 Lab6Document7 pagesS07 273 Lab6Carlos V.No ratings yet

- WEEK 13:: ObjectivesDocument35 pagesWEEK 13:: ObjectivesJohn Kenneth MantesNo ratings yet

- 4-Bit AluDocument45 pages4-Bit AluAllam Rajkumar0% (1)

- ALU MISSDV0716 G.kaladhar Design PlanDocument16 pagesALU MISSDV0716 G.kaladhar Design Plangourishettikaladhar562No ratings yet

- Unit 5Document22 pagesUnit 5Aditya AgrawalNo ratings yet

- Chapter 1lecture 1.3 (Computer Hardware Components) Notes+Homework+References+videoLinkDocument6 pagesChapter 1lecture 1.3 (Computer Hardware Components) Notes+Homework+References+videoLinkMeena Malik BaliharNo ratings yet

- Design of 8 Bit Alu Using Microwind 3.1Document6 pagesDesign of 8 Bit Alu Using Microwind 3.1ijaert100% (1)

- Applied ElectronicsDocument45 pagesApplied ElectronicsD-2009 Saswat Pritam BaruahNo ratings yet

- AluDocument10 pagesAluAbhishek PatraNo ratings yet

- VHDL Implementation of 8-Bit ALU: Arshabha AryaDocument7 pagesVHDL Implementation of 8-Bit ALU: Arshabha Aryamohammad aidilNo ratings yet

- Unit 5 Digital ElecDocument27 pagesUnit 5 Digital ElecSOFIANo ratings yet

- Combinational CircuitsDocument28 pagesCombinational CircuitsgurumohanNo ratings yet

- Lab # 01: Introduction To Basic Logic Gates & DLD Trainer: ObjectivesDocument96 pagesLab # 01: Introduction To Basic Logic Gates & DLD Trainer: ObjectivesAbdullah ShafiqNo ratings yet

- Unit Iii PDFDocument70 pagesUnit Iii PDFChristopher AndersonNo ratings yet

- Best College Kharian: Prof: Ali SubtainDocument5 pagesBest College Kharian: Prof: Ali SubtainAye ShaNo ratings yet

- NIM-BSEE-2020-40 Lab 10 657ef2696b082Document17 pagesNIM-BSEE-2020-40 Lab 10 657ef2696b082haidersheraz99No ratings yet

- CAwEDSD HW1Document6 pagesCAwEDSD HW1黃于瑄No ratings yet

- My ProjectDocument31 pagesMy Projectesam eisaNo ratings yet

- 8 Bit ALU Arithmetic Logic UnitDocument14 pages8 Bit ALU Arithmetic Logic Unitvenkateshprasad1562812No ratings yet

- Exp No. 3: Design of 8-Bit Arithmetic Logic Unit (ALU)Document3 pagesExp No. 3: Design of 8-Bit Arithmetic Logic Unit (ALU)Sara Ali100% (1)

- S.No Assignment Date Remarks 1. 2.: IndexDocument31 pagesS.No Assignment Date Remarks 1. 2.: IndexInstantNo ratings yet

- VHDL Code For A Simple ALUDocument4 pagesVHDL Code For A Simple ALUparammohali100% (1)

- Dokumen - Tips - 8 Bit Alu ReportDocument21 pagesDokumen - Tips - 8 Bit Alu ReportKshitize AgarwalNo ratings yet

- AluDocument37 pagesAluarushi_somaniNo ratings yet

- Lab 01Document6 pagesLab 01MUSKAN AMEER UD DINNo ratings yet

- 2.ar - enDocument12 pages2.ar - enاحمد احمدNo ratings yet

- Lecture 1.1.4 (Computer Hardware Components - ALU, Registers, Memory)Document5 pagesLecture 1.1.4 (Computer Hardware Components - ALU, Registers, Memory)adityaNo ratings yet

- EIA Notes - Week - 5Document7 pagesEIA Notes - Week - 5BHARAT NIKKAMNo ratings yet

- Bca I Semester Subject Code: BCA-104P ELECTRONICS: Laboratory ManualDocument24 pagesBca I Semester Subject Code: BCA-104P ELECTRONICS: Laboratory ManualGamplayNo ratings yet

- DLD Lab 1Document5 pagesDLD Lab 1گيدوڙو ماڇيNo ratings yet

- Summary Programmable Logic ControlDocument6 pagesSummary Programmable Logic ControlSagi NesiNo ratings yet

- Lab 7 Half & Full AdderDocument8 pagesLab 7 Half & Full Addersafdarmunir070No ratings yet

- Complete-Unit-01-Soft Copy of Notes - Computer Data Representations - CAODocument15 pagesComplete-Unit-01-Soft Copy of Notes - Computer Data Representations - CAOaayushgithala101No ratings yet

- Implementing Binary Adder and Subtractor Circuits: Laboratory Exercise 4Document11 pagesImplementing Binary Adder and Subtractor Circuits: Laboratory Exercise 4Alvin GilayNo ratings yet

- DE Unit-4Document31 pagesDE Unit-4Dheeraj GoswamiNo ratings yet

- Experiment Name: Adder and SubtractorDocument13 pagesExperiment Name: Adder and SubtractorA K M Fahim Faysal (182016018)No ratings yet

- EE200 Experiment 07Document5 pagesEE200 Experiment 07xanxus2012No ratings yet

- Activity Heal The Environmentpermentilla-Michael-Ray-E.Document1 pageActivity Heal The Environmentpermentilla-Michael-Ray-E.Michael Ray PermentillaNo ratings yet

- As 1330-2004 Metallic Materials - Drop Weight Tear Test For Ferritic SteelsDocument7 pagesAs 1330-2004 Metallic Materials - Drop Weight Tear Test For Ferritic SteelsSAI Global - APACNo ratings yet

- Chapter 22 - Physics - Coordinated Science - IGCSE CambridgeDocument154 pagesChapter 22 - Physics - Coordinated Science - IGCSE CambridgeAlvin DuaneNo ratings yet

- Decommissioning and Installation Project at Lillgrund Offshore Wind FarmDocument23 pagesDecommissioning and Installation Project at Lillgrund Offshore Wind FarmzakaNo ratings yet

- Guidelines For ReportDocument8 pagesGuidelines For ReportYash SinghNo ratings yet

- Advt. 4 Year 2022 - WebsiteDocument6 pagesAdvt. 4 Year 2022 - WebsiteprakashNo ratings yet

- Current Transformer - PACT RCP-4000A-1A-D95 - 2904921: Key Commercial DataDocument4 pagesCurrent Transformer - PACT RCP-4000A-1A-D95 - 2904921: Key Commercial DataЮрий ЛобановNo ratings yet

- Project Management Tools Document MatrixDocument35 pagesProject Management Tools Document MatrixtabaquiNo ratings yet

- MT6768 Android ScatterDocument18 pagesMT6768 Android ScatterGerryl DestorNo ratings yet

- DLL Grade 4 Q3 W2Document4 pagesDLL Grade 4 Q3 W2Floy ClarinNo ratings yet

- Itf World Tennis Tour Juniors Withdrawal Form 2020: IPI N Player DetailsDocument1 pageItf World Tennis Tour Juniors Withdrawal Form 2020: IPI N Player Detailsjean luis estNo ratings yet

- Ehv Ac & DC Transmission MCQ Unit - 5 - Math TradersDocument3 pagesEhv Ac & DC Transmission MCQ Unit - 5 - Math TradersRitNo ratings yet

- Plegadora WC67YDocument5 pagesPlegadora WC67YJhonny AlvarezNo ratings yet

- 3134478Document4 pages3134478Intan WidyawatiNo ratings yet

- Seeq 2023 Analytics Resolutions GuideDocument7 pagesSeeq 2023 Analytics Resolutions GuidebinaycNo ratings yet

- The New Aramaic Dialect of Qaraqosh HousDocument15 pagesThe New Aramaic Dialect of Qaraqosh HousPierre BrunNo ratings yet

- مطوية انجليزية 1Document2 pagesمطوية انجليزية 1Chaker HamdiNo ratings yet

- Long Quiz Prelim DiassDocument2 pagesLong Quiz Prelim DiassBel Patrice TisuelaNo ratings yet

- Canal SystemsDocument69 pagesCanal SystemsAnter TsatseNo ratings yet

- Flotation Process of GoldDocument5 pagesFlotation Process of GoldMickShazanNo ratings yet

- Intimate Partner Violence Among Pregnant Women in Kenya: Forms, Perpetrators and AssociationsDocument25 pagesIntimate Partner Violence Among Pregnant Women in Kenya: Forms, Perpetrators and AssociationsNove Claire Labawan EnteNo ratings yet

- NM Practical FileDocument12 pagesNM Practical Filejangra014No ratings yet

- When New Manager FailsDocument6 pagesWhen New Manager Failssultan alassamNo ratings yet

- Module 3: Induction Motor Drives: SyllabusDocument8 pagesModule 3: Induction Motor Drives: SyllabusManoj SkNo ratings yet

- Indonesian Society 'S Sentiment Analysis Against The COVID-19 Booster VaccineDocument6 pagesIndonesian Society 'S Sentiment Analysis Against The COVID-19 Booster VaccineKasiyemNo ratings yet

- Der DirectoryDocument262 pagesDer DirectoryBenNo ratings yet