Professional Documents

Culture Documents

SDZNMMBHER 008G SanDisk

SDZNMMBHER 008G SanDisk

Uploaded by

Satvik HardatOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

SDZNMMBHER 008G SanDisk

SDZNMMBHER 008G SanDisk

Uploaded by

Satvik HardatCopyright:

Available Formats

43nm

8GB (32Gb x 2-die)

16GB (32Gb x 4-die)

32GB (32Gb x 8-die)

Y

4LC 3V NAND Flash Memory Data Sheet

AR

Preliminary Version

Rev 1.3

IN

March 11, 2009

IM

Part Numbers: SDZNMMBHER-008G

SDZNMMCHER-016G

EL

SDZNMMDHER-032G

PR

Proprietary and Confidential

Copyright © 2009 by SanDisk Corporation and its applicable affiliates. All rights reserved.

This specification is confidential and is subject to any SanDisk Corporation handbooks or terms of use

provided or made available to the customer. This specification is subject to change and/or being updated

without notice. The customer assumes sole and exclusive responsibility for compliance with safety,

environmental, export, trade, and other applicable laws and regulations with respect to this specification.

In addition, the customer assumes sole and exclusive responsibility for any use, embedded or otherwise,

of device(s) described by this specification in any medical, aviation, nuclear, or ultra-hazardous

applications, as well as in applications that could cause property damage, bodily injury, or death.

All specifications are subject to change without notice.

For memory capacity, 1 megabyte (MB) = 1 million bytes, and 1 gigabyte (GB) = 1 billion bytes.

Some of the listed capacity is used for formatting and other functions, and thus is not available for

data storage.

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

Revision History

Version Revision Date Changes

Preliminary 0.3 01/09/09 Initial release.

Preliminary 1.0 01/14/09 Added Package Marking Spec; minor changes.

Preliminary 1.1 02/10/09 Updated timing diagrams.

Updated the following sections to clarify the Power On Reset

current consumption:

• 1.7 Power-On/Off Sequence

• 1.8 Power On Reset

Y

• 1.14 DC Characteristics

Updated the following sections to clarify the parameter value

AR

Preliminary 1.2 03/09/09 in multi-die package:

• 1.2 Features

• 1.11 Capacitance

• 1.12 Valid Blocks

IN

• 1.14 DC Characteristics

Preliminary 1.3 03/11/09 Updated Package Marking Specification.

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page ii

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

Table of Contents

1. Device Overview...............................................................................................................5

1.1 Description ...............................................................................................................5

1.2 Features...................................................................................................................5

1.3 Pin Assignment ........................................................................................................6

1.4 52-Pin LGA Package Outline Drawing......................................................................7

1.5 Pin Functions ...........................................................................................................8

1.6 Pin Decoding Tables ................................................................................................9

1.7 Power-On/Off Sequence ........................................................................................10

1.8 Power On Reset.....................................................................................................10

Y

1.9 Write Protect Signal................................................................................................11

1.10 Absolute Maximum Ratings....................................................................................12

AR

1.11 Capacitance ...........................................................................................................12

1.12 Valid Blocks ...........................................................................................................12

1.13 Recommended DC Operating Conditions...............................................................13

IN

1.14 DC Characteristics .................................................................................................13

1.15 AC Characteristics and Recommended Operating Conditions................................14

IM

1.16 AC Test Conditions ................................................................................................15

1.17 Programming and Erasing Characteristics .............................................................15

2. Address Assignment......................................................................................................16

EL

3. Timing Diagrams ............................................................................................................17

3.1 Write Timing ...........................................................................................................17

PR

3.2 Read Timing...........................................................................................................17

3.3 Latch Timing for Command/Address/Data..............................................................18

3.4 Command Input Cycle Timing ................................................................................18

3.5 Address Input Cycle Timing....................................................................................19

3.6 Data Input Cycle Timing .........................................................................................19

3.7 Serial Read Cycle Timing .......................................................................................20

3.8 Status Read Cycle Timing ......................................................................................20

3.9 Read Cycle Timing .................................................................................................21

3.10 Read Cycle Timing: When Interrupted by Command Enable..................................21

3.11 Read Cycle with Data Cache Timing (1/2)..............................................................22

3.12 Read Cycle with Data Cache Timing (2/2)..............................................................23

3.13 Column Address Change in Read Cycle Timing (1/2).............................................24

3.14 Column Address Change in Read Cycle Timing (2/2).............................................25

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page iii

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.15 Data Output Timing ................................................................................................26

3.16 Single Page Program Operation Timing .................................................................27

3.17 Auto Page Program with Data Cache Operation Timing (1/3).................................28

3.18 Auto Page Program with Data Cache Operation Timing (2/3).................................29

3.19 Auto Page Program with Data Cache Operation Timing (3/3).................................30

3.20 Multi Page Program with Data Cache Operation Timing (1/4) ................................31

3.21 Multi Page Program with Data Cache Operation Timing (2/4) ................................32

3.22 Multi Page Program with Data Cache Operation Timing (3/4) ................................33

3.23 Multi Page Program with Data Cache Operation Timing (4/4) ................................34

3.24 Single Block Erase Timing......................................................................................35

3.25 Multi Block Erase Timing........................................................................................36

Y

3.26 ID Read Operation Timing......................................................................................37

AR

4. Operation Mode: Logic and Command Tables.............................................................38

4.1 Logic Table ............................................................................................................38

4.2 Command Table.....................................................................................................39

IN

5. Device Operation............................................................................................................40

5.1 Read Mode ............................................................................................................40

5.2 Random Column Address Change in Read Cycle ..................................................40

IM

5.3 Read Operation with Read Cache ..........................................................................41

5.4 Multi Page Read Operation ....................................................................................42

EL

5.5 Single Page Program Operation.............................................................................45

5.6 Random Column Address Change in Single Page Program Operation ..................45

5.7 Auto Page Program with Data Cache Operation ....................................................46

PR

5.8 Multi Page Program with Data Cache Operation ....................................................48

5.9 Page Copy (2) ........................................................................................................52

5.10 Multi Page Copy (2)................................................................................................54

5.11 Single Block Erase .................................................................................................55

5.12 Multi Block Erase ...................................................................................................56

5.13 ID Read..................................................................................................................57

5.14 Status Read ...........................................................................................................58

5.15 Reset .....................................................................................................................59

6. Application Notes and Comments ................................................................................61

7. Package Marking Specification .....................................................................................67

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page iv

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

1. Device Overview

1.1 Description

The 43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory contains 2, 4, or 8 32Gb NAND Flash

Memory dies in a 52-lead 14 x 18 LGA package.

Each 32Gb NAND Flash Memory has two 8568-byte static registers, which allow program and read data

to be transferred between the register and the memory cell array in 8568-byte increments. The device is

organized as (8192 + 376) bytes × 128 pages × 4096 blocks. A single block unit consists of 1 Mbyte +

47 Kbytes = 8568 bytes x 128 pages.

This serial-type memory device makes use of I/O pins for command inputs, as well as for both address

and data input/output. Erase and Program operations are executed automatically, making the device

highly suited for applications such as solid-state file storage, image file memory for still cameras, voice

recording, and other systems that require high-density non-volatile memory data storage.

1.2 Features

Y

AR

Feature 32Gb (4LC)

Organization:

Memory Cell Array 8568 x 512K x 8 per die

Number of Registers 8568 x 8 per die

IN

Number of Planes 2 per die

Block Size (1M + 47K) bytes

Page Size (8192 + 376) bytes = 8568 bytes

IM

Number of Pages per Block 128

Read, Multi Page Read, Single Page Program, Auto Page Program,

Modes Multi Page Program, Page Copy, Multi Page Copy, Single Block

EL

Erase, Multi Block Erase, ID Read, Status Read, Reset

Serial input/output

Mode Control

Command control

PR

Number of Valid Blocks Max 4096 blocks per die; Min 3933 blocks per die

Power Supply VCC = 2.7V to 3.6V

Cell Array to Register: 200 μs max

Access Time

Serial Read Cycle: 25 ns min

Auto Page Program: 1600 μs/page typ.

Program/Erase Time

Single Block Erase: 3 ms/block typ.

Read (30 ns cycle): 50 mA max

Program (avg.): 50 mA max

Operating Current *

Erase (avg.): 50 mA max

Standby: 50 μA max

Package 14mm x 18mm x 1.0mm LGA 52-Pin

* Measured per selected active die at VCC = 3.6V, 30 ns Read/Write cycle time.

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 5

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

1.3 Pin Assignment

Top View

A B C D E F G H J K L M N

RY/

8 BY4 R R R VSS R

RY/ RY/

7 BY3 RE1 BY2 IO7-2 IO6-2 IO5-2 VCC

6 VCC RE2 VSS IO7-1 IO5-1 VCC

Y

RY/

5 R/B3#

CE1 CE2

BY1

WP2 IO6-1 IO4-1 IO4-2

AR

4

3 CLE1 CLE2 WE1 IO0-1 IO2-1 VSS IO3-2

IN

2 VSS ALE2 WP1 IO1-1 IO3-1 VSS

IM

1 CE3 ALE1 WE2 IO0-2 IO1-2 IO2-2 VCC

EL

0 CE4 R R R R R

PR

OA OB OC OD OE OF

Pin 1 Identifier

Figure 1: 14 x 18 52-Pin LGA Pinout

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 6

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

1.4 52-Pin LGA Package Outline Drawing

Y

AR

IN

IM

EL

PR

All Dimensions in Millimeters

Figure 2: 52-Pin Package Outline Drawing

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 7

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

1.5 Pin Functions

This serial access memory device makes use of timesharing for input of address information.

Pin Name Type Description

Chip Enable: The device goes into a low-power Standby mode when CE goes High

while the device is in Ready state. The CE signal is ignored when the device is in Busy

CE Input

state (RY/BY = L), such as during a Program, Erase, or Read operation, and does not

enter Standby mode even if the CE input goes High.

WE Input Write Enable: The WE signal is used to control the acquisition of data from the I/O port.

Read Enable: The RE signal controls serial data output. Data is available tREA after

RE Input the falling edge of RE. The internal column address counter is also incremented

(Address = Address + l) on this falling edge.

Y

Command Latch Enable: The CLE input signal is used to control loading of the

AR

operation mode command into the internal command register. The command is latched

CLE Input

into the command register from the I/O port on the rising edge of the WE signal while

CLE is High.

Address Latch Enable: The ALE signal is used to control loading address information into

IN

ALE Input the internal address register. Address information is latched into the address register from

the I/O port on the rising edge the WE signal while ALE is High.

Write Protect: The WP signal is used to protect the device from accidental

IM

programming or erasing. The internal voltage regulator is reset when WP is Low. This

WP Input

signal is usually used for protecting the data during the power-on/off sequence, when

input signals are invalid.

EL

Ready/Busy: The RY/BY output signal is used to indicate the operating condition of the

device. The RY/BY signal is in Busy state (RY/BY = L) during Program, Erase, and

RY/BY Output Read operations, and it returns to Ready state (RY/BY = H) after completion of the

operation. The output buffer for this signal is an open drain and must be pulled up to

PR

Vcc with an appropriate resistor.

VCC Supply Power Supply, 2.7 to 3.6V

VSS Supply Ground

I/O Ports: The I/O0 to 7 pins are used as a port for transferring address, command, and

I/O0 to I/O7 I/O

input/output data to and from the device.

NC Do Not Connect

There are 4 CE, 4 RY/BY, 2 RE, 2 CLE, 2 ALE, 2 WE, and 2 WP pins. There are two 8-bit-wide data I/O

buses, with CE1 and CE3 mapped to the I/O-1 bus, and CE2 and CE4 mapped to the I/O-2 bus, per the

ONFI 2.0 specification. See the “Pin Decoding Tables“ section for pin decoding information for 2, 4, and

8-die packages.

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 8

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

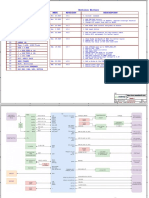

1.6 Pin Decoding Tables

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 9

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

1.7 Power-On/Off Sequence

The device is configured such that it does NOT go into automatic self initialization during power on. It is

highly recommended that the Write Protect signal should go high during the initial power-on and power-off

sequence (as shown in the diagram below) for protecting against data corruption.

1.8 Power On Reset

Since some input signals might not be stable at power on, performing an FFh Reset after power up is

necessary. During the FFh Reset Busy period, each selected die in the device consumes a maximum

current of 50mA (ICCO0). Only the selected die is reset by the FFh command.

For the 2-die device with 2 Chip Enable control pins and the 4-die device with 4 Chip Enable control pins,

one die is selected by each Chip Enable control pin. For the 8-die device with 4 Chip Enable control pins,

two die are selected by each Chip Enable control pin. The maximum current consumed during the Reset

Busy period is 50mA per die selected by the Chip Enable control pin(s). Therefore, for 2-die and 4-die

Y

devices, the maximum current consumed during the Reset Busy period is 50mA when one Chip Enable

control pin is asserted; and for 8-die devices, the maximum current consumed during the Reset Busy

AR

period is 100mA when one Chip Enable control pin is asserted.

IN

2.7 V 2.7 V

VCC 2.5 V 2.5 V

0V

V IH

IM

WP V IL V IL

tPS=100us

EL

CLE

t CLS t CLH

t CS t CH

CE

PR

t WP

WE

t ALS t ALH

ALE

t DS t DH

I/O FFh

tPOR=2ms

t WB

Don’t Care

RY / BY

V IH or V IL

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 10

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

1.9 Write Protect Signal

Erase and Program operations are automatically reset when the Write Protect signal goes Low. The

operations are enabled and disabled, as follows:

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 11

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

1.10 Absolute Maximum Ratings

SYMBOL RATING VALUE UNIT

VCC Power Supply Voltage –0.6 to 4.6 V

VIN Input Voltage –0.6 to 4.6 V

VI/O Input/Output Voltage –0.6 to VCC + 0.3 (≤ 4.6) V

PD Power Dissipation 0.3 W

TSOLDER Soldering Temperature (10 s) 260 °C

TSTG Storage Temperature –55 to 150 °C

TOPR Operating Temperature 0 to 70 °C

Y

AR

1.11 Capacitance

(Ta = 25° C, f = 1 MHz)

IN

SYMBOL PARAMETER CONDITION MIN TYP. MAX UNIT

IM

CIN * Input VIN = 0 V --- 5 10 pF

COUT * Output VOUT = 0 V --- 5 10 pF

EL

* This parameter is per die, is periodically sampled, and is not tested for every device.

PR

1.12 Valid Blocks

SYMBOL PARAMETER MIN TYP. MAX UNIT

NVB Number of Valid Blocks per Die 3933 --- 4096 Blocks

NOTE: The device occasionally contains unusable blocks. Refer to Application Note (6) toward the end of

this document.

The first block (Block 0) is guaranteed to be a valid block at the time of shipment.

The specification for the minimum number of valid blocks is applicable over the device lifetime.

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 12

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

1.13 Recommended DC Operating Conditions

SYMBOL PARAMETER MIN TYP. MAX UNIT

VCC Power Supply Voltage 2.7 --- 3.6 V

ViH High-Level Input Voltage 2.7 V ≤ VCC ≤ 3.6 V 0.8 x VCC --- VCC + 0.3 V

ViL Low-Level Input Voltage 2.7 V ≤ VCC ≤ 3.6 V –0.3 * --- 0.2 x VCC V

* –2 V (pulse width less than 20 ns)

Y

1.14 DC Characteristics

(Ta = 0 to 70°C, VCC = 2.7 V to 3.6 V)

AR

SYMBOL PARAMETER CONDITION MIN TYP. MAX UNIT

IIL Input Leakage Current VIN = 0 V to VCC ±10 µA

IN

ILO Output Leakage Current VOUT = 0 V to VCC ±10 µA

ICCO0 * Power On Reset Current During FFh command input after Power On 50 mA

IM

ICCO1 * Serial Read Current CE = VIL , IOUT = 0 mA, tcycle = 30 ns 50 mA

ICCO2 * Programming Current --- 50 mA

EL

ICCO3 * Erasing Current --- 50 mA

ICCS ** Standby Current CE = VCC – 0.2 V, WP = 0 V/VCC 50 µA

VOH IOH = – 0.4 mA (2.7 V ≤ VCC ≤ 3.6 V) 2.4 V

PR

High-Level Output Voltage

VOL Low-Level Output Voltage IOL = 2.1 mA (2.7 V ≤ VCC ≤ 3.6 V) 0.4 V

IOL

Output Current of RY/BY Pin VOL = 0.4 V (2.7 V ≤ VCC ≤ 3.6 V) 8 mA

(RY/BY)

* per selected active die in the package

** per die in the package

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 13

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

1.15 AC Characteristics and Recommended Operating Conditions

(Ta = 0 to 70°C, VCC = 2.7 V to 3.6 V)

Y

AR

IN

IM

EL

PR

* tWHW is the time from the WE rising edge of the final address cycle to the WE falling edge of the first data cycle.

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 14

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

1.16 AC Test Conditions

Y

AR

IN

IM

EL

PR

1.17 Programming and Erasing Characteristics

(Ta = 0 to 70°C, VCC = 2.7 V to 3.6 V)

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 15

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

2. Address Assignment

Page Address

(PA19 - 0)

00000h Block 0 (Plane 0) Page 0 Byte 0

00080h Block 1 (Plane 1) Page 1 Byte 1

00100h Block 2 (Plane 0) Page 2 Byte 2

00180h Main Bytes

Block 3 (Plane 1)

(8192 Bytes)

Main Blocks 00200h Block 4 (Plane 0)

(4096 Blocks)

00280h Block 5 (Plane 1) Page 125 Byte 8190

Y

Page 126 Byte 8191

Page 127 Byte 8192

AR

7FF00h Block 4094 (Plane 0)

7FF80h (128 Pages)

Block 4095 (Plane 1)

80000h Block 4096 (Plane 0) ECC Bytes

For 32GB (376 Bytes)

Byte 8565

IN

Only: 80080h Block 4097 (Plane 1)

Byte 8566

Main Blocks

(4096 Blocks) Byte 8567

IM

FFF00h Block 8190 (Plane 0)

FFF80h Block 8191 (Plane 1)

EL

PR

Table 1: Addressing

I/O7 I/O6 I/O5 I/O4 I/O3 I/O2 I/O1 I/O0

First Cycle CA7 CA6 CA5 CA4 CA3 CA2 CA1 CA0

CA0 to CA13: Column Address

Second Cycle L L CA13 CA12 CA11 CA10 CA9 CA8

PA0 to PA6: Page Address

Third Cycle PA7 PA6 PA5 PA4 PA3 PA2 PA1 PA0

PA7 to PA19: Block Address

Fourth Cycle PA15 PA14 PA13 PA12 PA11 PA10 PA9 PA8

Fifth Cycle L L L L PA19 PA18 PA17 PA16

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 16

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3. Timing Diagrams

3.1 Write Timing

Y

AR

3.2 Read Timing

IN

IM

EL

PR

Notes:

1. Hold time from RE rising edge is determined by the shorter one of either tRHOH or tREH + tRLOH.

2. When tREH is long, output buffers are disabled by RE=High, and the hold time of data output depends on

tRHOH (30 ns MIN). On this condition, waveforms look like normal serial read mode. (For instance, when tREH

= 30ns, it is tRHOH = 30ns.)

3. When tREH is short, output buffers are not disabled by RE=High, and the hold time of data output depends on

tRLOH (5ns MIN). On this condition, output buffers are disabled by the rising edge of CLE, ALE, CE, or the

falling edge of WE, and waveforms look like Extended Data Output Mode. (For instance, when tREH = 10ns, it is

tRHOH = tREH + tRLOH = 15ns.)

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 17

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.3 Latch Timing for Command/Address/Data

Y

AR

3.4 Command Input Cycle Timing

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 18

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.5 Address Input Cycle Timing

Y

AR

IN

IM

3.6 Data Input Cycle Timing

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 19

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.7 Serial Read Cycle Timing

Y

AR

3.8 Status Read Cycle Timing

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 20

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.9 Read Cycle Timing

Y

AR

IN

IM

3.10 Read Cycle Timing: When Interrupted by Command Enable

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 21

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.11 Read Cycle with Data Cache Timing (1/2)

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 22

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.12 Read Cycle with Data Cache Timing (2/2)

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 23

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.13 Column Address Change in Read Cycle Timing (1/2)

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 24

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.14 Column Address Change in Read Cycle Timing (2/2)

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 25

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.15 Data Output Timing

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 26

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.16 Single Page Program Operation Timing

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 27

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.17 Auto Page Program with Data Cache Operation Timing (1/3)

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 28

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.18 Auto Page Program with Data Cache Operation Timing (2/3)

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 29

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.19 Auto Page Program with Data Cache Operation Timing (3/3)

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 30

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.20 Multi Page Program with Data Cache Operation Timing (1/4)

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 31

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.21 Multi Page Program with Data Cache Operation Timing (2/4)

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 32

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.22 Multi Page Program with Data Cache Operation Timing (3/4)

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 33

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.23 Multi Page Program with Data Cache Operation Timing (4/4)

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 34

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.24 Single Block Erase Timing

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 35

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.25 Multi Block Erase Timing

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 36

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

3.26 ID Read Operation Timing

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 37

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

4. Operation Mode: Logic and Command Tables

4.1 Logic Table

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 38

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

4.2 Command Table

Table 3: Command Table (HEX)

First Second Third Acceptable

Command

Cycle Cycle Cycle while Busy

Auto Page Program with Data Cache (See note 1.) 80 15 –

Column Address Change in Serial Data Output 05 E0 –

Column Address in Serial Data Input 85 – –

ID Read 90 – –

Multi Block Erase 60 60 D0

Multi Page Program 80 11 –

Multi Page Read 60 60 30

Multi Page Read during Multi Page Copy (2) 60 60 3A

Read for Page Copy (2) 00 3A –

Y

Read Start for Last Page in Read cycle with Data Cache 3F – –

Read with Data Cache 31 – –

AR

Reset FF – – O

Serial Data Input 80 – –

Single Block Erase 60 D0 –

IN

Single Page Program 80 10 –

Single Page Program during Multi Page Copy (2) (See note 1.) 8C 11 –

Single Page Program for last page during Page Copy (2) (See note 1.) 8C 10 –

IM

Single Page Program with Data Cache during Page Copy (2) (See note 1.) 8C 15 –

Single Page Read 00 30 –

Status Read 70 – – O

EL

Status Read for Multi Page Program or Multi Block Erase 71 – – O

Notes: 1. Input of a command other than those specified in Table 3 is prohibited. Stored data

can be corrupted if an unknown command is entered during the command cycle.

PR

2. During the Busy state, do not input any command except 70h(71h) and FFh.

Table 4 shows the operation states for Read mode, when tREH is long.

Table 4. Read Mode Operation States

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 39

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

5. Device Operation

5.1 Read Mode

Y

AR

IN

IM

5.2 Random Column Address Change in Read Cycle

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 40

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

5.3 Read Operation with Read Cache

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 41

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

5.4 Multi Page Read Operation

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 42

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 43

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 44

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

5.5 Single Page Program Operation

Y

AR

IN

IM

EL

5.6 Random Column Address Change in Single Page Program Operation

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 45

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

5.7 Auto Page Program with Data Cache Operation

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 46

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 47

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

5.8 Multi Page Program with Data Cache Operation

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 48

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 49

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

Internal Addressing in Relation to the Planes

Address Input Restriction for Multi Page Program w/ Data Cache Operation

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 50

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

Operating Restriction During Multi Page Program w/ Data Cache Operation

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 51

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

5.9 Page Copy (2)

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 52

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 53

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

5.10 Multi Page Copy (2)

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 54

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

Y

AR

IN

IM

EL

5.11 Single Block Erase

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 55

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

5.12 Multi Block Erase

Y

AR

Internal Addressing in Relation to the Planes

IN

IM

EL

Address Input Restriction for Multi Block Erase Operation

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 56

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

5.13 ID Read

The device contains ID codes which can be used to identify the device type, the manufacturer, and

features of the device. The ID codes can be read out under the following timing conditions:

Y

AR

IN

IM

Table 5: CMD 90h ID Code

Address

EL

Chip 00h 01h 02h 03h 04h 05h 06h 07h

Maker Device Multi- Block Plane Technology

Reserved Reserved

Code Code * Die * Size Info * Code

PR

45h D7h 94h 32h 76h 54h

8GB

SanDisk 32Gb 1-die 1MB 2-plane 43nm

45h D7h 94h 32h 76h 54h

16GB

SanDisk 32Gb 1-die 1MB 2-plane 43nm

45h DEh 95h 32h 7Ah 54h

32GB

SanDisk 64Gb 2-die 1MB 4-plane 43nm

* Per CE pin

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 57

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

5.14 Status Read

The device automatically implements the execution and verification of the Program and Erase operations.

The Status Read function is used to monitor the Ready/Busy status of the device, determine the result

(pass / fail) of a Program or Erase operation, and determine whether the device is in Protect mode. The

device status is output via the I/O port using RE after a “70h” command input. The Status Read can also

be used during a Read operation to find out the Ready/Busy status.

The resulting information is outlined in Table 6.

Table 6: Status Output

Page Program Cache

Definition Cache Read

Block Erase Program

Chip Status1

I/O0 Pass/Fail Pass/Fail Invalid

Pass: 0 Fail: 1

Chip Status2

Y

I/O1 Invalid Pass/Fail Invalid

Pass: 0 Fail: 1

I/O2 Not Used 0 0 0

AR

I/O3 Not Used 0 0 0

I/O4 Not Used 0 0 0

Page Buffer Ready/Busy

I/O5 Ready/Busy Ready/Busy Ready/Busy

IN

Ready: 1 Busy: 0

Data Cache Ready/Busy

I/O6 Ready/Busy Ready/Busy Ready/Busy

Ready: 1 Busy: 0

IM

Write Protect

I/O7 Write Protect Write Protect Write Protect

Not Protected :1 Protected: 0

The Pass/Fail status on I/O0 and I/O1 is valid only during a Program/Erase operation when the device is

EL

in the Ready state.

Chip Status 1:

During a Single Page Program or Single Block Erase operation, this bit indicates the pass/fail result.

PR

During a Auto Page Programming with Data Cache operation, this bit shows the pass/fail results of the

current page program operation, and therefore this bit is valid only when I/O5 shows the Ready state.

Chip Status 2:

This bit shows the pass/fail result of the previous page program operation during Auto Page Programming

with Data Cache. This status is valid when I/O6 shows the Ready State.

The status output on the I/O5 is the same as that of I/O6 if the command input just before the 70h is not

15h or 31h.

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 58

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

Application Example

Y

AR

IN

IM

EL

PR

5.15 Reset

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 59

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 60

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

6. Application Notes and Comments

(1) Acceptable Commands After a Serial Input “80h” Command

Y

AR

IN

(2) Addressing for Program Operations

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 61

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

(3) Status Read During a Read Operation

Y

AR

IN

(4) Page Programming Failure

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 62

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

(5) When Six Address Cycles Are Input

Y

AR

IN

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 63

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

(6) Invalid Blocks (bad blocks)

A device occasionally contains unusable blocks. Therefore, the following issues must be

recognized:

• At the time of shipment, the bad block information is marked

on each bad block. Do not perform an erase operation on bad

blocks; it might be impossible to recover the bad block

information if the information is erased.

• Check for any bad blocks after installing the device into the

system. Refer to the test flow for bad block detection. Bad

blocks that are detected by the test flow must be managed as

unusable blocks by the system.

• Up to 4% of all blocks available on a die might be marked as

bad blocks throughout the lifetime of the device. The first

logical block on each die is guaranteed to be good, and each

block identified as good at shipment does not have

Y

program/erase status failure upon the first program/erase

cycle. A bad block does not affect the performance of good

blocks, because it is isolated from the bit lines by select gates.

AR

The number of valid blocks over the device lifetime is as follows:

MIN TYP MAX UNITS

IN

Valid (Good) Block Number 3933 –– 4096 Block

Bad Block Test Flow

IM

With regard to invalid blocks, the last page of the bad block is not all FFh.

Start

EL

Block No. = 1

PR

Read FFh Check Fail

Any Byte of

the Last Page

Block No. = Block No. + 1 Entry Bad Block *1

Pass

No

Last Block?

Yes

End

*1: No erase operations are allowed on detected bad blocks.

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 64

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

(7) Failure Phenomena for Program and Erase Operations

Y

AR

IN

IM

EL

PR

(8) Power Loss

Do not turn off the power before write/erase operation is complete. Avoid using the device

when the battery is low. Power shortage and/or power failure before a write/erase operation

is complete causes loss of data and/or damage to data.

(9) Reset Command

If an FF reset command is input before completion of a write operation to page B, it might

cause damage to data, not only to the programmed page, but also to the adjacent page A.

For more information about page A and B, see “Operating Restriction During Multi Page

Program w/ Data Cache Operation” on Page 48.

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 65

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

(10) Reliability Guidance

Although random bit errors might occur during use, it does not necessarily mean that a block

is bad. Generally, a block should be marked as bad when a program status failure or erase

status failure is detected. The other failure modes might be recovered by a block erase.

ECC treatment for read data is mandatory, due to the following Data Retention and Read

Disturb failures.

• Write/Erase Endurance

Write/Erase endurance failures might occur in a cell, page, or block, and are detected by

doing a status read after either an auto program or auto block erase operation. The

cumulative bad block count increases along with the number of write/erase cycles.

• Data Retention

The data in memory might change after a certain amount of storage time. This is due to

charge loss or charge gain. After block erasure and reprogramming, the block might

become usable again.

Y

• Read Disturb

A read operation might disturb the data in memory. The data might change due to charge

AR

gain. Usually, bit errors occur on other pages in the block, not the page being read. After

a large number of read cycles (between block erases), a tiny charge might build up and

can cause a cell to be soft programmed to another state. After block erasure and

reprogramming, the block might become usable again.

All reliability-related parameters and results are measured using a random data pattern

IN

stored in memory. Results might differ if other data patterns are used.

IM

EL

PR

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 66

SDZNMM(B/C/D)HER-0(08/16/32)G

43nm 8GB / 16GB / 32GB 4LC 3V NAND Flash Memory Data Sheet

7. Package Marking Specification

Y

AR

IN

IM

EL

PR

Table 7: SanDisk Internal Codes

Product Description SanDisk Part Number

8GB SDZNMMBHER – 008G

16GB SDZNMMCHER – 016G

32GB SDZNMMDHER – 032G

Preliminary Version, rev1.3 SanDisk Proprietary and Confidential page 67

You might also like

- Et Lake U PDGDocument708 pagesEt Lake U PDGjayixi4827100% (1)

- Lutron MHB-382SD Dattalogger PDFDocument20 pagesLutron MHB-382SD Dattalogger PDFFernando Mar100% (1)

- Nuvoton NCT7717U Datasheet V111Document19 pagesNuvoton NCT7717U Datasheet V111Tomy Aditya PratamaNo ratings yet

- USM 32X Operating Manual PDFDocument188 pagesUSM 32X Operating Manual PDFcorey jacobsNo ratings yet

- TLE5012B: 1 FeaturesDocument51 pagesTLE5012B: 1 FeaturesAbdi PrasetyoNo ratings yet

- Infineon TLE4998S8D DS v01 - 01 ENDocument24 pagesInfineon TLE4998S8D DS v01 - 01 ENMohammad SharghiNo ratings yet

- DDR3 KeyStone ArchitectureDocument121 pagesDDR3 KeyStone ArchitectureSyed ShafiNo ratings yet

- CF Industrial Data Sheet enDocument140 pagesCF Industrial Data Sheet end.simNo ratings yet

- TLE4998C4 DataSheet v01 - 00 enDocument44 pagesTLE4998C4 DataSheet v01 - 00 enDhashana MoorthyNo ratings yet

- 2132 PmaDocument48 pages2132 PmaAlanNo ratings yet

- Modulo Nand Flash ARDUINODocument78 pagesModulo Nand Flash ARDUINOWilmer Yesid Granados JaimesNo ratings yet

- X18 SAS Product ManualDocument62 pagesX18 SAS Product ManualnarciszuNo ratings yet

- Usx 10 PmbuDocument40 pagesUsx 10 PmbuYulian Stephan Zuleta MelendezNo ratings yet

- Ic25n020atda04 Travelstar 20 GB Hard DriveDocument220 pagesIc25n020atda04 Travelstar 20 GB Hard DriveromluxlightingNo ratings yet

- HCK0 Samsung Datasheet DDR3SDRAMDocument64 pagesHCK0 Samsung Datasheet DDR3SDRAMNilton OliveiraNo ratings yet

- S29CD016J Memória FlashDocument15 pagesS29CD016J Memória FlashMarcelo OemNo ratings yet

- Epir Motion Detection Zdots SBC: Zepir0Aas01SbcgDocument58 pagesEpir Motion Detection Zdots SBC: Zepir0Aas01Sbcghunterst5024100% (4)

- 013928ds k4b1g1646g X16only Rev111Document64 pages013928ds k4b1g1646g X16only Rev111Legna80No ratings yet

- Openrisc 1200 Ip Core Specification (Preliminary Draft)Document54 pagesOpenrisc 1200 Ip Core Specification (Preliminary Draft)Chandan MalleshNo ratings yet

- 204pin Unbuffered SODIMM Based On 4Gb E-Die: DatasheetDocument39 pages204pin Unbuffered SODIMM Based On 4Gb E-Die: DatasheetYiu Win HhuNo ratings yet

- ST6208C/ST6209C ST6210C/ST6220C: 8-Bit Mcus With A/D Converter, Two Timers, Oscillator Safeguard & Safe ResetDocument104 pagesST6208C/ST6209C ST6210C/ST6220C: 8-Bit Mcus With A/D Converter, Two Timers, Oscillator Safeguard & Safe ResetJananrdhana CpNo ratings yet

- W25Q256JV DTR RevI 10182022 PlusDocument118 pagesW25Q256JV DTR RevI 10182022 PlusDavid duranNo ratings yet

- S25FL116K 00 PDFDocument79 pagesS25FL116K 00 PDFfabioakioNo ratings yet

- HMS87C1304 (2) A HMS87C1204 (2) A HMS87C1104 (2) A: User's ManualDocument88 pagesHMS87C1304 (2) A HMS87C1204 (2) A HMS87C1104 (2) A: User's ManualBhadreshkumar SharmaNo ratings yet

- Samsung ChipsetDocument64 pagesSamsung ChipsetEgie WijaksonoNo ratings yet

- c6713 DSPDocument27 pagesc6713 DSPGhulam MujtabaNo ratings yet

- Chip Siemens Sle4442 Developed ManualDocument35 pagesChip Siemens Sle4442 Developed ManualsitiounoNo ratings yet

- W39V040B Data Sheet 512K 8 Cmos Flash Memory With LPC InterfaceDocument33 pagesW39V040B Data Sheet 512K 8 Cmos Flash Memory With LPC InterfacexoxovasNo ratings yet

- ddr3 SamsungDocument67 pagesddr3 Samsung0op9a3nNo ratings yet

- Infns21548 1 PDFDocument35 pagesInfns21548 1 PDFJason RicoNo ratings yet

- Datasheet PDFDocument29 pagesDatasheet PDFFRANCISCO NARVAEZNo ratings yet

- GD25Q10&512 Rev1.5 PDFDocument38 pagesGD25Q10&512 Rev1.5 PDFmirage0706No ratings yet

- EB7SMDocument18 pagesEB7SMAfif ZarradNo ratings yet

- TS5A3159 1 - SPDT Analog Switch: 1 Features 3 DescriptionDocument29 pagesTS5A3159 1 - SPDT Analog Switch: 1 Features 3 DescriptionDaniel VargasNo ratings yet

- Integrado TS250'Document61 pagesIntegrado TS250'julio sotoNo ratings yet

- W25 N 01 GvzeigDocument68 pagesW25 N 01 GvzeigFabio Da Silva Assunçao AssunçaoNo ratings yet

- Data SheetDocument56 pagesData SheetfaycelNo ratings yet

- ST62T108C6Document104 pagesST62T108C6أبو أنس المسلمNo ratings yet

- Fp2 Analog e PanasonicDocument124 pagesFp2 Analog e PanasonicUsman KhanNo ratings yet

- S905X AmlogicDocument528 pagesS905X AmlogicIsnaini RahmawatiNo ratings yet

- Infineon ICE2HS01G DS v02 01 En-1731445Document30 pagesInfineon ICE2HS01G DS v02 01 En-1731445marcoNo ratings yet

- 96mpaa 2.8g 2mam3t DatasheetDocument21 pages96mpaa 2.8g 2mam3t DatasheetArimitra ChakrabartiNo ratings yet

- SATA Product Manual: Standard Models SED-FIPS (140-2) ModelsDocument39 pagesSATA Product Manual: Standard Models SED-FIPS (140-2) Modelscolab aNo ratings yet

- dm00260799 Writing To Nonvolatile Memory Without Disrupting Code Execution On Microcontrollers of The stm32l0 and stm32l1 Series StmicroelectronicsDocument16 pagesdm00260799 Writing To Nonvolatile Memory Without Disrupting Code Execution On Microcontrollers of The stm32l0 and stm32l1 Series Stmicroelectronicsusha raman adapaNo ratings yet

- DAVICOM Semiconductor, Inc.: 10/100 Mbps Fast Ethernet Physical Layer Single Chip TransceiverDocument45 pagesDAVICOM Semiconductor, Inc.: 10/100 Mbps Fast Ethernet Physical Layer Single Chip Transceivernguyentienduy1512No ratings yet

- Cjoy Operator Terminal Hardware Module DescriptionDocument16 pagesCjoy Operator Terminal Hardware Module Descriptionedi2805No ratings yet

- XTW2020 1589249333000Document36 pagesXTW2020 1589249333000ziswilerNo ratings yet

- w25m512jv Revd 09052017Document91 pagesw25m512jv Revd 09052017nanda09lvNo ratings yet

- Djsa210 Travelstar 10 GB Hard DriveDocument211 pagesDjsa210 Travelstar 10 GB Hard DriveENZONo ratings yet

- K4B8G1646Q SamsungDocument66 pagesK4B8G1646Q SamsungHKmobileNo ratings yet

- SN 74 LVC 1 G 04Document44 pagesSN 74 LVC 1 G 04zigmund zigmundNo ratings yet

- SN 74 LVC 1 G 04Document42 pagesSN 74 LVC 1 G 04Jesus PachecoNo ratings yet

- SN 74 LVC 1 G 04Document43 pagesSN 74 LVC 1 G 04uhmgawaNo ratings yet

- DS - MM32F031xx HoverboardDocument74 pagesDS - MM32F031xx HoverboardAl AlveraNo ratings yet

- M25P80Document53 pagesM25P80api-3736976No ratings yet

- St7Lite0, St7Superlite: 8-Bit Mcu With Single Voltage Flash Memory, Data Eeprom, Adc, Timers, SpiDocument122 pagesSt7Lite0, St7Superlite: 8-Bit Mcu With Single Voltage Flash Memory, Data Eeprom, Adc, Timers, SpiadeelNo ratings yet

- Instructions For Digitrip RMS 510 Trip Unit: Instruction Leaflet I. L. 29-885DDocument20 pagesInstructions For Digitrip RMS 510 Trip Unit: Instruction Leaflet I. L. 29-885DBruno MilanNo ratings yet

- AMR User DescriptionDocument14 pagesAMR User DescriptionVinodNo ratings yet

- XDD 1000C.S10 Receiver and Processor Users Manual Part 1 374022Document150 pagesXDD 1000C.S10 Receiver and Processor Users Manual Part 1 374022tntkikNo ratings yet

- Smart Card Applications: Design models for using and programming smart cardsFrom EverandSmart Card Applications: Design models for using and programming smart cardsNo ratings yet

- WDocument19 pagesWSatvik HardatNo ratings yet

- SCH Te0727 02 41C34Document14 pagesSCH Te0727 02 41C34Satvik HardatNo ratings yet

- Snapdragon 865 Mobile HDK Product Brief - 87 pn003 1 PDFDocument2 pagesSnapdragon 865 Mobile HDK Product Brief - 87 pn003 1 PDFSatvik HardatNo ratings yet

- HP 15 Ae019TX ABW50 LA-C501P Rev 10 SchematicsDocument63 pagesHP 15 Ae019TX ABW50 LA-C501P Rev 10 SchematicsSatvik HardatNo ratings yet

- Tinkerfest - ViiiDocument1 pageTinkerfest - ViiiSatvik HardatNo ratings yet

- Hades Schematic Print PDFDocument6 pagesHades Schematic Print PDFSatvik HardatNo ratings yet

- Intel® Pentium® and Celeron® Processor N-And J - Series: Datasheet Volume 3 of 3Document4,654 pagesIntel® Pentium® and Celeron® Processor N-And J - Series: Datasheet Volume 3 of 3Satvik HardatNo ratings yet

- qrb5165 Soc Product Brief - 87 28730 1 BDocument2 pagesqrb5165 Soc Product Brief - 87 28730 1 BSatvik HardatNo ratings yet

- ATL Tinkerpreneur 2022 Brochure PDFDocument14 pagesATL Tinkerpreneur 2022 Brochure PDFSatvik HardatNo ratings yet

- stm32h750vbt6 PDFDocument335 pagesstm32h750vbt6 PDFSatvik HardatNo ratings yet

- Pgurl 12192663594361198Document4 pagesPgurl 12192663594361198Satvik HardatNo ratings yet

- BeagleV V0.9wbergerDocument21 pagesBeagleV V0.9wbergerSatvik HardatNo ratings yet

- Schematic - STM32H743I-F767I Core Board - 2020-11-19 - 00-05-36Document1 pageSchematic - STM32H743I-F767I Core Board - 2020-11-19 - 00-05-36Satvik HardatNo ratings yet

- 114atom c2000 Microserver DatasheetDocument746 pages114atom c2000 Microserver DatasheetSatvik HardatNo ratings yet

- Sa800u Baseboard HWDocument12 pagesSa800u Baseboard HWSatvik HardatNo ratings yet

- Adl 8104Document23 pagesAdl 8104Satvik HardatNo ratings yet

- MCT 8316 Awghw 4 GDDocument178 pagesMCT 8316 Awghw 4 GDSatvik HardatNo ratings yet

- Fla Unit 4 and 5Document198 pagesFla Unit 4 and 5lard BaringNo ratings yet

- CTP 11 - Status of Minor Bridges 17-03-2019Document2 pagesCTP 11 - Status of Minor Bridges 17-03-2019Eswara PrasadNo ratings yet

- imageRUNNERFirmwareChart 2Document3 pagesimageRUNNERFirmwareChart 2jesus maximiliano100% (1)

- Hasee Pricelist On JanurayDocument3 pagesHasee Pricelist On JanuraywahajnayatelNo ratings yet

- S-Chapter 3Document43 pagesS-Chapter 3ranaNo ratings yet

- Multi Row Fetch, INSERT and Get Diagnostics How To Put It Into CodeDocument40 pagesMulti Row Fetch, INSERT and Get Diagnostics How To Put It Into CodeKalimuthu SangarNo ratings yet

- Practical File ContentsDocument59 pagesPractical File ContentsHarshit SethiNo ratings yet

- Hướng dẫn kết nối board plc FK3UDocument7 pagesHướng dẫn kết nối board plc FK3UHiệp Trần100% (1)

- Previous Year TCS Coding QuestionDocument19 pagesPrevious Year TCS Coding QuestionMAHESH VNo ratings yet

- Vignesh RameshDocument4 pagesVignesh RameshMr 360No ratings yet

- Concepts and Techniques: Data MiningDocument52 pagesConcepts and Techniques: Data MiningindiraNo ratings yet

- HP StorageWorks MSL Library Extender UserDocument96 pagesHP StorageWorks MSL Library Extender Uservanessa escalonaNo ratings yet

- Mathematics: Blockchain Technology For Secure Accounting Management: Research Trends AnalysisDocument26 pagesMathematics: Blockchain Technology For Secure Accounting Management: Research Trends AnalysisAlesya Julian LauendeNo ratings yet

- Session 13a Rysman Two Sided MktsDocument43 pagesSession 13a Rysman Two Sided MktsDanielaNo ratings yet

- RGPV NotesDocument90 pagesRGPV NotesIslamic India100% (1)

- Software Engineering Module 3Document7 pagesSoftware Engineering Module 3amantNo ratings yet

- User Manual: I-Thermo 163Mg, 64Mg and I-Thermo 62Lg, 163Lg Revision of The Software BPGTH - 1 - 00Document36 pagesUser Manual: I-Thermo 163Mg, 64Mg and I-Thermo 62Lg, 163Lg Revision of The Software BPGTH - 1 - 00MelanyNo ratings yet

- 02 Laboratory Exercise 1Document3 pages02 Laboratory Exercise 1Antiporta KenNo ratings yet

- SBC Installation InstructionsDocument2 pagesSBC Installation InstructionsHevon YangNo ratings yet

- Secure IoT Data Using BlockchainDocument18 pagesSecure IoT Data Using BlockchainAsicsNewNo ratings yet

- Jibin Grey 3Document2 pagesJibin Grey 3jibingrey augustineNo ratings yet

- Results For Panalo Ako Translation From Tagalog To English: Ask GoogleDocument6 pagesResults For Panalo Ako Translation From Tagalog To English: Ask GoogleLebron FajardoNo ratings yet

- Number Theory 6 Solutions UHSMCDocument6 pagesNumber Theory 6 Solutions UHSMCWalker KroubalkianNo ratings yet

- Estimate Motor Parameters by Using Motor Control Blockset Parameter Estimation Tool - MATLAB & SimulinkDocument5 pagesEstimate Motor Parameters by Using Motor Control Blockset Parameter Estimation Tool - MATLAB & SimulinkarashengNo ratings yet

- S - 4 HanaDocument27 pagesS - 4 Hanaavnit anandNo ratings yet

- Fundamentals of Artificial Intelligence - Unit 3 - Week 1 - AI and AI Problem SolvingDocument4 pagesFundamentals of Artificial Intelligence - Unit 3 - Week 1 - AI and AI Problem Solvingabdul.azeezNo ratings yet

- Careandfeedingvios Aug2117Document46 pagesCareandfeedingvios Aug2117Jayson JHBZANo ratings yet

- Fall 2022 - CS101 - 2Document4 pagesFall 2022 - CS101 - 2Lisa PowellNo ratings yet

- Case+study-+IIITB+ +upGrad+Template-+Solution+doc.Document26 pagesCase+study-+IIITB+ +upGrad+Template-+Solution+doc.Kartikey Shukla100% (2)

- Application of Regular Expression in Search Engine OptimizationDocument12 pagesApplication of Regular Expression in Search Engine OptimizationDevanshu AgarwalNo ratings yet