Professional Documents

Culture Documents

Op-Amp 3

Op-Amp 3

Uploaded by

azriedarmawan5Copyright:

Available Formats

You might also like

- Automated Broad and Narrow Band Impedance Matching for RF and Microwave CircuitsFrom EverandAutomated Broad and Narrow Band Impedance Matching for RF and Microwave CircuitsNo ratings yet

- Major ProjectDocument28 pagesMajor ProjectNeeraj MishraNo ratings yet

- The Designer's Guide To Analog and Mixed-Signal Modeling Illustrated With VHDL-AMS and MASTDocument356 pagesThe Designer's Guide To Analog and Mixed-Signal Modeling Illustrated With VHDL-AMS and MASTAmaniDarwishNo ratings yet

- Design and Analysis of Two Stage CMOS Operational Amplifier Using 0.13 M TechnologyDocument6 pagesDesign and Analysis of Two Stage CMOS Operational Amplifier Using 0.13 M TechnologyJunaid KhanNo ratings yet

- Research Paper On AmplifierDocument5 pagesResearch Paper On Amplifiereh1dvt0m100% (1)

- Design and Layout of 1.8V Two Stage CMOS Operational Amplifier (Unbuffered)Document5 pagesDesign and Layout of 1.8V Two Stage CMOS Operational Amplifier (Unbuffered)sudarshan poojaryNo ratings yet

- Op-Amp ReportDocument27 pagesOp-Amp ReportGaurav Singh100% (15)

- Opamp Desiging Project ReportDocument6 pagesOpamp Desiging Project ReportTarun PrakashNo ratings yet

- Koneru Lakshmaiah Education Foundation: Department of Electronics and Communication EngineeringDocument12 pagesKoneru Lakshmaiah Education Foundation: Department of Electronics and Communication EngineeringLakshmi JagupillaNo ratings yet

- Modelling of Operational Amplifier by Using CMOS Technology: VSRD-IJEECE, Vol. 2 (6), 2012, 330-336Document7 pagesModelling of Operational Amplifier by Using CMOS Technology: VSRD-IJEECE, Vol. 2 (6), 2012, 330-336Akash VermaNo ratings yet

- MSD Aat (Ec144, Ec171)Document7 pagesMSD Aat (Ec144, Ec171)srusti.ec21No ratings yet

- Design of CMOS Based Biosensor OTA 2018Document10 pagesDesign of CMOS Based Biosensor OTA 2018RajeeNo ratings yet

- High Speed Analog Design and Application Seminar: From Texas InstrumentsDocument39 pagesHigh Speed Analog Design and Application Seminar: From Texas InstrumentshaoyuqianNo ratings yet

- Robotics 17Document27 pagesRobotics 17setsindia3735No ratings yet

- Amplifier DesignDocument20 pagesAmplifier DesignCurtinNo ratings yet

- Amplifier Build and Design: Faculty of Engineering and Applied ScienceDocument21 pagesAmplifier Build and Design: Faculty of Engineering and Applied ScienceFarrukh ZamanNo ratings yet

- 2stage Opamp 90nmDocument6 pages2stage Opamp 90nmsabbir.bhuyianNo ratings yet

- Power Amplifier Design ThesisDocument6 pagesPower Amplifier Design Thesisdwm7sa8p100% (1)

- Microwave Amplifier Design (Part 1) : San Jose State University Department of Electrical EngineeringDocument22 pagesMicrowave Amplifier Design (Part 1) : San Jose State University Department of Electrical EngineeringTran NamNo ratings yet

- Design of High Performance Cmos Comparator Using 90nm TechnologyDocument6 pagesDesign of High Performance Cmos Comparator Using 90nm TechnologyRAJANo ratings yet

- 2020 SEO Operational Amplifiers r1.0Document6 pages2020 SEO Operational Amplifiers r1.0Okiring JonahNo ratings yet

- Irjet V4i5125 PDFDocument5 pagesIrjet V4i5125 PDFAnonymous plQ7aHUNo ratings yet

- Linear and Digital Ic ApplicationsDocument47 pagesLinear and Digital Ic Applicationsభార్గవ్ కుమార్100% (1)

- Power Amplifier Application NoteDocument3 pagesPower Amplifier Application NoteSanthos KumarNo ratings yet

- A Study and Analysis of Two Stage Single Ended CMOS OP-AMPDocument9 pagesA Study and Analysis of Two Stage Single Ended CMOS OP-AMPsanjeevsoni64No ratings yet

- A High Performance CMOS Band - Gap Reference Circuit DesignDocument6 pagesA High Performance CMOS Band - Gap Reference Circuit DesignKhaja Mujeebuddin QuadryNo ratings yet

- Cmos Two Stage OpamppublishedDocument5 pagesCmos Two Stage Opamppublisheddeepak pandeyNo ratings yet

- An Analysis and Design of High Performance Power Consumption Double Tail Comparator Using Gated Clock and Power Gating TechniquesDocument7 pagesAn Analysis and Design of High Performance Power Consumption Double Tail Comparator Using Gated Clock and Power Gating TechniquesIJIRSTNo ratings yet

- Design of Two Stage Op-AmpDocument4 pagesDesign of Two Stage Op-AmpWARSE JournalsNo ratings yet

- 118A GaN HEMT Class AB RF Power AmplifierDocument4 pages118A GaN HEMT Class AB RF Power AmplifierNarasimha SunchuNo ratings yet

- Report About Operational Amplifiers 32020245Document6 pagesReport About Operational Amplifiers 32020245mohamedmohamedahmed172No ratings yet

- Electronics Laboratory ReportDocument6 pagesElectronics Laboratory ReportJohn Vincent SacloloNo ratings yet

- UNIT-1 Basics of Operational Amplifiers: EC8453-Linear Integrated Circuits Dept of ECE/PECDocument16 pagesUNIT-1 Basics of Operational Amplifiers: EC8453-Linear Integrated Circuits Dept of ECE/PECIniyan RaviNo ratings yet

- Sri Lanka Institute of Information Technology: EN16544246 W.A.M.Ranasinghe Group - 05Document13 pagesSri Lanka Institute of Information Technology: EN16544246 W.A.M.Ranasinghe Group - 05Shashini MaldeniyaNo ratings yet

- Comparison of BW For RC Coupled Single Stage and Multi Stage AmplifieDocument6 pagesComparison of BW For RC Coupled Single Stage and Multi Stage AmplifieFaras SmansaNo ratings yet

- Design and Development of Novel WeighingDocument4 pagesDesign and Development of Novel WeighingaatifdNo ratings yet

- A 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliDocument4 pagesA 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliAnika TahsinNo ratings yet

- 2-15-1381147174-25 .Design of 1 V.FULL PDFDocument10 pages2-15-1381147174-25 .Design of 1 V.FULL PDFABHILASH RAINo ratings yet

- Assignment Brief - Unit22 Asst (IVed) .1Document11 pagesAssignment Brief - Unit22 Asst (IVed) .1Kalana wickramanayakaNo ratings yet

- Operational Transconductance Amplifier Research PaperDocument6 pagesOperational Transconductance Amplifier Research PaperafeawjjwpNo ratings yet

- Which Amplifier Is Used To Provide Increased BandwidthDocument10 pagesWhich Amplifier Is Used To Provide Increased BandwidthjackNo ratings yet

- New Lab Manual (ECA)Document50 pagesNew Lab Manual (ECA)Shrinivas SaptalakarNo ratings yet

- ADE - Pspice Lab ManualDocument12 pagesADE - Pspice Lab ManualShashiNo ratings yet

- Polytechnic of Namibia School of Engineering Electrical Engineering DepartmentDocument17 pagesPolytechnic of Namibia School of Engineering Electrical Engineering DepartmentDarshan Rai KanungoNo ratings yet

- Inverter Circuit ThoeryDocument8 pagesInverter Circuit ThoeryAbhishek SainiNo ratings yet

- Instrumentation AmplifierDocument6 pagesInstrumentation Amplifiersarpanch100% (2)

- High Power Amplifier With Maximized Efficiency: by Bumjin KimDocument56 pagesHigh Power Amplifier With Maximized Efficiency: by Bumjin Kimluis lopezNo ratings yet

- Bandwidth Extension in CMOS With Optimized On-Chip InductorsDocument10 pagesBandwidth Extension in CMOS With Optimized On-Chip InductorsAlex WongNo ratings yet

- Schmitt TriggerDocument58 pagesSchmitt TriggerCharles BurgosNo ratings yet

- Opamp Design StepsDocument4 pagesOpamp Design StepspankajNo ratings yet

- 4 Differential Amplifier With OutputDocument5 pages4 Differential Amplifier With Outputmanishkavi89No ratings yet

- Differential Amplifier ThesisDocument8 pagesDifferential Amplifier Thesisbsqjpnxd100% (2)

- Isscc2022 000109CLDocument16 pagesIsscc2022 000109CLdashuai huaNo ratings yet

- SR21622171146Document4 pagesSR21622171146Kini FamilyNo ratings yet

- Literature Review of AmplifierDocument6 pagesLiterature Review of Amplifierea7sfn0f100% (1)

- 19BEC1211 - ClassB - Amplifier - AEC - WEEK 8Document6 pages19BEC1211 - ClassB - Amplifier - AEC - WEEK 8Tom ShibuNo ratings yet

- ECA ManualDocument62 pagesECA ManualAnonymous gP8ivl7fNo ratings yet

- Lab Experiment DCDocument7 pagesLab Experiment DCKumar ShashankNo ratings yet

- Ad844 PDFDocument20 pagesAd844 PDFkavi_mishra92No ratings yet

- rfrxd0420 PDFDocument32 pagesrfrxd0420 PDFYaroslavNo ratings yet

- Cold Junction Compensation PDFDocument10 pagesCold Junction Compensation PDFAbhayy DevNo ratings yet

- Affiliated Institutions Anna University, Chennai Regulations - 2009 Curriculum Ii To Iv Semesters (Full Time) M.E. Applied ElectronicsDocument21 pagesAffiliated Institutions Anna University, Chennai Regulations - 2009 Curriculum Ii To Iv Semesters (Full Time) M.E. Applied ElectronicsRamya VNo ratings yet

- ELEC2507 SummerCourse PA Assigned Problems Summer2021Document1 pageELEC2507 SummerCourse PA Assigned Problems Summer2021Ambar MendezNo ratings yet

- Op Amp MCQsDocument4 pagesOp Amp MCQsMuhammad Tousiq67% (3)

- CI SMDMC 33078Document15 pagesCI SMDMC 33078Djalma MoreiraNo ratings yet

- Hardware Design of Seismic Sensors in Wireless SenDocument8 pagesHardware Design of Seismic Sensors in Wireless SenpabloNo ratings yet

- An Open-Ended Laboratory System With Computer-Aided Simulation For Undergraduate Electronic EngineeringDocument5 pagesAn Open-Ended Laboratory System With Computer-Aided Simulation For Undergraduate Electronic Engineeringpmahesh268No ratings yet

- Unit 2: Definition of IcDocument26 pagesUnit 2: Definition of Icsai kiranNo ratings yet

- Baxandall Tone ControlDocument7 pagesBaxandall Tone ControlSheeNo ratings yet

- Pulse Oximeter DesignDocument31 pagesPulse Oximeter DesignPraba KaranNo ratings yet

- Bipolar Stepper Motor Control CircuitDocument3 pagesBipolar Stepper Motor Control CircuitArda AkberkNo ratings yet

- LM4766T DatasheetDocument14 pagesLM4766T DatasheetNikoinekoNo ratings yet

- Source:: Source: Op-Amps and Linear Integrated Circuits, Ramakant A.GayakwadDocument2 pagesSource:: Source: Op-Amps and Linear Integrated Circuits, Ramakant A.GayakwadBatool HerzallahNo ratings yet

- Electronics & Communication EngineeringDocument43 pagesElectronics & Communication EngineeringAtul Prakash DwivediNo ratings yet

- Analysis of The Impact of High-Order Integrator Dynamics On SC Sigma-Delta Modulator Performances-Q2KDocument13 pagesAnalysis of The Impact of High-Order Integrator Dynamics On SC Sigma-Delta Modulator Performances-Q2Kjulio perezNo ratings yet

- Lect26 OMP AMPDocument14 pagesLect26 OMP AMPJason LeeNo ratings yet

- Experiment 1 Electronics 1 Final 1.Document50 pagesExperiment 1 Electronics 1 Final 1.Neekita Chamane100% (4)

- Report - Automatic Power Factor Improvement Using ArduinoDocument27 pagesReport - Automatic Power Factor Improvement Using ArduinoLynn LucyNo ratings yet

- AD215Document12 pagesAD215gmludNo ratings yet

- A Digital-To-Analog Converter (DAC) Block Diagram.: Introduction To Microprocessor-Based ControlDocument3 pagesA Digital-To-Analog Converter (DAC) Block Diagram.: Introduction To Microprocessor-Based Controlnovo orderNo ratings yet

- B.Tech ELECTRICAL Engineering (AKU Syllabus) SEMESTER-VIIDocument2 pagesB.Tech ELECTRICAL Engineering (AKU Syllabus) SEMESTER-VIIkrishna mohan haitNo ratings yet

- Opax607 50-Mhz, Low-Power, Gain of 6-V/V Stable, Rail-To-Rail Output Cmos Operational AmplifierDocument43 pagesOpax607 50-Mhz, Low-Power, Gain of 6-V/V Stable, Rail-To-Rail Output Cmos Operational AmplifierMichael TaftNo ratings yet

- Ina 102Document13 pagesIna 102Erick GiioNo ratings yet

- What Effect Does Direct Coupling Have On A Two Stage BJT AmplifierDocument63 pagesWhat Effect Does Direct Coupling Have On A Two Stage BJT Amplifierzraider50% (2)

- Cmos Ota ThesisDocument5 pagesCmos Ota Thesislisabrownolathe100% (2)

- Biju Patnik University of Technology: Computer Science & Engineering (Cse) & Information Technology (IT)Document72 pagesBiju Patnik University of Technology: Computer Science & Engineering (Cse) & Information Technology (IT)Kumar AnupamNo ratings yet

Op-Amp 3

Op-Amp 3

Uploaded by

azriedarmawan5Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Op-Amp 3

Op-Amp 3

Uploaded by

azriedarmawan5Copyright:

Available Formats

See discussions, stats, and author profiles for this publication at: https://www.researchgate.

net/publication/318821663

Design and Analysis of Two Stage Op-Amp for Bio-Medical Application

Article · July 2017

DOI: 10.21742/ijwd.2016.3.1.02

CITATIONS READS

3 4,015

4 authors, including:

Praful Ranjan

THDC-IHET

19 PUBLICATIONS 87 CITATIONS

SEE PROFILE

All content following this page was uploaded by Praful Ranjan on 22 September 2017.

The user has requested enhancement of the downloaded file.

International Journal of Wearable Device

Vol. 3, No. 1 (2016), pp. 9-16

http://dx.doi.org/10.21742/ijwd.2016.3.1.02

Design and Analysis of Two Stage Op-Amp for Bio-Medical

Application

Praful Ranjan1, Nitin Dhaka2, Ishan Pant2, Ashutosh Pranav2

Dept. of Electronics & Communication Engineering

Graphic Era University, Dehradun

prafulmirchi@gmail.com, nitindhaka8@gmail.com, pantishan001@gmail.com,

ashutoshpranav@gmail.com

Abstract

Op Amps are the main building block in analog IC designing. Most of the real world

signals are mostly analog and they need to be converted into digital signals to analyze and

process them. So, analog circuits are of significant importance for us. We have been able to

implement a Two Stage Op-Amp using Cadence Tools. We successfully achieved the

specifications that we took as a reference in our design, and accordingly were able to design

a high gain Op-Amp with low power dissipation. We started with our work keeping in mind

the biomedical applications like ECG and EMG. After critically analyzing the design, gain of

72.54 db and power consumption of 1.02 mW is achieved with CMMR 60 and gain bandwidth

product 16.653.

Keywords: Op-amp, Cadence virtuoso, Gain, CMRR, Bio-Medical application

1. Introduction

Operational Amplifier (Op-Amp) is the important basic building block of any analog

circuit. The conventional operational amplifier has a high voltage gain differential input stage

with a second stage having high voltage gain with a last stage called buffer stage. Buffer stage

provides stumpy voltage gain and large current gain. The first two stages are responsible for

providing the overall voltage gain of the operational amplifier circuit. This operational

amplifier circuit sometimes called as the Widlar architecture. Compensating capacitor is

placed between the output of the first stage and the input of the second stage. CMOS circuit is

basic building block for designing operational amplifier because CMOS circuits have various

advantages over BJT including power consumption and noise reduction. The CMOS required

less fabrication steps than BJT.

We mainly needed to concentrate on designing a low power CMOS amplifier that would

need low supply voltages, and will still have the capability to amplify very weak signals to

make them suitably strong for further processing. Our main aim is to keep biomedical

applications in mind while designing the Op-Amp. In such applications, the amplifier (along

with other necessary circuits) comes in direct contact with the human body. It is mandatory to

keep power requirements and supplied voltages under control so that the user doesn’t get an

electric shock. We have tried to address this issue to some extent in our Op-Amp.

2. Block Diagram of the Proposed Design

The first stage of an op-amp is a differential amplifier stage. Differential Amplifier

having two inputs and the difference of these two input will be amplified. The first

Print ISSN: 2205-8613, eISSN: 2207-9785 IJWD

Copyright ⓒ 2016 GV School Publication

International Journal of Wearable Device

Vol. 3, No. 1 (2016)

stage provides the maximum gain of an op-amp. The second stage is a common source

stage. The compensation capacitance (C C) is placed between first stage and second

stage. The compensation capacitance (C C) provides the stability to the op-amp. The

compensation capacitance (C C) increase the phase margin of the design and for a stable

system the phase margin is should be greater than 45 0 . The second stage increases the

gain of the op-amp and converts the second stage input voltage into the current.

The second stage is nothing more than the current sink inverter. The second stage is a

common source stage which increases the DC voltage gain and improve the output

signal swing for a given power supply voltage. The second stage is followed by a buffer

stage, which provides a lower the output resistance and maintains a large voltage swing.

The buffer stage also provides better slew rate (SR) of an Op-Amp. It is not necessary

all applications require low output impedance. If the Op-Amp is intended to drive a

small purely capacitive load, which is the case in many switched capacitor or data

conversion applications, the output buffer is not used. The Biasing current is used to

provide to keep all the transistors in saturation region. The purpose of the compensation

circuit or compensation capacitance is to reduce the overall gain at higher frequencies

and provides stability when negative feedback is applied to the Op-Amp.

Figure 1. Block Diagram of Two Stage Differential Amplifier

3. Simulation Set-Up

Cadence Virtuoso 6.1.5 is used as a simulation tool for simulating Op-amp design.

Advanced features like Cadence Virtuoso Schematic Editor for providing high speed and easy

design methods, Cadence Virtuoso Layout Suite for speeding up the physical layout of the

design, Cadence Virtuoso Visualization and Analysis for efficiently analyzing the

performance of the design and Cadence Assura Physical Verification for reducing overall

verification time, because a quick and instinctive debug capability is incorporated within the

Virtuoso custom design environment. It easily compares, repair, remove and distinguish

errors.

10 Copyright ⓒ 2016 GV School Publication

International Journal of Wearable Device

Vol. 3, No. 1 (2016)

4. Performance Parameters of High Gain Amplifier

4.1. Open Loop Gain

The ratio of the output voltage and differential input voltage is called open loop gain of op-

amp. Since the output signal is much larger than the input signal, therefore it is termed as

large signal voltage gain. It may be expressed in decibels using the following relation,

AV (dB) = 20 log10 (Vout / VDM),

where, VDM is the differential input voltage and Vout is the output voltage.

4.2. Miller Effect

The effective input impedance of an amplifier depends on the impedance connected from

input to output of the amplifier. The perceptible scaling of this impedance often dominates the

input impedance and frequency response of the amplifier. This type of phenomena commonly

known as the Miller Effect. The virtually increased input capacitance due to the Miller effect

is given by:

CM = C (1+AV),

where, AV is the gain of the amplifier and C is the feedback capacitance.

4.3. Gain Bandwidth Product

For an amplifier the gain bandwidth product designated as GB is the product of the

amplifier’s gain and the bandwidth. For devices such as Op-Amps that are designed to have a

simple one-pole frequency response. In case of that type of design the GB is nearly

independent of the gain at which it is measured. So in this kind of devices the gain bandwidth

product will also be equal to the unity gain bandwidth of the amplifier.

4.4. Slew Rate

Slew rate (SR) is the rate of change of output voltage caused by changed in input. Its units

are V/ms or V/us.

Internal compensation capacitor CC is the primary factor controlling slew rate in most Op-

Amps , which makes the Op-Amp unity gain stable. Charging and discharging of the

compensation capacitor CC limits the voltage change in the second stage. The maximum rate

of change is when either side of the differential pair is conducting 2IE. All Op-Amps do not

have compensation capacitors. In Op-Amps without internal compensation capacitors, the

slew rate is determined by internal Op-Amp parasitic capacitances.

4.5. Gain Margin and Phase Margin

The amount of gain increase or decrease required to make the loop gain unity at the

frequency ωgm(phase crossover frequency, where the phase angle is –180°)is called the gain

margin. The gain margin is 1/f if f is the gain at the –180° phase frequency.

The difference between the phase of the response and –180° is called the phase margin

when the loop gain is 1.0 (or 0 dB). The unity-gain frequency or gain crossover frequency is

that frequency ωpm at which the magnitude is 1.0.

Copyright ⓒ 2016 GV School Publication 11

International Journal of Wearable Device

Vol. 3, No. 1 (2016)

5. Designing of Op-Amp

The Op-Amp design process mainly involves the two major steps. First one is called

Design conception while another one is termed as Design optimization. An architecture is

proposed to meet the given specifications in design conception. This step is usually done to

calculate the design values by hand calculations which is necessary for choices that must be

made. The “first-cut” design is taken & verified for the specifications and then optimized in

the second step of the design optimization. The optimization can include different

environmental influences or process variations and is usually done by using Computer

simulation.

Figure.2. Architecture of 2-stage Op-Amp

Model or Device Parameters

Kp = µp Cox = 60 µA/V2

Kn = µp Cox = 300 µA/V2

Threshold Voltage VTH (n) = 0.61 V, VTH (p) = 0.46 V.

First Stage (Differential Amplifier) Design Values:

The values of the (W/L) were calculated as follows:

S1,2 = 28, S3,4 = 84, S5,8 = 4.

DC current IC = 50 µA, VDD = 1.8 V, VSS = -1.8 V, CL = 10 pF.

12 Copyright ⓒ 2016 GV School Publication

International Journal of Wearable Device

Vol. 3, No. 1 (2016)

5.1. Circuits and Simulated Outputs of First Stage (Differential Amplifier)

Figure 3. Schematic of First Stage Op-Amp

Figure 4. Transient Response of First Stage Op-Amp

Figure 5. A.C Response of First Stage of Op-Amp

Copyright ⓒ 2016 GV School Publication 13

International Journal of Wearable Device

Vol. 3, No. 1 (2016)

Second Stage Design Values

The aspect ratio (W/L) values for different transistors were calculated as follows:

S1,2 = 6, S3,4 = 8, S5,8 = 8, S6 = 154, S7 = 102.

DC current IC = 15 µm, VDD = 1.8 V, VSS = -1.8 V, CC = 2.2 pF, CL = 10 pF.

5.2. Circuits and Simulated Outputs after addition of Second Stage

Figure 6. Two Stage Op-Amp Schematic

Figure 7. AC dB 20 Plot for Gain and Bandwidth

6. Result and Conclusion

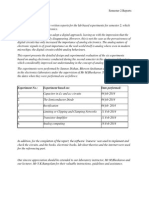

Design specification values obtained after simulation are tabulated in Table I. The obtained

results are further compared with the reference papers and shown in table II.

Table 1. Values obtained after simulation

S. No. Specifications Proposed Values Obtained Values

1 Technology 180 nanometres Used

14 Copyright ⓒ 2016 GV School Publication

International Journal of Wearable Device

Vol. 3, No. 1 (2016)

2 Power Supply (Vdd) 1.8 V 1.8 V

3 Load Capacitance (CL) 10 pF 10 pF

4 Coupling Capacitance (Cc) 2.2 pF 2.2 pF

5 Power dissipation (PD) < = 2 mW 1.003 mW

6 Differential DC gain (Av) > = 60 dB 72.54 dB

7 Unity Gain Bandwidth > 10 Mega hertz 16.653 MHz

8 Phase Margin (PM) > = 60 deg 61.417 deg

9 Common Mode >=60 dB 60 dB

Rejection(CMRR)

Table 2. Comparison of Obtained Results with Reference Papers

Parameters References Results of

Proposed Design

[6] [9] [11] [12] [13] [14] [16]

Gain (dB) 36.747 67 78 71 51 50 70 72.54

Gain BW Product 16 12 11 5 - 10 14 16.653

(MHz)

Power Dissipation (mW) 0.804 - - <2 - 2.4 2.1 1.003

CMRR (dB) - 78 60 - 64 - - 60

Phase Margin (deg) 48.1 59 85.85 - - 175 65 61.417

Power Supply (V) - - 5 2.5 2.3 - - 1.8

Technology (nm) 180 - tsmc 180 90 90 180 180

350

References

[1] D.R. Holberg and P.E. Allen, "CMOS Analog Circuit Design, Second Edition", Oxford

University Press, (2002).

[2] B. Razavi, "Design of Analog CMOS Integrated Circuits”, McGraw-Hill, (2002).

Copyright ⓒ 2016 GV School Publication 15

International Journal of Wearable Device

Vol. 3, No. 1 (2016)

[3] S.M. Kang, and Y. Leblebici, “CMOS Digital Integrated Circuits, Analysis and design”, Tata

McGraw-Hill Edition, (2003).

[4] P.R. Gray, P.J. Hurst, S.H. Lewis, and R.G. Meyer, “Analysis and Design of Analog Integrated

Circuits”, Fourth Edition, John Wiley &Sons, Inc., (2001).

[5] A.S Sedra, and K.C.Smith, “Microelectronics Circuits Theory and Applications”, Fifth Edition.

Oxford University Press, (2009).

[6] S. Bandyopadhyay, and D. Mukherjee, "Design of Two Stage CMOS Op-Amp in 180nm

Technology With Low Power and High CMRR", International Journal of Recent Trends in

Engineering & Technology, Vol. 11, June (2014).

[7] A. Dadoria, C.M Roy, and A.S. Yadav, "CMOS Current Mirrors Comparison", International

Journal of Advanced Research in Computer Science and Software Engineering, pp. 625-630,

April – (2013).

[8] R.S. Parihar, and A. Gupta, "Design of a Fully Differential Two-Stage CMOS Op-Amp for High

Gain, High Bandwidth Applications", May (2006).

[9] G. Palmisano, G. Palumbo, and S. Pennisi, "Design Procedure for Two-Stage CMOS

Transconductance Op-Amps: A Tutorial", Dipartimento Elettrico Elettronico e Sistemistico,

Universita’ di Catania, Viale Andrea Doria, 6 I-95125 Catania, Italy, September 12, (2000).

[10] A. Gupta, U.B.S. Chandrawat, D.K. Mishra, and R. Khatri, "A Two Stage and Three Stage

CMOS OPAMP with Fast Settling, High DC Gain and Low Power Designed in 180nm

Technology", International Conference on Computer Information Systems and Industrial

Management Applications, (2010).

[11] A. Yadav, “Design of Two-Stage CMOS Op-Amp and Analyze the Effect of Scaling”, IJERA

Vol. 2, No. 5, pp.647-654, September- October (2012).

[12] M. Vinoth Kumar, "Design of Mixed-Signal Integrator for RF Amplifier", International Journal of

Computer Applications, International Conference on Innovations in Intelligent Instrumentation,

Optimization And Signal Processing, ICIIIOSP-2013, (2013).

[13] P.K. Pandey, and A. Jain, "Design of Low-Voltage Op-Amp (700 mV)", International Journal of

Engineering and Innovative Technology (IJEIT), Vol. 3, No. 1, July (2013).

[14] M. Saravanakumar, N. Kaleeswari, and K. Rajendran, "Design and Analysis of Two-Stage

Operational Transconductance Amplifier (OTA) using Cadence tool", International Journal of

Emerging Technology and Advanced Engineering, Vol. 4, No. 4, April (2014).

[15] A.K. Singh, Anuradha, and Dr. V. Nath, "Design and Performance analysis of Low power CMOS

Op-Amp", International Journal of Engineering Sciences & Research, September (2013).

[16] B. Krishna, and D. Arunkumar, "A Novel Design of Low-Power Two Stage Cascode Op-Amp",

International Journal of Advanced Research in Computer Science and Software Engineering, Vol.

4, No. 5, May (2014).

16 Copyright ⓒ 2016 GV School Publication

View publication stats

You might also like

- Automated Broad and Narrow Band Impedance Matching for RF and Microwave CircuitsFrom EverandAutomated Broad and Narrow Band Impedance Matching for RF and Microwave CircuitsNo ratings yet

- Major ProjectDocument28 pagesMajor ProjectNeeraj MishraNo ratings yet

- The Designer's Guide To Analog and Mixed-Signal Modeling Illustrated With VHDL-AMS and MASTDocument356 pagesThe Designer's Guide To Analog and Mixed-Signal Modeling Illustrated With VHDL-AMS and MASTAmaniDarwishNo ratings yet

- Design and Analysis of Two Stage CMOS Operational Amplifier Using 0.13 M TechnologyDocument6 pagesDesign and Analysis of Two Stage CMOS Operational Amplifier Using 0.13 M TechnologyJunaid KhanNo ratings yet

- Research Paper On AmplifierDocument5 pagesResearch Paper On Amplifiereh1dvt0m100% (1)

- Design and Layout of 1.8V Two Stage CMOS Operational Amplifier (Unbuffered)Document5 pagesDesign and Layout of 1.8V Two Stage CMOS Operational Amplifier (Unbuffered)sudarshan poojaryNo ratings yet

- Op-Amp ReportDocument27 pagesOp-Amp ReportGaurav Singh100% (15)

- Opamp Desiging Project ReportDocument6 pagesOpamp Desiging Project ReportTarun PrakashNo ratings yet

- Koneru Lakshmaiah Education Foundation: Department of Electronics and Communication EngineeringDocument12 pagesKoneru Lakshmaiah Education Foundation: Department of Electronics and Communication EngineeringLakshmi JagupillaNo ratings yet

- Modelling of Operational Amplifier by Using CMOS Technology: VSRD-IJEECE, Vol. 2 (6), 2012, 330-336Document7 pagesModelling of Operational Amplifier by Using CMOS Technology: VSRD-IJEECE, Vol. 2 (6), 2012, 330-336Akash VermaNo ratings yet

- MSD Aat (Ec144, Ec171)Document7 pagesMSD Aat (Ec144, Ec171)srusti.ec21No ratings yet

- Design of CMOS Based Biosensor OTA 2018Document10 pagesDesign of CMOS Based Biosensor OTA 2018RajeeNo ratings yet

- High Speed Analog Design and Application Seminar: From Texas InstrumentsDocument39 pagesHigh Speed Analog Design and Application Seminar: From Texas InstrumentshaoyuqianNo ratings yet

- Robotics 17Document27 pagesRobotics 17setsindia3735No ratings yet

- Amplifier DesignDocument20 pagesAmplifier DesignCurtinNo ratings yet

- Amplifier Build and Design: Faculty of Engineering and Applied ScienceDocument21 pagesAmplifier Build and Design: Faculty of Engineering and Applied ScienceFarrukh ZamanNo ratings yet

- 2stage Opamp 90nmDocument6 pages2stage Opamp 90nmsabbir.bhuyianNo ratings yet

- Power Amplifier Design ThesisDocument6 pagesPower Amplifier Design Thesisdwm7sa8p100% (1)

- Microwave Amplifier Design (Part 1) : San Jose State University Department of Electrical EngineeringDocument22 pagesMicrowave Amplifier Design (Part 1) : San Jose State University Department of Electrical EngineeringTran NamNo ratings yet

- Design of High Performance Cmos Comparator Using 90nm TechnologyDocument6 pagesDesign of High Performance Cmos Comparator Using 90nm TechnologyRAJANo ratings yet

- 2020 SEO Operational Amplifiers r1.0Document6 pages2020 SEO Operational Amplifiers r1.0Okiring JonahNo ratings yet

- Irjet V4i5125 PDFDocument5 pagesIrjet V4i5125 PDFAnonymous plQ7aHUNo ratings yet

- Linear and Digital Ic ApplicationsDocument47 pagesLinear and Digital Ic Applicationsభార్గవ్ కుమార్100% (1)

- Power Amplifier Application NoteDocument3 pagesPower Amplifier Application NoteSanthos KumarNo ratings yet

- A Study and Analysis of Two Stage Single Ended CMOS OP-AMPDocument9 pagesA Study and Analysis of Two Stage Single Ended CMOS OP-AMPsanjeevsoni64No ratings yet

- A High Performance CMOS Band - Gap Reference Circuit DesignDocument6 pagesA High Performance CMOS Band - Gap Reference Circuit DesignKhaja Mujeebuddin QuadryNo ratings yet

- Cmos Two Stage OpamppublishedDocument5 pagesCmos Two Stage Opamppublisheddeepak pandeyNo ratings yet

- An Analysis and Design of High Performance Power Consumption Double Tail Comparator Using Gated Clock and Power Gating TechniquesDocument7 pagesAn Analysis and Design of High Performance Power Consumption Double Tail Comparator Using Gated Clock and Power Gating TechniquesIJIRSTNo ratings yet

- Design of Two Stage Op-AmpDocument4 pagesDesign of Two Stage Op-AmpWARSE JournalsNo ratings yet

- 118A GaN HEMT Class AB RF Power AmplifierDocument4 pages118A GaN HEMT Class AB RF Power AmplifierNarasimha SunchuNo ratings yet

- Report About Operational Amplifiers 32020245Document6 pagesReport About Operational Amplifiers 32020245mohamedmohamedahmed172No ratings yet

- Electronics Laboratory ReportDocument6 pagesElectronics Laboratory ReportJohn Vincent SacloloNo ratings yet

- UNIT-1 Basics of Operational Amplifiers: EC8453-Linear Integrated Circuits Dept of ECE/PECDocument16 pagesUNIT-1 Basics of Operational Amplifiers: EC8453-Linear Integrated Circuits Dept of ECE/PECIniyan RaviNo ratings yet

- Sri Lanka Institute of Information Technology: EN16544246 W.A.M.Ranasinghe Group - 05Document13 pagesSri Lanka Institute of Information Technology: EN16544246 W.A.M.Ranasinghe Group - 05Shashini MaldeniyaNo ratings yet

- Comparison of BW For RC Coupled Single Stage and Multi Stage AmplifieDocument6 pagesComparison of BW For RC Coupled Single Stage and Multi Stage AmplifieFaras SmansaNo ratings yet

- Design and Development of Novel WeighingDocument4 pagesDesign and Development of Novel WeighingaatifdNo ratings yet

- A 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliDocument4 pagesA 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliAnika TahsinNo ratings yet

- 2-15-1381147174-25 .Design of 1 V.FULL PDFDocument10 pages2-15-1381147174-25 .Design of 1 V.FULL PDFABHILASH RAINo ratings yet

- Assignment Brief - Unit22 Asst (IVed) .1Document11 pagesAssignment Brief - Unit22 Asst (IVed) .1Kalana wickramanayakaNo ratings yet

- Operational Transconductance Amplifier Research PaperDocument6 pagesOperational Transconductance Amplifier Research PaperafeawjjwpNo ratings yet

- Which Amplifier Is Used To Provide Increased BandwidthDocument10 pagesWhich Amplifier Is Used To Provide Increased BandwidthjackNo ratings yet

- New Lab Manual (ECA)Document50 pagesNew Lab Manual (ECA)Shrinivas SaptalakarNo ratings yet

- ADE - Pspice Lab ManualDocument12 pagesADE - Pspice Lab ManualShashiNo ratings yet

- Polytechnic of Namibia School of Engineering Electrical Engineering DepartmentDocument17 pagesPolytechnic of Namibia School of Engineering Electrical Engineering DepartmentDarshan Rai KanungoNo ratings yet

- Inverter Circuit ThoeryDocument8 pagesInverter Circuit ThoeryAbhishek SainiNo ratings yet

- Instrumentation AmplifierDocument6 pagesInstrumentation Amplifiersarpanch100% (2)

- High Power Amplifier With Maximized Efficiency: by Bumjin KimDocument56 pagesHigh Power Amplifier With Maximized Efficiency: by Bumjin Kimluis lopezNo ratings yet

- Bandwidth Extension in CMOS With Optimized On-Chip InductorsDocument10 pagesBandwidth Extension in CMOS With Optimized On-Chip InductorsAlex WongNo ratings yet

- Schmitt TriggerDocument58 pagesSchmitt TriggerCharles BurgosNo ratings yet

- Opamp Design StepsDocument4 pagesOpamp Design StepspankajNo ratings yet

- 4 Differential Amplifier With OutputDocument5 pages4 Differential Amplifier With Outputmanishkavi89No ratings yet

- Differential Amplifier ThesisDocument8 pagesDifferential Amplifier Thesisbsqjpnxd100% (2)

- Isscc2022 000109CLDocument16 pagesIsscc2022 000109CLdashuai huaNo ratings yet

- SR21622171146Document4 pagesSR21622171146Kini FamilyNo ratings yet

- Literature Review of AmplifierDocument6 pagesLiterature Review of Amplifierea7sfn0f100% (1)

- 19BEC1211 - ClassB - Amplifier - AEC - WEEK 8Document6 pages19BEC1211 - ClassB - Amplifier - AEC - WEEK 8Tom ShibuNo ratings yet

- ECA ManualDocument62 pagesECA ManualAnonymous gP8ivl7fNo ratings yet

- Lab Experiment DCDocument7 pagesLab Experiment DCKumar ShashankNo ratings yet

- Ad844 PDFDocument20 pagesAd844 PDFkavi_mishra92No ratings yet

- rfrxd0420 PDFDocument32 pagesrfrxd0420 PDFYaroslavNo ratings yet

- Cold Junction Compensation PDFDocument10 pagesCold Junction Compensation PDFAbhayy DevNo ratings yet

- Affiliated Institutions Anna University, Chennai Regulations - 2009 Curriculum Ii To Iv Semesters (Full Time) M.E. Applied ElectronicsDocument21 pagesAffiliated Institutions Anna University, Chennai Regulations - 2009 Curriculum Ii To Iv Semesters (Full Time) M.E. Applied ElectronicsRamya VNo ratings yet

- ELEC2507 SummerCourse PA Assigned Problems Summer2021Document1 pageELEC2507 SummerCourse PA Assigned Problems Summer2021Ambar MendezNo ratings yet

- Op Amp MCQsDocument4 pagesOp Amp MCQsMuhammad Tousiq67% (3)

- CI SMDMC 33078Document15 pagesCI SMDMC 33078Djalma MoreiraNo ratings yet

- Hardware Design of Seismic Sensors in Wireless SenDocument8 pagesHardware Design of Seismic Sensors in Wireless SenpabloNo ratings yet

- An Open-Ended Laboratory System With Computer-Aided Simulation For Undergraduate Electronic EngineeringDocument5 pagesAn Open-Ended Laboratory System With Computer-Aided Simulation For Undergraduate Electronic Engineeringpmahesh268No ratings yet

- Unit 2: Definition of IcDocument26 pagesUnit 2: Definition of Icsai kiranNo ratings yet

- Baxandall Tone ControlDocument7 pagesBaxandall Tone ControlSheeNo ratings yet

- Pulse Oximeter DesignDocument31 pagesPulse Oximeter DesignPraba KaranNo ratings yet

- Bipolar Stepper Motor Control CircuitDocument3 pagesBipolar Stepper Motor Control CircuitArda AkberkNo ratings yet

- LM4766T DatasheetDocument14 pagesLM4766T DatasheetNikoinekoNo ratings yet

- Source:: Source: Op-Amps and Linear Integrated Circuits, Ramakant A.GayakwadDocument2 pagesSource:: Source: Op-Amps and Linear Integrated Circuits, Ramakant A.GayakwadBatool HerzallahNo ratings yet

- Electronics & Communication EngineeringDocument43 pagesElectronics & Communication EngineeringAtul Prakash DwivediNo ratings yet

- Analysis of The Impact of High-Order Integrator Dynamics On SC Sigma-Delta Modulator Performances-Q2KDocument13 pagesAnalysis of The Impact of High-Order Integrator Dynamics On SC Sigma-Delta Modulator Performances-Q2Kjulio perezNo ratings yet

- Lect26 OMP AMPDocument14 pagesLect26 OMP AMPJason LeeNo ratings yet

- Experiment 1 Electronics 1 Final 1.Document50 pagesExperiment 1 Electronics 1 Final 1.Neekita Chamane100% (4)

- Report - Automatic Power Factor Improvement Using ArduinoDocument27 pagesReport - Automatic Power Factor Improvement Using ArduinoLynn LucyNo ratings yet

- AD215Document12 pagesAD215gmludNo ratings yet

- A Digital-To-Analog Converter (DAC) Block Diagram.: Introduction To Microprocessor-Based ControlDocument3 pagesA Digital-To-Analog Converter (DAC) Block Diagram.: Introduction To Microprocessor-Based Controlnovo orderNo ratings yet

- B.Tech ELECTRICAL Engineering (AKU Syllabus) SEMESTER-VIIDocument2 pagesB.Tech ELECTRICAL Engineering (AKU Syllabus) SEMESTER-VIIkrishna mohan haitNo ratings yet

- Opax607 50-Mhz, Low-Power, Gain of 6-V/V Stable, Rail-To-Rail Output Cmos Operational AmplifierDocument43 pagesOpax607 50-Mhz, Low-Power, Gain of 6-V/V Stable, Rail-To-Rail Output Cmos Operational AmplifierMichael TaftNo ratings yet

- Ina 102Document13 pagesIna 102Erick GiioNo ratings yet

- What Effect Does Direct Coupling Have On A Two Stage BJT AmplifierDocument63 pagesWhat Effect Does Direct Coupling Have On A Two Stage BJT Amplifierzraider50% (2)

- Cmos Ota ThesisDocument5 pagesCmos Ota Thesislisabrownolathe100% (2)

- Biju Patnik University of Technology: Computer Science & Engineering (Cse) & Information Technology (IT)Document72 pagesBiju Patnik University of Technology: Computer Science & Engineering (Cse) & Information Technology (IT)Kumar AnupamNo ratings yet