Professional Documents

Culture Documents

25CSM04 4 Mbit SPI Serial EEPROM With 128 Bit Seri-2944121

25CSM04 4 Mbit SPI Serial EEPROM With 128 Bit Seri-2944121

Uploaded by

ManunoghiCopyright:

Available Formats

You might also like

- Bitcoin Key ListDocument5 pagesBitcoin Key ListJohn Smith28% (18)

- Aria2 - The Ultra Fast Download UtilityDocument9 pagesAria2 - The Ultra Fast Download UtilityPaul OrozcoNo ratings yet

- 25AA640/25LC640: 64K Spi Bus Serial EEPROMDocument12 pages25AA640/25LC640: 64K Spi Bus Serial EEPROMinsomnium86No ratings yet

- 24CW16X 24CW32X 24CW64X 24CW128X Data Sheet 200057-1397638Document51 pages24CW16X 24CW32X 24CW64X 24CW128X Data Sheet 200057-1397638ManunoghiNo ratings yet

- 25AA040/25LC040/25C040: 4K Spi Bus Serial EEPROMDocument22 pages25AA040/25LC040/25C040: 4K Spi Bus Serial EEPROMAgustin AndrokaitesNo ratings yet

- 25AA640/25LC640/25C640: 64K Spi Bus Serial EEPROMDocument11 pages25AA640/25LC640/25C640: 64K Spi Bus Serial EEPROMAndrey OliveiraNo ratings yet

- Datasheet 25c040Document22 pagesDatasheet 25c040Perona PabloNo ratings yet

- SST26VF064B SST26VF064BA 2 5V 3 0V 64 Mbit Serial - 2935898Document91 pagesSST26VF064B SST26VF064BA 2 5V 3 0V 64 Mbit Serial - 2935898ManunoghiNo ratings yet

- Bus Serial EEPROMDocument12 pagesBus Serial EEPROMMatiasNo ratings yet

- SST26VF080A: 2.5V/3.0V 8-Mbit Serial Quad I/O™ (SQI™) Flash MemoryDocument72 pagesSST26VF080A: 2.5V/3.0V 8-Mbit Serial Quad I/O™ (SQI™) Flash MemoryManunoghiNo ratings yet

- Spansion S25FL256S - 32MB SPI FlashromDocument149 pagesSpansion S25FL256S - 32MB SPI FlashromcockNo ratings yet

- 8K/16K 5.0V SPI Bus Serial EEPROM: Features Package TypesDocument12 pages8K/16K 5.0V SPI Bus Serial EEPROM: Features Package Typesrıdvan71No ratings yet

- 25AA256/25LC256: 256K SPI Bus Serial EEPROMDocument32 pages25AA256/25LC256: 256K SPI Bus Serial EEPROMmelquisedecNo ratings yet

- 24C320-EP MicrochipTechnologyDocument12 pages24C320-EP MicrochipTechnologyMateus CorrêaNo ratings yet

- MCP79410/MCP79411/MCP79412: I C™ Real-Time Clock/Calendar With EEPROM, SRAM, Unique ID and Battery SwitchoverDocument38 pagesMCP79410/MCP79411/MCP79412: I C™ Real-Time Clock/Calendar With EEPROM, SRAM, Unique ID and Battery SwitchoverDaniel CortelettiNo ratings yet

- Continuity of SpecificationsDocument61 pagesContinuity of Specificationsshatruddha123No ratings yet

- SST26VF064BDocument76 pagesSST26VF064Bmar_barudjNo ratings yet

- Mcrf250: 125 KHZ Microid Passive Rfid Device With Anti-CollisionDocument24 pagesMcrf250: 125 KHZ Microid Passive Rfid Device With Anti-CollisionPanagiotis PanagosNo ratings yet

- SST25VF016B: 16 Mbit SPI Serial FlashDocument30 pagesSST25VF016B: 16 Mbit SPI Serial Flashzigmund zigmundNo ratings yet

- How Does The AT24CM02-SSHM-B EEPROM Memory FunctionDocument6 pagesHow Does The AT24CM02-SSHM-B EEPROM Memory FunctionjackNo ratings yet

- dsPIC33CK256MP508 Family Data Sheet DS70005349Document646 pagesdsPIC33CK256MP508 Family Data Sheet DS70005349testtestNo ratings yet

- 32K 5.0V I C Smart Serial EEPROM: Features Package TypesDocument12 pages32K 5.0V I C Smart Serial EEPROM: Features Package TypesRamon LopezNo ratings yet

- 25AA256 25LC256 256K SPI Bus Serial EEPROM 20001822harc2Document31 pages25AA256 25LC256 256K SPI Bus Serial EEPROM 20001822harc2Ken AlonsoNo ratings yet

- At26df161 PDFDocument31 pagesAt26df161 PDFMiloud ChouguiNo ratings yet

- 25P32 EonSiliconSolutionDocument34 pages25P32 EonSiliconSolutionAmilcar SilvaNo ratings yet

- SST26WF064C: 1.8V, 64 Mbit Serial Quad I/O (SQI) Flash MemoryDocument93 pagesSST26WF064C: 1.8V, 64 Mbit Serial Quad I/O (SQI) Flash MemoryManunoghiNo ratings yet

- SST25VF040B: 4 Mbit SPI Serial FlashDocument33 pagesSST25VF040B: 4 Mbit SPI Serial FlashDario EzequielNo ratings yet

- Catalog BeckDocument50 pagesCatalog BeckJJGLNo ratings yet

- SST26VF064BDocument85 pagesSST26VF064BAnonymous zOUoOJhRNo ratings yet

- SST25VF040B 4 Mbit SPI Serial Flash Data Sheet 20005051F 1Document31 pagesSST25VF040B 4 Mbit SPI Serial Flash Data Sheet 20005051F 1Drew AlbaneseNo ratings yet

- Cypr S A0011119747 1-3004816Document108 pagesCypr S A0011119747 1-3004816ManunoghiNo ratings yet

- 25AA160/25LC160/25C160: 16K Spi Bus Serial EEPROMDocument23 pages25AA160/25LC160/25C160: 16K Spi Bus Serial EEPROMЕвгенийNo ratings yet

- S25fl512sagbhia13 Fab024Document145 pagesS25fl512sagbhia13 Fab024中井一朗No ratings yet

- Infineon-S25fl128p 128 Mbit 3.0 V Flash Memory-datasheet-V14 00-EnDocument44 pagesInfineon-S25fl128p 128 Mbit 3.0 V Flash Memory-datasheet-V14 00-EnAlexNo ratings yet

- Microchiptechnology Sst25vf020b804csaet Datasheets 1062Document33 pagesMicrochiptechnology Sst25vf020b804csaet Datasheets 1062sara mehdipourNo ratings yet

- 8K/16K 5.0V Microwire Serial EEPROM: Features: Package TypesDocument20 pages8K/16K 5.0V Microwire Serial EEPROM: Features: Package Typesfarhood ranjbarkhanghahNo ratings yet

- 24AA52/24LCS52: 2K 2.2V I C Serial EEPROM With Software Write-ProtectDocument24 pages24AA52/24LCS52: 2K 2.2V I C Serial EEPROM With Software Write-Protecta4rfanNo ratings yet

- Tornado BSP Manual2Document335 pagesTornado BSP Manual2za_wizardNo ratings yet

- Macronix Nbit Memory Family: 64M-Bit (X 1) Cmos Serial Eliteflash MemoryDocument46 pagesMacronix Nbit Memory Family: 64M-Bit (X 1) Cmos Serial Eliteflash MemoryRoger Chavez PachasNo ratings yet

- Kingston EMMC16G IB29 70H01 v1 1-3236273Document25 pagesKingston EMMC16G IB29 70H01 v1 1-3236273ManunoghiNo ratings yet

- 24AA64/24LC64/24FC64: 64K I C™ Serial EEPROMDocument45 pages24AA64/24LC64/24FC64: 64K I C™ Serial EEPROMJuan Carlos CrespoNo ratings yet

- Mc9s08de60 V2 0 9 2007Document408 pagesMc9s08de60 V2 0 9 2007LuchazoNo ratings yet

- 25AA02E48 Spi Bus Serial EEPROMDocument26 pages25AA02E48 Spi Bus Serial EEPROMpiyushpandeyNo ratings yet

- 64K 5.0V I C Smart Serial Eeprom: FeaturesDocument16 pages64K 5.0V I C Smart Serial Eeprom: FeaturesFerner BriceñoNo ratings yet

- Kingston 10 25 2023 EMMC04G MT32 01G10 v1 2-3359335Document24 pagesKingston 10 25 2023 EMMC04G MT32 01G10 v1 2-3359335ManunoghiNo ratings yet

- Xmc-Xm25qh128ahig C328463Document78 pagesXmc-Xm25qh128ahig C328463Manishkumar JethvaNo ratings yet

- Kingston EMMC32G IX29 8AD01 v1 2-3236216Document26 pagesKingston EMMC32G IX29 8AD01 v1 2-3236216ManunoghiNo ratings yet

- Atmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetDocument20 pagesAtmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetalaitsevNo ratings yet

- 22131c PDFDocument24 pages22131c PDFAdilsonAmorimNo ratings yet

- MX25L8005 MxicDocument41 pagesMX25L8005 Mxicdanehcan graNo ratings yet

- 25AA080C/D, 25LC080C/D: 8K SPI Bus Serial EEPROMDocument28 pages25AA080C/D, 25LC080C/D: 8K SPI Bus Serial EEPROMrudy pumacahuaNo ratings yet

- S 29 GL 128 MXXXMDocument160 pagesS 29 GL 128 MXXXMpuh1967No ratings yet

- Embedded Multi-Media Card: (E - MMC 5.0)Document23 pagesEmbedded Multi-Media Card: (E - MMC 5.0)FotoContoNo ratings yet

- Kingston EMMC04G M657 K03U v1 1-3236214-1Document25 pagesKingston EMMC04G M657 K03U v1 1-3236214-1ManunoghiNo ratings yet

- Atecc608A: Microchip Cryptoauthentication™ DeviceDocument28 pagesAtecc608A: Microchip Cryptoauthentication™ Deviceedward blancoNo ratings yet

- Mc9s08ac128 96 DSDocument370 pagesMc9s08ac128 96 DSVladimir AlcalaNo ratings yet

- Kingston EMMC16G TB29 70H01 v1 1-3236240Document25 pagesKingston EMMC16G TB29 70H01 v1 1-3236240ManunoghiNo ratings yet

- SKEA64PB, Product Brief - Product BriefDocument14 pagesSKEA64PB, Product Brief - Product BriefMayank VyasNo ratings yet

- Pm25LD010020datasheet v04Document33 pagesPm25LD010020datasheet v04Sutu ValentinNo ratings yet

- 24C32Document12 pages24C32SilviuCocoloșNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- D32 27245S 001 DDR4 ECC DIMM 3200 22 1024x8 8GB SA-3107331Document17 pagesD32 27245S 001 DDR4 ECC DIMM 3200 22 1024x8 8GB SA-3107331ManunoghiNo ratings yet

- Gsi Technology Gsits01771 1 1759339Document30 pagesGsi Technology Gsits01771 1 1759339ManunoghiNo ratings yet

- Gd25wq64e v1 2 20200415-1825549Document60 pagesGd25wq64e v1 2 20200415-1825549ManunoghiNo ratings yet

- 8662DxxB 350M 976388Document32 pages8662DxxB 350M 976388ManunoghiNo ratings yet

- 25lp064a 2936098Document101 pages25lp064a 2936098ManunoghiNo ratings yet

- D32 27306S 001 DDR4 ECC DIMM 3200 22 2048x8 32GB S-3106760Document17 pagesD32 27306S 001 DDR4 ECC DIMM 3200 22 2048x8 32GB S-3106760ManunoghiNo ratings yet

- Kingston MKF 981 Vp80es Encrypted App 2-3240008Document2 pagesKingston MKF 981 Vp80es Encrypted App 2-3240008ManunoghiNo ratings yet

- Apacer SV250 CFast BiCS5 AA2 XX5XXX XXXEX Spec v1 - 3107344Document25 pagesApacer SV250 CFast BiCS5 AA2 XX5XXX XXXEX Spec v1 - 3107344ManunoghiNo ratings yet

- Infineon 512 MBIT HYPERFLASH 2b 64 MBIT HYPERRAM - 3360504Document15 pagesInfineon 512 MBIT HYPERFLASH 2b 64 MBIT HYPERRAM - 3360504ManunoghiNo ratings yet

- 96FD M064 ITR71 - Datasheet20170616093152 1128937Document13 pages96FD M064 ITR71 - Datasheet20170616093152 1128937ManunoghiNo ratings yet

- Adet S A0001156012 1-2956578Document73 pagesAdet S A0001156012 1-2956578ManunoghiNo ratings yet

- Flash 11 Click-3218255Document3 pagesFlash 11 Click-3218255ManunoghiNo ratings yet

- Is25lp032 064 128 463542Document91 pagesIs25lp032 064 128 463542ManunoghiNo ratings yet

- Infineon S70GL02GT 2 Gbit 256 MB 3 0V Flash Memo-3107504Document25 pagesInfineon S70GL02GT 2 Gbit 256 MB 3 0V Flash Memo-3107504ManunoghiNo ratings yet

- Kingston EMMC16G TB29 70H01 v1 1-3236240Document25 pagesKingston EMMC16G TB29 70H01 v1 1-3236240ManunoghiNo ratings yet

- Kingston EMMC16G IB29 70H01 v1 1-3236273Document25 pagesKingston EMMC16G IB29 70H01 v1 1-3236273ManunoghiNo ratings yet

- Kingston IronKey Keypad 200 Series Datasheet-3318191Document3 pagesKingston IronKey Keypad 200 Series Datasheet-3318191ManunoghiNo ratings yet

- 24CW16X 24CW32X 24CW64X 24CW128X Data Sheet 200057-1397638Document51 pages24CW16X 24CW32X 24CW64X 24CW128X Data Sheet 200057-1397638ManunoghiNo ratings yet

- Innodisk m5s0 Bgm2oavp-3317554Document22 pagesInnodisk m5s0 Bgm2oavp-3317554ManunoghiNo ratings yet

- 6500 Ion Nvme SSD Product Brief-3223536Document4 pages6500 Ion Nvme SSD Product Brief-3223536ManunoghiNo ratings yet

- Adet S A0006353185 1-2956540Document63 pagesAdet S A0006353185 1-2956540ManunoghiNo ratings yet

- Gsits01767 1-2295275Document27 pagesGsits01767 1-2295275ManunoghiNo ratings yet

- Adet S A0003827057 1-2956525Document58 pagesAdet S A0003827057 1-2956525ManunoghiNo ratings yet

- Infineon FM24CL64B 64 Kbit 8 K 8 Serial I2C Au-3361484-2Document19 pagesInfineon FM24CL64B 64 Kbit 8 K 8 Serial I2C Au-3361484-2ManunoghiNo ratings yet

- Adet S A0001553754 1-2956489Document70 pagesAdet S A0001553754 1-2956489ManunoghiNo ratings yet

- 25AA640A 25LC640A 64K SPI Bus Serial EEPROM 200018-2449118Document39 pages25AA640A 25LC640A 64K SPI Bus Serial EEPROM 200018-2449118ManunoghiNo ratings yet

- Asf36c8gx72pz 1649492Document12 pagesAsf36c8gx72pz 1649492ManunoghiNo ratings yet

- Gsits01765 1-2294917Document33 pagesGsits01765 1-2294917ManunoghiNo ratings yet

- SST26VF080A: 2.5V/3.0V 8-Mbit Serial Quad I/O™ (SQI™) Flash MemoryDocument72 pagesSST26VF080A: 2.5V/3.0V 8-Mbit Serial Quad I/O™ (SQI™) Flash MemoryManunoghiNo ratings yet

- Apacer SH250 CFast BiCS5 AA2 259XXX XXXF8 Spec v1 - 3107240Document24 pagesApacer SH250 CFast BiCS5 AA2 259XXX XXXF8 Spec v1 - 3107240ManunoghiNo ratings yet

- ReadmeDocument2 pagesReadmeVenkat VenkateshanNo ratings yet

- UntitledDocument399 pagesUntitledElemar KiangaNo ratings yet

- UNIX Tips and Tricks For A New UserDocument16 pagesUNIX Tips and Tricks For A New UserkevinNo ratings yet

- HTML TableDocument4 pagesHTML TableTwelve Forty-fourNo ratings yet

- Adbms 1.1234Document53 pagesAdbms 1.1234Anoo ShresthaNo ratings yet

- 5-8: PLA (Programmable Logic Array)Document19 pages5-8: PLA (Programmable Logic Array)Asheque IqbalNo ratings yet

- CPDocument157 pagesCPnaman jaiswalNo ratings yet

- BRKCRS 2113Document60 pagesBRKCRS 2113masterlinh2008No ratings yet

- Oracle Database 11g Data Guard Administration Release 2 - D52161GC30 - 1080544 - USDocument4 pagesOracle Database 11g Data Guard Administration Release 2 - D52161GC30 - 1080544 - USJinendraabhiNo ratings yet

- Encapsulation Security PayloadDocument3 pagesEncapsulation Security PayloadRekha DivyatejNo ratings yet

- Java Programs Java 1658665821Document37 pagesJava Programs Java 1658665821Spoorthi BNo ratings yet

- Proc Us Pack Enterprise Doc UenDocument18 pagesProc Us Pack Enterprise Doc UenAkoKhalediNo ratings yet

- SAS® 9.1 OLAP Server Security: Table 1: Summary of Permissions Required For OLAP-related TasksDocument9 pagesSAS® 9.1 OLAP Server Security: Table 1: Summary of Permissions Required For OLAP-related TasksJoydeep LahiriNo ratings yet

- Encrypted Data Management With Deduplication in Cloud ComputingDocument13 pagesEncrypted Data Management With Deduplication in Cloud ComputingsharathNo ratings yet

- 9 ArraysDocument16 pages9 Arraysyashwanth ThikkavarapuNo ratings yet

- Hercules - Ethernet Converter SETUP UtilityDocument3 pagesHercules - Ethernet Converter SETUP UtilityKoteeswara Rodda100% (1)

- Materi SO - 9Document69 pagesMateri SO - 9135 Novariya Br SaragihNo ratings yet

- Python - How To Parse The Body From A Raw Email, Given That Raw Email Does Not Have A - Body - Tag or Anything - Stack Overflow PDFDocument7 pagesPython - How To Parse The Body From A Raw Email, Given That Raw Email Does Not Have A - Body - Tag or Anything - Stack Overflow PDFAlan PetzoldNo ratings yet

- 0042130740Document2 pages0042130740uzmaNo ratings yet

- Database Migration-What Do You Need To Know Before You Start - AWS Database BlogDocument8 pagesDatabase Migration-What Do You Need To Know Before You Start - AWS Database Blogshu2uNo ratings yet

- CSC1041 Session 10 Python Collection Data TypesDocument25 pagesCSC1041 Session 10 Python Collection Data Typespasan lahiruNo ratings yet

- Zeal Polytechnic, Pune.: Third Year (Ty) Diploma in Computer Engineering Scheme: I Semester: VDocument34 pagesZeal Polytechnic, Pune.: Third Year (Ty) Diploma in Computer Engineering Scheme: I Semester: V974-Abhijeet MotewarNo ratings yet

- 6.4. Building Display Filter ExpressionsDocument8 pages6.4. Building Display Filter ExpressionsalaritooNo ratings yet

- Chương Trình Mẫu Các Bài Tập Học Phần Kỹ Thuật Vi Xử Lý 1. Điều khiển Led đơn và nhận phím bấm sử dụng hàm trễ thời gianDocument34 pagesChương Trình Mẫu Các Bài Tập Học Phần Kỹ Thuật Vi Xử Lý 1. Điều khiển Led đơn và nhận phím bấm sử dụng hàm trễ thời gianThresh GoldNo ratings yet

- 0478 m17 QP 22Document12 pages0478 m17 QP 22Kiron DebNo ratings yet

- SQR User's GuideDocument253 pagesSQR User's Guidevinitpatil85No ratings yet

- HANA Memory OutOfMemoryEvents 1.00.120+Document9 pagesHANA Memory OutOfMemoryEvents 1.00.120+pradeepNo ratings yet

- SQLServer2000 - R3 Com SAPDocument17 pagesSQLServer2000 - R3 Com SAPAlexandre OliveiraNo ratings yet

25CSM04 4 Mbit SPI Serial EEPROM With 128 Bit Seri-2944121

25CSM04 4 Mbit SPI Serial EEPROM With 128 Bit Seri-2944121

Uploaded by

ManunoghiCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

25CSM04 4 Mbit SPI Serial EEPROM With 128 Bit Seri-2944121

25CSM04 4 Mbit SPI Serial EEPROM With 128 Bit Seri-2944121

Uploaded by

ManunoghiCopyright:

Available Formats

25CSM04

4-Mbit SPI Serial EEPROM with 128-Bit Serial Number

and Enhanced Write Protection

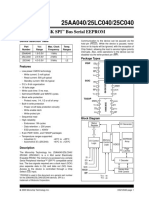

Features Package Types (not to scale)

• 4-Mbit Serial EEPROM:

- 524,288 x 8 organization 8-Lead SOIC

- Page size of 256 bytes

CS 1 8 VCC

- Byte or sequential reads

- Byte or page writes SO 2 7 HOLD

- Self-timed write cycle (5 ms maximum) WP 3 6 SCK

• Security Register: VSS 4 5 SI

- Preprogrammed 128-bit serial number

- 256-byte user-programmable lockable ID

page 8-Ball CSP

8-Pad TDFN-S

• Built-in Error Correction Code (ECC) Logic:

- ECC Status bit via the STATUS register CS 1 8 VCC

VCC CS

• JEDEC® SPI Manufacturer Read ID Support SO 2 7 HOLD

• High-Speed Clock Frequency: WP 3 6 SCK HOLD SO

- 8 MHz at VCC ≥ 3.0V VSS 4 5 SI

- 5 MHz at VCC ≥ 2.5V SCK WP

• Legacy Write Protection Mode: SI VSS

- Block protection functionality (quarter, half or

entire memory array)

• Enhanced Write Protection Mode:

- User-definable memory partitions Pin Function Table

- Each partition can be set independently and

Name Function

have unique protection behavior

• Low-Power CMOS Technology: CS Chip Select Input

- Voltage range: 2.5V to 5.5V SO Serial Data Output

- Write current: 3.0 mA at 5.0V WP Write-Protect Pin

- Read current: 3.0 mA at 5.0V, 8 MHz VSS Ground

- Standby current: 1.0 µA at 2.5V (I-Temp.)

SI Serial Data Input

• High Reliability:

SCK Serial Clock Input

- More than one million erase/write cycles

- Built-in ECC logic for increased reliability HOLD Hold Input

- Data retention: >100 years VCC Supply Voltage

- ESD protection: >4000V

• Available Temperature Ranges:

- Industrial (I): -40°C to +85°C

Packages

• 8-Lead SOIC, 8-Pad TDFN-S and 8-Ball CSP

packages

2019-2022 Microchip Technology Inc. and its subsidiares DS20005817D-page 1

25CSM04

General Description The user-programmable section of the Security

register can later be permanently write-protected via a

The Microchip Technology Inc. 25CSM04 provides software sequence.

4-Mbits of Serial EEPROM utilizing the Serial

Peripheral Interface (SPI) compatible bus. The device The 25CSM04 features a configurable write protection

is organized as 524,288 bytes of 8 bits each scheme which allows the user to select Legacy Write

(512 Kbyte) and is optimized for use in consumer and Protection mode or Enhanced Write Protection mode.

industrial applications where reliable and dependable Legacy Write Protection mode enables the Block

nonvolatile memory storage is essential. The Protection function via the STATUS register. Enhanced

25CSM04 is capable of operation across a broad Write Protection mode segments the memory into

voltage range (2.5V to 5.5V). independent partitions. Each partition can be

configured to inhibit writing based on the status of the

The bus signals required are a clock input (SCK) plus Memory Partition register setting.

separate data in (SI) and data out (SO) lines. Access to

the device is controlled through a Chip Select (CS) For added reliability the 25CSM04 uses a built-in Error

input. Communication to the device can be paused via Correction Code (ECC) scheme. This scheme can

the HOLD pin. While the device is paused, transitions correct up to one incorrectly read bit within four bytes

on its inputs will be ignored, with the exception of Chip read out. Additionally, the 25CSM04 includes a flag in

Select, allowing the host to service higher priority the STATUS register to report if any errors were

interrupts. detected and corrected in the most recent memory

array read sequence.

The 25CSM04 features a nonvolatile Security register

independent of the 4 Mbit main memory array. The first The 25CSM04 features an identification register that

half of the Security register is read-only and contains a contains identification information that can be read

factory-programmed, globally unique 128-bit serial from the device. This enables the application to

number in the first 16 bytes. The 128-bit serial number electronically query and identify the 25CSM04 while it

is unique across the entire CS series of Serial is in the system. The identification method and the

EEPROM products and eliminates the time consuming instruction opcode comply with the JEDEC® standard

step of performing and ensuring serialization of a for “Manufacturer and Device ID Read Methodology for

product on a manufacturing line. The 128-bit read-only SPI Compatible Serial Interface Memory Devices”. The

serial number is followed by an additional 256 bytes of type of information that can be read from the device

user-programmable EEPROM. includes the JEDEC defined Manufacturer ID, the

vendor-specific Device ID, and the vendor-specific

Extended Device Information (EDI).

Bus Connections for the 25CSM04

Client 0 Client 1 Client 2 Client 3

DS20005817D-page 2 2019-2022 Microchip Technology Inc. and its subsidiares

25CSM04

Block Diagram

CS Memory Power

System Control On Reset VCC

High Voltage Module Generator

Generation

Circuit

Register Bank:

STATUS Register

Security Register

Memory Partition Registers

Identification Register

Pause

SO Operation HOLD

Row Decoder

Control

EEPROM Array

1 page

Address Register

and Counter

Security Register

Column Decoder

WP SCK

Data Register

Data Output

Buffer

VSS Write Protection SI

Control

2019-2022 Microchip Technology Inc. and its subsidiares DS20005817D-page 3

25CSM04

1.0 ELECTRICAL CHARACTERISTICS

Absolute Maximum Ratings (†)

VCC ...........................................................................................................................................................................6.25V

All inputs and outputs w.r.t. VSS ...........................................................................................................0.6V to VCC +1.0V

Storage temperature ...............................................................................................................................-65°C to +155°C

Ambient temperature under bias .............................................................................................................-40°C to +125°C

ESD protection on all pins ..........................................................................................................................................4 kV

† NOTICE: Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the

device. This is a stress rating only and functional operation of the device at those or any other conditions above those

indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for

extended periods may affect device reliability.

TABLE 1-1: DC CHARACTERISTICS

DC CHARACTERISTICS Industrial (I): TA = -40°C to +85°C, VCC = +2.5V to 5.5V

Param.

Symbol Characteristic Minimum Maximum Units Test Conditions

No.

D001 VIH High-Level Input Voltage VCC X 0.7 VCC + 1 V

D002 VIL Low-Level Input Voltage -0.3 VCC X 0.3 V VCC ≥ 2.5V

D003 VOL Low-Level Output Voltage — 0.4 V IOL = 3.0 mA, 3.6V ≤ VCC ≤ 5.5V

D004 VOL Low-Level Output Voltage — 0.2 V IOL = 0.15 mA, 2.5V ≤ VCC ≤ 3.6V

D005 VOH High-Level Output Voltage VCC - 0.5 — V IOH = -100 µA

D006 ILI Input Leakage Current — ±1.0 µA CS = VCC, VIN = VSS or VCC

D007 ILO Output Leakage Current — ±1.0 µA CS = VCC, VOUT = VSS or VCC

Internal Capacitance TA = +25°C, FCLK = 1.0 MHz,

D008 CINT — 7.0 pF

(all inputs and outputs) VCC = 5.0V (Note 1)

VCC = 5.0V, SCK = 8 MHz,

— 3.0 mA

SO = Open

D009 ICCREAD Operating Current

VCC ≤ 3.0V, SCK = 5 MHz,

— 2.0 mA

SO = Open

D010 ICCWRITE Operating Current — 3.0 mA VCC = 5.0V

VCC = 5.0V, CS = VCC,

— 2.0 µA

VIN = VCC or VSS

D011 ICCS Standby Current

VCC = 2.5V, CS = VCC,

— 1.0 µA

VIN = VCC or VSS

Note 1: This parameter is not tested but ensured by characterization.

DS20005817D-page 4 2019-2022 Microchip Technology Inc. and its subsidiares

25CSM04

TABLE 1-2: AC CHARACTERISTICS

AC CHARACTERISTICS Industrial (I): TA = -40°C to +85°C VCC = 2.5V to 5.5V

Param.

Symbol Characteristic Minimum Maximum Units Test Conditions

No.

— 8 MHz VCC ≥ 3.0V

1 FCLK Clock Frequency

— 5 MHz VCC ≥ 2.5V

30 — ns VCC ≥ 3.0V

2 TCSS CS Setup Time

60 — ns VCC ≥ 2.5V

30 — ns VCC ≥ 3.0V

3 TCSH CS Hold Time

60 — ns VCC ≥ 2.5V

30 — ns VCC ≥ 3.0V

4 TCSD CS Disable Time

60 — ns VCC ≥ 2.5V

10 — ns VCC ≥ 3.0V

5 TSU Data Setup Time

20 — ns VCC ≥ 2.5V

10 — ns VCC ≥ 3.0V

6 THD Data Hold Time

20 — ns VCC ≥ 2.5V

7 TR CLK Rise Time — 50 ns Note 1

8 TF CLK Fall Time — 50 ns Note 1

40 — ns VCC ≥ 3.0V

9 THI Clock High Time

80 — ns VCC ≥ 2.5V

40 — ns VCC ≥ 3.0V

10 TLO Clock Low Time

80 — ns VCC ≥ 2.5V

11 TCLD Clock Delay Time 50 — ns

12 TCLE Clock Enable Time 50 — ns

— 40 ns VCC ≥ 3.0V

13 TV Output Valid from Clock Low

— 80 ns VCC ≥ 2.5V

14 THO Output Hold Time 0 — ns Note 1

— 40 ns VCC ≥ 3.0V

15 TDIS Output Disable Time

— 80 ns VCC ≥ 2.5V

10 — ns VCC ≥ 3.0V

16 THS HOLD Setup Time

20 — ns VCC ≥ 2.5V

10 — ns VCC ≥ 3.0V

17 THH HOLD Hold Time

20 — ns VCC ≥ 2.5V

— 40 ns VCC ≥ 3.0V (Note 1)

18 THZ HOLD Low to Output High Z

— 80 ns VCC ≥ 2.5V (Note 1)

— 40 ns VCC ≥ 3.0V

19 THV HOLD High to Output Valid

— 80 ns VCC ≥ 2.5V

20 TWC Internal Write Cycle Time — 5 ms Note 2

Note 1: This parameter is not tested but ensured by characterization.

2: TWC begins on the rising edge of CS after a valid write sequence and ends when the internal write cycle

is complete.

2019-2022 Microchip Technology Inc. and its subsidiares DS20005817D-page 5

25CSM04

FIGURE 1-1: INPUT TEST WAVEFORMS FIGURE 1-2: OUTPUT TEST LOAD

AND MEASUREMENT

LEVELS

Device

0.9 VCC under

AC AC Test

Driving VCC/2 Measurement

Level Level 30 pF

0.1 VCC

Note: tR, tF < 2 ns (10% to 90%)

FIGURE 1-3: SERIAL INPUT TIMING

CS 12

2 11

7

Mode 1,1 8 3

SCK Mode 0,0

5 6

SI MSb in LSb in

High-Impedance

SO

FIGURE 1-4: SERIAL OUTPUT TIMING

CS

9 10 3

Mode 1,1

SCK Mode 0,0

13

14 15

SO MSb out LSb out

Don’t Care

SI

DS20005817D-page 6 2019-2022 Microchip Technology Inc. and its subsidiares

25CSM04

FIGURE 1-5: HOLD TIMING

CS

17 17

16 16

SCK

18 19

High-Impedance

SO n+2 n+1 n n n-1

Don’t Care 5

SI n+2 n+1 n n n-1

HOLD

TABLE 1-3: EEPROM CELL PERFORMANCE CHARACTERISTICS

Operation Test Condition Minimum Maximum Units

Write Endurance(1,2) TA = +25°C, 2.5V ≤ VCC ≤ 5.5V 1,000,000 — Write Cycles

Data Retention(1) TA = +55°C 100 — Years

Note 1: Performance is determined through characterization and the qualification process.

2: Due to the memory array architecture, the write cycle endurance is specified for write sequences in groups

of four data bytes. The beginning of any 4-byte boundaries can be determined by multiplying any integer

(N) by four (i.e., 4*N). The end address can be found by adding three to the beginning value (i.e., 4*N+3).

See Section 8.2 “Error Correction Code (ECC) Architecture” for more details on this implementation.

2019-2022 Microchip Technology Inc. and its subsidiares DS20005817D-page 7

25CSM04

1.1 Power-Up Requirements and

Default Conditions

During a power-up sequence, the VCC supplied to the

25CSM04 should monotonically rise from VSS to the

minimum VCC level as specified in Table 1-1 with a

slew rate no faster than 0.1 V/µs.

1.1.1 DEVICE POWER-ON RESET

TABLE 1-4: POWER-UP CONDITIONS

Symbol Parameter Minimum Maximum Units

TVCSL Minimum VCC to Chip Select Low Time 100 — µs

VPOR Power-on Reset Threshold Voltage — 1.5 V

TPOFF Minimum time at VCC = 0V between power cycles 1 — ms

To prevent spurious events from happening during a 1.1.2 SOFTWARE RESET

power-up sequence, the 25CSM04 includes a

The 25CSM04 includes a Software Device Reset

Power-on Reset (POR) circuit. Upon power-up, the

(SRST) instruction that gives the user the opportunity to

device will not respond to any instructions until the VCC

reset the device to its power-on default behavior

level crosses the internal voltage threshold (VPOR) that

(Section 1.2 “Device Default State”) without the need

brings the device out of Reset and into Standby mode.

to power cycle the device. To execute this Reset, first,

Microchip recommends that CS follows the rise of VCC the CS pin must be driven low to select the device and

at power-up through the use of a pull-up resistor. The then a 7Ch opcode is clocked in on the SI pin.

system designer must ensure that no instruction is sent

Then the CS pin can be driven high and the Reset

to the device and CS is driven high until the VCC supply

mechanism will engage. The Reset will have internally

reaches a stable value greater than the minimum VCC

completed by the time the minimum TCSD time is

level. Once VCC has surpassed the minimum level, the

satisfied.

SPI host must wait at least TVCSL before asserting the

CS pin. See Table 1-4 for the values associated with

Note: The SRST instruction cannot interrupt the

these power-up parameters.

device while it is in a Busy state

If an event occurs in the system where the VCC level (Section 6.1.4 “Ready/Busy Status

supplied to the 25CSM04 drops below the maximum Latch”).

VPOR level specified, it is recommended that a full

power cycle sequence be performed by first driving the

VCC pin to VSS, waiting at least the minimum TPOFF

time and then performing a new power-up sequence in

compliance with the requirements defined in this

section.

FIGURE 1-6: SOFTWARE DEVICE RESET (SRST) INSTRUCTION

CS

0 1 2 3 4 5 6 7

SCK

SRST Opcode (7Ch)

SI 0 1 1 1 1 1 0 0

MSb

High-Impedance

SO

DS20005817D-page 8 2019-2022 Microchip Technology Inc. and its subsidiares

25CSM04

1.2 Device Default State The Security register contains a preprogrammed,

128-bit serial number in the lower 16 bytes. The

1.2.1 POWER-UP DEFAULT STATE user-programmable portion (lockable ID page) is

unlocked and set to logic ‘1’ resulting in 256 bytes of

The 25CSM04 default state upon power-up consists of:

FFh data. In the various device registers, the following

• Standby mode (CS = HIGH) nonvolatile bits are set:

• A high-to-low level transition on CS is required to • Write Protection Enable (WPEN) bit in the

enter the active state STATUS register is set to logic ‘0’ allowing writing

• Write Enable Latch (WEL) bit in the STATUS to the STATUS register. (See Table 1-5).

register = 0 • Block Write-Protect (BP[1:0] bits in the STATUS

• Error Correction State Latch (ECS) bit in the register are logic ‘0’ indicating no write protection

STATUS register = 0 set when in Legacy mode. (See Table 1-5).

• Partition Register Write Enable Latch (PREL) bit • Write Protection Mode (WPM) bit in the STATUS

in the STATUS register = 0 register is set to logic ‘0’, indicating the device is

• Ready/Busy (RDY/BUSY) bit in the STATUS set for Legacy Write Protection mode. (See

register = 0, indicating the device is ready to Table 1-6).

accept a new instruction • Freeze Memory Protection Configuration (FMPC)

bit in the STATUS register is set to logic ‘0’,

1.2.2 DEVICE FACTORY DEFAULT indicating the Memory Partition Registers (MPRs)

CONDITION and the Write Protection Mode (WPM) bit are not

locked and can be changed. (See Table 1-6).

The 25CSM04 is shipped to the customer with the

• Protect Address Boundary Protection (PABP) bit

EEPROM array set to an all FFh data pattern (logic ‘1’

in the STATUS register is set to logic ‘0’, indicat-

state).

ing the partition endpoint address value in each

MPR can be modified. (See Table 1-6).

• Memory Partition Registers (MPR0-MPR7) are

set to 00h, indicating that the entire 4 Mbit

memory can be written. (See Table 1-7).

TABLE 1-5: STATUS REGISTER BITS – BYTE 0 (FACTORY DEFAULT)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

WPEN Reserved Reserved Reserved BP1 BP0 WEL(1) RDY/BUSY(1)

0 0 0 0 0 0 0 0

Note 1: These bits are volatile and reset to this value upon power-up.

TABLE 1-6: STATUS REGISTER BITS – BYTE 1 (FACTORY DEFAULT)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

WPM ECS(1) FMPC PREL(1) PABP Reserved Reserved RDY/BUSY(1)

0 0 0 0 0 0 0 0

Note 1: These bits are volatile and reset to this value upon power-up.

2019-2022 Microchip Technology Inc. and its subsidiares DS20005817D-page 9

25CSM04

TABLE 1-7: MEMORY PARTITION REGISTERS (FACTORY DEFAULT)

MPR No. Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Partition Behavior Partition Endpoint Address

A18 A17 A16 A15 A14 A13

MPR0 0 0 0 0 0 0 0 0

MPR1 0 0 0 0 0 0 0 0

MPR2 0 0 0 0 0 0 0 0

MPR3 0 0 0 0 0 0 0 0

MPR4 0 0 0 0 0 0 0 0

MPR5 0 0 0 0 0 0 0 0

MPR6 0 0 0 0 0 0 0 0

MPR7 0 0 0 0 0 0 0 0

DS20005817D-page 10 2019-2022 Microchip Technology Inc. and its subsidiares

25CSM04

2.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 2-1.

TABLE 2-1: PIN FUNCTION TABLE

Name 8-Lead SOIC 8-Pad TDFN-S(1) 8-Ball CSP Function

CS 1 1 1 Chip Select Input

SO 2 2 2 Serial Data Output

WP 3 3 3 Write-Protect

VSS 4 4 4 Ground

SI 5 5 5 Serial Data Input

SCK 6 6 6 Serial Clock Input

HOLD 7 7 7 Hold Input

VCC 8 8 8 Device Power Supply

Note 1: The exposed pad on the TDFN-S package can be connected to VSS or left floating.

2.1 Chip Select (CS) 2.5 Serial Clock (SCK)

Asserting the CS pin selects the device. When the CS The Serial Clock (SCK) pin is used to provide a clock

pin is deasserted, the device will be deselected and signal to the device and is used to synchronize the flow

placed in Standby mode and the SO pin will be in a of data to and from the device. Instructions, addresses

high-impedance state. When the device is deselected, and data present on SI pin are always latched in on the

data will not be accepted on the SI pin. rising edge of SCK, while output data on the SO pin are

A high-to-low transition on the CS pin is required to always clocked out on the falling edge of SCK.

start a sequence and a low-to-high transition is

required to end a sequence. For write sequences, the 2.6 Hold (HOLD)

device will not enter Standby mode until the completion

When the device is selected and a serial

of the self-timed internal write cycle.

communication sequence is underway, HOLD can be

used to pause the communication with the host device

2.2 Serial Data Output (SO) without resetting the serial sequence.

The SO pin is used to shift data out from the device.

Data on the SO pin are always clocked out on the

falling edge of SCK. The SO pin is in a high-impedance

state whenever the device is deselected (CS is

deasserted) as well as when the Hold function is

engaged.

2.3 Write-Protect Pin (WP)

The Write-Protect (WP) pin can be used to protect the

STATUS register and memory array contents via the

Block Protection modes when Legacy Write Protection

mode is enabled.

When Enhanced Write Protection mode is enabled, the

WP pin can be used to protect any memory zone in

accordance with how its corresponding Memory

Partition registers are programmed.

2.4 Serial Data Input (SI)

Instructions, addresses and data are latched by the

25CSM04 on the rising edge of the Serial Clock (SCK)

line via the Serial Data Input (SI) pin.

2019-2022 Microchip Technology Inc. and its subsidiares DS20005817D-page 11

25CSM04

3.0 MEMORY ORGANIZATION 3.2.3 MEMORY PARTITION REGISTERS

The 25CSM04 is equipped with eight Memory Partition

3.1 EEPROM Organization registers. Each register is an 8-bit nonvolatile register

which can be programmed with an ending address for

The 25CSM04 is internally organized as 2,048 pages

the partition as well as determine the behavior of that

of 256 bytes each.

partition. The partition protection can be set to one of

four levels:

3.2 Device Registers

• Unprotected

The 25CSM04 contains four types of registers that

• Software write-protected

modulate device operation and/or report on the current

status of the device. These registers are: • Hardware write-protected by the WP pin

• STATUS register • Software write-protected with locked memory

• Security register partition register

• Memory Partition registers (eight total) A complete description of the Memory Partition register

• Identification register function can be found in Section 10.0 “Memory

Partition Functionality”.

3.2.1 STATUS REGISTER

The STATUS register is a 16-bit combination of volatile 3.2.4 IDENTIFICATION REGISTER

and nonvolatile bits. It is used to modify the write The Identification register is a 40-bit nonvolatile,

protection functions as well as store various aspects of read-only register that contains device identification

the current status of the device. Details about the data in compliance with the JEDEC® standard for

STATUS register are covered in Section 6.0 “STATUS “Manufacturer and Device ID Read Methodology for

Register”. SPI Compatible Serial Interface Memory Devices”. The

contents and format of the Identification register can be

3.2.2 SECURITY REGISTER reviewed in Section 11.1 “Reading the Identification

The Security register is split into a read-only section Register”.

and a user-programmable lockable ID page section.

The read-only section contains a preprogrammed,

globally unique, 128-bit serial number.

The user-programmable (lockable ID page) section of

the Security register is ideal for applications that need

to irreversibly protect critical or sensitive application

data from ever being altered. See Section 9.0

“Security Register” for more details about the

Security register.

FIGURE 3-1: MEMORY ORGANIZATION

Memory Address Range Protection Features

Legacy Write Protection

• Block Protection (BP bits in STATUS register)

• Hardware Write Protection

4-Mbit 4-Mbit Address Range: (WP pin via STATUS register)

EEPROM 000000h–07FFFFh

Enhanced Write Protection

• User-Definable Memory Partitioning (WP Pin or

Software Write Protection)

128-bit Serial Number Reserved for Future Use (FFh)

Address Range Address Range Read-Only

4-Kbit (000000h–00000Fh) (000010h–0000FFh)

Security

Register User-Programmable Lockable ID Page Permanently Lockable by

Address Range (000100h–0001FFh) Software

DS20005817D-page 12 2019-2022 Microchip Technology Inc. and its subsidiares

25CSM04

4.0 FUNCTIONAL DESCRIPTION The SPI protocol defines a total of four modes of

operation (Mode 0, 1, 2, or 3) with each mode differing

in respect to the SCK polarity and phase and how the

4.1 Device Operation

polarity and phase control the flow of data on the SPI

The 25CSM04 is controlled by a set of instructions that bus. The 25CSM04 supports the two most common

are sent from a host controller, commonly referred to as modes, SPI Mode 0 and 3. With SPI Modes 0 and 3,

the SPI host. The SPI host communicates with the data are always latched in on the rising edge of SCK

25CSM04 via the SPI bus which is comprised of four and always output on the falling edge of SCK. The only

signal lines: difference between SPI Modes 0 and 3 is the polarity of

the SCK signal when in the inactive state (when the SPI

• Chip Select (CS)

host is in Standby mode and not transferring any data).

• Serial Clock (SCK) SPI Mode 0 is defined as a low SCK while CS is not

• Serial Input (SI) asserted (high) and SPI Mode 3 has SCK high in the

• Serial Output (SO) inactive state. The SCK Idle state must match when the

CS is deasserted both before and after the

communication sequence in SPI Mode 0 and 3.

The figures in this document depict Mode 0 with a solid

line on SCK while CS is inactive and Mode 3 with a

dotted line.

FIGURE 4-1: SPI MODE 0 AND MODE 3

CS

Mode 3 Mode 3

SCK Mode 0 Mode 0

SI MSb LSb

SO MSb LSb

4.2 Interfacing the 25CSM04 on the 4.2.2 SENDING DATA TO THE DEVICE

SPI Bus The 25CSM04 uses the Serial Data Input (SI) pin to

receive information. All instructions, addresses and

Communication to and from the 25CSM04 must be

data input bytes are clocked into the device with the

initiated by the SPI host device. The SPI host device

Most Significant bit (MSb) first. The SI pin begins

must generate the serial clock for the 25CSM04 on the

sampling on the first rising edge of the SCK line after

SCK pin. The 25CSM04 always operates as a client

the CS has been asserted.

due to the fact that the Serial Clock pin (SCK) is always

an input.

4.2.3 RECEIVING DATA FROM THE

4.2.1 SELECTING THE DEVICE DEVICE

The 25CSM04 is selected when the CS pin is low. Data output from the device is transmitted on the Serial

When the device is not selected, data will not be Data Output (SO) pin with the MSb output first. The SO

accepted via the SI pin and the SO pin will remain in a data are latched on the falling edge of the first SCK

high-impedance state. clock cycle after the instruction and address bytes, if

necessary, have been clocked into the device.

2019-2022 Microchip Technology Inc. and its subsidiares DS20005817D-page 13

25CSM04

4.3 Device Opcodes

4.3.1 SERIAL OPCODE

After the device is selected by driving CS low, the first

byte sent must be the opcode that defines the

sequence to be performed.

The 25CSM04 utilizes an 8-bit instruction register. The

list of instructions and their operation opcodes are

contained in Table 4-1. All instructions, addresses and

data are transferred with the MSb first and are initiated

with a high-to-low CS transition.

TABLE 4-1: INSTRUCTION SET FOR 25CSM04

Address Data Reference

Instruction Instruction Description Opcode

Bytes Bytes Section

STATUS Register Instructions

RDSR Read STATUS Register 05h 0000 0101 0 1 or 2 6.2

WRBP Write Ready/Busy Poll 08h 0000 1000 0 1 6.1.4.1

WREN Set Write Enable Latch (WEL) 06h 0000 0110 0 0 5.1

WRDI Reset Write Enable Latch (WEL) 04h 0000 0100 0 0 5.2

WRSR Write STATUS Register 01h 0000 0001 0 1 or 2 6.3

EEPROM and Security Register Instructions

READ Read from EEPROM Array 03h 0000 0011 3 1+ 7.1

WRITE Write to EEPROM Array (1 to 256 bytes) 02h 0000 0010 3 1+ 8.0

RDEX Read from the Security Register 83h 1000 0011 3 1+ 9.1

WREX Write to the Security Register 82h 1000 0010 3 1+ 9.2

LOCK Lock the Security Register (permanent) 82h 1000 0010 3 1 9.2.1

CHLK Check Lock Status of Security Register 83h 1000 0011 3 1 9.2.2

Memory Partition Register Instructions

RMPR Read Contents of Memory Partition Registers 31h 0011 0001 3 1 10.3

PRWE Set Memory Partition Write Enable Latch 07h 0000 0111 0 0 10.2.1

PRWD Reset Memory Partition Write Enable Latch 0Ah 0000 1010 0 0 10.2.2

WMPR Write Memory Partition Registers 32h 0011 0010 3 1 10.2.3

PPAB Protect Partition Address Boundaries 34h 0011 0100 3 1 10.1.3

FRZR Freeze Memory Protection Configuration (per- 37h 0011 0111 3 1 4.5.4

manent)

Identification Register Instructions

SPID Read the SPI Manufacturer ID Data 9Fh 1001 1111 0 5 11.1

Device Reset Instruction

SRST Software Device Reset 7Ch 0111 1100 0 0 1.1.2

DS20005817D-page 14 2019-2022 Microchip Technology Inc. and its subsidiares

25CSM04

4.4 Hold Function While in Hold mode, the SO pin will be in a high-imped-

ance state. In addition, both the SI pin and the SCK pin

The HOLD pin is used to pause the serial will be ignored. The WP pin, however, can still be

communication with the device without having to stop asserted or deasserted while in the Hold mode.

or reset the clock sequence. The Hold mode, however,

does not have an effect on the internal write cycle. To end the Hold mode and resume serial communica-

Therefore, if a write cycle is in progress, asserting the tion, the HOLD pin must be deasserted during the SCK

HOLD pin will not pause the sequence and the write low pulse. If the HOLD pin is deasserted during the

cycle will continue until it is finished. SCK high pulse, then the Hold mode will not end until

the beginning of the next SCK low pulse.

The Hold mode can only be entered while the CS pin is

asserted. The Hold mode is activated by asserting the If the CS pin is deasserted while the HOLD pin is still

HOLD pin during the SCK low pulse. If the HOLD pin is asserted, then any sequence that may have been

asserted during the SCK high pulse, then the Hold started will be aborted.

mode will not be started until the beginning of the next

SCK low pulse. The device will remain in the Hold

mode as long as the HOLD pin and CS pin are

asserted.

FIGURE 4-2: HOLD MODE

CS

SCK

Hold Hold Hold

HOLD

4.5 Write Protection Additionally, the contents of the STATUS register can

be protected by enabling the Write-Protect Enable

The 25CSM04 write protection schemes are first (WPEN) bit in the STATUS register.

controlled by the state of Write Protection Mode (WPM)

bit in the STATUS register (bit 7, byte 1). The device When the WPEN function is enabled, the STATUS reg-

can be set for either Legacy Write Protection mode or ister contents will be protected when the WP pin is

Enhanced Write Protection mode by the state of the asserted (low). Details about the WPEN function are

WPM bit. provided in Section 6.1.1 “Write-Protect Enable Bit”.

The write protection mode can be made permanent by 4.5.2 ENHANCED WRITE PROTECTION

executing the FRZR instruction. This can be done in MODE

both Legacy Write Protection mode and Enhanced

Write Protection mode. Refer to Section 4.5.4 “Freeze In Enhanced Write Protection mode, the EEPROM

Memory Protection Configuration (FRZR)” for protection is determined by the contents of the Memory

details. Partition Registers (MPR). Each MPR can be

programmed to specify the ending address of a given

4.5.1 LEGACY WRITE PROTECTION partition as well as to set the desired protection

MODE behavior of that partition.

In Legacy Write Protection mode, the EEPROM array Full details about the Memory Partition registers can be

can only be programmed in accordance with how the found in Section 10.0 “Memory Partition Functional-

Block Protect bits in the STATUS register are ity”.

programmed. Refer to Section 6.1.2 “Block Note: If Enhanced Write Protection mode is

Write-Protect Bits” for details. disabled, the MPRs will be ignored

regardless of their configured behavior.

2019-2022 Microchip Technology Inc. and its subsidiares DS20005817D-page 15

25CSM04

4.5.3 WRITE-PROTECT PIN FUNCTION Before a FRZR instruction can be issued, first a WREN

instruction must be issued to set the WEL bit in the

While in both Legacy Write Protection mode and

STATUS register to a logic ‘1’, followed by a PRWE

Enhanced Write Protection mode, writing to the

instruction to set the PREL bit to a logic ‘1’ as well.

STATUS register and the Memory Partition registers

Once these two steps are complete, the FRZR instruc-

can be inhibited by enabling the WPEN bit in the

tion can be sent to the device.

STATUS register. When the WPEN function is enabled,

the contents of these registers will be protected when

the WP pin is asserted (low). In order for these Note: The FRZR instruction will be ignored if the

registers to be protected, the WP pin must be asserted WPEN Bit (byte 0, bit 7) of the STATUS

for the entire CS valid time. Details about the WPEN register is set to a logic ‘1’ and the WP pin

function are provided in Section 6.1.1 “Write-Protect is asserted.

Enable Bit”. To freeze the state of the Memory Protection

If the internal write cycle has already been initiated, WP Configuration with the FRZR instruction, the CS pin

pin going low will have no effect on any write sequence. must be driven low, followed by sending an opcode of

37h to the device on the SI line. Next, an address of

The WP pin function is blocked when the WPEN bit in

AA40h is sent, followed by a confirmation data byte of

the STATUS register is a logic ‘0’. This will allow the

D2h. Upon deasserting the CS pin, the device will

user to install the 25CSM04 device in a system with the

begin a self-timed internal write cycle to set the FMPC

WP pin tied to VSS and still be able to write to the

bit, freeze all eight Memory Partition registers and the

STATUS register. All WP pin functions are enabled

Write Protection Mode (WPM) bit in the STATUS

when the WPEN bit is set to a logic ‘1’.

register.

4.5.4 FREEZE MEMORY PROTECTION

CONFIGURATION (FRZR)

Note: Once the Memory Partition Registers and

The current state of the Memory Partition registers and WPM bit have been frozen, it will be

write protection mode can be permanently frozen so impossible to change their state.

that no further modification of their contents is possible.

This is accomplished by the use of the Freeze Memory Once the write cycle is completed, the PREL bit and

Protection Configuration (FRZR) instruction. For addi- WEL bit in the STATUS register will be reset back to the

tional information on the Memory Partition registers, logic ‘0’ state, the WPM STATUS register bit (bit 7, byte

refer to Section 10.0 “Memory Partition Functional- 1) will be permanently set to its current state and the

ity”. FMPC STATUS register bit (bit 5, byte 1) will be

permanently set to a logic ‘1’ to indicate that the

Memory Protection Configuration has been frozen. If

Note: The Write-Protect Enable (WPEN) and

the registers and WPM bit have already been frozen,

Block Protection (BP[1:0]) bits are not

any attempt to issue the FRZR instruction will be

affected by the FRZR instruction.

ignored. The device will return to the Idle state once the

CS pin has been deasserted.

Note: If the CS pin is deasserted before the end

of the 40-bit sequence, the instruction will

be aborted and no write cycle will take

place.

DS20005817D-page 16 2019-2022 Microchip Technology Inc. and its subsidiares

25CSM04

FIGURE 4-3: FREEZE MEMORY PROTECTION CONFIGURATION (FRZR) SEQUENCE

CS

TWC(1)

0 1 2 3 4 5 6 7 8 9 10 11 12 29 30 31 32 33 34 35 36 37 38 39

SCK

FRZR Opcode (37h) Address Bits A23-A0(2) Data In (D2h)

SI 0 0 1 1 0 1 1 1 X X X X X X 0 0 0 0 1 1 0 1 0 0 1 0

MSb MSb MSb

High-Impedance

SO

Note 1: This sequence initiates a self-timed internal write cycle on the rising edge of CS after a valid sequence.

2: Address bits A23-A16 are ignored. Address bits A15-A0 must be set to AA40h.

2019-2022 Microchip Technology Inc. and its subsidiares DS20005817D-page 17

25CSM04

5.0 WRITE ENABLE AND DISABLE The WEL bit will be reset to a logic ‘0’ in the following

circumstances:

5.1 Write Enable Instruction (WREN) • Upon power-up as the power-on default condition

is the Write Disable state (Section 1.2.2 “Device

The Write Enable Latch (WEL) bit of the STATUS Factory Default Condition”)

register must be set to a logic ‘1’ prior to each WRSR,

• The successful completion of any write sequence

WRITE, WREX, LOCK, PPWE, WMPR, PPAB and FRZR

(WRITE, WRSR, WREX, LOCK, WMPR, PPAB, FRZR)

instructions. Some of these sequences need further

instructions prior to being executed and are noted in • Executing a Write Disable (WRDI) instruction

their corresponding section. The WEL bit is set to a (Section 5.2 “Write Disable Instruction

logic ‘1’ by sending a WREN (06h) instruction to the (WRDI)”)

25CSM04. First, the CS pin is driven low to select the • Executing a Software Device Reset (SRST)

device and then a 06h instruction is clocked in on the instruction

SI pin. Then the CS pin is driven high. The WEL bit will

be immediately updated in the STATUS register to a

logic ‘1’.

FIGURE 5-1: WRITE ENABLE (WREN) INSTRUCTION

CS

0 1 2 3 4 5 6 7

SCK

WREN Opcode (06h)

SI 0 0 0 0 0 1 1 0

MSb

High-Impedance

SO

5.2 Write Disable Instruction (WRDI)

To protect the device against inadvertent write

sequences, the Write Disable (04h) instruction disables

all programming modes by setting the WEL bit to a

logic ‘0’. The WRDI instruction is independent of the

WP pin state.

FIGURE 5-2: WRITE DISABLE (WRDI) INSTRUCTION

CS

0 1 2 3 4 5 6 7

SCK

WRDI Opcode (04h)

SI 0 0 0 0 0 1 0 0

MSb

High-Impedance

SO

DS20005817D-page 18 2019-2022 Microchip Technology Inc. and its subsidiares

25CSM04

6.0 STATUS REGISTER

6.1 Status Register Bit Definition

The 25CSM04 includes a 2-byte STATUS register

which is a combination of six nonvolatile bits of

EEPROM and five volatile latches. The STATUS

register bits modulate various features of the device as

shown in Register 6-1 and Register 6-2. These bits can

be read or modified by specific instructions that are

detailed in the subsequent sections.

REGISTER 6-1: STATUS REGISTER (BYTE 0)

R/W U-0 U-0 U-0 R/W R/W R-0 R-0

WPEN — — — BP1 BP0 WEL RDY/BSY

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 7 WPEN: Write-Protect Enable bit

1 = Write-Protect pin is enabled

0 = Write-Protect pin is ignored

bit 6-4 Unimplemented: Read as ‘0’

bit 3-2 BP[1:0]: Block Protection bits (see Table 6-2)

00 = No array write protection

01 = Upper quarter memory array protection

10 = Upper half memory array protection

11 = Entire memory array protection

bit 1 WEL: Write Enable Latch bit

1 = WREN has been executed and device is enabled for writing

0 = Device is not write-enabled

bit 0 RDY/BSY: Ready/Busy Status Latch bit

1 = Device is busy with an internal write cycle

0 = Device is ready for a new sequence

2019-2022 Microchip Technology Inc. and its subsidiares DS20005817D-page 19

25CSM04

REGISTER 6-2: STATUS REGISTER (BYTE 1)

R/W-1 R-0 R R-0 R U-0 U-0 R-0

WPM ECS FMPC PREL PABP — — RDY/BSY

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 7 WPM: Write Protection Mode bit(1)

1 = Enhanced Write Protection mode selected

0 = Legacy Write Protection mode selected

bit 6 ECS: Error Correction State Latch bit

1 = The previously executed read sequence did require the Error Correction Code (ECC)

0 = The previous executed read sequence did not require the Error Correction Code (ECC)

bit 5 FMPC: Freeze Memory Protection Configuration bit(2)

1 = Memory Partition registers and write protection mode are permanently frozen and cannot be

modified

0 = Memory Partition registers and write protection mode are not frozen and are modifiable

bit 4 PREL: Partition Register Write Enable Latch bit

1 = PRWE has been executed and WMPR, FRZR and PPAB instructions are enabled

0 = WMPR, FRZR and PPAB instructions are disabled

bit 3 PABP: Partition Address Boundary Protection bit

1 = Partition Address Endpoints set in Memory Partition registers cannot be modified

0 = Partition Address Endpoints set in Memory Partition registers are modifiable

bit 2-1 Unimplemented: Read as ‘0’

bit 0 RDY/BSY: Ready/Busy Status Latch bit

1 = Device is busy with an internal write cycle

0 = Device is ready for a new sequence

Note 1: If the FMPC bit is set to a logic ‘1’, the WPM bit is read-only.

2: Once the FMPC bit has been set, it cannot be cleared.

6.1.1 WRITE-PROTECT ENABLE BIT

The Write-Protect Enable (WPEN) bit in the STATUS

register (byte 0, bit 7) can be used in conjunction with

the WP pin to inhibit writing to the various registers

within the device.

The device is hardware write-protected when both the

WP pin is low and the WPEN bit has been set to a

logic ‘1’. The affected registers depend on the write

protection mode selected.

The write protection mode is determined by the WPM

bit in the STATUS register (bit 7, byte 1). Hardware

write protection is disabled when either the WP pin is

deasserted (high) or the WPEN bit is a logic ‘0’.

Table 6-1 describes which registers will be protected

from being modified. The WP pin must be asserted

(low) to enable any protection capabilities.

DS20005817D-page 20 2019-2022 Microchip Technology Inc. and its subsidiares

25CSM04

TABLE 6-1: REGISTER BEHAVIOR IN LEGACY WRITE PROTECTION AND ENHANCED WRITE

PROTECTION MODES

Write Protection Memory Partition

WP Pin WPEN Bit STATUS Register

Mode Registers

Low 0 Not Protected Not Protected

Legacy or

Low 1 Protected Protected

Enhanced

High X Not Protected Not Protected

Note: When the WPEN bit is a logic ‘1’, it cannot be changed back to a logic ‘0’, as long as the WP pin is asserted

(low).

When the device is hardware write-protected, the The four levels of array protection are:

nonvolatile bits of the STATUS register (WPEN, BP1, • Level 0 – No portion of the EEPROM is protected,

BP0, WPM, FMPC, PABP) become read-only and the while the lower 256 bytes of the Security register

Write STATUS Register (WRSR), Freeze Memory are read-only.

Protection Configuration (FRZR) and Protect Partition

• Level 1 – The upper quarter address range is

Address Boundaries (PPAB), Write Memory Partition

write-protected meaning the highest order 1 Mbits

Registers (WMPR) and Lock the Security Register

in the EEPROM are read-only. The lower

(LOCK) instructions will not be accepted.

256 bytes of the Security register are read-only.

6.1.2 BLOCK WRITE-PROTECT BITS • Level 2 – The upper half address range is

write-protected meaning the highest order 2 Mbits

The 25CSM04 contains four levels of EEPROM write

in the EEPROM are read-only. The lower

protection using the Block Protection function. The

256 bytes of the Security register are read-only.

nonvolatile Block Write-Protect bits (BP1, BP0) are

located in bits three and two of the first STATUS • Level 3 – Both the EEPROM and Security

register byte and define the region of the EEPROM and register are write-protected meaning all

Security register that are to be treated as read-only. addresses are read-only.

These values are only valid if the device has been set The address ranges that are protected for each Block

to Legacy Write Protection mode via the WPM STATUS Write Protection level and corresponding STATUS

register bit (byte 1, bit 7). register control bits are shown in Table 6-2.

TABLE 6-2: BLOCK WRITE-PROTECT BITS

STATUS Register Byte 0

Protected Address Range

Level Bits [3:2]

BP1 BP0 Memory Region 25CSM04

0 0 0 EEPROM None

Security Register 00000h-000FFh

1 0 1 EEPROM 60000h-7FFFFh

Security Register 00000h-000FFh

2 1 0 EEPROM 40000h-7FFFFh

Security Register 00000h-000FFh

3 1 1 EEPROM 00000h-7FFFFh

Security Register 00000h-001FFh

Note: The Block Protection mechanism will only function with the WPM bit of the STATUS register (bit 7, byte 1)

set to a logic ‘0’, indicating Legacy Write Protection mode. If the WPM is set to logic ‘1’, the device will

respond in accordance with the Enhanced Write Protection mode. For more details on the Enhanced Write

Protection mode, refer to Section 10.1 “Enhanced Write Protection Mode”.

2019-2022 Microchip Technology Inc. and its subsidiares DS20005817D-page 21

25CSM04

6.1.3 WRITE ENABLE LATCH A logic ‘0’ bit in this position indicates the device is

ready to accept new instructions.

Enabling and disabling writing to any nonvolatile

register, the EEPROM array, and the Security register

6.1.4.1 Write Ready/Busy Poll

is accomplished through the Write Enable instruction

(WREN) as shown in Section 5.1 “Write Enable The Write Ready/Busy Poll (WRBP) instruction provides

Instruction (WREN)” and the Write Disable instruction direct access to the Ready/Busy STATUS register bit in

(WRDI) as shown in Section 5.2 “Write Disable an 8-bit format. The WRBP instruction can be used after

Instruction (WRDI)”. These functions change the any nonvolatile write sequence as a means to check if

state of the Write Enable Latch (WEL) bit (byte 0, bit 1) the device has completed its internal write cycle.

in the STATUS register. This instruction will return an FFh value when the

device is still busy completing the write cycle or a 00h

6.1.4 READY/BUSY STATUS LATCH value if the device is no longer in a write cycle.

The Ready/Busy Status Latch (RDY/BSY) is used to Refer to Section 8.3 “Polling Routine” for a

indicate whether the device is currently active in a description on implementing a polling routine.

nonvolatile write sequence. This bit is read-only and Continuous reading of the WRBP state is supported

automatically updated by the device. This bit is and the value output by the device will be updated

provided in bit 0 of both STATUS register bytes. every eight bits.

A logic ‘1’ bit indicates that the device is currently busy

performing a nonvolatile write sequence. During this

time, only the Read STATUS Register (RDSR) and the

Write Ready/Busy Poll (WRBP) instructions will be

executed by the device.

FIGURE 6-1: WRITE READY/BUSY POLL (WRBP) SEQUENCE

CS

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

SCK

WRBP Opcode (08h)

SI 0 0 0 0 1 0 0 0

MSb

FFh or 00h Data Out

High-Impedance

SO D7 D6 D5 D4 D3 D2 D1 D0

MSb

6.1.5 WRITE PROTECTION MODE BIT The WPM bit in the STATUS register can only be

modified using the WRSR instruction as described in

The 25CSM04 write protection behavior is controlled

Section 6.3 “Write STATUS Register (WRSR)”.

by the nonvolatile Write Protection Mode (WPM) bit in

the STATUS register. This bit is located in bit 7, byte 1 Write protection mode can be made permanent by

of the STATUS register. A logic ‘0’ indicates the device executing the FRZR instruction. This can be done in

is in Legacy Write Protection mode whereas a logic ‘1’ both Legacy Write Protection mode and Enhanced

indicates the device is in Enhanced Write Protection Write Protection mode. Refer to Section 4.5.4 “Freeze

mode. Memory Protection Configuration (FRZR)” for

additional information.

The write protection modes control how the contents of

the EEPROM and Security register as well as the

various nonvolatile registers in the device can be

inhibited from writing. An overview of the two protection

modes can be found in Section 4.5 “Write

Protection”. Details on which nonvolatile registers are

protected, in conjunction with the WP pin, can be found

in Section 6.1.1 “Write-Protect Enable Bit”.

DS20005817D-page 22 2019-2022 Microchip Technology Inc. and its subsidiares

25CSM04

6.1.6 ERROR CORRECTION STATE 6.1.8 PARTITION WRITE ENABLE LATCH

LATCH In addition to the WEL bit, enabling and disabling

The Error Correction State (ECS) bit is located in byte writing to the Memory Partition register is done by

1, bit 6 of the STATUS register. This bit indicates issuing the Set Memory Partition Write Enable Latch

whether the on-chip Error Correction Code (ECC) logic (PRWE) as shown in Figure 10-3 and the Reset Memory

scheme was invoked during the previous read Partition Write Enable Latch (PRWD) as shown in

sequence. For more information related to ECC, refer Figure 10-4. These functions change the status of the

to Section 8.2 “Error Correction Code (ECC) PREL bit (byte 1, bit 4). in the STATUS register.

Architecture”.

The ECS bit will be set to logic ‘0’ unless the previously

Note: The WEL bit must first be set before

executed read sequence required the use of the ECC

issuing the PRWE instruction, otherwise it

logic scheme. When this occurs the ECS bit will set to

is ignored.

logic ‘1’.

The ECS bit will continue to read a logic ‘1’ until another 6.1.9 PARTITION ADDRESS BOUNDARY

read sequence occurs where the use of the ECC logic PROTECTION BIT

scheme was not required, a Power-on Reset (POR)

event occurs, or a Software Device Reset (SRST) The Partition Address Boundary Protection (PABP) bit

instruction is sent to the 25CSM04. is located in byte 1, bit 3 of the STATUS register. This

bit can be read through an RDSR instruction but can

6.1.7 FREEZE MEMORY PROTECTION only be set or cleared through a Protect Partition

CONFIGURATION BIT Address Boundary sequence (see Section 10.1.3

“Protecting the Partition Endpoint Addresses”).

The Freeze Memory Protection Configuration (FMPC) When programmed to a Logic ‘1’, the address range

bit resides in byte 1, bit 5 of the STATUS register. This bits in the Memory Partition registers are read-only and

bit is nonvolatile and One-Time-Programmable (OTP) cannot be modified but the behavior bits can still be

with a factory default value of a logic ‘0’. modified.

This bit can only be set to a logic ‘1’ as a result of the If the Freeze Memory Protection Configuration bit has

Freeze Memory Protection Configuration (FRZR) been programmed to a logic ‘1’, the address range and

instruction (Section 4.5.4 “Freeze Memory behavior bits are permanently read-only and cannot be

Protection Configuration (FRZR)”). This bit cannot modified regardless of the state of the PABP bit.

be modified with a Write STATUS Register (WRSR)

instruction. Once this bit has been permanently set to a

logic ‘1’, the memory configuration cannot be changed.

2019-2022 Microchip Technology Inc. and its subsidiares DS20005817D-page 23

25CSM04

6.2 Read STATUS Register (RDSR) The STATUS register can be continuously read for data

by continuing to read beyond the first 16-bit value

The Read STATUS Register (RDSR) instruction returned. The 25CSM04 will update the value of the

provides access to the contents of the STATUS volatile bits (RDY/BSY, WEL and PREL) in the STATUS

register. The STATUS register is read by asserting the register at byte boundaries, thereby allowing new

CS pin followed by sending in a 05h opcode. The STATUS register volatile bit values to be read without

device will return the 16-bit STATUS register value on having to issue a new RDSR instruction.

the SO pin.

A new RDSR instruction needs to be initiated in order for

the nonvolatile bits (WPEN, BP0, BP1 and WPM) in the

STATUS register to be updated.

FIGURE 6-2: READ STATUS REGISTER (RDSR) SEQUENCE

CS

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

SCK

RDSR Opcode (05h)

SI 0 0 0 0 0 1 0 1

STATUS Register Byte 0 STATUS Register Byte 1

High-Impedance

SO D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

DS20005817D-page 24 2019-2022 Microchip Technology Inc. and its subsidiares

25CSM04

6.3 Write STATUS Register (WRSR) When writing to the STATUS register, byte 0 must

always be written. Byte 1 can optionally be written to

The Write STATUS Register (WRSR) instruction enables utilize Enhanced Write Protection mode.

the SPI host to change selected bits of the STATUS

register. Before a WRSR sequence can be initiated, a

WREN instruction must be executed to set the WEL bit Note: If the CS pin is deasserted at somewhere

to logic ‘1’. Upon completion of a WREN instruction, a other than the end of an 8-bit byte

WRSR sequence can be executed. boundary, the sequence will be aborted

and no write cycle will take place.

The WRSR instruction will only modify:

• Byte 0: bit 7, bit 3 and bit 2 The 25CSM04 will not respond to instructions other

than a RDSR or a WRBP after a WRSR sequence until

• Byte 1: bit 7

the self-timed internal write cycle has completed. When

These modifiable bits are the Write-Protect Enable the write cycle has completed, the WEL bit in the

(WPEN) bit, the Block Protect (BP1, BP0) bits and the STATUS register is reset to a logic ‘0’.

Write Protection Mode (WPM) bit.

These four bits are nonvolatile cells that have the same

properties and functions as regular EEPROM cells.

Their values are retained while power is removed from

the device. While FMPC (byte 1, bit 5) and PABP

(byte 1, bit 3) of the STATUS register are also

nonvolatile bits, they are modified through dedicated

instructions. Refer to Section 6.1.7 “Freeze Memory

Protection Configuration Bit” and Section 10.1.3

“Protecting the Partition Endpoint Addresses” for

more details about these requirements.

FIGURE 6-3: WRITE STATUS REGISTER (WRSR) SEQUENCE

CS

TWC(1)

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

SCK

WRSR Opcode STATUS Register Byte STATUS Register Byte

SI 0 0 0 0 0 0 0 1 D7 X X X D3 D2 X X D7 X X X X X X X

MSb MSb MSb

Optional

High-Impedance

SO

Note 1: This sequence initiates a self-timed internal write cycle on the rising edge of CS after a valid sequence.

2019-2022 Microchip Technology Inc. and its subsidiares DS20005817D-page 25

25CSM04

7.0 READ SEQUENCES Upon completion of the 24-bit address, any data on the

SI line will be ignored. The data (D7–D0) at the

specified address is then shifted out onto the SO line. If

7.1 Reading from the EEPROM

only one byte is to be read, the CS line should be driven

Reading the EEPROM contents can be done whenever high after the data are clocked out.

the device is not in an internal write cycle, as indicated The read sequence can be continued since the byte

by the Ready/Busy bit of the STATUS register. To read address is automatically incremented and data will

the EEPROM, first the CS line is pulled low to select the continue to be shifted out. When the highest address is

device and the READ (03h) instruction is transmitted via reached, the address counter will “rollover” to the

the SI line followed by the 24-bit address to be read. lowest address (000000h) allowing the entire memory

Address bits A23 through A19 are “don’t care” bits to be read in one continuous read cycle regardless of

because they do not fall within the addressable the starting address.

memory range.

The read sequence can be terminated at any point of

the sequence (drive CS high).

FIGURE 7-1: READ EEPROM (READ) SEQUENCE

CS

0 1 2 3 4 5 6 7 8 9 10 11 12 29 30 31 32 33 34 35 36 37 38 39 40 41

SCK

READ Opcode (03h) Address Bits A23-A0

SI 0 0 0 0 0 0 1 1 X X X X X A A A A

MSb MSb

Data Byte 1

High-Impedance

SO D7 D6 D5 D4 D3 D2 D1 D0 D7 D6

MSb MSb

DS20005817D-page 26 2019-2022 Microchip Technology Inc. and its subsidiares

25CSM04

8.0 WRITE SEQUENCES Address bits A23 through A19 are “don’t care” bits

because they do not fall within the addressable

In order to program the EEPROM in the 25CSM04, the memory range.

device must be write-enabled via the Write Enable

Programming will start after the CS pin is brought high.

instruction (WREN). If the device is not write-enabled,

The low-to-high transition of the CS pin must occur

the device will ignore the WRITE instruction and will

during the SCK low time (mode 0) and SCK high time

return to the Standby state when CS is brought high.

(mode 3) immediately after clocking in the D0 (LSB)

The address of the memory location(s) to be

data bit.

programmed must be outside the protected address

range(s) selected by the Block Write Protection level or

the contents of the various Memory Partition registers. Note: If the CS pin is deasserted at somewhere

During an internal write cycle, all instructions will be other than the end of an 8-bit byte

ignored except the RDSR and the WRBP instructions. boundary, the sequence will be aborted

and no write cycle will take place.

8.1 Write Instruction Sequences The 25CSM04 is automatically returned to the Write

Disable state (STATUS register bit WEL = 0) at the

8.1.1 BYTE WRITE

completion of a write cycle.

Once a WREN instruction has been completed, a byte

write sequence can be performed as shown in

Figure 8-1. After the CS line is pulled low to select the

device, the WRITE (02h) instruction is transmitted via

the SI line followed by the 24-bit address and the data

(D7-D0) to be programmed.

FIGURE 8-1: BYTE WRITE SEQUENCE

CS

TWC(1)

0 1 2 3 4 5 6 7 8 9 10 11 12 29 30 31 32 33 34 35 36 37 38 39

SCK

WRITE Opcode (02h) Address Bits A23-A0 Data In

SI 0 0 0 0 0 0 1 0 X X X X X A A A A A D7 D6 D5 D4 D3 D2 D1 D0

MSb MSb MSb

High-Impedance

SO

Note 1: This sequence initiates a self-timed internal write cycle on the rising edge of CS after a valid sequence.

8.1.2 PAGE WRITE Upon completion of a write cycle, the 25CSM04

automatically returns to the Write Disable state

A page write sequence is the same as a byte write,

(STATUS register bit WEL = 0).

however allowing up to 256 bytes to be written in the

same write cycle, provided that all bytes are in the Note: If the CS pin is deasserted at somewhere

same page of the memory array (where addresses A18 other than the end of an 8-bit byte

through A8 are the same). Partial page writes of less boundary, the sequence will be aborted

than 256 bytes are allowed. After each byte of data is and no write cycle will take place.

received, the eight lowest order address bits are

internally incremented by one and the remaining

address bits will remain constant.

If more bytes of data are transmitted than what will fit to

the end of that memory page, the address counter will

“rollover” to the beginning of the same page and only

the last 256 bytes of data received will be written to the

device.

2019-2022 Microchip Technology Inc. and its subsidiares DS20005817D-page 27

25CSM04

FIGURE 8-2: PAGE WRITE SEQUENCE

CS

TWC(1)

0 1 2 3 4 5 6 7 8 9 29 30 31 32 33 34 35 36 37 38 39

SCK

WRITE Opcode (02h) Address Bits A23-A0 Data In Byte 1 Data In Byte n (256 max.)

SI 0 0 0 0 0 0 1 0 X X X A A A D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

MSb MSb MSb MSb

High-Impedance

SO

Note 1: This sequence initiates a self-timed internal write cycle on the rising edge of CS after a valid sequence.

8.2 Error Correction Code (ECC) The polling routine is repeatedly sending Read

Architecture STATUS Register (RDSR) or Write Ready/Busy Poll

(WRBP) instructions to determine if the device has

The 25CSM04 incorporates a built-in Error Correction completed its self-timed internal write cycle (see

Code (ECC) logic scheme. The EEPROM array is Figure 8-3). If the RDY/BSY bit = 1 from RDSR or FFh

internally organized as a group of four connected bytes from WRBP the write cycle is still in progress.

plus an additional six ECC parity bits of EEPROM. If RDY/BSY bit = 0 from RDSR or 00h from WRBP this

These 38 bits are referred to as the internal physical indicates the write cycle has ended. If the device is still

data word. During a read sequence, the ECC logic in a busy state, repeated RDSR or WRBP instructions