Professional Documents

Culture Documents

2015 Macbook Air A1466 ALL - SYS - PWRGD

2015 Macbook Air A1466 ALL - SYS - PWRGD

Uploaded by

Vivek VarshneyOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

2015 Macbook Air A1466 ALL - SYS - PWRGD

2015 Macbook Air A1466 ALL - SYS - PWRGD

Uploaded by

Vivek VarshneyCopyright:

Available Formats

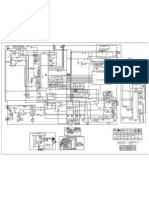

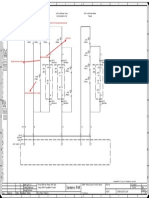

8 7 6 5 4 3 2 1

S5 Enables

S3 Enables

PLACE_NEAR=U7501.21:7mm 59 37 36 29 18 13 IN PM_SLP_S4_L

54 38 37 OUT SMC_PM_G2_EN R8140 34 29 28 18 17 16 15 13 11 8 PP3V3_S5 1 1 1

59

54 38 37 SMC_PM_G2_EN 1

100

2 59 54 S5_PWR_EN S5_PWR_EN 54 59

74 64 62 60 59 58 57 42

NOSTUFF

Standby Enables R8111

20K

R8116

0

R8112

0

59 IN OUT

MAKE_BASE=TRUE MAKE_BASE=TRUE 5% 5% 5%

5% C8170 1

1/20W 1/20W 1/20W

1/20W NOSTUFF 0.1UF MF MF MF

MF 201 0201 0201

201 1

C8142 10%

6.3V

2

PLACE_NEAR=U7400.16:6mm

2

PLACE_NEAR=U7820.2:6mm

2

PLACE_NEAR=U8010.D2:6mm

2

0.47UF CERM-X5R

10% 0201 59 58 P3V3S3_EN P3V3S3_EN

6.3V OUT 58 59

2 CERM-X5R BYPASS=U8170.6:2.3mm NOSTUFF MAKE_BASE=TRUE

402

6 U8170 59 57 P1V8S3_EN P1V8S3_EN 57 59

D PLACE_NEAR=U7501.21:7mm

37 13 IN PM_SLP_S5_L 2

74LVC1G32

SOT891

59 53

MAKE_BASE=TRUE

DDRREG_EN DDRREG_EN

OUT

OUT 53 59

D

4 S4_PWR_EN S4_PWR_EN OUT 18 28 58 59 MAKE_BASE=TRUE

MAKE_BASE=TRUE

SMC_S4_WAKESRC_EN 1 NO STUFF NO STUFF

S5 Power Good 38 37 IN NC S4_PWR_EN OUT 18 28 58 59

1

C8111 1

C8116 1

C8112

5 3

61 59 50 49

36 35 30 17 PP3V42_G3H 0.1UF 0.47UF 0.47UF

46 40 38 37 20% 10% 10%

65 64 62 NC 10V 6.3V 6.3V

PLACE_NEAR=U7501.20:7mm

R8115 2

CERM

402

2

CERM-X5R 2

CERM-X5R

1 402 402

R8141 0

1 2 USB_PWR:STBY USB_PWR:S3 PLACE_NEAR=U7400.16:6mm PLACE_NEAR=U7820.2:6mm PLACE_NEAR=U8010.D2:6mm

100K 1 1

5%

5%

1/20W S5_PWRGD-->SMC 1/20W R8114 R8117

MF MF 100 100

201 SMC-->PM_DSW_PWRGD 0201 5% 5%

2

1/20W 1/20W Mobile System Power State Table

USB_PWR:STBY MF MF

59 54 37 S5_PWRGD S5_PWRGD OUT 37 54 59 201 201

2 2

MAKE_BASE=TRUE

R8177 PLACE_NEAR=U4600.4:6mm PLACE_NEAR=U4600.4:6mm

State SMC_ADAPTER_EN SMC_PM_G2_ENABLE SMC_S4_WAKESRC_EN PM_SUS_EN PM_SLP_S5_L PM_SLP_S4_L PM_SLP_S3_L

0

59 58 28 18 S4_PWR_EN 1 2 65 61 59 35 USB_PWR_EN USB_PWR_EN OUT 35 59 61 65 Run (S0) X 1 1 1 1 1 1

MAKE_BASE=TRUE

5%

Sleep (S3AC) 1 1 1 1 1 1 0

NO STUFF

SSD Enable 1/20W

MF

0201 1

C8114 Sleep (S3) 0 1 1 1 1 1 0

P5VS4RS3_EN_RC 0.47UF Deep Sleep (S4AC) 1 1 1 0 0 0 0

USB_PWR:S3

64 59 58 30 15 IN SSD_PWR_EN SSD_PWR_EN OUT 15 30 58 59 64 PLACE_NEAR=U7501.4:15mm 10%

6.3V Deep Sleep (S4) 0 1 1 0 0 0 0

MAKE_BASE=TRUE

R8179 A NO STUFF 1

2 CERM-X5R

0 D8175 R8175 402 Deep Sleep (S5AC) 1 1 0 0 0 0 0

59 37 36 29 18 13 PM_SLP_S4_L 1 2 0201 0 PLACE_NEAR=U4600.4:6mm

Deep Sleep (S5) 0 1 0 0 0 0 0

5%

5% RB521ES-30 1/20W Battery Off (G3HotAC) toggle 3Hz 0 0 0 0 0 0

1/20W K MF

MF NO STUFF 2

0201 Battery Off (G3Hot) 1 0 0 0 0 0 0

0201

R8176 PLACE_NEAR=U7501.4:15mm

240

P5VS4RS3_EN_D 1 2

5V needs to be held up 5% P5VS4RS3_EN OUT 54

1/20W

so 1.05V can fall after 1.5V MF NO STUFF

201

PLACE_NEAR=U7501.4:15mm 1

C8175

C 2

2.2UF

10%

6.3V 34 29 28 18 17 16 15 13 11 8

74 64 62 60 59 58 57 42

PP3V3_S5 C

X5R

402

PLACE_NEAR=U7501.4:15mm

BYPASS=U8180.6:3mm

1

C8180

0.1UF

10%

6.3V

R8178

2 CERM-X5R

0201

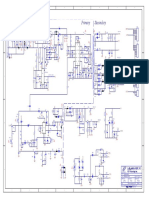

S0 Enables

100 5

MC74VHC1G08

S0 Rail PGOOD (BJT Version) 37 18 17 13 IN PM_SLP_S3_L 1 2 59 PM_SLP_S3_R_L 1

SC70-HF

5% 4 59 57 28 PM_SLP_S3_BUF_L PM_SLP_S3_BUF_L 28 57 59

1/20W

2

U8180 MAKE_BASE=TRUE

OUT

PP5V_S0 16 17 32 45 51 52 56 58 59 61 MF NOSTUFF A NO STUFF

PM_SLP_S3_BUF_L OUT 28 57 59

62 64 28 18 17 16 15 13 11 8 PP3V3_S5 201 1

R8185 1

R8184 1

R8186 1

R8187

1

74 64 62 60 59 58 57 42 34 29

3

1

R8180 D8185 0 330 20K 0

R8151 1 330K

0201

54.9K R8156 5% RB521ES-30 5%

1/20W

5%

1/20W

5%

1/20W

5%

1/20W

1% 150K 1/20W K PLACE_NEAR=U7600.16:6mm

MF MF MF MF

1/20W 1% MF 0201 201 201 0201

MF

R8153 1/20W

2

201 NO STUFF 2 2 D8184 2 2

2

201 MF

R8138

PLACE_NEAR=U7600.16:6mm PLACE_NEAR=U8030.2:6mm 0201 PLACE_NEAR=U8030.2:6mm PLACE_NEAR=U8080.2:6mm

1K 201 2

K A

VMON_5V_DIV 1 2 ALL_SYS_PWRGD 16 17 37 59 820 P3V3S0_EN_D 59 58 P5VS0_EN P5VS0_EN OUT 58 59

5.0V Divider: 1.07V S0PGD_C P1V05_EN_D 1 2 MAKE_BASE=TRUE

1

5%

1/20W

1.5V Codec Enable 5% 59 58 P3V3S0_EN P3V3S0_EN

R8152 C8159 1 MF PLACE_NEAR=U8040.2:C7mm 1/20W

RB521ES-30

MAKE_BASE=TRUE

OUT 58 59

15K 201 MF

6

PLACE_NEAR=U8030.2:6mm

1UF 201

1%

1/20W

10%

CRITICAL R8145 PLACE_NEAR=U7600.16:6mm

10V 100K

MF X5R 2 9ms RC delay

2

201 402 Q8150 65 61 13 IN AUD_PWR_EN 1 2 P1V5S0SW_AUDIO_EN OUT 58 59 55 P1V05S0_EN P1V05S0_EN OUT 55 59

Q1 5%

MAKE_BASE=TRUE

VMON_Q2_BASE 5 ASMCC0179 1/20W NO STUFF NO STUFF

Q2

DFN2015H4-8 D8146 MF

R8146

PP3V3_S0

64 65 74

38 39 40 41 42 8 0201 201

1K

1

C8185 1

C8186 1

C8187

8 11 12 13 15

17 18 26 30 36

43 44 45 56 59 61 62

R8154 NC K A P1V5CODEC_EN_D 1 2 0.22UF 0.1UF 0.68UF

1K 10% 20% 10%

1 1 2 VMON_Q3_BASE 7 10V 10V 6.3V

R8158 Q3 376S0854 5% 2 2 2

RB521ES-30 1/20W 1

C8146 CERM

402

CERM

402

CERM

402

15K 5%

2

MF

0.1UF

1% 1/20W PLACE_NEAR=U8040.2:C7mm 201 PLACE_NEAR=U7600.16:6mm

NC PLACE_NEAR=U8030.2:6mm PLACE_NEAR=U8080.2:6mm

B 2

1/20W

MF

201

MF

201

1

Q4

2

10%

25V

X5R

402

B

VMON_3V3_DIV

3.3V Divider: 1.07V

PLACE_NEAR=U8040.C2:7mm

3.3V SUS Detect

1

R8159 34 29 28 18 17 16 15 13 11 8 PP3V3_S5

3

7.15K 74 64 62 60 59 58 57 42

1%

1/20W S0PGD_BJT_GND_R

MF BYPASS=U8130.6:2.3mm

No stuff C8131, 12ms PP3V3_SUS

2

201

R8157 1 Min delay time C8130 1

8 11 14 18 46 57 58 59 62 64

CHGR VFRQ Generation

R8155 100 U8130 Sense input 0.1UF 1

1K 5% threhold is 3.07V 10% R8133

PP1V5_S0 1 2 VMON_Q4_BASE 6.3V 100K

64 62 59 58 57 8 1/20W CERM-X5R 2

MF 59 57 28 PM_SLP_S3_BUF_L 0201 5% 50 49 46 40 38 37 36 35 30 17 PP3V42_G3H

Vbe 0.7V max @ 2mA CRITICAL 65 64 62 61 59

1

5% 201 1/20W

1/20W 2 MF

MF

201

Vce(sat) 0.1V max @ 1mA 1 VDD 2 201 R8131 1

Q1 Vth 0.7~1V @Id 250uA R8167 330K

10K PP3V3_SUS 2 SENSE RESET* 6 PM_RSMRST_L

5%

64 62 59 58 57 46 18 14 11 8

U8130 OUT 13 64 5%

1/20W

1/20W TPS3808G33 MF

MF QFN VFRQ Low: Fix Frequency 201

2 201

SUS_PGOOD_CT 3 CT MR* 4 TP_SUS_PGOOD_MR_L 2

THRM VFRQ High: Variable Frequency CHGR_VFRQ OUT 50

Thresholds: NO STUFF GND

VDD: 2.734V-3.010V

S0 Rail PGOOD Circuitry R8166 1

C8131

PAD

Q8131 D 3

7

100

V2MON: 2.815V-3.099V (ISL version used for development) IN P1V8S3_PGOOD 1 2 1000PF

10% DMN32D2LFB4

16V DFN1006H4-3

V3MON: 0.572V-0.630V 5% 2 X7R-1 SYM_VER_2

1/20W

V4MON: 0.572V-0.630V 74 65 64 62 61

R8165 MF 0201

36 30 26 18 17 15 13 12 11 8 PP3V3_S0 100 201

59 56 45 44 43 42 41 40 39 38 54 IN P5VS4RS3_PGOOD 1 2

55 51 42 38 17 16 15 11 8 6 PP1V05_S0 S0PGOOD_ISL 1 G S

64 62 58 5% 2

PP1V5_S0

C8160 1 1/20W

MF

59 PM_SLP_S3_R_L

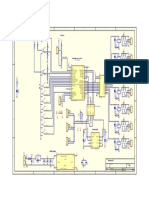

64 62 59 58 57 8

0.1UF 201

61

52

59

51

10% R8164

PP5V_S0 6.3V 100

2

17

45

16

32 S0PGOOD_ISL S0PGOOD_ISL S0PGOOD_ISL

CERM-X5R

55 IN P1V05S0_PGOOD 1 2 SUS Enables

2

58 56 0201

64 62 1 1 1

A 5V Divider:

R8160

6.04K

1%

R8170

15K

1%

R8172

6.04K

1%

VDD

S0PGOOD_ISL

U8160

R8168

100

5%

1/20W

MF

201

59 42 13 IN PM_SLP_SUS_L

MAKE_BASE=TRUE

PM_SLP_SUS_L OUT 13 42 59

SYNC_MASTER=J43_MLB SYNC_DATE=09/16/2012 A

DDRREG_PGOOD 1 2 1 PAGE TITLE

3.19V @ 4.5Vmin

1/20W 1/20W 1/20W

ISL88042IRTEZ 53 IN R8190

2

MF

201

2

MF

201

2

MF

201 TDFN

(IPU)

353S2310

S0PGOOD_ISL

5%

1/20W

0

5%

Power Control

P5V_DIV_VMON 3 V2MON MR* 1

NC MF 1/20W DRAWING NUMBER SIZE

201

1.5V Divider:

P1V5_DIV_VMON 5 V3MON

CRITICAL

R8162 MF

0201 <SCH_NUM> D

0.718V @ 1.45Vmin

P1V05_DIV_VMON 6 V4MON RST* 8 ALL_SYS_PWRGD_R 1

330

2 ALL_SYS_PWRGD 16 17 37 59 59 58

2

P3V3SUS_EN P3V3SUS_EN 58 59

Apple Inc. REVISION

OUT OUT

S0PGOOD_ISL S0PGOOD_ISL S0PGOOD_ISL MAKE_BASE=TRUE R

1 1 1 GND THRM_PAD 5%

1/20W

<E4LABEL>

1.05V Divider: R8161 R8171 R8173 NO STUFF

MF NOTICE OF PROPRIETARY PROPERTY: BRANCH

4

0.723V @ 1.02Vmin 15K 15K 15K 201 1

C8190

1% 1% 1%

0.1UF THE INFORMATION CONTAINED HEREIN IS THE <BRANCH>

1/20W 1/20W 1/20W

10%

PROPRIETARY PROPERTY OF APPLE INC.

MF MF MF 25V THE POSESSOR AGREES TO THE FOLLOWING: PAGE

201 201 201 2

2 2 2 X5R I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE 81 OF 121

402

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART SHEET

IV ALL RIGHTS RESERVED 59 OF 76

8 7 6 5 4 3 2 1

You might also like

- POPM (6.0) - SAFe® Product Owner-Product ManagerDocument2 pagesPOPM (6.0) - SAFe® Product Owner-Product ManagerGiang LuongNo ratings yet

- Google Analytics Certification Questions AnswersDocument83 pagesGoogle Analytics Certification Questions AnswersPratik GandhiNo ratings yet

- Air Instructor Manual March 14Document128 pagesAir Instructor Manual March 14jamesbeaudoin100% (1)

- The Toyota Kata Practice Guide: Practicing Scientific Thinking Skills for Superior Results in 20 Minutes a DayFrom EverandThe Toyota Kata Practice Guide: Practicing Scientific Thinking Skills for Superior Results in 20 Minutes a DayRating: 4.5 out of 5 stars4.5/5 (7)

- Apple MacBook Air 13 - A1466 - J13 - 820-3209 3Document1 pageApple MacBook Air 13 - A1466 - J13 - 820-3209 3EduinMaracuchoFernandezChaparro0% (1)

- Datasheet IT8987E PDFDocument1 pageDatasheet IT8987E PDFAnalia Madeled Tovar JimenezNo ratings yet

- Datasheet IT8987E PDFDocument1 pageDatasheet IT8987E PDFAnalia Madeled Tovar JimenezNo ratings yet

- Datasheet IT8987E PDFDocument1 pageDatasheet IT8987E PDFd4l170100% (1)

- SG 247777Document862 pagesSG 247777ieatbeesNo ratings yet

- PO178 - 20 10t X 20m Span + 5.2m Cantilever Gantry Crane - Part16Document1 pagePO178 - 20 10t X 20m Span + 5.2m Cantilever Gantry Crane - Part16ahmed saadNo ratings yet

- PO178 - 20 10t X 20m Span + 5.2m Cantilever Gantry Crane - Part16Document1 pagePO178 - 20 10t X 20m Span + 5.2m Cantilever Gantry Crane - Part16ahmed saadNo ratings yet

- Apple MacBook Air - A1465 - J11 - 820-3208 3Document1 pageApple MacBook Air - A1465 - J11 - 820-3208 3EduinMaracuchoFernandezChaparroNo ratings yet

- 1TB02011 011C44 Amp FF R1 SDW Ar 10001Document1 page1TB02011 011C44 Amp FF R1 SDW Ar 10001Sher DilNo ratings yet

- Rear Cab Wiring Dash Wiring Dash Wiring (Interior View) : Electrical System 793F Off-Highway TruckDocument8 pagesRear Cab Wiring Dash Wiring Dash Wiring (Interior View) : Electrical System 793F Off-Highway TruckFelipeNicolasSilvaNo ratings yet

- 797 FDocument10 pages797 FRonny Leon NuñezNo ratings yet

- Engine Controls - IMA Circuit (Powertrain Management) - ALLDATA RepairDocument3 pagesEngine Controls - IMA Circuit (Powertrain Management) - ALLDATA RepairRigoberto Buendía menaNo ratings yet

- Angelo Valse PDFDocument6 pagesAngelo Valse PDFJoseIaconaNo ratings yet

- CIRCUITSDocument17 pagesCIRCUITSSteven WassaakaNo ratings yet

- Uenr7758uenr7758-03 Sis PDFDocument10 pagesUenr7758uenr7758-03 Sis PDFDarwin Herrera SalinasNo ratings yet

- Cortes Raros y Otras CosasDocument3 pagesCortes Raros y Otras Cosasmzarate75No ratings yet

- 793C Off-Highway Truck Hydraulic SchematicDocument2 pages793C Off-Highway Truck Hydraulic SchematicNicole SmithNo ratings yet

- Usb Interface: KeyboardDocument18 pagesUsb Interface: KeyboardRedNo ratings yet

- 17MB70 2Document16 pages17MB70 2Leandro RossiNo ratings yet

- Admiral TG-142, 203, 2100Document1 pageAdmiral TG-142, 203, 2100victorino2009No ratings yet

- WL950G BAAHidDocument2 pagesWL950G BAAHidGrupoSisolMaquinariasNo ratings yet

- Datasheet It8987e PDF FreeDocument1 pageDatasheet It8987e PDF Freemauri kñazovicNo ratings yet

- Datasheet It8987e PDF FreeDocument1 pageDatasheet It8987e PDF Freejhonnattan moreno casilimasNo ratings yet

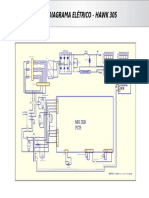

- Diagrama Elétrico - Hawk 305Document1 pageDiagrama Elétrico - Hawk 305LUMAQ SOLDANo ratings yet

- PIC EASY ShematicDocument1 pagePIC EASY Shematicvishnum277No ratings yet

- PR - CL - 0228 - DD - 0550 - Rev01 - Overall Single Line DiagramDocument1 pagePR - CL - 0228 - DD - 0550 - Rev01 - Overall Single Line Diagramsergio vogadpNo ratings yet

- Fa Rsag7.820.1947Document3 pagesFa Rsag7.820.1947ies837No ratings yet

- Beko Chassis KT KU Main Code VKT190RDocument18 pagesBeko Chassis KT KU Main Code VKT190RtaviNo ratings yet

- SCX-6345N XET SM EN 20070130090204078 09-Connection Diagram PDFDocument5 pagesSCX-6345N XET SM EN 20070130090204078 09-Connection Diagram PDFSoraphong NaknoppakoonNo ratings yet

- Mặt Bằng Bố Trí Thiết Bị Điện Thông Minh Tầng 4Document1 pageMặt Bằng Bố Trí Thiết Bị Điện Thông Minh Tầng 4SmartHome AlphaHomeNo ratings yet

- Control PanelDocument7 pagesControl PanelTahirNo ratings yet

- Quince Primaveras IntroDocument1 pageQuince Primaveras IntroLucas AgustínNo ratings yet

- Usb Interface: BluerayDocument16 pagesUsb Interface: BluerayRedNo ratings yet

- Res RP Wdo WP WDI VDDDocument2 pagesRes RP Wdo WP WDI VDDspamail73887No ratings yet

- fsp488-4f01 Power Supply SCHDocument1 pagefsp488-4f01 Power Supply SCHCarlos Junior PereiraNo ratings yet

- NPCE285Document1 pageNPCE285atefdinNo ratings yet

- E - Manuals - Controller Wiring Diagram - Controller Wiring Diagram - DWG Model (1) - 2Document1 pageE - Manuals - Controller Wiring Diagram - Controller Wiring Diagram - DWG Model (1) - 2abmtechnosolution2018No ratings yet

- Manual-Deepers 12Document1 pageManual-Deepers 12Beny StephenNo ratings yet

- Diy Inverter PSW - 2022-01-07Document1 pageDiy Inverter PSW - 2022-01-07Kareem Solar EngineeringNo ratings yet

- LG C3380 SchematicsDocument8 pagesLG C3380 Schematicsberafta zakariaNo ratings yet

- Cool CalypsoDocument1 pageCool Calypsotrantrungheo155No ratings yet

- Propth-E Rev04 - Esquema 3000Document1 pagePropth-E Rev04 - Esquema 3000shekinah oficialNo ratings yet

- CDM 570 (SC10901 Rev. C)Document13 pagesCDM 570 (SC10901 Rev. C)Gomia DetuttiNo ratings yet

- The Black Dahlia Murder - A Grave Robbers WorkDocument1 pageThe Black Dahlia Murder - A Grave Robbers WorkVgh GoghNo ratings yet

- Sacred Reich S Surf Nicaragua-Guitar 1Document5 pagesSacred Reich S Surf Nicaragua-Guitar 1Miguel Angel Herrera MartinezNo ratings yet

- Switches: Manual AutoDocument1 pageSwitches: Manual AutoMario Alfaro CanoNo ratings yet

- Siemens PAK: Change Contacts Q12 To Q3 and Add Terminals DetailsDocument1 pageSiemens PAK: Change Contacts Q12 To Q3 and Add Terminals DetailsMehroz KhanNo ratings yet

- Samyung Enc Co.,Ltd.: Inteface LCDDocument1 pageSamyung Enc Co.,Ltd.: Inteface LCDjasonelectronicsphilNo ratings yet

- LLDM311B7-5 (L3110) Í Õè¡ Ý - V1.0Document36 pagesLLDM311B7-5 (L3110) Í Õè¡ Ý - V1.0Garik StepanyanNo ratings yet

- The Intel Microprocessors 8086 - 8088, 80... Itecture, Programming, and InterfacingDocument944 pagesThe Intel Microprocessors 8086 - 8088, 80... Itecture, Programming, and InterfacingRenato RamirezNo ratings yet

- Nandha Kumar L Press Tool 16/05/2022: GP GB S2 S2 S2 S2Document6 pagesNandha Kumar L Press Tool 16/05/2022: GP GB S2 S2 S2 S2nandha kumar.LNo ratings yet

- 50A 7 8 9 2 or 7 8 9 1 331 55 56 59 Or56aor60 55 60 59 or 57A or 57Document1 page50A 7 8 9 2 or 7 8 9 1 331 55 56 59 Or56aor60 55 60 59 or 57A or 57ANGEL MURILLONo ratings yet

- Ts2 P 7 F 26 - Bpek: Specifications: MechanicalDocument2 pagesTs2 P 7 F 26 - Bpek: Specifications: Mechanicalsebinjose87No ratings yet

- Transcript Maqueta Guitar 2Document8 pagesTranscript Maqueta Guitar 2Pepe CuenquillaNo ratings yet

- Alto Saxophone 2: E. Bozza Arr. Philippe TrovãoDocument1 pageAlto Saxophone 2: E. Bozza Arr. Philippe TrovãoPhilippe B. TrovãoNo ratings yet

- Sony VGN-CR MBX - 177 - Quanta Gd1 - TouchpadDocument1 pageSony VGN-CR MBX - 177 - Quanta Gd1 - TouchpadNicolás TorresNo ratings yet

- Fill Your Glass With Gold-When It's Half-Full or Even Completely ShatteredFrom EverandFill Your Glass With Gold-When It's Half-Full or Even Completely ShatteredNo ratings yet

- Lenovo Ziji2 Ella - Sovp - MB La-A811p r10 - 0321Document54 pagesLenovo Ziji2 Ella - Sovp - MB La-A811p r10 - 0321Vivek VarshneyNo ratings yet

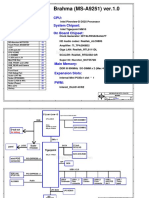

- INTEL Braswell Platform: Cover Page Rosa - Lily SFF Cover Page Rosa - Lily SFF Cover PageDocument105 pagesINTEL Braswell Platform: Cover Page Rosa - Lily SFF Cover Page Rosa - Lily SFF Cover PageVivek VarshneyNo ratings yet

- Ms-A9251 Rev1.0Document34 pagesMs-A9251 Rev1.0Vivek VarshneyNo ratings yet

- LA-5573P Discrete SchematicsDocument70 pagesLA-5573P Discrete SchematicsVivek VarshneyNo ratings yet

- Trends and Challenges in Soc Design v3Document32 pagesTrends and Challenges in Soc Design v3Nitheesh Kumar100% (1)

- No Grass S18Document37 pagesNo Grass S18Bahrudin UdinNo ratings yet

- Sequence Alignment Methods FinalDocument69 pagesSequence Alignment Methods FinalDr. Kaushal Kishor SharmaNo ratings yet

- Hometaxial-Base Medium Power Silicon NPN Transistor: FeaturesDocument2 pagesHometaxial-Base Medium Power Silicon NPN Transistor: Featuresovidiu ovidiusNo ratings yet

- Afosi Exp22 Word Ch04 ML1 DesignDocument5 pagesAfosi Exp22 Word Ch04 ML1 Designw215019229No ratings yet

- Short-Term Load Forecasting Method Based On ARIMA and LSTMDocument5 pagesShort-Term Load Forecasting Method Based On ARIMA and LSTMandrew manuelNo ratings yet

- 2860 Outline F 090Document2 pages2860 Outline F 090TheBBlitzNo ratings yet

- Surfer GriddingDocument19 pagesSurfer GriddingNUHA MNo ratings yet

- Monitoring DPRNT White PaperDocument4 pagesMonitoring DPRNT White PaperHoàngTrầnNo ratings yet

- IT Chapter 11Document6 pagesIT Chapter 11Elyani RamliNo ratings yet

- Traffic Sign Recognition Using Machine Learning Models For Smart Driving Support SystemDocument21 pagesTraffic Sign Recognition Using Machine Learning Models For Smart Driving Support SystemRahul JajuNo ratings yet

- BeSweet BelightDocument41 pagesBeSweet BelightMab AcNo ratings yet

- Gmail - Refer Now - Scheduled Off Campus Drive For Freshers - 2020 MCA, M.Tech and Engineering GraduatesDocument3 pagesGmail - Refer Now - Scheduled Off Campus Drive For Freshers - 2020 MCA, M.Tech and Engineering GraduatesTamilselviNo ratings yet

- 50 PC 55 ZBDocument53 pages50 PC 55 ZBVali IgnatNo ratings yet

- Part A Entity Relationship ModelingDocument8 pagesPart A Entity Relationship Modelinghaha huhuNo ratings yet

- Cisco IronPortDocument59 pagesCisco IronPortMuralyNo ratings yet

- Fluke 79 PDFDocument12 pagesFluke 79 PDFMiguel CarvajalNo ratings yet

- SAP TM DocumentDocument4 pagesSAP TM DocumentsreenusrNo ratings yet

- p174 Wireless Application Pro To CalDocument9 pagesp174 Wireless Application Pro To Caljnanesh582No ratings yet

- These Are Examples Where You Can Base Your Business Case This Is Not A Complete DocumentDocument12 pagesThese Are Examples Where You Can Base Your Business Case This Is Not A Complete DocumentCyLo PatricioNo ratings yet

- Citation 28 - On-The-Combination-Of-Naive-Bayes-And-Decision-Trees-For-IntrusiDocument6 pagesCitation 28 - On-The-Combination-Of-Naive-Bayes-And-Decision-Trees-For-IntrusiZahedi AzamNo ratings yet

- IGMP & IGMP Snooping Clement DuvalDocument32 pagesIGMP & IGMP Snooping Clement DuvalCarlos Andres Silva ZuritaNo ratings yet

- Personal Data Use in Financial Services and The Role of Financial EducationDocument36 pagesPersonal Data Use in Financial Services and The Role of Financial EducationNhật QuangNo ratings yet

- RmantroublrshootingDocument28 pagesRmantroublrshootingapi-3730388No ratings yet

- Loop Length of Plain Single Weft Knitted Structure With ElastaneDocument11 pagesLoop Length of Plain Single Weft Knitted Structure With ElastaneNobodyNo ratings yet

- Fitero B. Garlitos 2017-E905019: Multiple ChoiceDocument2 pagesFitero B. Garlitos 2017-E905019: Multiple Choicefitz garlitosNo ratings yet