Professional Documents

Culture Documents

MP4462

MP4462

Uploaded by

Esteban RodriguezOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

MP4462

MP4462

Uploaded by

Esteban RodriguezCopyright:

Available Formats

MP4462

3.5A, 4MHz, 36V

Step-Down Converter

The Future of Analog IC Technology

DESCRIPTION FEATURES

The MP4462 is a high frequency step-down 120μA Quiescent Current

switching regulator with an integrated internal Wide 3.8V to 36V Operating Input Range

high-side high voltage power MOSFET. It 150mΩ Internal Power MOSFET

provides 3.5A output with current mode control for Up to 4MHz Programmable Switching

fast loop response and easy compensation. Frequency

The wide 3.8V to 36V input range accommodates Ceramic Capacitor Stable

a variety of step-down applications, including Internal Soft-Start

those in an automotive input environment. A Internally Set Current Limit without a

120µA operational quiescent current allows use in Current Sensing Resistor

battery-powered applications. Output Adjustable from 0.8V to 30V

High power conversion efficiency over a wide Available in 3x3mm QFN10 and SOIC8E

load range is achieved by scaling down the Packages.

switching frequency at light load condition to APPLICATIONS

reduce the switching and gate driving losses.

High Voltage Power Conversion

The frequency foldback helps prevent inductor Automotive Systems

current runaway during startup and thermal Industrial Power Systems

shutdown provides reliable, fault tolerant Distributed Power Systems

operation. Battery Powered Systems

In some applications, such as AM radio and All MPS parts are lead-free and adhere to the RoHS directive. For MPS green

ADSL applications, in which the device is status, please visit MPS website under Products, Quality Assurance page.

sensitive to frequency band, the MP4462 can “MPS” and “The Future of Analog IC Technology” are registered trademarks of

Monolithic Power Systems, Inc.

avoid the related EMI problem by setting the

frequency at 4MHz.

The MP4462 is available in small 3x3mm QFN10

and SOIC8E packages.

TYPICAL APPLICATION

C4

100nF

10

8,9 BST 1,2 VOUT

VIN VIN SW 3.3V

D1

3 5

EN EN FB

MP4462

7 4

FREQ COMP

C3

GND 220pF

6

MP4462 Rev. 1.03 www.MonolithicPower.com 1

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

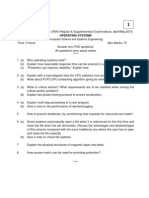

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

ORDERING INFORMATION

Part Number Package Top Marking

MP4462DQ* 3x3mm QFN10 Z2

MP4462DN** SOIC8E MP4462DN

* For Tape & Reel, add suffix –Z (e.g. MP4462DQ–Z);

For RoHS, compliant packaging, add suffix –LF (e.g. MP MP4462DQ–LF–Z).

** For Tape & Reel, add suffix –Z (e.g. MP4462DN–Z);

For RoHS, compliant packaging, add suffix –LF (e.g. MP MP4462DN–LF–Z).

PACKAGE REFERENCE

TOP VIEW

TOP VIEW

SW 1 10 BST

SW 2 9 VIN SW 1 8 BST

EN 3 8 VIN

EN 2 7 VIN

COMP 4 7 FREQ

COMP 3 6 FREQ

FB 5 6 GND

FB 4 5 GND

EXPOSED PAD

ON BACKSIDE

QFN10 SOIC8E

ABSOLUTE MAXIMUM RATINGS (1) Thermal Resistance

(4)

θJA θJC

Supply Voltage (VIN).....................–0.3V to +40V 3x3mm QFN10 ....................... 50 ...... 12... C/W

Switch Voltage (VSW)............ –0.3V to VIN + 0.3V SOIC8E .................................. 50 ...... 10... C/W

BST to SW .....................................–0.3V to +6V

All Other Pins .................................–0.3V to +6V Notes:

(2) 1) Exceeding these ratings may damage the device.

Continuous Power Dissipation (TA = +25°C) 2) The maximum allowable power dissipation is a function of the

3x3mm QFN10 .......................................... 2.5W maximum junction temperature TJ (MAX), the junction-to-

ambient thermal resistance θJA, and the ambient temperature

SOIC8E...................................................... 2.5W TA. The maximum allowable continuous power dissipation at

Junction Temperature ...............................150C any ambient temperature is calculated by PD (MAX) = (TJ

(MAX)-TA)/θJA. Exceeding the maximum allowable power

Lead Temperature ....................................260C dissipation will cause excessive die temperature, and the

Storage Temperature.............. –65°C to +150C regulator will go into thermal shutdown. Internal thermal

shutdown circuitry protects the device from permanent

(3) damage.

Recommended Operating Conditions 3) The device is not guaranteed to function outside of its

Supply Voltage VIN ...........................3.8V to 36V operating conditions.

Output Voltage VOUT .........................0.8V to 30V 4) Measured on JESD51-7, 4-layer PCB.

Operating Junct. Temp. .......... –40C to +125C

MP4462 Rev. 1.03 www.MonolithicPower.com 2

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

ELECTRICAL CHARACTERISTICS

VIN = 12V, VEN = 2.5V, VCOMP = 1.4V, TA= +25C, unless otherwise noted.

Parameter Symbol Condition Min Typ Max Units

Feedback Voltage VFB 4.5V < VIN < 36V 0.776 0.8 0.824 V

Upper Switch On Resistance RDS(ON) VBST – VSW = 5V 150 mΩ

Upper Switch Leakage VEN = 0V, VSW = 0V, VIN = 36V 1 μA

Current Limit 4.0 4.7 A

COMP to Current Sense

GCS 9 A/V

Transconductance

Error Amp Voltage Gain (5) 200 V/V

Error Amp Transconductance ICOMP = ±3µA 40 60 80 µA/V

Error Amp Min Source current VFB = 0.7V 5 µA

Error Amp Min Sink current VFB = 0.9V –5 µA

VIN UVLO Threshold 2.7 3.0 3.3 V

VIN UVLO Hysteresis 0.35 V

Soft-Start Time (5) 0V < VFB < 0.8V 1.5 ms

RFREQ = 45kΩ 1.6 2 2.4 MHz

Oscillator Frequency

RFREQ = 18kΩ 3.2 4 4.8 MHz

Shutdown Supply Current VEN = 0V 12 20 µA

Quiescent Supply Current No load, VFB = 0.9V 120 145 µA

Thermal Shutdown 150 C

Thermal Shutdown Hysteresis 15 C

Minimum Off Time (5) 100 ns

Minimum On Time (5) 100 ns

EN Up Threshold 1.35 1.5 1.65 V

EN Hysteresis 300 mV

Note:

5) Guaranteed by design.

MP4462 Rev. 1.03 www.MonolithicPower.com 3

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

PIN FUNCTIONS

SOIC QFN

Name Description

Pin # Pin #

Switch Node. This is the output from the high-side switch. A low forward drop Schottky

1 1, 2 SW diode to ground is required. The diode must be close to the SW pins to reduce

switching spikes.

Enable Input. Pulling this pin below the specified threshold shuts the chip down. Pulling

2 3 EN

it up above the specified threshold or leaving it floating enables the chip.

Compensation. This node is the output of the error amplifier. Control loop frequency

3 4 COMP

compensation is applied to this pin.

Feedback. This is the input to the error amplifier. The output voltage is set by a resistive

4 5 FB divider connected between the output and GND which scales down VOUT equal to the

internal +0.8V reference.

GND Ground. It should be connected as close as possible to the output capacitor to shorten

5 6 Exposed the high current switch paths. Connect exposed pad to GND plane for optimal thermal

Pad performance.

Switching Frequency Program Input. Connect a resistor from this pin to ground to set

6 7 FREQ

the switching frequency.

Input Supply. This supplies power to all the internal control circuitry, both BS regulators

7 8, 9 VIN and the high-side switch. A decoupling capacitor to ground must be placed close to this

pin to minimize switching spikes.

Bootstrap. This is the positive power supply for the internal floating high-side MOSFET

8 10 BST

driver. Connect a bypass capacitor between this pin and SW pin.

MP4462 Rev. 1.03 www.MonolithicPower.com 4

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

TYPICAL PERFORMANCE CHARACTERISTICS

VIN = 12V, C1 = 10µF, C2 = 22µF, L = 10µH and TA = +25C, unless otherwise noted.

MP4462 Rev. 1.03 www.MonolithicPower.com 5

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

TYPICAL PERFORMANCE CHARACTERISTICS (continued)

VIN = 12V, C1 = 10µF, C2 = 22µF, L = 10µH and TA = +25C, unless otherwise noted.

Startup Shutdown Startup

IOUT = 0.1A IOUT = 0.1A IOUT = 1A

VEN

VEN VEN

5V/div.

5V/div. 5V/div.

VOUT VOUT

VOUT

2V/div. 2V/div.

2V/div.

VSW VSW VSW

10V/div. 10V/div. 10V/div.

IL IL IL

1A/div. 1A/div. 1A/div.

1ms/div. 1ms/div. 1ms/div.

Shutdown Startup Shutdown

IOUT = 1A IOUT = 2A IOUT = 2A

VEN VEN VEN

5V/div. 5V/div. 5V/div.

VOUT VOUT VOUT

2V/div. 2V/div. 2V/div.

VSW VSW VSW

10V/div. 10V/div. 10V/div.

IL IL IL

1A/div. 2A/div. 2A/div.

1ms/div.

Short Circuit Entry Short Circuit Recovery

IOUT = 0.1A to Short IOUT = Short to 0.1A

VOUT VOUT

2V/div. 2V/div.

IL IL

1A/div. 1A/div.

MP4462 Rev. 1.03 www.MonolithicPower.com 6

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

BLOCK DIAGRAM

VIN VIN

+

--

REFERENCE UVLO/ 5V +

--

INTERNAL

EN THERMAL 2.6V BST

REGULATORS

SHUTDOWN

SW

ISW --

1.5ms SS SS +

VOUT

Level ISW

SW

Shift

FB Gm Error Amp

-- COMP

SS

0V8 + OSCILLATOR CLK

VOUT

COMP GND FREQ

Figure 1—Functional Block Diagram

MP4462 Rev. 1.03 www.MonolithicPower.com 7

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

OPERATION

The MP4462 is a variable frequency, can be enabled and disabled by EN which has

non-synchronous, step-down switching positive logic. Its falling threshold is a precision

regulator with an integrated high-side high 1.2V, and its rising threshold is 1.5V (300mV

voltage power MOSFET. It provides a single higher).

highly efficient solution with current mode

When floating, EN is pulled up to about 3.0V by

control for fast loop response and easy

an internal 1µA current source so it is enabled.

compensation. It features a wide input voltage

To pull it down, 1µA current capability is needed.

range, internal soft-start control and precision

current limiting. Its very low operational When EN is pulled down below 1.2V, the chip is

quiescent current makes it suitable for battery put into the lowest shutdown current mode.

powered applications. When EN is higher than zero but lower than its

rising threshold, the chip is still in shutdown

PWM Control

mode but the shutdown current increases

At moderate to high output current, the MP4462

slightly.

operates in a fixed frequency, peak current

control mode to regulate the output voltage. A Under-Voltage Lockout (UVLO)

PWM cycle is initiated by the internal clock. The Under-voltage lockout (UVLO) is implemented

power MOSFET is turned on and remains on to protect the chip from operating at insufficient

until its current reaches the value set by the supply voltage. The UVLO rising threshold is

COMP voltage. When the power switch is off, it about 3.0V while its falling threshold is a

remains off for at least 100ns before the next consistent 2.6V.

cycle starts. If, in one PWM period, the current

in the power MOSFET does not reach the Internal Soft-Start

COMP set current value, the power MOSFET The soft-start is implemented to prevent the

remains on, saving a turn-off operation. converter output voltage from overshooting

during startup. When the chip starts, the

Error Amplifier internal circuitry generates a soft-start voltage

The error amplifier compares the FB pin voltage (SS) ramping up from 0V to 2.6V. When it is

with the internal reference (REF) and outputs a lower than the internal reference (REF), SS

current proportional to the difference between overrides REF so the error amplifier uses SS as

the two. This output current is then used to the reference. When SS is higher than REF,

charge the external compensation network to REF regains control.

form the COMP voltage, which is used to

control the power MOSFET current. Thermal Shutdown

Thermal shutdown is implemented to prevent

During operation, the minimum COMP voltage the chip from operating at exceedingly high

is clamped to 0.9V and its maximum is clamped temperatures. When the silicon die temperature

to 2.0V. COMP is internally pulled down to GND is higher than its upper threshold, it shuts down

in shutdown mode. COMP should not be pulled the whole chip. When the temperature is lower

up beyond 2.6V. than its lower threshold, the chip is enabled

Internal Regulator again.

Most of the internal circuitries are powered from Floating Driver and Bootstrap Charging

the 2.6V internal regulator. This regulator takes The floating power MOSFET driver is powered

the VIN input and operates in the full VIN range. by an external bootstrap capacitor. This floating

When VIN is greater than 3.0V, the output of driver has its own UVLO protection. This

the regulator is in full regulation. When VIN is UVLO’s rising threshold is 2.2V with a threshold

lower than 3.0V, the output decreases. of 150mV.

Enable Control The bootstrap capacitor is charged and

The MP4462 has a dedicated enable control pin regulated to about 5V by the dedicated internal

(EN). With high enough input voltage, the chip bootstrap regulator. When the voltage between

MP4462 Rev. 1.03 www.MonolithicPower.com 8

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

the BST and SW nodes is lower than its maximum current of the internal power

regulation, a PMOS pass transistor connected MOSFET is internally limited.

from VIN to BST is turned on. The charging

Startup and Shutdown

current path is from VIN, BST and then to SW.

External circuit should provide enough voltage If both VIN and EN are higher than their

headroom to facilitate the charging. appropriate thresholds, the chip starts. The

reference block starts first, generating stable

As long as VIN is sufficiently higher than SW,

reference voltage and currents, and then the

the bootstrap capacitor can be charged. When

internal regulator is enabled. The regulator

the power MOSFET is ON, VIN is about equal

provides stable supply for the remaining

to SW so the bootstrap capacitor cannot be

circuitries.

charged. When the external diode is on, the

difference between VIN and SW is largest, thus While the internal supply rail is up, an internal

making it the best period to charge. When there timer holds the power MOSFET OFF for about

is no current in the inductor, SW equals the 50µs to blank the startup glitches. When the

output voltage VOUT so the difference between internal soft-start block is enabled, it first holds

VIN and VOUT can be used to charge the its SS output low to ensure the remaining

bootstrap capacitor. circuitries are ready and then slowly ramps up.

At higher duty cycle operation condition, the Three events can shut down the chip: EN low,

time period available to the bootstrap charging VIN low and thermal shutdown. In the shutdown

is less so the bootstrap capacitor may not be procedure, power MOSFET is turned off first to

sufficiently charged. avoid any fault triggering. The COMP voltage

and the internal supply rail are then pulled down.

In case the internal circuit does not have

sufficient voltage and the bootstrap capacitor is Programmable Oscillator

not charged, extra external circuitry can be The MP4462 oscillating frequency is set by an

used to ensure the bootstrap voltage is in the external resistor, RFREQ from the FREQ pin to

normal operational region. Refer to External ground. The relationship between RFREQ and fS

Bootstrap Diode in Application section. refer to table1 in Application section.

The DC quiescent current of the floating driver

is about 20µA. Make sure the bleeding current

at the SW node is higher than this value, such

that:

VO

IO 20A

(R1 R2)

Current Comparator and Current Limit

The power MOSFET current is accurately

sensed via a current sense MOSFET. It is then

fed to the high speed current comparator for the

current mode control purpose. The current

comparator takes this sensed current as one of

its inputs. When the power MOSFET is turned

on, the comparator is first blanked till the end of

the turn-on transition to avoid noise issues. The

comparator then compares the power switch

current with the COMP voltage. When the

sensed current is higher than the COMP

voltage, the comparator output is low, turning

off the power MOSFET. The cycle-by-cycle

MP4462 Rev. 1.03 www.MonolithicPower.com 9

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

APPLICATION INFORMATION

COMPONENT SELECTION About 20µA current from high side BS circuitry

can be seen at the output when the MP4462 is

Setting the Frequency at no load. In order to absorb this small amount

The MP4462 has an externally adjustable of current, keep R2 under 40KΩ. A typical

frequency. The switching frequency (fS) can be value for R2 can be 40.2kΩ. With this value, R1

set using a resistor at FREQ pin (RFREQ). The

can be determined by:

recommended RFREQ value for various fS, see

Table1. R1 50.25 ( VOUT 0.8)(k)

Table 1—fS vs. RFREQ

For example, for a 3.3V output voltage, R2 is

RFREQ (kΩ) fS (MHz) 40.2kΩ, and R1 is 127kΩ.

18 4

Inductor

20 3.8 The inductor is required to supply constant

22.1 3.5

current to the output load while being driven by

the switched input voltage. A larger value

24 3.3 inductor will result in less ripple current that will

26.7 3 result in lower output ripple voltage. However,

the larger value inductor will have a larger

30 2.8 physical size, higher series resistance, and/or

33.2 2.5 lower saturation current.

39 2.2

A good rule for determining the inductance to

45.3 2 use is to allow the peak-to-peak ripple current in

the inductor to be approximately 30% of the

51 1.8

maximum switch current limit. Also, make sure

57.6 1.6 that the peak inductor current is below the

68 1.4 maximum switch current limit. The inductance

value can be calculated by:

80.6 1.2

VOUT V

100 1 L1 1 OUT

fS ΔIL VIN

133 0.8

Where VOUT is the output voltage, VIN is the input

200 0.5

voltage, fS is the switching frequency, and ΔIL is

340 0.3 the peak-to-peak inductor ripple current.

536 0.2 Choose an inductor that will not saturate under

the maximum inductor peak current. The peak

Setting the Output Voltage inductor current can be calculated by:

The output voltage is set using a resistive

voltage divider from the output voltage to FB pin. VOUT V

ILP ILOAD 1 OUT

The voltage divider divides the output voltage 2 fS L1 VIN

down to the feedback voltage by the

ratio: Where ILOAD is the load current.

VFB VOUT

R2 Table 2 lists a number of suitable inductors

R1 R2 from various manufacturers. The choice of

Thus the output voltage is: which style inductor to use mainly depends on

the price vs. size requirements and any EMI

(R1 R2) requirement.

VOUT VFB

R2

MP4462 Rev. 1.03 www.MonolithicPower.com 10

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

Table 2—Inductor Selection Guide

Dimensions

Part Number Inductance (µH) Max DCR (Ω) Current Rating (A) L x W x H (mm3)

Wurth Electronics

7447789002 2.2 0.019 4 7.3x7.3x3.2

7447789003 3.3 0.024 3.42 7.3x7.3x3.2

7447789004 4.7 0.033 2.9 7.3x7.3x3.2

744066100 10 0.035 3.6 10x10x3.8

744771115 15 0.025 3.75 12x12x6

744771122 22 0.031 3.37 12x12x6

TDK

RLF7030T-2R2 2.2 0.012 5.4 7.3x6.8x3.2

RLF7030T-3R3 3.3 0.02 4.1 7.3x6.8x3.2

RLF7030T-4R7 4.7 0.031 3.4 7.3x6.8x3.2

SLF10145T-100 10 0.0364 3 10.1x10.1x4.5

SLF12565T-150M4R2 15 0.0237 4.2 12.5x12.5x6.5

SLF12565T-220M3R5 22 0.0316 3.5 12.5x12.5x6.5

Toko

FDV0630-2R2M 2.2 0.021 5.3 7.7x7x3

FDV0630-3R3M 3.3 0.031 4.3 7.7x7x3

FDV0630-4R7M 4.7 0.049 3.3 7.7x7x3

919AS-100M 10 0.0265 4.3 10.3x10.3x4.5

919AS-160M 16 0.0492 3.3 10.3x10.3x4.5

919AS-220M 22 0.0776 3 10.3x10.3x4.5

Output Rectifier Diode Input Capacitor

The output rectifier diode supplies the current to The input current to the step-down converter is

the inductor when the high-side switch is off. To discontinuous, therefore a capacitor is required to

reduce losses due to the diode forward voltage supply the AC current to the step-down converter

and recovery times, use a Schottky diode. while maintaining the DC input voltage. Use low

ESR capacitors for the best performance. Ceramic

Choose a diode whose maximum reverse

capacitors are preferred, but tantalum or low-ESR

voltage rating is greater than the maximum

electrolytic capacitors may also suffice.

input voltage, and whose current rating is

greater than the maximum load current. Table 3 For simplification, choose the input capacitor

lists example Schottky diodes and with RMS current rating greater than half of the

manufacturers. maximum load current.

Table 3—Diode Selection Guide

Voltage/

Diodes Current Manufacturer

Rating

B340A-13-F 40V, 3A Diodes Inc.

CMSH3-40MA 40V, 3A Central Semi

MP4462 Rev. 1.03 www.MonolithicPower.com 11

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

The input capacitor (C1) can be electrolytic, Compensation Components

tantalum or ceramic. When using electrolytic or MP4462 employs current mode control for easy

tantalum capacitors, a small, high quality compensation and fast transient response. The

ceramic capacitor, i.e. 0.1μF, should be placed system stability and transient response are

as close to the IC as possible. When using controlled through the COMP pin. COMP pin is

ceramic capacitors, make sure that they have the output of the internal error amplifier. A

enough capacitance to provide sufficient charge series capacitor-resistor combination sets a

to prevent excessive voltage ripple at input. The pole-zero combination to control the

input voltage ripple caused by capacitance can characteristics of the control system. The DC

be estimated by: gain of the voltage feedback loop is given by:

ILOAD V V VFB

VIN OUT 1 OUT A VDC R LOAD G CS A VEA

fS C1 VIN VIN VOUT

Output Capacitor Where AVEA is the error amplifier voltage gain,

The output capacitor (C2) is required to 200V/V; GCS is the current sense

maintain the DC output voltage. Ceramic, transconductance, 3.7A/V; RLOAD is the load

tantalum, or low ESR electrolytic capacitors are resistor value.

recommended. Low ESR capacitors are The system has two poles of importance. One

preferred to keep the output voltage ripple low. is due to the compensation capacitor (C3), the

The output voltage ripple can be estimated by: output resistor of error amplifier. The other is

VOUT V 1 due to the output capacitor and the load resistor.

VOUT 1 OUT R ESR These poles are located at:

fS L VIN 8 f S C2

GEA

Where L is the inductor value and RESR is the fP1

2 C3 A VEA

equivalent series resistance (ESR) value of the

output capacitor. 1

fP2

In the case of ceramic capacitors, the 2 C2 R LOAD

impedance at the switching frequency is

Where, GEA is the error amplifier

dominated by the capacitance. The output

transconductance, 60μA/V.

voltage ripple is mainly caused by the

capacitance. For simplification, the output The system has one zero of importance, due to

voltage ripple can be estimated by: the compensation capacitor (C3) and the

compensation resistor (R3). This zero is located

VOUT V at:

ΔVOUT 2

1 OUT

8 fS L C2 VIN

1

f Z1

In the case of tantalum or electrolytic capacitors, 2 C3 R3

the ESR dominates the impedance at the

The system may have another zero of

switching frequency. For simplification, the

importance, if the output capacitor has a large

output ripple can be approximated to:

capacitance and/or a high ESR value. The zero,

VOUT V due to the ESR and capacitance of the output

ΔVOUT 1 OUT R ESR

f S L VIN capacitor, is located at:

The characteristics of the output capacitor also 1

fESR

affect the stability of the regulation system. The 2 C2 R ESR

MP4462 can be optimized for a wide range of

capacitance and ESR values.

MP4462 Rev. 1.03 www.MonolithicPower.com 12

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

In this case (as shown in Figure 2), a third pole

1. Choose the compensation resistor (R3) to set

set by the compensation capacitor (C6) and the

the desired crossover frequency. Determine the

compensation resistor (R3) is used to

R3 value by the following equation:

compensate the effect of the ESR zero on the

loop gain. This pole is located at: 2 C2 f C VOUT

R3

1 G EA G CS VFB

f P3

2 C6 R3 Where fC is the desired crossover frequency.

The goal of compensation design is to shape 2. Choose the compensation capacitor (C3) to

the converter transfer function to get a desired achieve the desired phase margin. For

loop gain. The system crossover frequency applications with typical inductor values, setting

where the feedback loop has the unity gain is the compensation zero, fZ1, below one forth of

important. Lower crossover frequencies result the crossover frequency provides sufficient

in slower line and load transient responses, phase margin. Determine the C3 value by the

while higher crossover frequencies could cause following equation:

system unstable. A good rule of thumb is to set

the crossover frequency to approximately one- 4

C3

tenth of the switching frequency. The Table 4 2 R3 f C

lists the typical values of compensation 3. Determine if the second compensation

components for some standard output voltages capacitor (C6) is required. It is required if the

with various output capacitors and inductors. ESR zero of the output capacitor is located at

The values of the compensation components less than half of the switching frequency, or the

have been optimized for fast transient following relationship is valid:

responses and good stability at given conditions.

1 f

Table 4—Compensation Values for Typical S

2 C2 R ESR 2

Output Voltage/Capacitor Combinations

VOUT C2 R3 C3 If this is the case, then add the second

L (µH) C6 compensation capacitor (C6) to set the pole fP3

(V) (µF) (kΩ) (pF)

at the location of the ESR zero. Determine the

1.8 4.7 47 105 100 None C6 value by the equation:

2.5 4.7 - 6.8 22 54.9 220 None C2 R ESR

C6

R3

3.3 6.8 -10 22 68.1 220 None

5 15 - 22 22 100 150 None

12 22 - 33 22 147 150 None

To optimize the compensation components for

conditions not listed in Table 3, the following

procedure can be used.

MP4462 Rev. 1.03 www.MonolithicPower.com 13

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

High Frequency Operation Layout becomes more important when the

The switching frequency of MP4462 can be device switches at higher frequency. It is

programmed up to 4MHz by an external resistor. essential to place the input decoupling

Please pay attention to the following if the capacitor, catch diode and the MP4462 (Vin pin,

switching frequency is above 2MHz. SW pin and PGND) as close as possible, with

traces that are very short and fairly wide. This

The minimum on time of MP4462 is about 80ns

can help to greatly reduce the voltage spike on

(typ). Pulse skipping operation can be seen

SW node, and lower the EMI noise level as well.

more easily at higher switching frequency due

to the minimum on time. Recommended Try to run the feedback trace as far from the

operating voltage is 12V or below, and 24V or inductor and noisy power traces as possible. It

below at 2MHz. Refer to Figure 2 below for is often a good idea to run the feedback trace

detailed information. on the side of the PCB opposite of the inductor

with a ground plane separating the two. The

Recommended VIN (max) compensation components should be placed

vs Switching Frequency closed to the MP4462. Do not place the

30

compensation components close to or under

high dv/dt SW node, or inside the high di/dt

25

power loop. If you have to do so, the proper

ground plane must be in place to isolate those.

VIN (MAX) (V)

20

Switching loss is expected to be increased at

VOUT=3.3V

high switching frequency. To help to improve

15

the thermal conduction, a grid of thermal vias

can be created right under the exposed pad. It

10

is recommended that they be small (15mil

VOUT=2.5V

barrel diameter) so that the hole is essentially

5

1500 2000 2500 3000 3500 4000 filled up during the plating process, thus aiding

fs (KHz) conduction to the other side. Too large a hole

can cause ‘solder wicking’ problems during the

Figure 2—Recommend Max VIN vs. fs

reflow soldering process. The pitch (distance

Since the internal bootstrap circuitry has higher between the centers) of several such thermal

impedance, which may not be adequate to vias in an area is typically 40mil. Please refer to

charge the bootstrap capacitor during each (1- the layout example on EV4460 datasheet.

D)×Ts charging period, an external bootstrap

charging diode is strongly recommended if the

switching frequency is above 2MHz (see

External Bootstrap Diode section for detailed

implementation information).

With higher switching frequencies, the inductive

reactance (XL) of capacitor comes to dominate,

so that the ESL of input/output capacitor

determines the input/output ripple voltage at

higher switching frequency. As a result of that,

high frequency ceramic capacitor is strongly

recommended as input decoupling capacitor

and output filtering capacitor for such high

frequency operation.

MP4462 Rev. 1.03 www.MonolithicPower.com 14

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

This diode is also recommended for high duty

External Bootstrap Diode

cycle operation (when VOUT /VIN >65%) or low

It is recommended that an external bootstrap

VIN (<5Vin) applications.

diode be added when the input voltage is no

greater than 5V or the 5V rail is available in the At no load or light load, the converter may

system. This helps improve the efficiency of the operate in pulse skipping mode in order to

regulator. The bootstrap diode can be a low maintain the output voltage in regulation. Thus

cost one such as IN4148 or BAT54. there is less time to refresh the BS voltage. In

order to have enough gate voltage under such

5V operating conditions, the difference of VIN –VOUT

should be greater than 3V. For example, if the

BS

VOUT is set to 3.3V, the VIN needs to be higher

than 3.3V+3V=6.3V to maintain enough BS

MP4462 voltage at no load or light load. To meet this

SW requirement, EN pin can be used to program

the input UVLO voltage to Vout+3V.

Figure 3—External Bootstrap Diode

MP4462 Rev. 1.03 www.MonolithicPower.com 15

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

TYPICAL APPLICATION CIRCUITS

C4

100nF

10

VIN 8,9 BST 1,2 VOUT

6V - 36V VIN SW 1.8V

D1

3 5

EN EN FB

MP4462

7 4

FREQ COMP

C3

GND 100pF

C6

6 NS

Figure 4—1.8V Output Typical Application Schematic

C4

100nF

10

VIN 8,9 BST 1,2 VOUT

10V - 36V VIN SW 5V

D1

3 5

EN EN FB

MP4462

7 4

FREQ COMP

C3

GND 150pF

C6

6 NS

Figure 5—5V Output Typical Application Schematic

MP4462 Rev. 1.03 www.MonolithicPower.com 16

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

PCB LAYOUT GUIDE

PCB layout is very important to achieve stable 2) Bypass ceramic capacitors are suggested

operation. It is highly recommended to duplicate to be put close to the VIN Pin.

EVB layout for optimum performance. 3) Ensure all feedback connections are short

If change is necessary, please follow these and direct. Place the feedback resistors

guidelines and take Figure 6 for reference. and compensation components as close to

the chip as possible.

1) Keep the path of switching current short

and minimize the loop area formed by Input 4) Route SW away from sensitive analog

cap, high-side MOSFET and external areas such as FB.

switching diode. 5) Connect IN, SW, and especially GND

respectively to a large copper area to cool

the chip to improve thermal performance

and long-term reliability.

C4

L1

BST

VIN VIN SW VOUT

D1 C2

C1

R5

EN EN FB

MP4462 R1

R4 R2

FREQ COMP

GND C3

R6

R3

MP4462 Typical Application Circuit

GND

L1

R5

R3

C3

R4

R2

COMP 4

R1

SW 2

SW 1

SW

EN 3

FB 5

C4

10 BST

6 GND

7 FREQ

8

9

Vin

Vin

D1

R6

C2

C1

Vin GND GND Vo

MP4462DQ Top Layer MP4462DQ Bottom Layer

MP4462 Rev. 1.03 www.MonolithicPower.com 17

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

6

GND

L1

R3

C3

R4

R5

R2

R1

SW

4

1

COMP FREQ

FB

EN

SW

GND

VIN

BST

C4

D1

5

R6

C2

C1

Vin GND GND Vo

MP4462DN Top Layer MP4462DN Bottom Layer

Figure 6―MP4462 Typical Application Circuit and PCB Layout Guide

MP4462 Rev. 1.03 www.MonolithicPower.com 18

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

PACKAGE INFORMATION

3mm x 3mm QFN10

2.90 0.30 1.45 PIN 1 ID

3.10 0.50 1.75 SEE DETAIL A

PIN 1 ID

MARKING

0.18

10 1

0.30

2.90 2.25

PIN 1 ID 2.55

3.10 0.50

INDEX AREA

BSC

6 5

TOP VIEW BOTTOM VIEW

PIN 1 ID OPTION A PIN 1 ID OPTION B

R0.20 TYP. R0.20 TYP.

0.80

1.00

0.20 REF

0.00

0.05

SIDE VIEW DETAIL A

NOTE:

2.90

1) ALL DIMENSIONS ARE IN MILLIMETERS.

0.70 1.70 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETER MAX.

0.25 4) DRAWING CONFORMS TO JEDEC MO-229, VARIATION VEED-5.

5) DRAWING IS NOT TO SCALE.

2.50

0.50

RECOMMENDED LAND PATTERN

MP4462 Rev. 1.03 www.MonolithicPower.com 19

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

MP4462 – 3.5A, 4MHz, 36V STEP-DOWN CONVERTER

SOIC8E (EXPOSED PAD)

0.189(4.80) 0.124(3.15)

0.197(5.00) 0.136(3.45)

8 5

0.150(3.80) 0.228(5.80) 0.089(2.26)

PIN 1 ID 0.157(4.00) 0.244(6.20) 0.101(2.56)

1 4

TOP VIEW BOTTOM VIEW

SEE DETAIL "A"

0.051(1.30)

0.067(1.70)

0.0075(0.19)

SEATING PLANE

0.0098(0.25)

0.000(0.00)

0.013(0.33) 0.006(0.15)

0.020(0.51) SIDE VIEW

0.050(1.27)

BSC

FRONT VIEW 0.010(0.25)

x 45o

0.020(0.50)

GAUGE PLANE

0.010(0.25) BSC

0.024(0.61) 0.050(1.27)

0.016(0.41)

0o-8o 0.050(1.27)

0.063(1.60)

DETAIL "A"

0.103(2.62) 0.213(5.40)

NOTE:

1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN

BRACKET IS IN MILLIMETERS.

2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH,

PROTRUSIONS OR GATE BURRS.

3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH

0.138(3.51) OR PROTRUSIONS.

4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING)

SHALL BE 0.004" INCHES MAX.

RECOMMENDED LAND PATTERN 5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION BA.

6) DRAWING IS NOT TO SCALE.

NOTICE: The information in this document is subject to change without notice. Users should warrant and guarantee that third

party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not

assume any legal responsibility for any said applications.

MP4462 Rev. 1.03 www.MonolithicPower.com 20

2/27/2014 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

You might also like

- Condensador Ciac Ca43ax 18 Seer InverterDocument2 pagesCondensador Ciac Ca43ax 18 Seer InverterMantenimiento TechniaireNo ratings yet

- 020 Atpl Agk QuestionsDocument2 pages020 Atpl Agk QuestionsYahya Yıldırım50% (2)

- MP4462DN Step-Down ConverterDocument21 pagesMP4462DN Step-Down ConverterahmedNo ratings yet

- MP4569Document17 pagesMP4569Jesús Miguel LemNo ratings yet

- 2A, 4.2V-16V Input, Fast Transient Synchronous Step-Down ConverterDocument18 pages2A, 4.2V-16V Input, Fast Transient Synchronous Step-Down ConverterCesarS100% (1)

- MP2143DJDocument14 pagesMP2143DJlikhungtongNo ratings yet

- 3A, 4.2V-16V Input, Fast Transient Synchronous Step-Down ConverterDocument18 pages3A, 4.2V-16V Input, Fast Transient Synchronous Step-Down ConverterJuan C RiveraNo ratings yet

- 1.5A, 2Mhz, 55V Step-Down Converter: The Future of Analog Ic TechnologyDocument17 pages1.5A, 2Mhz, 55V Step-Down Converter: The Future of Analog Ic TechnologyBruno CamposNo ratings yet

- High Efficiency 2A, 36V, Synchronous Step Down Converter: The Future of Analog IC TechnologyDocument20 pagesHigh Efficiency 2A, 36V, Synchronous Step Down Converter: The Future of Analog IC TechnologyAspire2222No ratings yet

- MP1657 MPSDocument19 pagesMP1657 MPSCan IlicaNo ratings yet

- MP28167GQ ADocument32 pagesMP28167GQ AHamouda MahmodNo ratings yet

- Synchronous-Rectified Buck MOSFET Drivers: Features General DescriptionDocument5 pagesSynchronous-Rectified Buck MOSFET Drivers: Features General DescriptionTeles SilvaNo ratings yet

- uPI Semiconductor Up1735 Synchronous-Rectified Buck Converter DatasheetDocument13 pagesuPI Semiconductor Up1735 Synchronous-Rectified Buck Converter DatasheetSultan SinghNo ratings yet

- Nb679a MpsDocument19 pagesNb679a MpswarkeravipNo ratings yet

- 100V Input, 1A High Power LED Driver: The Future of Analog IC TechnologyDocument10 pages100V Input, 1A High Power LED Driver: The Future of Analog IC TechnologyAdrian WongNo ratings yet

- Boundary Mode PFC Controller: The Future of Analog IC TechnologyDocument14 pagesBoundary Mode PFC Controller: The Future of Analog IC TechnologydistefanoNo ratings yet

- 1Mhz, All-Ceramic, 3A PWM Buck DC/DC Converter: Global Mixed-Mode Technology IncDocument1 page1Mhz, All-Ceramic, 3A PWM Buck DC/DC Converter: Global Mixed-Mode Technology IncLeonardo FusserNo ratings yet

- 4-String, Max 400mA/String, 80V Return, Step-Up, WLED ControllerDocument17 pages4-String, Max 400mA/String, 80V Return, Step-Up, WLED ControllerLucía MitchellNo ratings yet

- REN Isl6269a DST 20040119Document15 pagesREN Isl6269a DST 20040119Martin WhybrowNo ratings yet

- MP2480Document12 pagesMP2480Abdiel Gomez vielzaNo ratings yet

- M2303ADNDocument15 pagesM2303ADNffyddNo ratings yet

- Slusck3 PDFDocument40 pagesSlusck3 PDFGlauco Borges BrumNo ratings yet

- Description Features: Ait Semiconductor IncDocument8 pagesDescription Features: Ait Semiconductor Incteranet tbtNo ratings yet

- MP3391 r1.12Document18 pagesMP3391 r1.12Elsa Nababan EchaNo ratings yet

- MP3391Document18 pagesMP3391Raul AlfaroNo ratings yet

- MP9943Document20 pagesMP9943techgamebr85No ratings yet

- MP3924GUDocument56 pagesMP3924GUProyecto EspecialNo ratings yet

- U1 Xbox OneDocument14 pagesU1 Xbox OneCheckpoint Game CenterNo ratings yet

- General Description Features: EzbuckDocument9 pagesGeneral Description Features: EzbuckCristina NistorNo ratings yet

- U P6103Document15 pagesU P6103Selmar CavalcantiNo ratings yet

- 3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesDocument12 pages3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesAbdul MuhidNo ratings yet

- TPS53219A 3-V To 28-V Input, D-CAP, Eco-Mode™, Synchronous Buck ControllerDocument36 pagesTPS53219A 3-V To 28-V Input, D-CAP, Eco-Mode™, Synchronous Buck ControllerGus Khoir SrNo ratings yet

- 3A, 1Mhz, Synchronous Step-Down Converter: General Description FeaturesDocument12 pages3A, 1Mhz, Synchronous Step-Down Converter: General Description FeatureskiryanoffNo ratings yet

- Ap64350 2Document26 pagesAp64350 2Nishanth MNo ratings yet

- A4960 A Automotive DatasheetDocument34 pagesA4960 A Automotive DatasheetCanerNo ratings yet

- MP3398A - r1.05 Driver Les Board Flaco BellohorizonteDocument20 pagesMP3398A - r1.05 Driver Les Board Flaco BellohorizonteAndres AlegriaNo ratings yet

- High Current Power Half Bridge: The Future of Analog IC TechnologyDocument8 pagesHigh Current Power Half Bridge: The Future of Analog IC Technologyقناة احترف بنفسكNo ratings yet

- TDA7088T - 2 - FM Receiver Circuit For BatteryDocument16 pagesTDA7088T - 2 - FM Receiver Circuit For BatteryAtulNo ratings yet

- TDA7088Document17 pagesTDA7088lumilanisNo ratings yet

- Mp1584en LF Z-2945524Document18 pagesMp1584en LF Z-2945524samuelRODNo ratings yet

- Dying Gasp Storage and Release Control IC: Description FeaturesDocument13 pagesDying Gasp Storage and Release Control IC: Description FeaturesSALAH NETNo ratings yet

- Ftm-300drde Ts Eh071m90aDocument59 pagesFtm-300drde Ts Eh071m90a1012268087No ratings yet

- 23V, 2.5A, 340Khz Synchronous Step-Down DC/DC Converter: Description FeaturesDocument14 pages23V, 2.5A, 340Khz Synchronous Step-Down DC/DC Converter: Description FeaturesFuadNo ratings yet

- 5.5A, 18V, 650Khz, Acot Synchronous Step-Down Converter: General Description FeaturesDocument18 pages5.5A, 18V, 650Khz, Acot Synchronous Step-Down Converter: General Description FeaturesALXNo ratings yet

- Data Sheet MKP1584Document17 pagesData Sheet MKP1584aafeletronicaNo ratings yet

- pll1700Document19 pagespll1700jessybanda1000No ratings yet

- MP5048GUDocument24 pagesMP5048GUHeraclio Camacho UlloaNo ratings yet

- Primary-Side Control, Offline LED Controller With Active PFC, NTC and PWM DimmingDocument19 pagesPrimary-Side Control, Offline LED Controller With Active PFC, NTC and PWM Dimmingzuffflor_925748656No ratings yet

- 8T Rt5768aDocument12 pages8T Rt5768aVISHALNo ratings yet

- 28V, 6.5A, Low Iq, Synchronous Buck Converter With 2-Bit VIDDocument24 pages28V, 6.5A, Low Iq, Synchronous Buck Converter With 2-Bit VIDElla Wijaya ChandraNo ratings yet

- Aerosemi MT1470Document10 pagesAerosemi MT1470StephieNo ratings yet

- AT1526 GlobalMixed ModetechnologyDocument2 pagesAT1526 GlobalMixed ModetechnologyFafa MangstabNo ratings yet

- Datasheet NCP81109Document28 pagesDatasheet NCP81109zigmund zigmundNo ratings yet

- ISL6269 Data SheetDocument14 pagesISL6269 Data SheetSummer SpringNo ratings yet

- Non-Isolated, Triac Dimmable PFC Led Driver For 120vac, Up To 10W LedsDocument21 pagesNon-Isolated, Triac Dimmable PFC Led Driver For 120vac, Up To 10W LedsJNarigonNo ratings yet

- 3A, 28V, 385Khz Step-Down Converter: The Future of Analog Ic TechnologyDocument13 pages3A, 28V, 385Khz Step-Down Converter: The Future of Analog Ic TechnologyIoan TivgaNo ratings yet

- MT3D-0113LSM-2-GaAs MMIC T3 Mixer With Differential IFDocument18 pagesMT3D-0113LSM-2-GaAs MMIC T3 Mixer With Differential IF2022ht80586No ratings yet

- Synchronous-Rectified Buck MOSFET Drivers: Features General DescriptionDocument12 pagesSynchronous-Rectified Buck MOSFET Drivers: Features General DescriptionALANRAFAELTECNICONo ratings yet

- 6A, 23V Synchronous Step-Down Converter With 3.3V/5V LDO: RT6256B/CDocument20 pages6A, 23V Synchronous Step-Down Converter With 3.3V/5V LDO: RT6256B/CkiryanoffNo ratings yet

- Zxmp4a16gq DiodesDocument7 pagesZxmp4a16gq DiodesashwinNo ratings yet

- Ap 64200Document26 pagesAp 64200Ciro SpanholiNo ratings yet

- High-Performance D/A-Converters: Application to Digital TransceiversFrom EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNo ratings yet

- Electromagnetic Engineering: ECE292 Sophomore Seminar 18 March 2008Document26 pagesElectromagnetic Engineering: ECE292 Sophomore Seminar 18 March 2008Alamgir Kabir ShuvoNo ratings yet

- Lab Report Heat ExchangerDocument17 pagesLab Report Heat ExchangerFirdaus Zainal AbidinNo ratings yet

- Fiber Optic Gyroscope ThesisDocument4 pagesFiber Optic Gyroscope Thesisangelashfordmurfreesboro100% (2)

- 3 To 6 KW Single PhaseDocument2 pages3 To 6 KW Single PhaseEureka SolarNo ratings yet

- Apollo XP95 SWITCH MONITORDocument3 pagesApollo XP95 SWITCH MONITORjuankaldeNo ratings yet

- BYV27-50, BYV27-100, BYV27-150, BYV27-200: Vishay SemiconductorsDocument4 pagesBYV27-50, BYV27-100, BYV27-150, BYV27-200: Vishay SemiconductorsPrabhat NarangNo ratings yet

- Test Report No. 7191049787-EEC13-KYM: Dated 04 Jul 2013Document31 pagesTest Report No. 7191049787-EEC13-KYM: Dated 04 Jul 2013Justin NgNo ratings yet

- 2-4 Cell Li+ Battery Smbus Charge Controller With N-Channel Power Mosfet Selector and Advanced Circuit ProtectionDocument41 pages2-4 Cell Li+ Battery Smbus Charge Controller With N-Channel Power Mosfet Selector and Advanced Circuit Protectionarranguezjr5991No ratings yet

- Infineon CYW43439 DataSheet v03 - 00 ENDocument88 pagesInfineon CYW43439 DataSheet v03 - 00 ENDenes MarschalkoNo ratings yet

- Electrical System in AutomobileDocument13 pagesElectrical System in AutomobileRohit kendreNo ratings yet

- 1 IntroductionDocument21 pages1 IntroductionEric MugaNo ratings yet

- CV-Bresly Tua SihiteDocument16 pagesCV-Bresly Tua SihiteYoppy YolandaNo ratings yet

- microTALK Mt200 User ManualDocument4 pagesmicroTALK Mt200 User ManualAnonymous lStpu6o44cNo ratings yet

- L42 ECEN5817 NotesDocument17 pagesL42 ECEN5817 NotesMuhammad Uzair BilalNo ratings yet

- Sylvania Quickstart GuideDocument1 pageSylvania Quickstart GuidethehardmaxNo ratings yet

- July 21, 1953: Frty. 4. INVENTOR BY%Document7 pagesJuly 21, 1953: Frty. 4. INVENTOR BY%Leonardo MarraffiniNo ratings yet

- Timer-Counter in AVRDocument20 pagesTimer-Counter in AVRرضا میرزانیاNo ratings yet

- EELab2 Exp8 AD ConverterDocument4 pagesEELab2 Exp8 AD ConverterAhmed Abdel AzizNo ratings yet

- Power Quality AnalysisDocument9 pagesPower Quality AnalysisJOSEPH ANTHONY VINCE MOICONo ratings yet

- Rwservlet (1personal Development)Document1 pageRwservlet (1personal Development)MuhammedSohelNo ratings yet

- CA LBP113w 913w MF113w 913w 2pp Brochure 13sept v3Document2 pagesCA LBP113w 913w MF113w 913w 2pp Brochure 13sept v3dhirajkumar_1No ratings yet

- Gymnopedie No1Document2 pagesGymnopedie No1Chris SeguinNo ratings yet

- CXD5602GG Technical ManualDocument52 pagesCXD5602GG Technical ManualAlex SmirnoffNo ratings yet

- 7mbr35u4p120 50Document1 page7mbr35u4p120 50LITMAS TECHNOLOGYNo ratings yet

- Actix CellrefsDocument24 pagesActix Cellrefsmoj900No ratings yet

- 9A15401 Operating SystemsDocument4 pages9A15401 Operating SystemssivabharathamurthyNo ratings yet

- UJVS 2 Brochure WEB LowRes en 201906 PDFDocument9 pagesUJVS 2 Brochure WEB LowRes en 201906 PDFMukarram Ali KhanNo ratings yet

- Section III: Symmetrical Fault in A Power System: Chapter 6: Short Circuit Studies - Symmetrical FaultsDocument3 pagesSection III: Symmetrical Fault in A Power System: Chapter 6: Short Circuit Studies - Symmetrical FaultsMichele OconnorNo ratings yet