Professional Documents

Culture Documents

ESD 정의 QRT

ESD 정의 QRT

Uploaded by

최대성Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ESD 정의 QRT

ESD 정의 QRT

Uploaded by

최대성Copyright:

Available Formats

World Best Reliability & Failure Analysis Company

Electrostatic Discharge 개요

큐알티반도체

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

• Electrostatic Discharge

• ESD model and Test mode

• LATCH-UP

• LATCH-UP Test 방법

• JEDEC & AEC Q-100 ESD Latch-up 비교

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

What is ESD ?

• Electrostatic discharge (ESD)

• 대전된 물체의 전위가 다른 물체와 접촉하여 짧은 순간에

전하의 이동이 발생하는 것.

• 접지 체와의 접촉으로 인하여 대전 물체가 가진 에너지가

순간적으로 방출되는 현상.

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

ESD Model

• Human Body Model (HBM)

• Machine Model (MM)

• Charged Device Model (CDM)

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

ESD Model

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

HBM Model

• Test standard : JESD22-A114F / AEC-Q100

charged person(사람)이 device와 접촉하면서 발생하는

정전기에 대한 저항성 평가. C=100pF, R=1.5kΩ

R

HV DUT

Supply

C

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

MM Model

• Test standard : JESD22-A115A / AEC-Q100

charged equipment(장비)가 device와 접촉하면서 발생하는

정전기에 대한 저항성 평가. C=200pF, R=0Ω

R

HV DUT

Supply

C

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

ESD Testing Mode

• VDD (Power) Mode : VDD Pin을 GND 化하고 Others Pin Zapping.

VDD VDD

V 0V

0V

-V

VSS VSS

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

• VSS Mode : VSS Pin을 GND 化하고 Others Pin Zapping.

VDD VDD

0V V

0V

-V

VSS VSS

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

• Non-power Pin (IO) Mode : Power & VSS Pin을 제외한

Non-power (IO) pin을 GND 化하고

Test 하고자 하는 1개의 I/O pin을 Zapping.

VDD VDD

V 0V

0V -V

VSS VSS

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

CDM Model

• Test standard : JESD22-C101F / AEC-Q100

• charged device가 metallic GND와 접촉하면서 짧은 시간 안에

device에서 GND로 discharge 하면서 발생하는 정전기에 대한

저항성 평가.

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

Field Induced (JESD22-C101F / AEC-Q100)

-Field charged plate의 전위를 높여 제품을 Charge 시키는 방법.

Field Induced Method

1Ω

Upper Ground plane

Discharge Probe

Insulating Fixture

containing Field

Charging electrode

EHT

☞ 금속 전극이 Device Package의 표면에 접촉하는 방법을 이용한 것으로 금속전극에

전압을 인가하고, 측정단자는 접지시켜 방전 경로를 형성시켜서 Device의 한계량을

평가하는 방법.

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

Direct charged (AEC-Q100)

-Pin (VSS 또는 Power)을 통하여 Charge 시킨 후 Others pin으로 Discharge.

Direct Charge Method

1Ω

Upper Ground plane

EHT charge Probe Discharge Probe

☞ Device Pin을 통해 단자를 접촉시켜 전압을 인가한 후 접지된 측정단자로 방전 경로를

형성시켜 Device의 한계를 평가하는 방법.

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

LATCH-UP ?

• CMOS 구조에서 외부의 전압 변동이나, 전기적 잡음 등으로

기생 bipolar Tr이 Turn on되어 소자의 동작을 방해 또는 파괴시키는 현상.

Vin

Vdd

Vout +

①

Vss

P+ N+ N+ P+ P+ N+

Rpw ②

⑤ R-n sub

Tr2 Tr4 Tr1 Tr3

③

P -Well

⑥

④

N -Well

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

I-Test

Test standard : JESD 78B / AEC-Q100

- Current Injection mode

Trigger Source Vsupply

+ - + -

Positive + 100 mA

Trigger Test Conditions

Test terminal Negative - 100 mA

VDD

The output terminal

Connected to the input

Is opened

Terminal the power supply

If absolute Inom≤25 mA, then absoulute Inom+10 mA is used

Or the GND Terminal

GND or

If absolute Inom>25 mA, then > 1.4 x absoulete Inom is used

Isupply Measurement

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

Vsupply over voltage test

Test standard : JESD 78B / AEC-Q100

- Voltage Injection mode

Vsupply(1.5 X max. Vsupply)

+ -

Trigger Test Conditions Positive 1.5 X max Vsupply

Connected to the input VDD The output terminal

Terminal the power supply Is opened

Or the GND Terminal If absolute Inom≤25 mA, then absoulute Inom+10 mA is used

or

GND

If absolute Inom>25 mA, then > 1.4 x absoulete Inom is used

Isupply Measurement

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

JEDEC & AEC Q-100 ESD Latch-up 비교

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

HUMAN BODY MODEL

Standard JEDEC AEC-Q-100

EOS/ESD Assoc STM5.

규격 JEDEC22-A114-F

EIA/JESD22-F114

Sample size 3 3

No of Zaps 1 positive &1 negative 1 or 3 positive & 1 or 3 negative

Pulse Interval ≥ 0.1s ≥ 0.5 s

Pin group

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

HUMAN BODY MODEL _ Classification

JEDEC AEC-Q-100

Component Class. Maximum Voltage

CLASS 0 ≤ 250V

CLASS 1A 250 to < 500V

CLASS 1B 500 to < 1000V

CLASS 1C 1000 to < 2000V

CLASS 2 2000 to <4000V

CLASS 3A 4000 to < 8000V

CLASS 3B > 8000V

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

MACHINE MODEL

Standard JEDEC AEC-Q-100

EOS/ESD Assoc STM5.

참고 규격 JEDEC22-A114-A

EIA/JESD22-F114

Sample size 3 3

No of Zaps 1 positive &1 negative 3 positive & 3 negative

Pulse Interval ≥ 0.5 s ≥ 1.0 s

Pin group

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

MACHINE MODEL _ Classification

JEDEC AEC-Q-100

Component Class. Maximum Voltage

CLASS A < 200V

CLASS B 200 to < 400V

CLASS C ≥ 400V

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

CHARGED DEVICE MODEL

Standard JEDEC AEC Q-100

EOS/ESD Assoc STM5.

참고규격 JEDEC22-A114-E

EIA/JESD22-D114

Sample size 3 3

No of Zaps 3 positive &3 negative 3 positive & 3 negative

Field-Induced Field-Induced Charge or Direct Charge

Charged

(Charge Cover : FR4) (Charge Cover : 130 Microns thick )

Test Pins All pins All pins

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

CARGED DEVICE MODEL _ Classification

JEDEC AEC-Q-100

Component Class. Maximum Voltage

CLASS Ⅰ < 200V

CLASS Ⅱ 200 to < 500V

CLASS Ⅲ 500 to 1000V

CLASS Ⅳ ≥ 1000V

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

LATCH-UP TEST

Standard JEDEC AEC-Q-100

참고규격 JEDEC 78B JEDEC 78B

Sample size 6 6

Test Temperature

Class Ⅰ or Class Ⅱ Class Ⅱ

Class

I-Test and Vsupply over voltage Test E-Test or I-Test

Test Matrix

Reliability Engineering Team

World Best Reliability & Failure Analysis Company

ESD is important

• Distribution of failure modes in silicon ICs

Reliability Engineering Team

You might also like

- Routine MCCB Test ReportDocument1 pageRoutine MCCB Test ReportYousif_AbdalhalimNo ratings yet

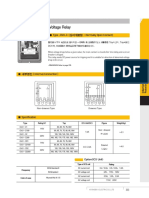

- Kasys Relay Socket - KoreaDocument44 pagesKasys Relay Socket - Koreatuanvutt0% (1)

- 사용설명서 배전반용디지털집합계기 (KDX-300) 광성계측기 (상세)Document28 pages사용설명서 배전반용디지털집합계기 (KDX-300) 광성계측기 (상세)blackhandNo ratings yet

- 계통전압제어Document66 pages계통전압제어KI OHNo ratings yet

- 설계06. DC power supply 설계 및 제작Document17 pages설계06. DC power supply 설계 및 제작댕댕이No ratings yet

- 첨부2 공통통합접지공사 검사업무처리방법 (2018)Document89 pages첨부2 공통통합접지공사 검사업무처리방법 (2018)happyme1791No ratings yet

- Curve จานหมุน Over voltage Type GVO-CD1Document5 pagesCurve จานหมุน Over voltage Type GVO-CD1หนุ่ม วัยทองNo ratings yet

- Sconi 2250 ADocument2 pagesSconi 2250 A반기서No ratings yet

- Battery Charger (Tdc-9030a) ManualDocument15 pagesBattery Charger (Tdc-9030a) Manualauto etrustNo ratings yet

- 실생활 전기전자회로-2주차-입출력장치Document48 pages실생활 전기전자회로-2주차-입출력장치skej sNo ratings yet

- 전자회로실험2Document12 pages전자회로실험2hoopnpNo ratings yet

- ES95400-10 - REV 18 - JX1, RG3 SVM RVC - 정기 신뢰성 성적서 - R00 - 220826Document36 pagesES95400-10 - REV 18 - JX1, RG3 SVM RVC - 정기 신뢰성 성적서 - R00 - 220826GiangNo ratings yet

- 12. 수소연료전지 특성 측정 2Document23 pages12. 수소연료전지 특성 측정 2김찬우No ratings yet

- 5장 1 P n Junctions (2018)Document34 pages5장 1 P n Junctions (2018)장대호No ratings yet

- 3.회로기판고장진단및수리기초 기본교안Document123 pages3.회로기판고장진단및수리기초 기본교안터미네이터No ratings yet

- A-1 - 2 - 3 주요 실험장비 - Measurement of Resistance - 옴의법칙Document23 pagesA-1 - 2 - 3 주요 실험장비 - Measurement of Resistance - 옴의법칙이지훈No ratings yet

- 전자회로의 기초Document44 pages전자회로의 기초지용No ratings yet

- 전자회로의 기초Document44 pages전자회로의 기초박서희No ratings yet

- SSU PE Ch. 4-1Document25 pagesSSU PE Ch. 4-1김현우No ratings yet

- Curve จานหมุน Under Voltage Type GVU-CD1Document4 pagesCurve จานหมุน Under Voltage Type GVU-CD1หนุ่ม วัยทองNo ratings yet

- 공통,통합접지 관련자료Document42 pages공통,통합접지 관련자료wowkoreansNo ratings yet

- (참고) 태양광발전설비 DC 지락차단장치 관련 업무처리방법Document9 pages(참고) 태양광발전설비 DC 지락차단장치 관련 업무처리방법붐비치훈No ratings yet

- 5. 첨단초음파탐상규격Document40 pages5. 첨단초음파탐상규격Tĩnh Hồ TrungNo ratings yet

- 세기전자정비메뉴얼 (구형) 노랑색Document28 pages세기전자정비메뉴얼 (구형) 노랑색최영진No ratings yet

- 서지보호기 spd k 1107Document40 pages서지보호기 spd k 1107조성철No ratings yet

- E50S Cat Kor 160408Document3 pagesE50S Cat Kor 160408머신비전No ratings yet

- Sconi SL DSCDocument3 pagesSconi SL DSCfarscapefeatNo ratings yet

- 고전압 기기의 공간 거리 및 연면 거리의 이해Document30 pages고전압 기기의 공간 거리 및 연면 거리의 이해이수영No ratings yet

- ASTM D6425 Measuring Friction and Wear Properties of Extreme Pressure - EP Lubricating Oils Using SRV Test Machine 한글Document10 pagesASTM D6425 Measuring Friction and Wear Properties of Extreme Pressure - EP Lubricating Oils Using SRV Test Machine 한글김인식No ratings yet

- 1-6까지 240125 162210Document6 pages1-6까지 240125 162210kt42884932No ratings yet

- 실험 2 중첩의 원리와 다이오드의 특성 결과Document6 pages실험 2 중첩의 원리와 다이오드의 특성 결과parkkiyoonNo ratings yet

- MSExp1 02Document18 pagesMSExp1 02이재훈No ratings yet

- 6장 중성점 접지 방식과 유도 장해Document23 pages6장 중성점 접지 방식과 유도 장해295terranNo ratings yet

- 6장 중성점 접지 방식과 유도 장해Document23 pages6장 중성점 접지 방식과 유도 장해295terranNo ratings yet

- SCN SL PMC (New)Document2 pagesSCN SL PMC (New)반기서No ratings yet

- (2022) E07 스피커 구동용 Power Amp 이해Document23 pages(2022) E07 스피커 구동용 Power Amp 이해김지수No ratings yet

- YVC-02 (ÀÚ ¿Àü Ð Á ÀýÀåÄ¡)Document16 pagesYVC-02 (ÀÚ ¿Àü Ð Á ÀýÀåÄ¡)hpiNo ratings yet

- A Study On The Generation of Stable Negative Voltage For IT EquipmentsDocument6 pagesA Study On The Generation of Stable Negative Voltage For IT Equipmentswoojoo1324No ratings yet

- 가상공학실험2 - 정승원 - 9주차 - DC Circuit - 최종 - WorksheetDocument3 pages가상공학실험2 - 정승원 - 9주차 - DC Circuit - 최종 - Worksheetdo hyun seoNo ratings yet

- 01 Varistor KorDocument29 pages01 Varistor Kor이태규No ratings yet

- Test Report - KRN50-1000-00 - RD07Document1 pageTest Report - KRN50-1000-00 - RD07tummalapallimanikanta99No ratings yet

- Truyen Tai DienDocument19 pagesTruyen Tai DienVũ MạnhNo ratings yet

- 4 피복아크용접+장비준비Document100 pages4 피복아크용접+장비준비yoonchankim0911No ratings yet

- _XGB-20_ XBO_DA02A_Installation Guide_V4.5Document2 pages_XGB-20_ XBO_DA02A_Installation Guide_V4.5sklee0730No ratings yet

- 17-Optical Detectors and DisplaysDocument33 pages17-Optical Detectors and DisplaysagushattaNo ratings yet

- 하중-저항계수설계법에의한 강교량의 설계Document40 pages하중-저항계수설계법에의한 강교량의 설계Junwhan KimNo ratings yet

- =4. 규격평가계획서 (DC power supply)Document2 pages=4. 규격평가계획서 (DC power supply)eng pebNo ratings yet

- Chapter5 v3 PDFDocument40 pagesChapter5 v3 PDFseojusangNo ratings yet

- Shinhanelec 22977 PgyrrpDocument7 pagesShinhanelec 22977 PgyrrpLei ZengrongNo ratings yet

- VS (Ver 4.3) (021-040)Document20 pagesVS (Ver 4.3) (021-040)NikoNo ratings yet

- Cable Supervision CS-08TDocument11 pagesCable Supervision CS-08Tdonald33No ratings yet

- MS940-01K_연소성시험 (전장부품)Document9 pagesMS940-01K_연소성시험 (전장부품)01028536351hNo ratings yet

- sPS-1000 Guide R2 0Document2 pagessPS-1000 Guide R2 0embeddsy0No ratings yet

- (XGB-7) XBF - AD04A, AD04D, AD08A - Installation Guide - V4.3Document2 pages(XGB-7) XBF - AD04A, AD04D, AD08A - Installation Guide - V4.3phildec73000No ratings yet

- 정류기 운영 Manual - - REV01Document24 pages정류기 운영 Manual - - REV01Justice KNo ratings yet

- UntitledDocument60 pagesUntitled구서경No ratings yet

- 2022년도-2학기-임베디드시스템 08 4주차 (2) 디지털입출력Document27 pages2022년도-2학기-임베디드시스템 08 4주차 (2) 디지털입출력Long PhamNo ratings yet

- 실생활 전기전자회로-3주차-자동스위치Document40 pages실생활 전기전자회로-3주차-자동스위치skej sNo ratings yet

- 2강 연산증폭기 특성 (202403)Document33 pages2강 연산증폭기 특성 (202403)aa aNo ratings yet