Professional Documents

Culture Documents

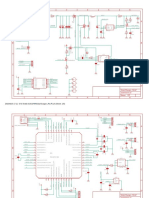

T5L典型应用原理图(2022 01 06)

T5L典型应用原理图(2022 01 06)

Uploaded by

ice.hanbingOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

T5L典型应用原理图(2022 01 06)

T5L典型应用原理图(2022 01 06)

Uploaded by

ice.hanbingCopyright:

Available Formats

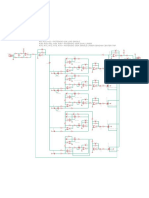

1 2 3 4 5 6 7 8

RX2

TX2

RX4

TX4

LED BL R22

MUSIC SPEAKER

100K

R7

R6

R5

R4

R3

R2

R1

R0

G7

G6

G5

G4

G3

G2

G1

G0

<=1.5W 5V 33uH SD_CLK

<=2.5W 5V 22uH Speaker Output

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

+5V C37 IC6

99

98

97

>2.5W 5V 10uH 104 NS4150B

1 8

EN OUT+

33uH

C5 C23

VIO

VIO

VIO

TX2/04

CRX/03

R7/67

R6/66

R5/65

R4/64

R3/63

R2/62

R1/61

R0/60

RX5

RX4

GND

RX2/05

CTX/02

TR5/01

TR4/00

VDD

VDD

G7/57

G6/56

G5/55

G4/54

G3/53

G2/52

G1/51

G0/50

VDD

TX5

TX4

R9

L1

470P 105 2 7

10R BP GND

M2 C20

R23 47K

96 B7 3404 3 6 470p//106

B7/47 IN+ VCC

D 1 95 B6 LED+ +5V D

TX3/06 B6/46 R24 47K

2 94 B5 C33 4 5

RX3/07 B5/45 IN- OUT-

93 B4 PWMI D1 223

8R 3W

B4/44 R21 10R

SPK1

3 92 B3 SS14 Z1

VDD B3/43 C35 R25

470P//106C

4 91 B2 13V

VIO B2/42 223 2.2K

90 B1 SPK C21

B1/41

5

P10

T5L B0/40

89 B0

C36

470p

C3

6

P11 R7 104//470p

7 88

P12 VIO 100R

8 87 IF_0.4 LED-

P13 VDD

ILED=400/R8 mA

9 Max HVGA difference of Chip Apps

P14

10 86 VS

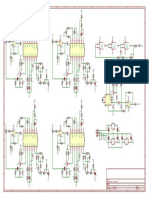

P15 IC Bit color TA Mode DGUS II Mode VS/37

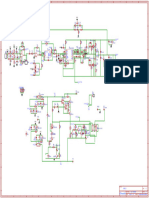

11 85 HS LCD data interface

P16 HS/36 R8 R4 10K

12 T5L0 18bit 1024*768 854*480 84 DE C4

P17 CPU_OS DE/35 RGB LCD INTERFACE 10R

83 PCLK 103 C11

T5L1 24bit 1366*768 720*720 PCK/34 R12

13 82 470p//106

VDD 33 22K

14 T5L2 24bit 1920*1080 1366*768 81 CS_C

VIO 32

80 CS_B

31

15 PS:DGUS II T5L1 MB not exceed 512*1024 79 DW3 DW2

VGL

P20 CKO/30

16 6.8V 16V

P21

17 78

P22 VIO

18 PACKAGE:ELQFP128 77 IC2

P23 VDD

19 74HC138 Multi SPI Flash C13

VGH

P24 R3 10K R10

20 VDD=1.25V T5L1 76 TPX0 +3.3 CS_A 1 16 +3.3 470p//475

P25 X0/27 A VCC 470R

21 VDD=1.20V T5L2/T5L0 75 TPY0 CS_B 2 15 CS0 16MB

P26 Y0/26 B Y0

22 74 TPX1 CS_C 3 14 CS1 32MB

P27 VDDPLL=VDD X1/25 C Y1

73 TPY1 4 13

Y1/24 R19 10K E1 Y2 D2

JTAG Debug Select: 23 VIO=3.3V 72 SPI_CK 5 12 R15

C VDD SCK/23 R13 10K E2 Y3 4148 C

24 AVDD=3.3V 71 CS_A +3.3 6 11 1K

0=GUI 1=OS VIO SCS/22 E3 Y4

VREF=3.3V CPU_GUI 70 SD_CMD +3.3 7 10 D6

CMD/21 Y7 Y5

25 69 SD_CLK 8 9 CS6 4148

P30/X0 CLK/20 R2 4.7K GND Y6 D7

JP1 26

P31/X1 4148

JUMPER 27 68 112MB

P32 VIO Used in add Flash !

28 67 C14

P33 VDD C12

29 103

GND 103

ON:JTAG GUI

OFF:JTAG OS

30 66 DATA3 +3.3 +3.3

GND SD3/17

31 65 DATA2 5V IO to 3.3V IO 3.3V T5L TXD to 3.3V TXD

1

GND SD2/16 D4

32 470p

OS/UI R11 R40 470p//106C 4148

4.7K 22K

VDDPLL

D3 C16

TMS/00

TDO/03

PW0/10

PW1/11

PW2/12

PW3/13

TCK/01

SD0/14

SD1/15

C19

JTAGS

TDI/02

AGND

AVDD

XOUT

ADC0

ADC1

ADC2

ADC3

ADC4

ADC5

ADC6

ADC7

VREF

SS14 AVDD

VDD

/RST

FRX

FTX

RX1

TX1

XIN

VIO

DIN RXD? DOUT TXD?

R28 AVDD=10.3V R30

10R 12K

C24 470p

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

R26

10K R35 R29

4

XT1

TCONSCL

TCONSDA

DATA0

DATA1

+5V

T5L1:2.2K//2.2K

TCONCS

/RST

PWMI

JTAGS

SPK

T5L2/L0=1.0K 1K

IF_0.4

+3.3 +1.2 +1.2

TDO

VOUT

FB

SW

R1

ADX0

ADY0

ADX1

ADY1

C41 C40 11.0592MHz C25 106 L3

4.7K

4

C1 C2

R5 4.7K

R6 4.7K

+3.3

470P//105

470P//105

22pJ 22pJ

1.2V Core 10uH IC4

R34

VIN

FB0.6

1K

TLV61046A

GND

VIN

EN

B IC5 B

TLV62568

JTAG PRG

+3.3

+5V

TCONCS C9 C28

GND

3

CS_A @ only 1 FLASH

SW

470P//105

EN

TCONSCL T5L0 Min60uF /RST

TCONSDA 3 CS0 1 8 +3.3 C18 LCD Bias

Power On Reset /CS VCC T5L1,T5L2 Min 40uF

TDO SGM809S +5V

R32

1 2 DATA1 2 7 DATA3

3

IO1 IO3 10K L2

JTAGS +5V 470p//106

R14 2.2uH

DATA2 3 6 SPI_CK +1.2

4.7K IO2 SCK

JTAG Interface

IC7

4 5 DATA0 C26 C31

GND IO0 SGM2019-33

226*3

C10 470p 103

C27

C28

470p

/RST

470p SPI Nor Flash 4 3

IC3 BP EN

GD/FM/BY/XTX25Q32/64/128 R33

10R

R39 2

3.3K GND

SD/SDHC C6 103

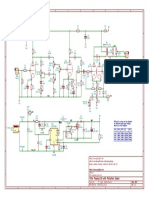

R38

CTP

220K 100K

R41 +3.3 5 1 +5V

DET VOUT VIN

TPX0

/RST

DATA1 Z6 C29

104

DAT1 Z2 5.1V

330K

5RTP 5.1V 4RTP 470p//226//226

R20

DATA0 C7 103 TPY0

DAT0 Z7 SCL 10R

TPY1 TPX0 ADX0 +5V

RD 5.1V X

C34

R42 220K

470p//106

R37

GND 3.3V IO

TPX1 C38 470P TPX1

RU /INT

SD_CLK TPY0 ADY0 D5

C32

CLK R27 100K Y

A ADX0 Z3 5.1V 4148 A

C39

22p

TP BUZZ

+3.3 TPY1

VCC SDA

TPY0 Z8 TPX1 ADX1 C8 103 M4

LU X

SD_CMD 5.1V 3404

CMD

TPX0 Title

LD Z9 R27*

DATA3 TPY1 ADY1 T5L UI TA&DGUS2

DAT3 5.1V Y Z4 5.1V 4.7K

+3.3 SPK

DATA2 Z6 C15 103 BUZZ Size Number Revision

DAT2 CTP Interface

5.1V

4RTP Interface Buzzer A3

SD/SDHC 5RTP Interface

Date: 6-Jan-2022 Sheet of

Z5 5.1V

File: F:\硬件研 发组管理\钉钉群 文件\PCB标准化 相关文件

Drawn By: \T5L原理图 \DEMO.ddb

1 2 3 4 5 6 7 8

You might also like

- The Hyper Accelerated Dragon - Extended - IM Raja PanjwaniDocument540 pagesThe Hyper Accelerated Dragon - Extended - IM Raja PanjwaniAlexis V.100% (2)

- 2kw Power Amplifier PDFDocument1 page2kw Power Amplifier PDFYuda Aditama100% (1)

- Welding Booth Layout DrawingDocument1 pageWelding Booth Layout DrawingJavier GutierrezNo ratings yet

- Pmodstep SCHDocument1 pagePmodstep SCHswati sakhareNo ratings yet

- C26 47nF/50V: Tc1010 Bloq A CobrarDocument1 pageC26 47nF/50V: Tc1010 Bloq A CobrarOsvaldo SantosNo ratings yet

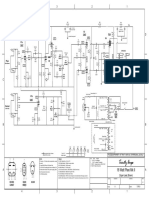

- Service Information Service Information: LaneyDocument5 pagesService Information Service Information: LaneyGladson GoesNo ratings yet

- Epq1200 PDFDocument18 pagesEpq1200 PDFNanang RachmanNo ratings yet

- Title: PDX RX Block - Pi Pico Based DIGITAL MODES HF TransceiverDocument1 pageTitle: PDX RX Block - Pi Pico Based DIGITAL MODES HF TransceiverDhiru Kholia100% (2)

- AH200 SchematicsDocument4 pagesAH200 SchematicsGio HernandezNo ratings yet

- Voxman Pa5000 SCHDocument1 pageVoxman Pa5000 SCHlaboratorium rsb100% (1)

- AMIS60 Power AmpDocument1 pageAMIS60 Power AmparcocerNo ratings yet

- Dummy Load SCHDocument1 pageDummy Load SCHRemiFlores100% (1)

- Schematic - GC-73 EQDocument3 pagesSchematic - GC-73 EQpitiligaNo ratings yet

- Schematic DiagramDocument1 pageSchematic Diagrambakadesu senpaitachiNo ratings yet

- VCC VCC VCC VCC: RA1/ Adc1 RA3/ Adc3 RA5/ Adc4Document1 pageVCC VCC VCC VCC: RA1/ Adc1 RA3/ Adc3 RA5/ Adc4Ankur KunduNo ratings yet

- CA9 SchematicDocument1 pageCA9 SchematiccamachoconeoroguelioNo ratings yet

- Práctica Semana 3Document1 pagePráctica Semana 3Andrey Vargas MoralesNo ratings yet

- Parametrix EqualizerDocument1 pageParametrix EqualizerSegaNo ratings yet

- PCB0052 IHM Control 200W Rev02 EsquemáticoDocument2 pagesPCB0052 IHM Control 200W Rev02 EsquemáticojosemarjuniorNo ratings yet

- Esquema Sub InealDocument4 pagesEsquema Sub Inealtesye fofrNo ratings yet

- Oneal Opsb2500, Opsb2800Document4 pagesOneal Opsb2500, Opsb2800Marcos Lima100% (2)

- Title:: File: Function Generator - SCH SheetDocument1 pageTitle:: File: Function Generator - SCH SheetMochammad PraditiaNo ratings yet

- DC12V Ac127v 400WDocument1 pageDC12V Ac127v 400WWalles PereiraNo ratings yet

- Schematic Leach Amp 700W 2023-10-06Document1 pageSchematic Leach Amp 700W 2023-10-06Francisco MadridNo ratings yet

- Ibanez Ph99 SchematicDocument1 pageIbanez Ph99 SchematicOwen KalauNo ratings yet

- Keith Rider R4 Oz13321 VectorDocument1 pageKeith Rider R4 Oz13321 Vectoradd2mixNo ratings yet

- 2 Way Crossover 24 DB-octaveDocument1 page2 Way Crossover 24 DB-octaveMamad SoheeNo ratings yet

- Trinity 18watt TMB Schematic v12Document1 pageTrinity 18watt TMB Schematic v12Fabio LimaNo ratings yet

- G5 PreampDocument1 pageG5 PreampLexallNo ratings yet

- TDS3000 LED BacklightDocument1 pageTDS3000 LED BacklightGaetan BernierNo ratings yet

- Schematic Tpa3116d2-Xh-M543 Sheet 1 20191123193718Document1 pageSchematic Tpa3116d2-Xh-M543 Sheet 1 20191123193718dougftvc100% (2)

- Modelos AntigosDocument9 pagesModelos AntigosGabriel de LimaNo ratings yet

- PS800ServiceManual PDFDocument35 pagesPS800ServiceManual PDFbruce hu100% (1)

- Group2 Cognitive Survey Summary FinalDocument5 pagesGroup2 Cognitive Survey Summary FinalJeanlyNo ratings yet

- Ref 1 Out 6 In-5 GND 2 In+ 4 VCC 3 Ref 1 Out 6 in - 5 GND 2 In+ 4 VCC 3Document5 pagesRef 1 Out 6 In-5 GND 2 In+ 4 VCC 3 Ref 1 Out 6 in - 5 GND 2 In+ 4 VCC 3Bryan Felton100% (1)

- Schematic - IRS UcD - 2022-06-06Document1 pageSchematic - IRS UcD - 2022-06-06vantri27082004No ratings yet

- Trinity 18watt Plexi MK - II Schematic v4Document1 pageTrinity 18watt Plexi MK - II Schematic v4Gregoria Cortes GarciaNo ratings yet

- Crate BT15 - PWA Bass Amplifier PCB Schematics (848SCH - A)Document2 pagesCrate BT15 - PWA Bass Amplifier PCB Schematics (848SCH - A)Guim EloyNo ratings yet

- Limit Compr 110 Schematic 01Document1 pageLimit Compr 110 Schematic 01samoNo ratings yet

- 2kw Power Amplifier PDFDocument1 page2kw Power Amplifier PDFYuda AditamaNo ratings yet

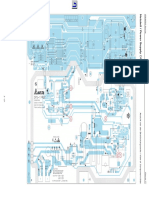

- Benq Fp222w Power Supply SCHDocument5 pagesBenq Fp222w Power Supply SCHmsicoie1851No ratings yet

- 2kw Power Amplifier PDFDocument1 page2kw Power Amplifier PDFYuda Aditama100% (1)

- Esquema Eletronico Ups East Bivolt - 600 - 1200va-Parte2Document1 pageEsquema Eletronico Ups East Bivolt - 600 - 1200va-Parte2Armandinho CaveroNo ratings yet

- Ac Amp01Document1 pageAc Amp01twifosNo ratings yet

- Jumper: " Ver Tabela "Document1 pageJumper: " Ver Tabela "Gabriel de LimaNo ratings yet

- IPR RELAY LED DimmerDocument1 pageIPR RELAY LED Dimmermitchel taylorNo ratings yet

- رافع 1000 PDFDocument1 pageرافع 1000 PDFابو جعفر الحمصيNo ratings yet

- DiagramaDocument9 pagesDiagramaCarlos Cajal100% (1)

- F1 Diagram CurcuitDocument1 pageF1 Diagram CurcuitDaniel Fernando Sotelo LagosNo ratings yet

- Ibanez rc99 PDFDocument1 pageIbanez rc99 PDFdNo ratings yet

- RaduinoDocument1 pageRaduinoCO6NMP100% (2)

- Grundig-Beko Delta dps-174bp PsuDocument3 pagesGrundig-Beko Delta dps-174bp PsuMy USERNAME100% (1)

- Alto+Ps5ha Amp+DiagramDocument1 pageAlto+Ps5ha Amp+Diagramangel miguel rodriguez morales100% (1)

- DEADplate 5 To Nine Issue 1 2Document3 pagesDEADplate 5 To Nine Issue 1 2Alberto DesechableNo ratings yet

- Input Jack PCB To Power PCBDocument2 pagesInput Jack PCB To Power PCBPablo Rodrigo Nazario Perez100% (2)

- Ss023a x10 Schematic Diagram2Document1 pageSs023a x10 Schematic Diagram2cattia0% (1)

- From Pre: Potência de Saida @ (1Khz) (@1Khz) Lim. 30V em 4R 225W Musical 42V em 4R 440WDocument1 pageFrom Pre: Potência de Saida @ (1Khz) (@1Khz) Lim. 30V em 4R 225W Musical 42V em 4R 440WfranciscoNo ratings yet

- Omnitronic Edp-700 Class DDocument3 pagesOmnitronic Edp-700 Class Dosman saraçNo ratings yet

- Simple CFA BJT OITPC FullDocument4 pagesSimple CFA BJT OITPC Fulllungpro01No ratings yet

- Autoclave Uc Pic Lib I/O: ItibbDocument1 pageAutoclave Uc Pic Lib I/O: ItibbLuis Elizee Blanco100% (1)

- The Rough Guide to Beijing (Travel Guide eBook)From EverandThe Rough Guide to Beijing (Travel Guide eBook)Rating: 2 out of 5 stars2/5 (1)

- Unit 1 OOSD NotesDocument18 pagesUnit 1 OOSD NotesAkshat Kumar100% (1)

- Win With The Caro-Kann (Sverre's Chess Openings)Document738 pagesWin With The Caro-Kann (Sverre's Chess Openings)Valentin dutillieux100% (5)

- Working Drawing PortfolioDocument15 pagesWorking Drawing PortfolioDimple PrasadNo ratings yet

- NAF Rules For Tournaments 2022Document2 pagesNAF Rules For Tournaments 2022juan david lópez montalegreNo ratings yet

- Summer Samba BB Clarinet FluteDocument2 pagesSummer Samba BB Clarinet FluteRaimon PouNo ratings yet

- Visualwize 20 Level 2 Exercise 140Document282 pagesVisualwize 20 Level 2 Exercise 140surya vevoNo ratings yet

- HISTORY and How To Play ScrabbleDocument4 pagesHISTORY and How To Play ScrabblexiaNo ratings yet

- Edward Winter - Capablanca On San Sebastián, 1912Document3 pagesEdward Winter - Capablanca On San Sebastián, 1912tuputhomas100% (1)

- Kangaroo Math TestDocument8 pagesKangaroo Math TestLe Linh100% (1)

- Mission B39 - Neverending Night (GH)Document1 pageMission B39 - Neverending Night (GH)Homar SánchezNo ratings yet

- Ramakrishnan - Mate in One Vol.2Document201 pagesRamakrishnan - Mate in One Vol.2gaurav_singh_md100% (2)

- B01 Vitruvius 1.12cDocument1 pageB01 Vitruvius 1.12cblitzkrieg76No ratings yet

- Shg4301a-101h DLBB449Document1 pageShg4301a-101h DLBB449LuisMiguelCalvo100% (1)

- Everrain ExpandedRoundSequenceDocument1 pageEverrain ExpandedRoundSequencerichard leonardoNo ratings yet

- The Livonian Knight Selected Games of Alvis VitolinsDocument215 pagesThe Livonian Knight Selected Games of Alvis VitolinsVijay ManjrekarNo ratings yet

- Potencia: Vista Inferior Vista Frontal Vista SupeirorDocument1 pagePotencia: Vista Inferior Vista Frontal Vista SupeirorcbsomtecladosNo ratings yet

- Catan - Base - Rules - 2020 - 200707 2 PDFDocument16 pagesCatan - Base - Rules - 2020 - 200707 2 PDFKevin AguilarNo ratings yet

- Mostra de Advanced DragonDocument19 pagesMostra de Advanced DragonJoao SilvaNo ratings yet

- Mate in Two - Dobrinetsky 1Document58 pagesMate in Two - Dobrinetsky 1darinchy100% (1)

- Games of GeneralDocument3 pagesGames of GeneralFel OfficialNo ratings yet

- LogDocument749 pagesLogTrámites UBNo ratings yet

- Taghdoutelive STB-06-17-2023Document10 pagesTaghdoutelive STB-06-17-2023Ledjon MetiNo ratings yet

- FB Dominion Prosperity Rulebook PDFDocument12 pagesFB Dominion Prosperity Rulebook PDFplayjake18No ratings yet

- 30th WB State Fide Rated Age Gr. Chess Championship-2018 (Open) /if Aicf Registration Due, Can Not Play Starting Rank No. Name Fideid Fed RTG SexDocument3 pages30th WB State Fide Rated Age Gr. Chess Championship-2018 (Open) /if Aicf Registration Due, Can Not Play Starting Rank No. Name Fideid Fed RTG SexRam KNo ratings yet

- PDF The Closed Sicilian CompressDocument20 pagesPDF The Closed Sicilian CompressfdsajçklfasdkjNo ratings yet

- Savage Worlds Character SheetDocument2 pagesSavage Worlds Character Sheetjesse.a.g.ridge790100% (1)

- R Ank & File: Matikozyan Wins Lina Grumette Memorial Day ClassicDocument28 pagesR Ank & File: Matikozyan Wins Lina Grumette Memorial Day ClassicMarlon DominguezNo ratings yet

- The Chigorin Bible - A Classic Defence To Ruy Lopez - Ivan Sokolov & Ivan Salgado LopezDocument551 pagesThe Chigorin Bible - A Classic Defence To Ruy Lopez - Ivan Sokolov & Ivan Salgado LopezSCARly100% (1)