Professional Documents

Culture Documents

Mpes Solved Dec 2017

Mpes Solved Dec 2017

Uploaded by

masterjiynCopyright:

Available Formats

You might also like

- Adam HistoryDocument1,189 pagesAdam HistoryMartim Silva100% (1)

- Microprocessor Lab Viva Questions With AnswerssDocument24 pagesMicroprocessor Lab Viva Questions With AnswerssRahul Kumar100% (2)

- Unit - IiiDocument41 pagesUnit - IiiJit Agg0% (1)

- MCT Unit 2Document26 pagesMCT Unit 2Aravind RajNo ratings yet

- 8085 Is Pronounced AsDocument9 pages8085 Is Pronounced AsArbaaz khan786No ratings yet

- Unit I PDFDocument25 pagesUnit I PDFSomnath2014No ratings yet

- Unit Ii 8085 Micro Processor 8085 Architecture:: ME 6702 Mechatronics Mechanical Engineering 2019-20Document26 pagesUnit Ii 8085 Micro Processor 8085 Architecture:: ME 6702 Mechatronics Mechanical Engineering 2019-20GopinathNo ratings yet

- MPMC Model Exam Answer KeyDocument21 pagesMPMC Model Exam Answer KeyVenkatesan SundaramNo ratings yet

- MICROPORCESSOR 8085 Lab ManualDocument53 pagesMICROPORCESSOR 8085 Lab ManualAjay PatilNo ratings yet

- Micro Processor DineshDocument9 pagesMicro Processor DineshsandyNo ratings yet

- EE6502MPMC1Document31 pagesEE6502MPMC1nirmal_inboxNo ratings yet

- Study of 8085 and Kit STS-85Document10 pagesStudy of 8085 and Kit STS-85Mohammed MansoorNo ratings yet

- Experiment No. 1: Department of Electronics & Comm - EnggDocument7 pagesExperiment No. 1: Department of Electronics & Comm - EnggJaspreet KaurNo ratings yet

- MM Assignmemt 2Document7 pagesMM Assignmemt 2ALL ÎÑ ÔÑÈNo ratings yet

- Syllabus: 8085 ArchitectureDocument25 pagesSyllabus: 8085 Architecturetamilvendhan87No ratings yet

- Micro-Processors 8085: D.Arun KumarDocument52 pagesMicro-Processors 8085: D.Arun Kumarsrihari yandrapragadaNo ratings yet

- MPMC - Unit 1 - 8085 ArchitectureDocument17 pagesMPMC - Unit 1 - 8085 ArchitectureWickNo ratings yet

- 8085 - Short SummaryDocument14 pages8085 - Short SummaryTarunVarmaNo ratings yet

- An Over View of 8085Document12 pagesAn Over View of 8085nskprasad89No ratings yet

- 8085 Architecture & Pin DescriptionFileDocument19 pages8085 Architecture & Pin DescriptionFileKaseya TakahashiNo ratings yet

- 8085 MaterialDocument12 pages8085 MaterialsameerNo ratings yet

- MIC 04 - Case Study One 8085 MPUDocument40 pagesMIC 04 - Case Study One 8085 MPUomar hanyNo ratings yet

- Unit-I: 8-Bit MicroprocessorsDocument55 pagesUnit-I: 8-Bit MicroprocessorsAASTHA KIETNo ratings yet

- MC8085Document7 pagesMC8085Bhavani BhavanNo ratings yet

- EMISY Second Test Exemplary Questions Solved-3Document15 pagesEMISY Second Test Exemplary Questions Solved-3YANG LIUNo ratings yet

- Microprocessor 8085 NotesDocument48 pagesMicroprocessor 8085 NotesDewal ChaturvediNo ratings yet

- MPMC NotesDocument301 pagesMPMC NotesVarinder KumarNo ratings yet

- Microprosser 8085Document15 pagesMicroprosser 8085saigdv1978No ratings yet

- Question Bank 1Document18 pagesQuestion Bank 1heligolwala1No ratings yet

- Microprocessor and Micro ControllerDocument118 pagesMicroprocessor and Micro ControllerShiva ShanNo ratings yet

- Embedded System and IoTDocument9 pagesEmbedded System and IoTNitysNo ratings yet

- Answers of Microprocessor (8085) & Electronics FAQDocument21 pagesAnswers of Microprocessor (8085) & Electronics FAQsoumyadev100% (23)

- Microcontrollers and Systems Lesson3 Microprocessor 8085Document9 pagesMicrocontrollers and Systems Lesson3 Microprocessor 8085Jean de Dieu NGUIMFACK NDONGMONo ratings yet

- Micrprocessor Notes 2023Document18 pagesMicrprocessor Notes 2023GautamNo ratings yet

- 8085 Features, Signal DescriptionDocument13 pages8085 Features, Signal DescriptionRakesh Kumar DNo ratings yet

- An Introduction To INTEL 8085 Microprocessor: By:Ravindra Nadh.V, Assistant Professor, GST, BangaloreDocument35 pagesAn Introduction To INTEL 8085 Microprocessor: By:Ravindra Nadh.V, Assistant Professor, GST, BangaloreVasudev Rao KonjetiNo ratings yet

- EE6502 MPMC Two Marks With AnswerDocument10 pagesEE6502 MPMC Two Marks With Answervlsimani9110100% (1)

- Basic Concepts of MicroprocessorsDocument32 pagesBasic Concepts of MicroprocessorsAakrati SharmaNo ratings yet

- Microprocessor Viva Questions and AnswersDocument17 pagesMicroprocessor Viva Questions and AnswersUtsav Suresh PanchalNo ratings yet

- Questionnaire MICROPROCESSOR PART 1 UNIT 1 and 2Document20 pagesQuestionnaire MICROPROCESSOR PART 1 UNIT 1 and 2aditya2021cs081No ratings yet

- Experiment 1 4 SemesterDocument6 pagesExperiment 1 4 Semesteraman YadavNo ratings yet

- Microprocessors and Its Applications Short AnswersDocument15 pagesMicroprocessors and Its Applications Short AnswersVidya MuthukrishnanNo ratings yet

- MP & MC Micro Doc-20240520-Wa0000Document82 pagesMP & MC Micro Doc-20240520-Wa0000Deba Comedy ClubNo ratings yet

- 8085 Architecture: Control UnitDocument10 pages8085 Architecture: Control UnitsweetmemoriesneverdiNo ratings yet

- 8085 MicroprocessorDocument25 pages8085 Microprocessorprofessor2062No ratings yet

- 8085 MicroprocessorDocument38 pages8085 MicroprocessorPrateek PandeyNo ratings yet

- Lecture1423722820 PDFDocument101 pagesLecture1423722820 PDFdavNo ratings yet

- Microprocessor Lab ManualDocument85 pagesMicroprocessor Lab ManualReddyNo ratings yet

- Viva Questions and Answers in MP Lab - 1Document6 pagesViva Questions and Answers in MP Lab - 1Sai KrishnaNo ratings yet

- 8085 MicroprocessorDocument13 pages8085 MicroprocessorSajid Akram100% (1)

- MP VivaDocument42 pagesMP VivaShubham Benjamin JohnNo ratings yet

- Imp MP QuesDocument24 pagesImp MP QuesbhatiaharryjassiNo ratings yet

- BGK MPMC Unit-3 Q and ADocument21 pagesBGK MPMC Unit-3 Q and AMallesh ArjaNo ratings yet

- ALPQPDocument20 pagesALPQPTanujaramNo ratings yet

- MPMC SougataDocument5 pagesMPMC SougataSherlok HolmesNo ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Security SoftwareDocument149 pagesSecurity SoftwarePumas UnamNo ratings yet

- Characteristics Location Capacity Unit of Transfer Access Method Performance Physical Type Physical Characteristics OrganisationDocument53 pagesCharacteristics Location Capacity Unit of Transfer Access Method Performance Physical Type Physical Characteristics Organisationapi-26594847No ratings yet

- ComputerDocument171 pagesComputerMrdark Warrior100% (1)

- Framework Manager Developer GuideDocument152 pagesFramework Manager Developer GuideMoataz DeiabNo ratings yet

- First Boot LogDocument38 pagesFirst Boot LogEdvin DukaNo ratings yet

- Chapter 3 - Lab Environment SettingsDocument42 pagesChapter 3 - Lab Environment SettingsjamyssonNo ratings yet

- OS Sheet (1) SolutionDocument6 pagesOS Sheet (1) Solutionhussienboss99No ratings yet

- Jtagjet Usb InstallDocument12 pagesJtagjet Usb Installbella_duaneNo ratings yet

- Data Connector Blog 3.0 PDFDocument11 pagesData Connector Blog 3.0 PDFsantoshs2002848No ratings yet

- SAP Inbound IDocDocument16 pagesSAP Inbound IDocBeing Ronnie100% (1)

- Aws Iam PDFDocument26 pagesAws Iam PDFTomi JerNo ratings yet

- Fortios v7.2.5 Release NotesDocument60 pagesFortios v7.2.5 Release NotesKarthickNo ratings yet

- A Day in The Life of Aloha : Back of House Computer (BOH)Document3 pagesA Day in The Life of Aloha : Back of House Computer (BOH)abiiboyoNo ratings yet

- Cambridge IGCSE: Computer Science 0478/21Document16 pagesCambridge IGCSE: Computer Science 0478/21Marvin Bin Abdulaziz AbbilaniNo ratings yet

- DNS Probe Finished Nxdomain ErrorDocument14 pagesDNS Probe Finished Nxdomain Errorjack ryanNo ratings yet

- IndexDocument3 pagesIndexgabrielvasNo ratings yet

- A USB Flash Dri-WPS OfficeDocument3 pagesA USB Flash Dri-WPS Officehanzel lopezNo ratings yet

- Oct00 PDFDocument20 pagesOct00 PDFAnonymous YynGVcqdBMNo ratings yet

- ATCA and MicroATCA GuideDocument60 pagesATCA and MicroATCA Guidedenkins2020100% (1)

- Jax WS PDFDocument19 pagesJax WS PDFLam Le TranNo ratings yet

- Bitdefender AntivirusDocument4 pagesBitdefender AntivirusMohd Jamil PatahNo ratings yet

- Todero"U I Ines: ZX PectrumDocument77 pagesTodero"U I Ines: ZX PectrumEleodor Paul CirlugeaNo ratings yet

- Vmware Data Protection With Hitachi Data Protection Suite: Please Insert Your Hitachi Truenorth Partner Logo HereDocument21 pagesVmware Data Protection With Hitachi Data Protection Suite: Please Insert Your Hitachi Truenorth Partner Logo HereWildan AbdatNo ratings yet

- Student KitDocument38 pagesStudent KitGautam RastogiNo ratings yet

- Microcontroller Experiments Using Vinytics KitDocument3 pagesMicrocontroller Experiments Using Vinytics KitPatel ParthNo ratings yet

- Cctalk44 1aDocument50 pagesCctalk44 1airfanNo ratings yet

- Voice-Actuated, Speaker-Dependent Control System For Hospital BedDocument3 pagesVoice-Actuated, Speaker-Dependent Control System For Hospital BedtamnovNo ratings yet

- "Payroll Management System": Project Report OnDocument16 pages"Payroll Management System": Project Report OnLahiru M SuraweeraNo ratings yet

- G H Raisoni University, AmravatiDocument2 pagesG H Raisoni University, AmravatiVijay GadichaNo ratings yet

Mpes Solved Dec 2017

Mpes Solved Dec 2017

Uploaded by

masterjiynOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Mpes Solved Dec 2017

Mpes Solved Dec 2017

Uploaded by

masterjiynCopyright:

Available Formats

Microprocessor And Embedded Systems (EE309) - Dec 2017

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

PART A, ANSWER ALL QUESTIONS, EACH CARRIES5

MARKS.

1 Explain demultiplexing of Address/Data Bus. (5)

Address and Data will appear on AD0-AD7 lines. When AD lined carry address, ALE will go high

and enables the latch. This will make the latch to conduct and the address will appear across A0-A7.

When there is data in AD lines, then ALE=0, the latch is disabled, there is no output across A0-A7,

and data appears in D0-D7 pins.

2 Write a delay subroutine program in 8085 for 0.4 ms. Assume the clock frequency as 3 MHz.

(5)

Delay Time Td = (T x 14 x n), Where T = 1/(3 MHz), n = count

Thus n = Td/(Tx14) = 0.4ms x 3MHz/(14) = 64d = 40H

MVI C, 40H ; Load count to C register (7T states, 1 time execution)

LOOP DCR C ; Decrement C register (4T, n times execution)

JNZ LOOP ; Loop if C non-zero (10T for [n-1], 7T for once)

3 Differentiate between maskable and non-maskable interrupts and list the interrupt related

instructions. (5)

An interrupt that can be disabled by writing some instruction is known as Maskable Interrupt,

otherwise it is called Non-Maskable Interrupt. TRAP is non maskable interrupt with the highest

priority. Hardware interrupts RST7.5, 6.5, 5.5, INTR are maskable. The SIM instruction is used to

mask or unmask RST hardware interrupts. When executed, the SIM instruction reads the content of

accumulator and accordingly mask or unmask the interrupts.

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

Interrupt Related instructions are,

SIM - Set Interrupt Mask

RIM - Read Interrupt Mask and

RST0 to RST7

4 Difference between Microprocessor and Microcontroller. (5)

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

5 Write an ALP using 8051 to generate a square wave of 50% duty cycle. (5)

ORG 0000H ; Define starting location in memory

START: SETB P1.0 ; Square wave on Port 1, Pin 1 set high=1

MOV R0,#249 ; Set register R0 for time delay

ONE : DJNZ R0,ONE ; ~0.5ms Time delay

CLRB P1.0 ; Square wave on Port 1, Pin 1 set low=0

MOV R1,#249 ; Set register R0 for time delay

TWO : DJNZ R1,TWO ; ~0.5ms Time delay

SJMP START ; Loop to start of program

END ; End of program

6 Explain SFR’s of 8051. (5)

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

7Explain Assembler Directives of 8051. (5)

] i.DB directive is the most widely used data directive in the assembler

It is used to define the 8-bit data

When DB is used to define data, the numbers can be in decimal, binary, hex,

ASCII formats

ii.ORG (origin)

The ORG directive is used to indicate the beginning of the address

The number that comes after ORG can be either in hex and decimal

If the number is not followed by H, it is decimal and the assembler will convert it

to hex

iii.END

This indicates to the assembler the end of the source (asm) file

The END directive is the last line of an 8051 program

Mean that in the code anything after the END directive is ignored by the assembler

iv.EQU (equate)

This is used to define a constant without occupying a memory location

The EQU directive does not set aside storage for a data item but associates a

constant value with a data label

When the label appears in the program, its constant value will be substituted for the

label

8 Explain the function of TMOD and TCON registers of 8051 Microcontroller. (5)

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

PART B Answer any twofull questions, each carries10 marks.

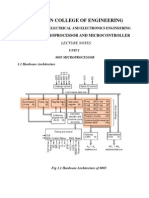

9 Explain the architecture of 8085 microprocessor with the help of a neat functional block

diagram. (10)

It is an 8 bit microprocessor. It is manufactured with N-MOS technology. It has 16 bit address bus and

hence can address upto 216 = 65536 bytes (64KB) memory locations through A 0-A15. The first 8

lines of address bus and 8 lines of databus are multiplexed AD 0 – AD 7. Data bus is a group of 8

lines D 0 – D 7. It supports external interrupt request. A 16 bit program counter (PC). A 16 bit stack

pointer (SP). Six 8-bit general purpose register arranged in pairs: BC, DE, HL. It requires a signal

+5V power supply and operates at 3 MHZ single phase clock.

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

Memory:

Program, data and stack memories occupy the same memory space. The total addressable memory

size is 64 KB. Program memory - program can be located anywhere in memory. Jump, branch and

call instructions use 16-bit addresses, i.e. they can be used to jump/branch anywhere within 64 KB.

All jump/branch instructions use absolute addressing. 8-bit H and 8-bit L registers can be used as one

16-bit HL register pair. When used as a pair the L register contains low-order byte. HL register

usually contains a data pointer used to reference memory addresses. Stack pointer is a 16 bit register.

This register is always decremented/incremented by 2 during push and pop. Program counter is a 16-

bit register.

Registers

Accumulator or A register is an 8-bit register used for arithmetic, logic, I/O and load/store operations.

Flag Register has five 1-bit flags.

Sign - set if the most significant bit of the result is set.

Zero - set if the result is zero.

Auxiliary carry - set if there was a carry out from bit 3 to bit 4 of the result.

Parity - set if the parity (the number of set bits in the result) is even.

Carry - set if there was a carry during addition, or borrow during

subtraction/comparison/rotation.

General Registers :

8-bit B and 8-bit C registers can be used as one 16-bit BC register pair. When used as a pair the C

register contains low-order byte. Some instructions may use BC register as a data pointer. 8-bit D and

8-bit E registers can be used as one 16-bit DE register pair. When used as a pair the E register

contains low-order byte. Some instructions may use DE register as a data pointer.

Interrupts

10

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

The processor has 5 interrupts. They are presented below in the order of their priority (from lowest to

highest): INTR is maskable 8080A compatible interrupt. When the interrupt occurs the processor

fetches from the bus one instruction, usually one of these instructions: One of the 8 RST instructions

(RST0 - RST7). The processor saves current program counter into stack and branches to memory

location N * 8 (where N is a 3-bit number from 0 to 7 supplied with the RST instruction). CALL

instruction (3 byte instruction). The processor calls the subroutine, address of which is specified in the

second and third bytes of the instruction. RST5.5 is a maskable interrupt. When this interrupt is

received the processor saves the contents of the PC register into stack and branches to 2CH

(hexadecimal) address. RST6.5 is a maskable interrupt. When this interrupt is received the processor

saves the contents of the PC register into stack and branches to 34H (hexadecimal) address. RST7.5 is

a maskable interrupt. When this interrupt is received the processor saves the contents of the PC

register into stack and branches to 3CH (hexadecimal) address. TRAP is a non-maskable interrupt.

When this interrupt is received the processor saves the contents of the PC register into stack and

branches to 24H (hexadecimal) address.

RESET IN : When this signal goes low, the program counter (PC) is set to Zero, µp is reset and resets

the interrupt enable and HLDA flip-flops. RESET OUT: This signal indicates that µp is being reset.

This signal can be used to reset other devices. The signal is synchronized to the processor clock and

lasts an integral number of clock periods.

Serial Communication

SID - Serial Input Data Line: The data on this line is loaded into accumulator bit 7 when ever a RIM

instruction is executed. SOD – Serial Output Data Line: The SIM instruction loads the value of bit 7

of the accumulator into SOD latch if bit 6 (SOE) of the accumulator is 1.

DMA Signals

HOLD: Indicates that another master is requesting the use of the address and data buses. The CPU,

upon receiving the hold request, will relinquish the use of the bus as soon as the completion of the

current bus transfer. HLDA: Hold Acknowledge : Indicates that the CPU has received the HOLD

request and that it will relinquish the bus in the next clock cycle.

READY : This signal Synchronizes the fast CPU and the slow memory, peripherals. If READY is

high during a read or write cycle, it indicates that the memory or peripheral is ready to send or receive

data.

Instruction execution in MP-8085

11

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

Architecture of MP-8085

10 Draw and explain the timing diagram of LDAX D. (10)

LDAX D - Load accumulator indirect - The contents of the designated register pair ‘DE’ point to a

memory location. This instruction copies the contents of that memory location into the accumulator.

The contents of either the register pair or the memory location are not altered. The Machine cycles

included are,

i. Opcode fetch to read and decode the opcode from memory

ii. Memory Read to read the contents of address location in DE register pair and to copy it ti

Accumulator register.

Thus the instruction will take 7 T-states to complete execution.

12

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

Fetch Cycle

For fetching a byte, the microprocessor must find out the memory location where it is stored.

Then provide condition (control) for data flow from memory to the microprocessor. The process

of data flow and timing diagram of fetch operation are shown in Figs. The μP fetches opcode of the

instruction from the memory as per the sequence below.

• A low IO/M means microprocessor wants to communicate with memory.

• The μP sends a high on status signal S1 and S0 indicating fetch operation.

• The μP sends 16-bit address. AD bus has address in 1st clock of the 1st machine cycle, T1.

• AD7 to AD0 address is latched in the external latch when ALE = 1.

• AD bus now can carry data.

• In T2, the RD control signal becomes low to enable the memory for read operation.

• The memory places opcode on the AD bus

• The data is placed in the data register (DR) and then it is transferred to IR.

• During T3 the RD signal becomes high and memory is disabled.

• During T4 the opcode is sent for decoding and decoded in T4.

• The execution is also completed in T4 if the instruction is single byte.

Read Cycle

The high order address (A15 -A8) and low order address (AD7 -AD0) are asserted on 1st low going

transition of the clock pulse. The timing diagram for IO/M read are shown . The A15 -A8 remains

valid in T1, T2, and T3 i.e. duration of the bus cycle, but AD7 -AD0 remains valid only in T1. Since it

has to remain valid for the whole bus cycle, it must be saved for its use in the T2 and T3. ALE is

asserted at the beginning of T1 of each bus cycle and is negated towards the end of T1. ALE is active

during T1 only and is used as the clock pulse to latch the address (AD7-AD0) during T1. The RD is

asserted near the beginning of T2. It ends at the end of T3. As soon as the RD becomes active, it

forces the memory or I/O port to assert data. RD becomes inactive towards the end of T3, causing the

port or memory to terminate the data.

11 a) Explain different addressing modes in 8085 with examples. (6)

The process of identifying the operands for a particular instruction can be carried out in several ways.

The various types of addressing modes are as shown below.

i. Immediate Addressing Mode:

In this type of addressing mode the operand is specified within the instruction itself. Consider this

instruction ADI 34H – This instruction adds the immediate data, 34H to the accumulator. 34H is the

13

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

data here. H represents Hexadecimal value and the immediate value is added to the accumulator. In

this case 34H is added to the accumulator. Suppose if accumulator has a value 8H and when this

instruction is executed, 34H is added to the 8H and the result is stored in accumulator. In the above

instruction the operand is specified within instruction itself.

ii. Direct Addressing Mode:

In this mode of addressing, the address of the data (operand) is specified within the instruction.

There is a subtle difference between the direct addressing modes and immediate addressing modes. In

immediate addressing mode the data itself is specified within instruction, but in direct addressing

mode the address of the data is specified in the instruction.

Example:

OUT 10H

LDA 4100H

STA 2000H

iii. Register Addressing Mode:

In this type of addressing mode the instruction specifies the name of the register in which the data is

available and Opcode specifies the name (or) address of the register on which the operation would be

performed.

Example: MOV A, B

Here the Opcode is MOV. If the above instruction is executed, the contents of Register B are moved

to the Register A, which is nothing but the accumulator.

iv. Register Indirect Addressing Mode:

This is indirect way of addressing. In this mode the instruction specifies the name of the register in

which the address of the data is available.

Example:

MOV A, M

SUB M

DCR M

Consider MOV A, M. This instruction will move the contents of memory location, whose address is

in H-L register pair to the accumulator. M represents the address present in the H-L register pair. So

when MOV A, M is executed, the contents of the address specified in H-L register pair are moved to

accumulator.

v. Implicit Addressing Mode:

There are certain instructions in 8085 which does not require the address of the operand to perform

the operation. They operate only upon the contents of accumulator.

Example:

CMA

RAL

RAR

11 b) Explain the terms Machine cycle and T-states. (4)

T-state is one sub-division of an operation performed in one clock cycle. Each clock cycle is called as

T-states. For 3MHz clock, one T state is (1/3MHz), which is 0.33micro seconds.

14

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

Machine cycle is the time required by the microprocessor to complete the operation of accessing the

memory devices or I/O devices. In machine cycle various operations like opcode fetch,

memory read, memory write, I/O read, I/O write are performed.

PART C Answer any two full questions, each carries10 marks.

12 a) Draw the interrupt structure of 8085. (5)

15

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

12 b) Design memory systems to interface 2K ROM and 2K RAM using 2K x 8 bit

memory chips. (5)

2K RAM/ROM Chip requires 8 Data lines (D0 to D7) and 11 Address lines(A0 to A10) to interface

with 8085. Three address lines (A11 to A13) is used as three decoder inputs to the 3 to 8 decoder

74LS138. Remaining two address lines are used to enable the decoder using a NAND gate.

Memory Map of Interfacing

A12 to HEX Address Range of Selected

A0-A3 A4-A7 A8-A11

A15 Address Chip Chip

0000 0000 0000 0000 0000 H Stating Address RAM Chip

(0000H

1111 1111 1110 0000 08FF H Ending Address to

08FFH)

0000 0000 0001 0000 Stating Address ROM Chip

0900 H

(0900H

1111 1111 1111 0000 0FFF H Ending Address to

0FFFH)

0000 0000 0000 1000 1000 H Unused None

1111 1111 1111 1111 FFFF H Unused None

Interfacing diagram

16

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

13 a) Give the current trends and challenges in the field of Embedded Systems. (5)

17

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

13 b) Describe the Embedded System product development model. (5)

18

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

19

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

20

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

21

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

14 a) Explain Assembler, Compiler, Linker and Loader. (5)

22

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

Linker: In high level languages, some built in header files or libraries are stored. These libraries are

predefined and these contain basic functions which are essential for executing the program. These

functions are linked to the libraries by a program called Linker. If linker does not find a library of a

function then it informs to compiler and then compiler generates an error. The compiler automatically

invokes the linker as the last step in compiling a program.Not built in libraries, it also links the user

defined functions to the user defined libraries. Usually a longer program is divided into smaller

subprograms called modules. And these modules must be combined to execute the program. The

process of combining the modules is done by the linker.

Loader: Loader is a program that loads machine codes of a program into the system

memory. In Computing, a loader is the part of an Operating System that is responsible for loading

programs. It is one of the essential stages in the process of starting a program. Because it places

programs into memory and prepares them for execution. Loading a program involves reading the

contents of executable file into memory. Once loading is complete, the operating system starts the

program by passing control to the loaded program code. All operating systems that support program

loading have loaders. In many operating systems the loader is permanently resident in memory.

23

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

14 b) Draw the block diagram of 8255. (5)

This three-state bi-directional 8-bit buffer is used to interface the 8255 to the system data bus. Data is

transmitted or received by the buffer upon execution of input or output instructions by the CPU.

Control words and status information are also transferred through the data bus buffer.

24

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

PART D Answer any two full questions, each carries 10 marks.

15 With neat block diagram, explain the architecture of 8051. (10)

25

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

26

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

27

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

28

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

29

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

30

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

31

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

16 a) Explain the addressing modes of 8051 with examples. (6)

32

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

MOV A, @R0 moves content of address pointed by R0 to A

External Data Addressing :

Pointer used for external data addressing can be either R0/R1 (256 byte access) or DPTR (64kbyte access).

For example -

MOVX A, @R0; Moves content of 8-bit address pointed by R0 to A

MOVX A, @DPTR; Moves content of 16-bit address pointed by DPTR to A

External Code Addressing :

Sometimes we may want to store non-volatile data into the ROM e.g. look-up tables. Such data may require reading

the code memory. This may be done as follows -

MOVC A, @A+DPTR; Moves content of address pointed by A+DPTR to A

MOVC A, @A+PC; Moves content of address pointed by A+PC to A

16 b) Explain how serial port programming is done in 8051. (4)

SBUF is an 8-bit register used solely for serial communication. For a byte data to be transferred via

the TxD line, it must be placed in the SBUF register. The moment a byte is written into SBUF, it is

framed with the start and stop bits and transferred serially via the TxD line. SBUF holds the byte of

data when it is received by 8051 RxD line. When the bits are received serially via RxD, the 8051 de-

frames it by eliminating the stop and start bits, making a byte out of the data received, and then

placing it in SBUF. SCON is an 8-bit register used to program the start bit, stop bit, and data

bits of data framing, among other things. The basic steps in serial data ttransfer in 8051 are the

following.

1. TMOD register is loaded with the value 20H, indicating the use of timer 1 in mode 2 (8-bit auto-

reload) to set baud rate

2. The TH1 is loaded with one of the values to set baud rate for serial data transfer

3. The SCON register is loaded with the value 50H, indicating serial mode 1, where an 8- bit data is

framed with start and stop bits

4. TR1 is set to 1 to start timer 1

5. TI is cleared by CLR TI instruction

6. The character byte to be transferred serially is written into SBUF register

33

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

7. The TI flag bit is monitored with the use of instruction JNB TI,xx to see if the character has been

transferred completely

8. To transfer the next byte, go to step 5

17 Show how an LCD can be interfaced with 8051 and also write a program to send

‘Y’, ‘E’, ‘S’ to LCD continuously. (10)

All types of text LCDs have 8 data pins and 3 control signals. here data pins are connected with

P1 and three control pins RS, R/W and EN are connected with P2.0, P2.1 and P2.2 respectively.

It is a 16X2 LCD.

Steps for Data transfer to LCD

1. Initializing LCD:

Enable LCD and load control word to Control Register by selecting

RS=0, E=1, R/W=0, Port P1=Control Word.

Commands to be transferred are,

38H - 2 line 5x7 matrix mode

0Eh – Display on, Cursor on

01h – Clear LCD

80h – Cursor to beginning of first line

Make E=0 on completion of data transfer.

2. Displaying Data:

To continuously load data into the data register of LCD and to display it, the following

signals are required.

RS=1, R/W=0, E=1, Port P1= Data to be displayed on LCD

Make E=0 on completion of data transfer.

As LCD is a slow device, every transfer of Control word or data to it will require

more time. Hence a time delay should follow the data transfer from 8051 to LCD.

34

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

Programme to display the characters YES on the LCD screen

#include <reg51.h>

sfr 1data=0x90 //Port P1 address

sbit RS= P2^0; //Declare P2.0 as rs pin

sbit RW= P2^1; //Declare P2.1 as read/write pin

sbit EN= P2^2; //Declare P2.2 as enable pin

void main()

// lcdcmd() is a function to write a command to control register

lcdcmd(0x38); // Command for 2 line 5x7 matrix mode disply

msdelay(250); //Wait for LCD to read command

lcdcmd(0xE0); // Command for Disply on, Cursor on

msdelay(250); //Wait for LCD to read command

lcdcmd(0x01); // Command to Clear LCD display

msdelay(250); //Wait for LCD to read command

lcdcmd(0x80); //Command for positioning cursor at line-1 beginning

msdelay(250); //Wait for LCD to read command

// lcddata() is a function to write a data to data register

lcddata(‘Y’); //Send ASCII data ‘M’ to data register of LCD to display

msdelay(250); //Wait for LCD to read data

lcddata(‘E’); //Send ASCII data ‘D’ to data register of LCD to display

msdelay(250); //Wait for LCD to read data

lcddata(‘S’); //Send ASCII data ‘E’ to data register of LCD to display

msdelay(250); //Wait for LCD to read data

}

void lcdcmd(unsigned char value) // function to write a command to control register

{

1data = value; //control word

RS=0; //Select control register

RW=0; //Select write to LCD

EN=1; //Enable LCD

msdelay(100); //Wait for LCD to read control word

EN=0; //Disable LCD

Return; //Return to main program

}

void lcddata(unsigned char value) // function to write a data to data register to display

{

1data=value; //data to data register for displaying

RS=1; //Select data register

RW=0; //Select write to LCD

EN=1; //Enable LCD

msdelay(100); //Wait for LCD to read data

EN=0; //Disable LCD

35

Downloaded from Ktunotes.in

Microprocessor And Embedded Systems (EE309) - Dec 2017

return; //Return to main program

}

void msdelay(unsigned int dtime) // function for time delay

{

unsigned int i, j; // define i, j

for(i==0, i<dtime, i++) //time delay outer loop

for(i==0, i<FFFh, i++); //time delay inner loop

return;

}

36

Downloaded from Ktunotes.in

You might also like

- Adam HistoryDocument1,189 pagesAdam HistoryMartim Silva100% (1)

- Microprocessor Lab Viva Questions With AnswerssDocument24 pagesMicroprocessor Lab Viva Questions With AnswerssRahul Kumar100% (2)

- Unit - IiiDocument41 pagesUnit - IiiJit Agg0% (1)

- MCT Unit 2Document26 pagesMCT Unit 2Aravind RajNo ratings yet

- 8085 Is Pronounced AsDocument9 pages8085 Is Pronounced AsArbaaz khan786No ratings yet

- Unit I PDFDocument25 pagesUnit I PDFSomnath2014No ratings yet

- Unit Ii 8085 Micro Processor 8085 Architecture:: ME 6702 Mechatronics Mechanical Engineering 2019-20Document26 pagesUnit Ii 8085 Micro Processor 8085 Architecture:: ME 6702 Mechatronics Mechanical Engineering 2019-20GopinathNo ratings yet

- MPMC Model Exam Answer KeyDocument21 pagesMPMC Model Exam Answer KeyVenkatesan SundaramNo ratings yet

- MICROPORCESSOR 8085 Lab ManualDocument53 pagesMICROPORCESSOR 8085 Lab ManualAjay PatilNo ratings yet

- Micro Processor DineshDocument9 pagesMicro Processor DineshsandyNo ratings yet

- EE6502MPMC1Document31 pagesEE6502MPMC1nirmal_inboxNo ratings yet

- Study of 8085 and Kit STS-85Document10 pagesStudy of 8085 and Kit STS-85Mohammed MansoorNo ratings yet

- Experiment No. 1: Department of Electronics & Comm - EnggDocument7 pagesExperiment No. 1: Department of Electronics & Comm - EnggJaspreet KaurNo ratings yet

- MM Assignmemt 2Document7 pagesMM Assignmemt 2ALL ÎÑ ÔÑÈNo ratings yet

- Syllabus: 8085 ArchitectureDocument25 pagesSyllabus: 8085 Architecturetamilvendhan87No ratings yet

- Micro-Processors 8085: D.Arun KumarDocument52 pagesMicro-Processors 8085: D.Arun Kumarsrihari yandrapragadaNo ratings yet

- MPMC - Unit 1 - 8085 ArchitectureDocument17 pagesMPMC - Unit 1 - 8085 ArchitectureWickNo ratings yet

- 8085 - Short SummaryDocument14 pages8085 - Short SummaryTarunVarmaNo ratings yet

- An Over View of 8085Document12 pagesAn Over View of 8085nskprasad89No ratings yet

- 8085 Architecture & Pin DescriptionFileDocument19 pages8085 Architecture & Pin DescriptionFileKaseya TakahashiNo ratings yet

- 8085 MaterialDocument12 pages8085 MaterialsameerNo ratings yet

- MIC 04 - Case Study One 8085 MPUDocument40 pagesMIC 04 - Case Study One 8085 MPUomar hanyNo ratings yet

- Unit-I: 8-Bit MicroprocessorsDocument55 pagesUnit-I: 8-Bit MicroprocessorsAASTHA KIETNo ratings yet

- MC8085Document7 pagesMC8085Bhavani BhavanNo ratings yet

- EMISY Second Test Exemplary Questions Solved-3Document15 pagesEMISY Second Test Exemplary Questions Solved-3YANG LIUNo ratings yet

- Microprocessor 8085 NotesDocument48 pagesMicroprocessor 8085 NotesDewal ChaturvediNo ratings yet

- MPMC NotesDocument301 pagesMPMC NotesVarinder KumarNo ratings yet

- Microprosser 8085Document15 pagesMicroprosser 8085saigdv1978No ratings yet

- Question Bank 1Document18 pagesQuestion Bank 1heligolwala1No ratings yet

- Microprocessor and Micro ControllerDocument118 pagesMicroprocessor and Micro ControllerShiva ShanNo ratings yet

- Embedded System and IoTDocument9 pagesEmbedded System and IoTNitysNo ratings yet

- Answers of Microprocessor (8085) & Electronics FAQDocument21 pagesAnswers of Microprocessor (8085) & Electronics FAQsoumyadev100% (23)

- Microcontrollers and Systems Lesson3 Microprocessor 8085Document9 pagesMicrocontrollers and Systems Lesson3 Microprocessor 8085Jean de Dieu NGUIMFACK NDONGMONo ratings yet

- Micrprocessor Notes 2023Document18 pagesMicrprocessor Notes 2023GautamNo ratings yet

- 8085 Features, Signal DescriptionDocument13 pages8085 Features, Signal DescriptionRakesh Kumar DNo ratings yet

- An Introduction To INTEL 8085 Microprocessor: By:Ravindra Nadh.V, Assistant Professor, GST, BangaloreDocument35 pagesAn Introduction To INTEL 8085 Microprocessor: By:Ravindra Nadh.V, Assistant Professor, GST, BangaloreVasudev Rao KonjetiNo ratings yet

- EE6502 MPMC Two Marks With AnswerDocument10 pagesEE6502 MPMC Two Marks With Answervlsimani9110100% (1)

- Basic Concepts of MicroprocessorsDocument32 pagesBasic Concepts of MicroprocessorsAakrati SharmaNo ratings yet

- Microprocessor Viva Questions and AnswersDocument17 pagesMicroprocessor Viva Questions and AnswersUtsav Suresh PanchalNo ratings yet

- Questionnaire MICROPROCESSOR PART 1 UNIT 1 and 2Document20 pagesQuestionnaire MICROPROCESSOR PART 1 UNIT 1 and 2aditya2021cs081No ratings yet

- Experiment 1 4 SemesterDocument6 pagesExperiment 1 4 Semesteraman YadavNo ratings yet

- Microprocessors and Its Applications Short AnswersDocument15 pagesMicroprocessors and Its Applications Short AnswersVidya MuthukrishnanNo ratings yet

- MP & MC Micro Doc-20240520-Wa0000Document82 pagesMP & MC Micro Doc-20240520-Wa0000Deba Comedy ClubNo ratings yet

- 8085 Architecture: Control UnitDocument10 pages8085 Architecture: Control UnitsweetmemoriesneverdiNo ratings yet

- 8085 MicroprocessorDocument25 pages8085 Microprocessorprofessor2062No ratings yet

- 8085 MicroprocessorDocument38 pages8085 MicroprocessorPrateek PandeyNo ratings yet

- Lecture1423722820 PDFDocument101 pagesLecture1423722820 PDFdavNo ratings yet

- Microprocessor Lab ManualDocument85 pagesMicroprocessor Lab ManualReddyNo ratings yet

- Viva Questions and Answers in MP Lab - 1Document6 pagesViva Questions and Answers in MP Lab - 1Sai KrishnaNo ratings yet

- 8085 MicroprocessorDocument13 pages8085 MicroprocessorSajid Akram100% (1)

- MP VivaDocument42 pagesMP VivaShubham Benjamin JohnNo ratings yet

- Imp MP QuesDocument24 pagesImp MP QuesbhatiaharryjassiNo ratings yet

- BGK MPMC Unit-3 Q and ADocument21 pagesBGK MPMC Unit-3 Q and AMallesh ArjaNo ratings yet

- ALPQPDocument20 pagesALPQPTanujaramNo ratings yet

- MPMC SougataDocument5 pagesMPMC SougataSherlok HolmesNo ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Security SoftwareDocument149 pagesSecurity SoftwarePumas UnamNo ratings yet

- Characteristics Location Capacity Unit of Transfer Access Method Performance Physical Type Physical Characteristics OrganisationDocument53 pagesCharacteristics Location Capacity Unit of Transfer Access Method Performance Physical Type Physical Characteristics Organisationapi-26594847No ratings yet

- ComputerDocument171 pagesComputerMrdark Warrior100% (1)

- Framework Manager Developer GuideDocument152 pagesFramework Manager Developer GuideMoataz DeiabNo ratings yet

- First Boot LogDocument38 pagesFirst Boot LogEdvin DukaNo ratings yet

- Chapter 3 - Lab Environment SettingsDocument42 pagesChapter 3 - Lab Environment SettingsjamyssonNo ratings yet

- OS Sheet (1) SolutionDocument6 pagesOS Sheet (1) Solutionhussienboss99No ratings yet

- Jtagjet Usb InstallDocument12 pagesJtagjet Usb Installbella_duaneNo ratings yet

- Data Connector Blog 3.0 PDFDocument11 pagesData Connector Blog 3.0 PDFsantoshs2002848No ratings yet

- SAP Inbound IDocDocument16 pagesSAP Inbound IDocBeing Ronnie100% (1)

- Aws Iam PDFDocument26 pagesAws Iam PDFTomi JerNo ratings yet

- Fortios v7.2.5 Release NotesDocument60 pagesFortios v7.2.5 Release NotesKarthickNo ratings yet

- A Day in The Life of Aloha : Back of House Computer (BOH)Document3 pagesA Day in The Life of Aloha : Back of House Computer (BOH)abiiboyoNo ratings yet

- Cambridge IGCSE: Computer Science 0478/21Document16 pagesCambridge IGCSE: Computer Science 0478/21Marvin Bin Abdulaziz AbbilaniNo ratings yet

- DNS Probe Finished Nxdomain ErrorDocument14 pagesDNS Probe Finished Nxdomain Errorjack ryanNo ratings yet

- IndexDocument3 pagesIndexgabrielvasNo ratings yet

- A USB Flash Dri-WPS OfficeDocument3 pagesA USB Flash Dri-WPS Officehanzel lopezNo ratings yet

- Oct00 PDFDocument20 pagesOct00 PDFAnonymous YynGVcqdBMNo ratings yet

- ATCA and MicroATCA GuideDocument60 pagesATCA and MicroATCA Guidedenkins2020100% (1)

- Jax WS PDFDocument19 pagesJax WS PDFLam Le TranNo ratings yet

- Bitdefender AntivirusDocument4 pagesBitdefender AntivirusMohd Jamil PatahNo ratings yet

- Todero"U I Ines: ZX PectrumDocument77 pagesTodero"U I Ines: ZX PectrumEleodor Paul CirlugeaNo ratings yet

- Vmware Data Protection With Hitachi Data Protection Suite: Please Insert Your Hitachi Truenorth Partner Logo HereDocument21 pagesVmware Data Protection With Hitachi Data Protection Suite: Please Insert Your Hitachi Truenorth Partner Logo HereWildan AbdatNo ratings yet

- Student KitDocument38 pagesStudent KitGautam RastogiNo ratings yet

- Microcontroller Experiments Using Vinytics KitDocument3 pagesMicrocontroller Experiments Using Vinytics KitPatel ParthNo ratings yet

- Cctalk44 1aDocument50 pagesCctalk44 1airfanNo ratings yet

- Voice-Actuated, Speaker-Dependent Control System For Hospital BedDocument3 pagesVoice-Actuated, Speaker-Dependent Control System For Hospital BedtamnovNo ratings yet

- "Payroll Management System": Project Report OnDocument16 pages"Payroll Management System": Project Report OnLahiru M SuraweeraNo ratings yet

- G H Raisoni University, AmravatiDocument2 pagesG H Raisoni University, AmravatiVijay GadichaNo ratings yet