Professional Documents

Culture Documents

Onsemi Fairchild

Onsemi Fairchild

Uploaded by

pratik gautamOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Onsemi Fairchild

Onsemi Fairchild

Uploaded by

pratik gautamCopyright:

Available Formats

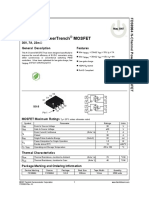

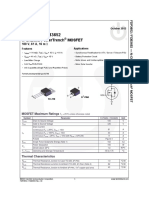

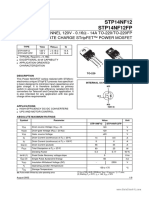

FDMA8884 N-Channel Power Trench® MOSFET

May 2014

FDMA8884

Single N-Channel Power Trench® MOSFET

30 V, 6.5 A, 23 mΩ

Features General Description

Max rDS(on) = 23 mΩ at VGS = 10 V, ID = 6.5 A This N-Channel MOSFET is produced using Fairchild

Semiconductor‘s advanced Power Trench® process that has

Max rDS(on) = 30 mΩ at VGS = 4.5 V, ID = 6.0 A

been optimized for rDS(on) switching performance.

High performance trench technology for extremely low rDS(on)

Fast switching speed

Application

RoHS Compliant

Primary Switch

Pin 1 D D G Bottom Drain Contact

D D

Drain Source

D D

G S

D D S

MicroFET 2X2 (Bottom View)

MOSFET Maximum Ratings TA = 25 °C unless otherwise noted

Symbol Parameter Ratings Units

VDS Drain to Source Voltage 30 V

VGS Gate to Source Voltage (Note 3) ±20 V

Drain Current -Continuous (Package limited) TC = 25 °C 8.0

ID -Continuous TA = 25 °C (Note 1a) 6.5 A

-Pulsed 25

Power Dissipation (Note 1a) 1.9

PD W

Power Dissipation (Note 1b) 0.7

TJ, TSTG Operating and Storage Junction Temperature Range -55 to +150 °C

Thermal Characteristics

RθJA Thermal Resistance, Junction to Ambient (Note 1a) 65

°C/W

RθJA Thermal Resistance, Junction to Ambient (Note 1b) 180

Package Marking and Ordering Information

Device Marking Device Package Reel Size Tape Width Quantity

884 FDMA8884 MicroFET 2x2 7 ’’ 8 mm 3000 units

©2012 Fairchild Semiconductor Corporation 1 www.fairchildsemi.com

FDMA8884 Rev.C5

FDMA8884 N-Channel Power Trench® MOSFET

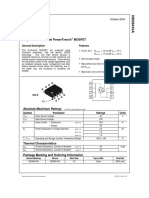

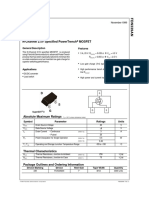

Electrical Characteristics TJ = 25 °C unless otherwise noted

Symbol Parameter Test Conditions Min Typ Max Units

Off Characteristics

BVDSS Drain to Source Breakdown Voltage ID = 250 μA, VGS = 0 V 30 V

ΔBVDSS Breakdown Voltage Temperature

ID = 250 μA, referenced to 25 °C 15 mV/°C

ΔTJ Coefficient

IDSS Zero Gate Voltage Drain Current VDS = 24 V, VGS = 0 V 1 μA

IGSS Gate to Source Leakage Current, Forward VGS = 20 V, VDS = 0 V 100 nA

On Characteristics

VGS(th) Gate to Source Threshold Voltage VGS = VDS, ID = 250 μA 1.2 1.8 3.0 V

ΔVGS(th) Gate to Source Threshold Voltage

ID = 250 μA, referenced to 25 °C -5 mV/°C

ΔTJ Temperature Coefficient

VGS = 10 V, ID = 6.5 A 19 23

rDS(on) Static Drain to Source On Resistance VGS = 4.5 V, ID = 6.0 A 25 30 mΩ

VGS = 10 V, ID = 6.5 A, TJ = 125 °C 25 30

gFS Forward Transconductance VDD = 5 V, ID = 6.5 A 26 S

Dynamic Characteristics

Ciss Input Capacitance 339 450 pF

VDS = 15 V, VGS = 0 V,

Coss Output Capacitance 132 175 pF

f = 1 MHz

Crss Reverse Transfer Capacitance 18 28 pF

Rg Gate Resistance 1.1 Ω

Switching Characteristics

td(on) Turn-On Delay Time 5 10 ns

tr Rise Time VDD = 15 V, ID = 6.5 A, 1 10 ns

td(off) Turn-Off Delay Time VGS = 10 V, RGEN = 6 Ω 11 20 ns

tf Fall Time 1 10 ns

Total Gate Charge VGS = 0 V to 10 V 5.4 7.5 nC

Qg(TOT)

Total Gate Charge VGS = 0 V to 4.5 V VDD = 15 V 2.7 3.7 nC

Qgs Total Gate Charge ID = 6.5 A 1.0 nC

Qgd Gate to Drain “Miller” Charge 0.9 nC

Drain-Source Diode Characteristics

VSD Source to Drain Diode Forward Voltage VGS = 0 V, IS = 6.5 A (Note 2) 0.86 1.2 V

trr Reverse Recovery Time 16 28 ns

IF = 6.5 A, di/dt = 100 A/μs

Qrr Reverse Recovery Charge 4 10 nC

NOTES:

1. RθJA is the sum of the junction-to-case and case-to-ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of the drain pins.

RθJC is guaranteed by design while RθCA is determined by the user's board design.

a. 65 °C/W when mounted b. 180 °C/W when mounted on a

on a 1 in2 pad of 2 oz copper. minimum pad of 2 oz copper.

2. Pulse Test: Pulse Width < 300 μs, Duty cycle < 2.0 %.

3. As an N-ch device, the negative Vgs rating is for low duty cycle pulse occurrence only. No continuous rating is implied.

©2012 Fairchild Semiconductor Corporation 2 www.fairchildsemi.com

FDMA8884 Rev.C5

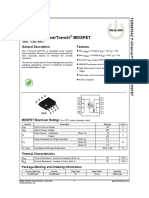

FDMA8884 N-Channel Power Trench® MOSFET

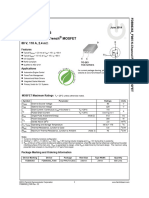

Typical Characteristics TJ = 25 °C unless otherwise noted

25

3.5

VGS = 10 V

DRAIN TO SOURCE ON-RESISTANCE

PULSE DURATION = 80 μs

VGS = 6 V DUTY CYCLE = 0.5% MAX

20 3.0

ID, DRAIN CURRENT (A)

VGS = 4.5 V VGS = 3.5 V

2.5

NORMALIZED

15

VGS = 4 V

VGS = 3.5 V VGS = 4 V

2.0

10 VGS = 4.5 V

1.5

5

PULSE DURATION = 80 μs 1.0

DUTY CYCLE = 0.5% MAX VGS = 6 V VGS = 10 V

0

0 0.4 0.8 1.2 1.6 2.0 0.5

0 5 10 15 20 25

VDS, DRAIN TO SOURCE VOLTAGE (V) ID, DRAIN CURRENT (A)

Figure 1. On Region Characteristics Figure 2. Normalized On-Resistance

vs Drain Current and Gate Voltage

1.5 80

DRAIN TO SOURCE ON-RESISTANCE

ID = 6.5 A PULSE DURATION = 80 μs

1.4

SOURCE ON-RESISTANCE (mΩ)

VGS = 10 V DUTY CYCLE = 0.5% MAX

1.3 60

rDS(on), DRAIN TO

ID = 6.5 A

NORMALIZED

1.2

1.1 40

1.0 TJ = 125 oC

0.9

20

0.8 TJ = 25 oC

0.7

-75 -50 -25 0 25 50 75 100 125 150 0

2 4 6 8 10

TJ, JUNCTION TEMPERATURE (oC)

VGS, GATE TO SOURCE VOLTAGE (V)

Figure 3. Normalized On Resistance Figure 4. On-Resistance vs Gate to

vs Junction Temperature Source Voltage

25 30

PULSE DURATION = 80 μs VGS = 0 V

IS, REVERSE DRAIN CURRENT (A)

DUTY CYCLE = 0.5% MAX 10

20

ID, DRAIN CURRENT (A)

VDS = 5 V

TJ = 150 oC

15 1

TJ = 150 oC TJ = 25 oC

10

TJ = 25 oC

0.1

5 TJ = -55 oC

TJ = -55 oC

0 0.01

1 2 3 4 5 0.2 0.4 0.6 0.8 1.0 1.2

VGS, GATE TO SOURCE VOLTAGE (V) VSD, BODY DIODE FORWARD VOLTAGE (V)

Figure 5. Transfer Characteristics Figure 6. Source to Drain Diode

Forward Voltage vs Source Current

©2012 Fairchild Semiconductor Corporation 3 www.fairchildsemi.com

FDMA8884 Rev.C5

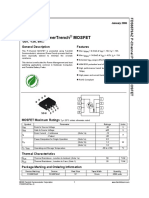

FDMA8884 N-Channel Power Trench® MOSFET

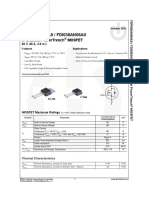

Typical Characteristics TJ = 25 °C unless otherwise noted

10 500

VGS, GATE TO SOURCE VOLTAGE (V)

ID = 6.5 A

8 Ciss

CAPACITANCE (pF)

VDD = 10 V VDD = 15 V

6 100

Coss

VDD = 20 V

4

2

f = 1 MHz

VGS = 0 V Crss

0 10

0 1 2 3 4 5 6 0.1 1 10 30

Qg, GATE CHARGE (nC) VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 7. Gate Charge Characteristics Figure 8. Capacitance vs Drain

to Source Voltage

30 200

SINGLE PULSE

P(PK), PEAK TRANSIENT POWER (W)

10 100 RθJA = 180 oC/W

TA = 25 oC

ID, DRAIN CURRENT (A)

100 μs

1

THIS AREA IS 1 ms 10

LIMITED BY rDS(on)

10 ms

SINGLE PULSE 100 ms

0.1

TJ = MAX RATED 1s

RθJA = 180 oC/W 10 s

1

TA = 25 oC DC

0.01 0.5 -4 -3 -2 -1 3

0.01 0.1 1 10 100 10 10 10 10 1 10 100 10

VDS, DRAIN to SOURCE VOLTAGE (V) t, PULSE WIDTH (sec)

Figure 9. Forward Bias Safe Figure 10. Single Pulse Maximum

Operating Area Power Dissipation

2

DUTY CYCLE-DESCENDING ORDER

1

NORMALIZED THERMAL

D = 0.5

IMPEDANCE, ZθJA

0.2

0.1 PDM

0.1 0.05

0.02

0.01 t1

t2

SINGLE PULSE NOTES:

DUTY FACTOR: D = t1/t2

o

RθJA = 180 C/W PEAK TJ = PDM x ZθJA x RθJA + TA

0.01

0.005

-4 -3 -2 -1

10 10 10 10 1 10 100 1000

t, RECTANGULAR PULSE DURATION (sec)

Figure 11. Junction-to-Ambient Transient Thermal Response Curve

Figure 12.

©2012 Fairchild Semiconductor Corporation 4 www.fairchildsemi.com

FDMA8884 Rev.C5

FDMA8884 N-Channel Power Trench® MOSFET

Dimensional Outline and Pad Layout

0.05 C 2.0 A

2X B

2.0

1.70

(0.20)

1.00 No Traces

0.05 C 6 4 allowed in

PIN#1 IDENT TOP VIEW 2X this Area

1.05 2.30

0.10 C

0.47(6X)

0.08 C SIDE VIEW 1 3

C 0.40(6X)

0.65

SEATING RECOMMENDED

PLANE

LAND PATTERN OPT 1

(0.15)

(0.50)

1.70

PIN #1 IDENT (0.20)4X 0.45

1 3 (0.20)

1.00

(6X) 6 4

(0.50)

1.05 0.66

6 4 2.30

(6X)

0.65 0.47(6X)

0.10 C A B

1.30 1 3

0.05 C 0.40(7X)

0.65

BOTTOM VIEW

RECOMMENDED

NOTES: LAND PATTERN OPT 2

A. PACKAGE DOES NOT FULLY CONFORM

TO JEDEC MO-229 REGISTRATION

B. DIMENSIONS ARE IN MILLIMETERS.

C. DIMENSIONS AND TOLERANCES PER

ASME Y14.5M, 2009.

D. LAND PATTERN RECOMMENDATION IS

EXISTING INDUSTRY LAND PATTERN.

E. DRAWING FILENAME: MKT-MLP06Lrev4.

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, spe-

cifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/package/packageDetails.html?id=PN_MLDEB-C06

©2012 Fairchild Semiconductor Corporation 5 www.fairchildsemi.com

FDMA8884 Rev.C5

FDMA8884 N-Channel Power Trench® MOSFET

TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not

intended to be an exhaustive list of all such trademarks.

AccuPower™ F-PFS™ ®*

AX-CAP®* FRFET® ® tm

BitSiC™ Global Power ResourceSM PowerTrench®

TinyBoost®

Build it Now™ GreenBridge™ PowerXS™

TinyBuck®

CorePLUS™ Green FPS™ Programmable Active Droop™

TinyCalc™

CorePOWER™ Green FPS™ e-Series™ QFET®

TinyLogic®

CROSSVOLT™ Gmax™ QS™

TINYOPTO™

CTL™ GTO™ Quiet Series™

TinyPower™

Current Transfer Logic™ IntelliMAX™ RapidConfigure™

TinyPWM™

DEUXPEED® ISOPLANAR™ ™ TinyWire™

Dual Cool™ Marking Small Speakers Sound Louder

TranSiC™

EcoSPARK® and Better™ Saving our world, 1mW/W/kW at a time™

TriFault Detect™

EfficentMax™ MegaBuck™ SignalWise™

TRUECURRENT®*

ESBC™ MICROCOUPLER™ SmartMax™

μSerDes™

® MicroFET™ SMART START™

MicroPak™ Solutions for Your Success™

Fairchild® MicroPak2™ SPM®

Fairchild Semiconductor® MillerDrive™ STEALTH™ UHC®

FACT Quiet Series™ MotionMax™ SuperFET® Ultra FRFET™

FACT® mWSaver® SuperSOT™-3 UniFET™

FAST® OptoHiT™ SuperSOT™-6 VCX™

FastvCore™ OPTOLOGIC® SuperSOT™-8 VisualMax™

FETBench™ OPTOPLANAR® SupreMOS® VoltagePlus™

FPS™ SyncFET™ XS™

Sync-Lock™ 仙童 ™

*Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE

RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY

PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY

THEREIN, WHICH COVERS THESE PRODUCTS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE

EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used here in:

1. Life support devices or systems are devices or systems which, (a) are 2. A critical component in any component of a life support, device, or

intended for surgical implant into the body or (b) support or sustain life, system whose failure to perform can be reasonably expected to cause

and (c) whose failure to perform when properly used in accordance with the failure of the life support device or system, or to affect its safety or

instructions for use provided in the labeling, can be reasonably effectiveness.

expected to result in a significant injury of the user.

ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation’s Anti-Counterfeiting Policy. Fairchild’s Anti-Counterfeiting Policy is also stated on our external website,

www.Fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufactures of semiconductor products are experiencing counterfeiting of their

parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed

application, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the

proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild

Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild

Distributors are genuine parts, have full traceability, meet Fairchild’s quality standards for handing and storage and provide access to Fairchild’s full range of

up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address and

warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is

committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Datasheet contains the design specifications for product development. Specifications

Advance Information Formative / In Design

may change in any manner without notice.

Datasheet contains preliminary data; supplementary data will be published at a later

Preliminary First Production date. Fairchild Semiconductor reserves the right to make changes at any time without

notice to improve design.

Datasheet contains final specifications. Fairchild Semiconductor reserves the right to

No Identification Needed Full Production

make changes at any time without notice to improve the design.

Datasheet contains specifications on a product that is discontinued by Fairchild

Obsolete Not In Production

Semiconductor. The datasheet is for reference information only.

Rev. I68

©2012 Fairchild Semiconductor Corporation 6 www.fairchildsemi.com

FDMA8884 Rev.C5

You might also like

- N-Channel Powertrench Mosfet: 30V, 7A, 23M General Description FeaturesDocument6 pagesN-Channel Powertrench Mosfet: 30V, 7A, 23M General Description FeaturesLuis CarlosNo ratings yet

- Fdc658Ap: Single P-Channel Logic Level Powertrench Mosfet - 30V, - 4A, 50MDocument5 pagesFdc658Ap: Single P-Channel Logic Level Powertrench Mosfet - 30V, - 4A, 50MKakatuar KakatuaNo ratings yet

- Fdc642P: Single P-Channel 2.5V Specified Powertrench MosfetDocument5 pagesFdc642P: Single P-Channel 2.5V Specified Powertrench MosfetdistefanoNo ratings yet

- CBE6030LDocument8 pagesCBE6030LgdiliogNo ratings yet

- N-Channel Low QG Mosfet 30V, 100A, 3.3m: MOS-TECH Semiconductor Co.,LTDDocument9 pagesN-Channel Low QG Mosfet 30V, 100A, 3.3m: MOS-TECH Semiconductor Co.,LTDAnonymous p1ig0zX6p0No ratings yet

- Onsemiconductor Fds6679az Datasheets 0664Document6 pagesOnsemiconductor Fds6679az Datasheets 0664Yohandris FernandezNo ratings yet

- FDP 5800Document8 pagesFDP 5800Khalid JakirNo ratings yet

- FDD8880Document11 pagesFDD8880DannyNo ratings yet

- Onsemiconductor Nds8410a Datasheets 3577Document5 pagesOnsemiconductor Nds8410a Datasheets 3577Google EyeNo ratings yet

- FDM S3672Document7 pagesFDM S3672chudungk57No ratings yet

- N-Channel Powertrench Mosfet: 30V, 8.5A, 23M General Descriptions FeaturesDocument6 pagesN-Channel Powertrench Mosfet: 30V, 8.5A, 23M General Descriptions FeaturesjokophpNo ratings yet

- Fdd9407L - F085: N-Channel Logic Level Powertrench MosfetDocument7 pagesFdd9407L - F085: N-Channel Logic Level Powertrench Mosfetonis1 onis1No ratings yet

- Stp80Pf55: P-Channel 55V - 0.016 - 80A To-220 Stripfet Ii Power MosfetDocument7 pagesStp80Pf55: P-Channel 55V - 0.016 - 80A To-220 Stripfet Ii Power MosfetRadoslav RadoslavovNo ratings yet

- Fds6679Az P-Channel Powertrench Mosfet: - 30V, - 13A, 9M General Description FeaturesDocument6 pagesFds6679Az P-Channel Powertrench Mosfet: - 30V, - 13A, 9M General Description FeaturesEdgxr DxnielNo ratings yet

- DO3N10 DatasheetDocument4 pagesDO3N10 DatasheetMattNo ratings yet

- Fds4435Bz: P-Channel Powertrench MosfetDocument6 pagesFds4435Bz: P-Channel Powertrench MosfetKevin TateNo ratings yet

- MDF13N50: N-Channel MOSFET 500V, 13.0 A, 0.5Document6 pagesMDF13N50: N-Channel MOSFET 500V, 13.0 A, 0.5Moroșan CristiNo ratings yet

- MDF9N50F MagnaChipDocument6 pagesMDF9N50F MagnaChipchokNo ratings yet

- FDS6679AZ DatasheetDocument6 pagesFDS6679AZ DatasheetMarivaldo NascimentoNo ratings yet

- Rd3g01battl1 eDocument14 pagesRd3g01battl1 eJSN GDYNo ratings yet

- N-Channel Power Trench Mosfet: Features General DescriptionDocument8 pagesN-Channel Power Trench Mosfet: Features General DescriptionRicardo VieiraNo ratings yet

- Fdn358P: Single P-Channel, Logic Level, Powertrench MosfetDocument5 pagesFdn358P: Single P-Channel, Logic Level, Powertrench MosfetAlex KarimNo ratings yet

- MTP3055VLDocument3 pagesMTP3055VLsybiantechnologies2009No ratings yet

- TPC8064-H: DescriptionDocument5 pagesTPC8064-H: DescriptionBari ShobariNo ratings yet

- Fds6612A: Single N-Channel, Logic-Level, Powertrench MosfetDocument8 pagesFds6612A: Single N-Channel, Logic-Level, Powertrench MosfetCarlos Manuel PeraltaNo ratings yet

- Rq3e120at e 1139149Document13 pagesRq3e120at e 1139149Rudy SuprayogiNo ratings yet

- HL Haolin Elec 5N04 - C237240Document4 pagesHL Haolin Elec 5N04 - C237240German ValenciaNo ratings yet

- FDN352 ApDocument5 pagesFDN352 ApTecnicos SlotsNo ratings yet

- Datasheet - HK Fds9431a10 4643859Document5 pagesDatasheet - HK Fds9431a10 4643859jim campbellNo ratings yet

- 8205A RZCMicroelectronicsDocument6 pages8205A RZCMicroelectronicsabdouzaouiidrissiNo ratings yet

- Mt2301 Mos TechDocument8 pagesMt2301 Mos Techdoraemon007No ratings yet

- Fdc658Ap: Single P-Channel Logic Level Powertrench Mosfet - 30V, - 4A, 50MDocument5 pagesFdc658Ap: Single P-Channel Logic Level Powertrench Mosfet - 30V, - 4A, 50MfaberjetNo ratings yet

- Fdp3652 / Fdb3652: N-Channel Powertrench MosfetDocument14 pagesFdp3652 / Fdb3652: N-Channel Powertrench Mosfethalil ibrahim soysalNo ratings yet

- 8 N 80Document5 pages8 N 80pravin jadavNo ratings yet

- La Conquista Divina Aw TozerDocument4 pagesLa Conquista Divina Aw TozerEmmanuel ZambranoNo ratings yet

- 06n03Document8 pages06n03buba.kastorsNo ratings yet

- FDB 7030 LDocument4 pagesFDB 7030 LIsu IstvánNo ratings yet

- Fdd6680 / Fdu6680: 30V N-Channel Powertrench MosfetDocument6 pagesFdd6680 / Fdu6680: 30V N-Channel Powertrench Mosfetmarcelo giussaniNo ratings yet

- N-Channel Enhancement Mode Field Effect Transistor: FeaturesDocument7 pagesN-Channel Enhancement Mode Field Effect Transistor: Features5a DOHCNo ratings yet

- Fdn339An: N-Channel 2.5V Specified Powertrench MosfetDocument5 pagesFdn339An: N-Channel 2.5V Specified Powertrench MosfetKevinAlexisVelascoPeraltaNo ratings yet

- RSC002P03Document13 pagesRSC002P03Avijit DuttaNo ratings yet

- STB 8 NM 60 DDocument13 pagesSTB 8 NM 60 DErkanNo ratings yet

- MDF1752 MagnaChipDocument6 pagesMDF1752 MagnaChipA.hNo ratings yet

- Rohm S A0001611900 1-2561600Document14 pagesRohm S A0001611900 1-2561600RamonAngelNo ratings yet

- sh8kc7tb1 eDocument14 pagessh8kc7tb1 eudaymachNo ratings yet

- STM 4820Document7 pagesSTM 4820JourneyNo ratings yet

- SOT-23-6L Plastic-Encapsulate MOSFETS: CJL8205ADocument5 pagesSOT-23-6L Plastic-Encapsulate MOSFETS: CJL8205AdexterNo ratings yet

- STP80NF75L STB80NF75L STB80NF75L-1: N-CHANNEL 75V - 0.008 - 80A TO-220/D Pak/I PAK Stripfet™ Ii Power MosfetDocument11 pagesSTP80NF75L STB80NF75L STB80NF75L-1: N-CHANNEL 75V - 0.008 - 80A TO-220/D Pak/I PAK Stripfet™ Ii Power MosfetRyn YahuFNo ratings yet

- TDS ONS ON Semiconductor EN 1582622441460Document5 pagesTDS ONS ON Semiconductor EN 1582622441460pafot16448No ratings yet

- FDMC7692: N-Channel Power Trench MosfetDocument6 pagesFDMC7692: N-Channel Power Trench MosfetHerdhis VegaNo ratings yet

- Fdb86363 - F085: N-Channel Powertrench MosfetDocument6 pagesFdb86363 - F085: N-Channel Powertrench MosfetNobreak ServiceNo ratings yet

- Tmp12n60a Tmpf12n60aDocument7 pagesTmp12n60a Tmpf12n60aHenrique VendasNo ratings yet

- 3400Document4 pages3400Duta HastaNo ratings yet

- Fdp038An06A0 / Fdi038An06A0: N-Channel Powertrench MosfetDocument12 pagesFdp038An06A0 / Fdi038An06A0: N-Channel Powertrench Mosfetdani pedroNo ratings yet

- Fdp050an06a0 241446Document14 pagesFdp050an06a0 241446ElvisNo ratings yet

- Fdmc6679Az: P-Channel Powertrench MosfetDocument7 pagesFdmc6679Az: P-Channel Powertrench MosfetMahmoud ElrefaeyNo ratings yet

- STP14NF12 STP14NF12FP: N-CHANNEL 120V - 0.16 - 14A TO-220/TO-220FP Low Gate Charge Stripfet™ Power MosfetDocument9 pagesSTP14NF12 STP14NF12FP: N-CHANNEL 120V - 0.16 - 14A TO-220/TO-220FP Low Gate Charge Stripfet™ Power MosfetDavid Duarte VeraNo ratings yet

- Fds8880 N-Channel Powertrench: MosfetDocument12 pagesFds8880 N-Channel Powertrench: MosfetDavid J. Pinto ApazaNo ratings yet

- Sn74als133 NAND GateDocument16 pagesSn74als133 NAND Gatepratik gautamNo ratings yet

- Sanyou WJ31X RelayDocument3 pagesSanyou WJ31X Relaypratik gautamNo ratings yet

- ROHMDocument16 pagesROHMpratik gautamNo ratings yet

- NEXPERIADocument14 pagesNEXPERIApratik gautamNo ratings yet

- KG-K111 - Latching Relay - Data Sheet - 052017Document3 pagesKG-K111 - Latching Relay - Data Sheet - 052017pratik gautamNo ratings yet

- TL 4903Document1 pageTL 4903pratik gautamNo ratings yet

- 8 Pin MosfetDocument10 pages8 Pin Mosfetpratik gautamNo ratings yet

- 45DB161E-Adesto Flash MemoryDocument73 pages45DB161E-Adesto Flash Memorypratik gautamNo ratings yet

- 10RDocument124 pages10RJosé Alexánder Mesa García100% (1)

- Capacitor Bank Switching With Vacuum Circuit Breakers - Schneider Electric PDFDocument5 pagesCapacitor Bank Switching With Vacuum Circuit Breakers - Schneider Electric PDFpitambervermaNo ratings yet

- 18W Greengo Go-4231 Led Tube 17082022Document4 pages18W Greengo Go-4231 Led Tube 17082022LezorngiaNo ratings yet

- Chapter 2Document42 pagesChapter 2Zekarias LibenaNo ratings yet

- Theni GIS FT 10 MWDocument3 pagesTheni GIS FT 10 MWgohilnarendra100% (1)

- 2 SK 1056Document9 pages2 SK 1056Bryan WahyuNo ratings yet

- 45CB Thermal Magnetic Electronic TripDocument23 pages45CB Thermal Magnetic Electronic Tripryan varonaNo ratings yet

- 1ph & 3 PH Ac CircuitsDocument58 pages1ph & 3 PH Ac CircuitsSuman naidu RNo ratings yet

- Operating Instructions (Included Installation Instruction) : Compact Axial Flow FanDocument12 pagesOperating Instructions (Included Installation Instruction) : Compact Axial Flow FanmoceNo ratings yet

- DORNA EPS-B1 Servo User Manual V1.11 OcrDocument191 pagesDORNA EPS-B1 Servo User Manual V1.11 Ocrnapo3tNo ratings yet

- Asumsi HargaDocument84 pagesAsumsi HargaAbdur Rozaq FakhruddinNo ratings yet

- VDO Diesel Tach GuageDocument2 pagesVDO Diesel Tach GuageicbidtNo ratings yet

- B 01Document27 pagesB 01Kasi ChinnaNo ratings yet

- Madhu ThesisDocument65 pagesMadhu Thesisrv_andeNo ratings yet

- 14PM M201V NMBDocument1 page14PM M201V NMBCristianEnacheNo ratings yet

- 001 ERICSSON MC1 Opc A - 84510992Document7 pages001 ERICSSON MC1 Opc A - 84510992albertoNo ratings yet

- IEEE Standard Guide For Methods Of: Power-Factor Measurement For Low-Voltage Inductive Test CircuitsDocument13 pagesIEEE Standard Guide For Methods Of: Power-Factor Measurement For Low-Voltage Inductive Test CircuitsukritNo ratings yet

- Power System Studies ObjectivesDocument3 pagesPower System Studies ObjectivesAmit ShekhatNo ratings yet

- D-AAA-CIV-LIGHT (Rev.0-2019) Data SheetDocument12 pagesD-AAA-CIV-LIGHT (Rev.0-2019) Data SheetWael AlmassriNo ratings yet

- Icom Ic-T3hDocument31 pagesIcom Ic-T3hvjt.radioNo ratings yet

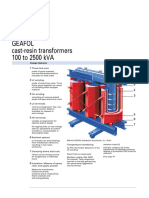

- Geafolproduct EnglishDocument4 pagesGeafolproduct EnglishkostyaNo ratings yet

- Efie Device Schematic PlansDocument3 pagesEfie Device Schematic Plansguillermo1serranoNo ratings yet

- Module 11A 1Document23 pagesModule 11A 1Chitrali SontakkeNo ratings yet

- DigitalDocument414 pagesDigitalRichard JonesNo ratings yet

- BUL312FH: High Voltage Fast-Switching NPN Power TransistorDocument6 pagesBUL312FH: High Voltage Fast-Switching NPN Power TransistorAngel Simo MoralesNo ratings yet

- What Is Programmable Logic ControllerDocument4 pagesWhat Is Programmable Logic ControllerNgwe Soe HanNo ratings yet

- Section 68Document2 pagesSection 68dan_geplNo ratings yet

- Infinitum Gen4 IoM 20230811Document10 pagesInfinitum Gen4 IoM 20230811jonaslomlomNo ratings yet

- HP54201AD Service ManualDocument173 pagesHP54201AD Service ManualapocalipcNo ratings yet

- Simulation of An Impulse Arc Discharge in Line Lightning Protection DevicesDocument5 pagesSimulation of An Impulse Arc Discharge in Line Lightning Protection DevicesJARINGAN KTBNo ratings yet