Professional Documents

Culture Documents

UVM, SV Assesment

UVM, SV Assesment

Uploaded by

krishnaavOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

UVM, SV Assesment

UVM, SV Assesment

Uploaded by

krishnaavCopyright:

Available Formats

UVM

(Neccessary use the code snippets as example)

1) What is the purpose of UVM and explain the UVM testbench with block diagram?

2) Explain the UVM hierarchy with flow diagram

3) Explain the Phases in UVM

4) What is virtual sequence and difference b/w p_sequencer & m_sequencer?

5) What is the 'uvm_do and explain the use of macro

6) How to print testbench topology

7) Explain driver-sequence handshake mechanism

8) Explain about UVM factory and override methods

9) Difference b/w uvm_config_db and uvm_resource_db

10) What are TLM ports and requirements in Testbench

11) Explain RAL Model

12) Write a Testbench code for SPI Protocol should include Top, Environment,

Interface, Agent, Driver, Sequence, Sequencer, Monitor, Scoreboard(if neccessary

required)

SPI Protocol contains 4 slaves (CS0, CS1, CS2, CS3)

Interface Pins - MISO, MOSI, CLK (100MHz), CS0, CS1, CS2, CS3.

System Verilog

(Neccessary use the code snippets as example)

1) What is shallow and deep copy with example?

2) What is the difference of virtual and pure virtual function

3) Explain the SV thread process methods?

4) Explain the Polymorphism and virtual methods?

5) Explain the weighted distrbution constraints?

6) What are immediate and concurrent assertion and three methods?

7) Explain the useage of scope resolution operator?

8) What is functional coverage and coverpoint, covergroups?

9) Explain the associative, dynamic and queues?

10) Write a Testbench code for I2C protocol? - Only in System Verilog Concepts

You might also like

- Interview DVDocument5 pagesInterview DVPrasad Reddy100% (1)

- Intel. Interview QuestionsDocument3 pagesIntel. Interview QuestionsSatish MbNo ratings yet

- Coverage/Block Level Functional Coverage ExampleDocument14 pagesCoverage/Block Level Functional Coverage ExampleYeshoda MallikarjunaNo ratings yet

- Coa Important QuestionsDocument5 pagesCoa Important QuestionsGanesh Babu100% (2)

- ATPG Methodology FlowDocument37 pagesATPG Methodology FlowaanbalanNo ratings yet

- A Practical Guide To Adopting The Universal Verfication MethodologyDocument199 pagesA Practical Guide To Adopting The Universal Verfication MethodologykrishnaavNo ratings yet

- Verilog Sv Interview QuestionsDocument21 pagesVerilog Sv Interview Questionsctulasi1411No ratings yet

- Large List of Intel Interview QuestionsDocument4 pagesLarge List of Intel Interview QuestionsvaghelamiralNo ratings yet

- Verilog SV Interview QuestionsDocument21 pagesVerilog SV Interview QuestionsShakeel ScetNo ratings yet

- Emebbedd Question BankDocument25 pagesEmebbedd Question Banksujith100% (3)

- 8051 QuestionDocument9 pages8051 QuestionJai Singh MauryaNo ratings yet

- Cao Question BankDocument4 pagesCao Question Banknashikexplore1No ratings yet

- Questions Collection of Embedded SystemDocument6 pagesQuestions Collection of Embedded Systemkaran subediNo ratings yet

- Insights of An InverterDocument2 pagesInsights of An InverterArunKumarSainiNo ratings yet

- Paper ID (A0406) : M.Sc. IT/PGDCA (201) (S05) (Sem. - 2) Computer Networks Instruction To Candidates: 1) 2)Document2 pagesPaper ID (A0406) : M.Sc. IT/PGDCA (201) (S05) (Sem. - 2) Computer Networks Instruction To Candidates: 1) 2)Ravjot Singh SachdevaNo ratings yet

- Intel Interview QuestionsDocument11 pagesIntel Interview QuestionsdumpsatNo ratings yet

- Nited Nstitute of EchnologyDocument11 pagesNited Nstitute of Echnologykeerthi3214No ratings yet

- Design ExercisesDocument13 pagesDesign ExercisesCristal NgoNo ratings yet

- Unit 1 Typical Embedded SystemDocument4 pagesUnit 1 Typical Embedded SystemsukeshNo ratings yet

- DFT Interview QuestionsDocument2 pagesDFT Interview Questionsjagruthims75% (4)

- Insights of An InverterDocument4 pagesInsights of An InverterSowmya BarliNo ratings yet

- Computer Organization and Architecture: Part-ADocument4 pagesComputer Organization and Architecture: Part-AMohamed YousufdeenNo ratings yet

- Intel Interview QuestionsDocument3 pagesIntel Interview QuestionsRuchi GujarathiNo ratings yet

- Question Bank: Subject Name: Operating Systems Subject Code: CS2254 Year/ Sem: IVDocument6 pagesQuestion Bank: Subject Name: Operating Systems Subject Code: CS2254 Year/ Sem: IVMuralidharan RadhakrishnanNo ratings yet

- InterviewDocument6 pagesInterviewAbhishek KumarNo ratings yet

- CS2254 QBDocument7 pagesCS2254 QBkuttymythuNo ratings yet

- Cs2253 Computer Organization and Architecture Question BankDocument10 pagesCs2253 Computer Organization and Architecture Question BankVenkat RamNo ratings yet

- VLSI Placement PapersDocument5 pagesVLSI Placement PapersAsn RoyNo ratings yet

- Mainframe Gatekeeper Rules, Requirements and RecommendationsDocument7 pagesMainframe Gatekeeper Rules, Requirements and Recommendationsmukherje_sanjoyNo ratings yet

- Computer Architecture Question BankDocument7 pagesComputer Architecture Question BankSalma Mehajabeen ShajahanNo ratings yet

- Protacall TestingDocument11 pagesProtacall Testingkumar0% (1)

- Assignment Questions of ES1Document5 pagesAssignment Questions of ES1tanviNo ratings yet

- Verilog - Q&ADocument24 pagesVerilog - Q&A6055 - Ragul TNo ratings yet

- DFT Interview QuestionsDocument3 pagesDFT Interview QuestionsJayesh PopatNo ratings yet

- IMP QuestionsDocument1 pageIMP QuestionsWednesdayNo ratings yet

- Embedded System IT2354 Question Bank Anna University R2008Document6 pagesEmbedded System IT2354 Question Bank Anna University R2008Mukesh BollineniNo ratings yet

- ASIC-System On Chip-VLSI Design: Intel Interview QuestionsDocument5 pagesASIC-System On Chip-VLSI Design: Intel Interview QuestionsKeerthiKalyanNo ratings yet

- Unit IIDocument13 pagesUnit IISoundarrajan RajanNo ratings yet

- COARdbjiM - QBDocument7 pagesCOARdbjiM - QBquetiepie7No ratings yet

- Interview q1Document6 pagesInterview q1Abhishek KumarNo ratings yet

- SPARC T5-Based Servers Implementation-Installation Online AssessmentDocument20 pagesSPARC T5-Based Servers Implementation-Installation Online Assessmentjucamisternet100% (1)

- Blic EviDocument3 pagesBlic EviMartin AndračićNo ratings yet

- Cs1358 Ece Computer ArchitectureDocument8 pagesCs1358 Ece Computer ArchitectureMarimuthu MuthaiyanNo ratings yet

- Question Bank CompleteDocument5 pagesQuestion Bank CompleteSaurabh SenNo ratings yet

- Ugc Net Paper 3Document7 pagesUgc Net Paper 3RajaReddy VNNo ratings yet

- CHAPTER-1: Introduction To Microprocessor (10%) : Short Answer QuestionsDocument6 pagesCHAPTER-1: Introduction To Microprocessor (10%) : Short Answer QuestionsRAHULNo ratings yet

- ARM Interview QuestionsDocument17 pagesARM Interview QuestionsSahil Khan0% (1)

- MID-3 EXAM (16EC370 - Microcontrollers For Embedded Systems)Document3 pagesMID-3 EXAM (16EC370 - Microcontrollers For Embedded Systems)Vijayaraghavan VNo ratings yet

- Protocol BroucherDocument11 pagesProtocol Brouchermanojsingh474No ratings yet

- VLSI Interview Experience SynopsysDocument2 pagesVLSI Interview Experience SynopsysAkash KattaNo ratings yet

- 3165 BCA C 301 COA QBAnkDocument6 pages3165 BCA C 301 COA QBAnkDevipriya RajendranNo ratings yet

- CSE-MECS Super-Imp-Tie-22Document2 pagesCSE-MECS Super-Imp-Tie-22Shan MpNo ratings yet

- Esnug15 Final Submit Andersen Jensen Steffensen 20150616Document11 pagesEsnug15 Final Submit Andersen Jensen Steffensen 20150616shagu952No ratings yet

- DVCon Europe 2015 TA2 2 PaperDocument8 pagesDVCon Europe 2015 TA2 2 PaperJon DCNo ratings yet

- CAN Interview Questions: 1) What Is CAN and Its Uses?Document50 pagesCAN Interview Questions: 1) What Is CAN and Its Uses?satyakrishna electricalsNo ratings yet

- Performance Evaluation by Simulation and Analysis with Applications to Computer NetworksFrom EverandPerformance Evaluation by Simulation and Analysis with Applications to Computer NetworksNo ratings yet

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksFrom EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksNo ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Doulos SysVlog Interface Modports PaperDocument8 pagesDoulos SysVlog Interface Modports PaperkrishnaavNo ratings yet

- Integrated Circuit Fabrication Process Study Notes For ECEDocument9 pagesIntegrated Circuit Fabrication Process Study Notes For ECEkrishnaav100% (1)

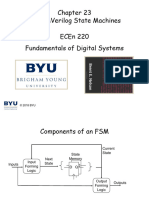

- FSM SVDocument23 pagesFSM SVkrishnaavNo ratings yet

- Sample Interview QuesitonsDocument2 pagesSample Interview QuesitonskrishnaavNo ratings yet

- Fpga Vs Asic Design FlowDocument32 pagesFpga Vs Asic Design FlowkrishnaavNo ratings yet

- Cmos Design Rules Layout PDFDocument33 pagesCmos Design Rules Layout PDFkrishnaavNo ratings yet

- Synopsys Test BenchDocument294 pagesSynopsys Test BenchkrishnaavNo ratings yet

- Sva CDC Paper Dvcon2006 PDFDocument6 pagesSva CDC Paper Dvcon2006 PDFkrishnaavNo ratings yet

- Bridge Axi AhbDocument22 pagesBridge Axi Ahbkrishnaav100% (1)

- Cadence ManualDocument51 pagesCadence Manualapi-27099960100% (4)

- MicroDocument20 pagesMicrokrishnaavNo ratings yet

- Improved Accuracy Current-Mode Multiplier Circuits With Applications in Analog Signal Processing PDFDocument5 pagesImproved Accuracy Current-Mode Multiplier Circuits With Applications in Analog Signal Processing PDFkrishnaavNo ratings yet

- K L University: Time: 3 Hours Max. Marks: 100Document1 pageK L University: Time: 3 Hours Max. Marks: 100krishnaavNo ratings yet

- Prasad HTC InvoiceDocument2 pagesPrasad HTC InvoicekrishnaavNo ratings yet

- Advanced Electronic Design Automation: VHDL Quick Reference GuideDocument47 pagesAdvanced Electronic Design Automation: VHDL Quick Reference GuidegokulchandruNo ratings yet

- Fpga-01 Sp3 Im ManualDocument67 pagesFpga-01 Sp3 Im ManualkrishnaavNo ratings yet