Professional Documents

Culture Documents

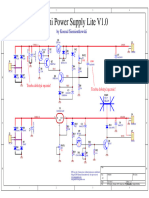

Wireless Shell Reference Hardware Design

Wireless Shell Reference Hardware Design

Uploaded by

BrentOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Wireless Shell Reference Hardware Design

Wireless Shell Reference Hardware Design

Uploaded by

BrentCopyright:

Available Formats

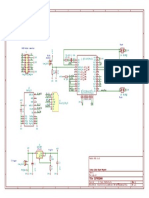

1 2 3 4 5 6 7 8

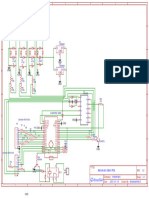

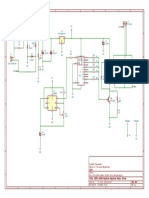

Programming Logic

USB1 F1 +5V

VUSB

1

R17 22R D_N

2 6V 500mA R18

R19 22R D_P

3 1k

4 D3

GND R20 D5

5 RSB6.8S

A 10k 1N5819 A

G Boot Mode Configuration

1

Header 5

U6 R4 10K

S1 3.3V

D3 2S 2 3 Auto-Reset

IN OUT 3.3V

Q4 EN

1 GND

GND GND AO3401 GND Boot Mode Configuration RESET C

S9013

C58 C59 Pin Default Boot Download C53 B R5 10K DTR

P-CH: G < S ON HT7333-1 10uF 1uF 4.7uF T1

C60 GPIO0 1 1 0 E

1uF U0TXD 1 1 x

GPIO2 0 x 0

GPIO4 0 x x

GND MTDO 1 x x

GND GND GND

GPIO5 1 1 x

U7 JP4

S9013

E

If U0TXD, GPIO2, GPIO5 are floating, R6 10K R7 10K RTS

4 3 VBAT S2 3.3V B

+5V VCC BAT 1 GPIO0 determines boot mode T2 C

C61 R21 2 2 0

GND GND

10uF 330R C63 If DTR is LOW, toggling RTS from HIGH to LOW resets to run mode. BTN-0

5 1 Header 2

PROG CHRG 220nF If RTS is HIGH, toggling DTR from LOW to HIGH resets to bootloader.

R22 TP4054

GND 2K

D4 GND GND GND

LED1

GND

B B

Power Supply

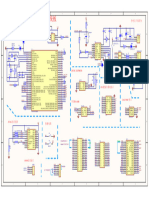

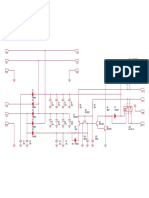

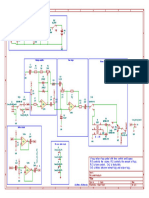

Wireless Shell module & 2.54 Headers USB - UART Bridge

U8 Wireless_Shell

+5V

JP2 JP3

C 1 44 37 32 +5V C

Vext Vext GND 20 20 R2

2 43 38 DIO1

Vext GND 19 19 U1 4.7K

39 DIO2 C1 1uF

18 18

3 42 EN 33 7 9

3.3V 3V3 GND 17 17 REGIN !RST

4 41 36 25 GND C2 0.1uF 8

3V3 GND 16 16 VBUS

21 DIO0 12

15 15 SUSPEND

LoRa_Reset 5 40 MOSI U0TXD 12 C3 1uF 6 11

LoRa_RST MOSI 14 14 VDD !SUSPEND

11 6 39 10 GND U0RXD 13 GND

GPIO11 GPIO10 13 13

6 7 38 9 22 15 D_P 4 2

GPIO6 GPIO9 12 12 D+ RI

7 8 37 17 MISO 2 1

GPIO7 GPIO17 11 11 DCD

8 9 36 16 23 0 D_N 5 28 DTR

GPIO8 GPIO16 10 10 D- DTR

SCK 10 35 4 CS 4 27

SCK GPIO4 9 9 DSR

CS 11 34 0 SCK 16 26 U0RXD

CS GPIO0 8 8 TXD

23 12 33 2 8 17 25 U0TXD

GPIO23 GPIO2 7 7 RXD

MISO 13 32 15 7 9 0 24 RTS

MISO GPIO15 6 6 GND@EXP RTS

22 14 31 13 6 10 3 23

GPIO22 GPIO13 D2 5 5 GND CTS

U0RXD 15 30 12 11 MOSI

RXD GPIO12 4 4

U0TXD 16 29 DIO0 LoRa_Reset GND CP2102

TXD DIO0 R9 3 3

21 17 28 25 GND GND

GPIO21 GPIO25 GND 2 2

36 18 27 33 10K

GPI 36 GPIO33 1 1

LED1

GPIO32

Header 20 Vext GND Header 20 +5V 3.3V GND

GPI 37

GPI 38

GPI 39

DIO2

DIO1

ANT

EN

19

20

21

22

23

24

25

26

DIO2

DIO1

ANT

D D

EN

37

38

39

32

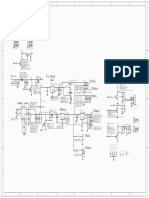

Title

Heltec Automation

Size Number Revision

E2 Wireless Shell Reference Hardware Design

A3

U.FL Antenna

Date: 2019/6/2 www.heltec.org

Sheet of

File: E:\DreamSpark\..\客户用原理图(基于V2).SchDoc

Drawn By:

1 2 3 4 5 6 7 8

You might also like

- BYHX SystemDocument13 pagesBYHX SystemErkan Kabakçı100% (4)

- Analog Isolation Module (V1.0) SchematicDocument1 pageAnalog Isolation Module (V1.0) Schematicbokic88100% (2)

- NKS PK-5000 PK-1000Document15 pagesNKS PK-5000 PK-1000FRANK NIELE DE OLIVEIRANo ratings yet

- Machine Learning Internship ReportDocument31 pagesMachine Learning Internship Reportsuchithra Nijaguna33% (9)

- WIFI Kit 32 Schematic Diagram V2Document1 pageWIFI Kit 32 Schematic Diagram V2Jose M. Paredes100% (2)

- WIFI Kit 32 Schematic Diagram V2Document1 pageWIFI Kit 32 Schematic Diagram V2Miguel Caldas100% (2)

- WIFI LoRa 32 V2 (868-915)Document1 pageWIFI LoRa 32 V2 (868-915)Pablo Parreño100% (1)

- Component Ratings: Reflow & Lamp ControllerDocument1 pageComponent Ratings: Reflow & Lamp ControllerKeith Dobbelaere100% (4)

- Schematic - Motomatic Nano With Clamps 800c - 2021-01!17!23!57!31Document1 pageSchematic - Motomatic Nano With Clamps 800c - 2021-01!17!23!57!31Vaishnavi LokhandeNo ratings yet

- Wizfi360: Lqfp48Document1 pageWizfi360: Lqfp48rdsonsantos0No ratings yet

- Schematic - ADAU1701 DSP AD8608 OP - 2020-08-28 - 12-57-02Document1 pageSchematic - ADAU1701 DSP AD8608 OP - 2020-08-28 - 12-57-02Ednilson FariaNo ratings yet

- 紫电a原理图Document1 page紫电a原理图treitenyNo ratings yet

- w5500 Ref Rj45with20150406 PDFDocument1 pagew5500 Ref Rj45with20150406 PDFTrần Linh100% (1)

- CVMV26L-G Schematic DiagramDocument6 pagesCVMV26L-G Schematic DiagrambelajartvkuNo ratings yet

- Catalex-Micro-SD-Card-Module-SCH ModificadoDocument1 pageCatalex-Micro-SD-Card-Module-SCH ModificadoBabobrillNo ratings yet

- Schematic PrintsDocument1 pageSchematic PrintsDân Kỹ Thuật100% (1)

- Previo 07 CompletoDocument2 pagesPrevio 07 CompletoRomeo Hernandez VillaNo ratings yet

- RGB LedDocument1 pageRGB LedJho CloworNo ratings yet

- ESP8266 For EPD-SCH092eDocument1 pageESP8266 For EPD-SCH092ejhonatan cock100% (1)

- Esp8266 For Epd-Sch092eDocument1 pageEsp8266 For Epd-Sch092ejhonatan cock100% (1)

- Dummy Load SCHDocument1 pageDummy Load SCHRemiFlores100% (1)

- Cybot Baseboard LCD SchematicDocument6 pagesCybot Baseboard LCD Schematicapi-584352705No ratings yet

- Pdf 文件使用 "Pdffactory Pro" 试用版本创建: Ic3 Cd4052Document1 pagePdf 文件使用 "Pdffactory Pro" 试用版本创建: Ic3 Cd4052Василий ЛитвинNo ratings yet

- Global RF 회로도 (B type) - 02Document4 pagesGlobal RF 회로도 (B type) - 02김진오No ratings yet

- Schematic - Inverter Egs HF - 2021-01-25Document1 pageSchematic - Inverter Egs HF - 2021-01-25Ihya Ulumuddin100% (1)

- Schematic Inverter Egs HF 2021-01-25Document1 pageSchematic Inverter Egs HF 2021-01-25Luis ValerianoNo ratings yet

- Schematic Inverter Egs HF 2021-01-25Document1 pageSchematic Inverter Egs HF 2021-01-25Penikmat Senja 6No ratings yet

- Schematic - Inverter Egs HF - 2021!01!25.Document1 pageSchematic - Inverter Egs HF - 2021!01!25.INFORCEL ELETRÔNICA E MARCENARIANo ratings yet

- Schematic Leach Amp 700W 2023-10-06Document1 pageSchematic Leach Amp 700W 2023-10-06Francisco MadridNo ratings yet

- 100V-240V Woshine Machine Motor Driver-DiagrameDocument1 page100V-240V Woshine Machine Motor Driver-DiagrameWasantha MunasinghaNo ratings yet

- TPS3839G33DBZR U3 U1: Low PowerDocument1 pageTPS3839G33DBZR U3 U1: Low Powermarcoteran007No ratings yet

- Psu 002Document1 pagePsu 002Harun ARIKNo ratings yet

- Schematic GhofranDocument1 pageSchematic GhofranGhofrane DaouasNo ratings yet

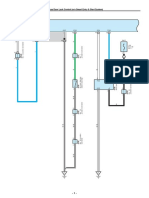

- Wireless Door Lock Control (W/o Smart Entry & Start System) : G33 (A), G34 (B)Document18 pagesWireless Door Lock Control (W/o Smart Entry & Start System) : G33 (A), G34 (B)CLC 18C4No ratings yet

- Company Name:Guangzhou Mingo Feijun Electronic Co., LTD Model No: PK 1000Document15 pagesCompany Name:Guangzhou Mingo Feijun Electronic Co., LTD Model No: PK 1000OdimarNo ratings yet

- NKS PK5000 PK1000Document15 pagesNKS PK5000 PK1000Adilson RochaNo ratings yet

- NKS PK5000 PK1000Document15 pagesNKS PK5000 PK1000Flavio de sousa oliveiraNo ratings yet

- NKS PK-5000 PK-1000Document15 pagesNKS PK-5000 PK-1000ala sousa LimaNo ratings yet

- NKS PK5000 PK1000Document15 pagesNKS PK5000 PK1000Flavio de sousa oliveiraNo ratings yet

- NKS PK-5000 PK-1000Document15 pagesNKS PK-5000 PK-1000Wagner LucianoNo ratings yet

- Clap CKTDocument2 pagesClap CKTMunavir k100% (1)

- TOPHOUSE - KONKA KDL32MD662LN - Diagrama Placa Única Principal y Fuente.Document13 pagesTOPHOUSE - KONKA KDL32MD662LN - Diagrama Placa Única Principal y Fuente.manuel cordobaNo ratings yet

- HelTec Wifi Kit 8 Schematics DiagramDocument1 pageHelTec Wifi Kit 8 Schematics DiagrammarcoNo ratings yet

- Konka KDL32MD662LN MSD6486 BGH Ble3218rtxDocument12 pagesKonka KDL32MD662LN MSD6486 BGH Ble3218rtxpedro100% (1)

- Pedal - PCBWay CommunityDocument1 pagePedal - PCBWay Communityheric fernandesNo ratings yet

- Flex PARKSIDE PWS125F6Document1 pageFlex PARKSIDE PWS125F6CatalinNo ratings yet

- Mach - Delay NPNDocument1 pageMach - Delay NPNNghia PhanNo ratings yet

- Cau H KHTDocument1 pageCau H KHTBảo NguyễnNo ratings yet

- UPD77C25 Programmer SchematicDocument3 pagesUPD77C25 Programmer SchematicAli Gachkar0% (1)

- Muzgaudio HV Semi Ps Lite v3Document1 pageMuzgaudio HV Semi Ps Lite v3slobodan.jovanovic.jaNo ratings yet

- Usb-Sata Rev.ADocument1 pageUsb-Sata Rev.Adigitalelectric2483No ratings yet

- Schematic Arduino+Solar+Charge+Controller+V2.0 Sheet 1 20200320104815Document1 pageSchematic Arduino+Solar+Charge+Controller+V2.0 Sheet 1 20200320104815Taha Chergui MouaneNo ratings yet

- Schematic Hand+Gesture+Car+Rx 2021-04-17Document1 pageSchematic Hand+Gesture+Car+Rx 2021-04-17REGINALDO BORIKO OKOMO NGUEMANo ratings yet

- Schematic - B - LM358 BATTERY TESTER - 2022-06-22Document1 pageSchematic - B - LM358 BATTERY TESTER - 2022-06-22usmfusmfNo ratings yet

- Lm358 Battery Voltage TesterDocument1 pageLm358 Battery Voltage TestermukhtarsafarofffNo ratings yet

- Autosteer ESP V1.2 SchematicsDocument1 pageAutosteer ESP V1.2 SchematicsŽivoin Bogdanov100% (1)

- Schematic MPPT Wind Turbine 2020-07!17!14!53!50Document1 pageSchematic MPPT Wind Turbine 2020-07!17!14!53!50Đức VõNo ratings yet

- Schematic MPPT Wind Turbine 2020-07!17!14!53!50Document1 pageSchematic MPPT Wind Turbine 2020-07!17!14!53!50Đức VõNo ratings yet

- Hisense Rsag7.820.1933 Psu SCHDocument10 pagesHisense Rsag7.820.1933 Psu SCHJuan Carlos CortesNo ratings yet

- Diagrama EsquemáticoDocument2 pagesDiagrama EsquemáticoJuan Sebastian GiraldoNo ratings yet

- Instructions ShoulderPocket PricklyGorseDocument19 pagesInstructions ShoulderPocket PricklyGorseBrentNo ratings yet

- Clamshellpouchjowizo 2Document2 pagesClamshellpouchjowizo 2BrentNo ratings yet

- RM-5 (Remote Meter)Document8 pagesRM-5 (Remote Meter)BrentNo ratings yet

- WebbingLadderTemplate USLetter PaperDocument2 pagesWebbingLadderTemplate USLetter PaperBrentNo ratings yet

- WebbingLadderTemplate A4 PaperDocument2 pagesWebbingLadderTemplate A4 PaperBrentNo ratings yet

- RBC3050D1S ManualDocument24 pagesRBC3050D1S ManualBrentNo ratings yet

- Cheat Sheet: A Brave NEW WorldDocument5 pagesCheat Sheet: A Brave NEW WorldBrentNo ratings yet

- FTGU Workbook FullDocument78 pagesFTGU Workbook FullBrent100% (1)

- Hybris Software Developer - AgendaDocument5 pagesHybris Software Developer - Agendavidhyaa1011No ratings yet

- ZXR10 T160G T64G Technical SpecificationsDocument61 pagesZXR10 T160G T64G Technical SpecificationsErnestoLopezGonzalezNo ratings yet

- Os-Module 1-Notes-1Document49 pagesOs-Module 1-Notes-1Sai SumanNo ratings yet

- Design of Micro Controllers For SafetyDocument50 pagesDesign of Micro Controllers For SafetyLuca BeniniNo ratings yet

- User's Manual: Wireless HeadphoneDocument77 pagesUser's Manual: Wireless HeadphoneGHAVBAN DAVIDNo ratings yet

- LogcatDocument149 pagesLogcatwww.gedeputra78No ratings yet

- The Contiki Operating System: Jack NosekDocument13 pagesThe Contiki Operating System: Jack NosekguruannamalaiNo ratings yet

- Industrial Training Report (SagarGarg)Document35 pagesIndustrial Training Report (SagarGarg)kartik guptaNo ratings yet

- Исупов Илья ИгоревичDocument4 pagesИсупов Илья ИгоревичSwinXNo ratings yet

- Homework # 1 SolutionDocument2 pagesHomework # 1 SolutionShayan Raza100% (2)

- SASE Vs SD WAN Beyond SecurityDocument11 pagesSASE Vs SD WAN Beyond SecurityEve AthanasekouNo ratings yet

- Windows Kernel Exploitation Tutorial Part 5: NULL Pointer DereferenceDocument7 pagesWindows Kernel Exploitation Tutorial Part 5: NULL Pointer DereferenceRonaldMartinezNo ratings yet

- EN111 42908990A IND690 and Weighing ModuleDocument12 pagesEN111 42908990A IND690 and Weighing ModuleJahir BallesterosNo ratings yet

- ID-FirePumpController-1 1 1Document71 pagesID-FirePumpController-1 1 1LUATNo ratings yet

- Project Management: Muhammad ZubairDocument21 pagesProject Management: Muhammad ZubairsweetwaqarNo ratings yet

- IPC 221 EngDocument50 pagesIPC 221 Engoscar perez perez nietoNo ratings yet

- BIN-3000A حضانة beingDocument2 pagesBIN-3000A حضانة beingالأمين ميديكالNo ratings yet

- Re-Com Profile 31 Jan 2022Document21 pagesRe-Com Profile 31 Jan 2022Acharya Rajiev GoelNo ratings yet

- Complete Audio Amplifier OpampDocument5 pagesComplete Audio Amplifier OpampdodifirmanNo ratings yet

- Simatic Hmi HMI Devices Migration Guide Comfort PanelsDocument52 pagesSimatic Hmi HMI Devices Migration Guide Comfort PanelsD Manmath RaoNo ratings yet

- Ficha Ténica Software Balanceo Bently NevadaDocument5 pagesFicha Ténica Software Balanceo Bently NevadaCAGERIGONo ratings yet

- November 2020 QP - Paper 1 OCR Computer Science A-LevelDocument24 pagesNovember 2020 QP - Paper 1 OCR Computer Science A-Levelvalerie luongNo ratings yet

- New Multi-Functional & Economical PLC: Plenty of I/O Points - 150 Points MaxDocument4 pagesNew Multi-Functional & Economical PLC: Plenty of I/O Points - 150 Points MaxGeorge Romero Carvalho NunesNo ratings yet

- Department of Computer Applications Syllabus For B.C.A. Under Choice Based Credit System (CBCS) For Candidates Admitted From 2019 - 2020Document39 pagesDepartment of Computer Applications Syllabus For B.C.A. Under Choice Based Credit System (CBCS) For Candidates Admitted From 2019 - 2020Saran VNo ratings yet

- Ims HSSRDocument642 pagesIms HSSRJOE SCHOLTZNo ratings yet

- 6188 PDFDocument24 pages6188 PDFMasudur RahmanNo ratings yet

- Data Visualization Using STEP Lothar KleinDocument31 pagesData Visualization Using STEP Lothar KleinacnonNo ratings yet

- Heathkit CR-1Document2 pagesHeathkit CR-1SamRNo ratings yet