Professional Documents

Culture Documents

Hardwired Controler Brief

Hardwired Controler Brief

Uploaded by

Deepak majhiCopyright:

Available Formats

You might also like

- Chapter1 - Basic Concepts & Computer - EvolutionDocument67 pagesChapter1 - Basic Concepts & Computer - EvolutionElias HedamoNo ratings yet

- Thumb-2 Instruction SetDocument11 pagesThumb-2 Instruction SetSai Keerthana DNo ratings yet

- CS501-Advance Computer Architecture: Solved MCQS From Final Term PapersDocument27 pagesCS501-Advance Computer Architecture: Solved MCQS From Final Term Papersmuhammad zulqarnainNo ratings yet

- Hardwired Controler BriefDocument2 pagesHardwired Controler BriefAKSHAT GARGNo ratings yet

- Basic Computer OrganizationMemory Reference InstructionsDocument9 pagesBasic Computer OrganizationMemory Reference InstructionsHARI HARAN REDDYNo ratings yet

- ch5 SolDocument9 pagesch5 Solblue_fire_englandNo ratings yet

- Samsung Plasma Training ManualDocument57 pagesSamsung Plasma Training Manualedsel72100% (2)

- Mk7a25p v06Document53 pagesMk7a25p v06אור מהללאל בן השםNo ratings yet

- Unit 2 Mcu PDFDocument12 pagesUnit 2 Mcu PDFatulNo ratings yet

- Lecture 29Document10 pagesLecture 29Roopali AgarwalNo ratings yet

- Chapter SevenDocument29 pagesChapter Sevenremi1989No ratings yet

- Lecture 24Document8 pagesLecture 24Roopali AgarwalNo ratings yet

- Week 04Document68 pagesWeek 04aroosa naheedNo ratings yet

- Design Task 1 Final LabDocument15 pagesDesign Task 1 Final Labrazorblademk2No ratings yet

- Lecture 21Document10 pagesLecture 21VINAYNo ratings yet

- Lecture 22Document8 pagesLecture 22VINAYNo ratings yet

- CombinepdfDocument14 pagesCombinepdfDuoDrenchNo ratings yet

- Lab 14Document10 pagesLab 14ubaidNo ratings yet

- PS2 EE SIO InfoDocument5 pagesPS2 EE SIO InfozokiNo ratings yet

- MicroControllers HandbookDocument13 pagesMicroControllers Handbookjhon doeNo ratings yet

- About 2G Integration (CIG, Alarms, Dump)Document4 pagesAbout 2G Integration (CIG, Alarms, Dump)Aziz AbassiNo ratings yet

- Hcs12 Instruction Set SummaryDocument15 pagesHcs12 Instruction Set SummaryRedduan HarisNo ratings yet

- Ccs-Picc - HTML: // LCD Module ConnectionsDocument5 pagesCcs-Picc - HTML: // LCD Module ConnectionsagreykatoNo ratings yet

- Basic Computer Organization and DesignDocument35 pagesBasic Computer Organization and DesignVinay KumarNo ratings yet

- CA SolutionDocument14 pagesCA SolutionSaba InamNo ratings yet

- Sechtor300 Job AidDocument10 pagesSechtor300 Job AidGreg WilliamsNo ratings yet

- Lecture-31 6. Rcond: This Is A Conditional Return Statement. It Is Also A Part ofDocument7 pagesLecture-31 6. Rcond: This Is A Conditional Return Statement. It Is Also A Part ofWilliamNo ratings yet

- F 818Document9 pagesF 818Eric YangNo ratings yet

- ph208 Up Slides 1bDocument6 pagesph208 Up Slides 1bHarshita TripathiNo ratings yet

- Lecture-25 7. SUB R: This Is A Single Byte Instruction. The Meaning of TheDocument9 pagesLecture-25 7. SUB R: This Is A Single Byte Instruction. The Meaning of TheWilliamNo ratings yet

- 08 GT E2530 Tshoo 7Document44 pages08 GT E2530 Tshoo 7Fabiomarferreira100% (1)

- Pic 16 F 628Document20 pagesPic 16 F 628Merényi Oszkár100% (1)

- General Description: MK7A25PDocument53 pagesGeneral Description: MK7A25Pאור מהללאל בן השםNo ratings yet

- Bapatla Engineering College Dept. of EceDocument9 pagesBapatla Engineering College Dept. of Ecevenkat1115No ratings yet

- ADCTest 2Document4 pagesADCTest 2JasonNo ratings yet

- Question No. 2 How Snmpv3 Enhances Security Compared To Snmpv2? Question No. 3 A) Define Rmon B) What Are The Benefits of Rmon ?Document32 pagesQuestion No. 2 How Snmpv3 Enhances Security Compared To Snmpv2? Question No. 3 A) Define Rmon B) What Are The Benefits of Rmon ?shravaniNo ratings yet

- 6803 Instruction Set (68HC11 Subset)Document93 pages6803 Instruction Set (68HC11 Subset)Saukani HalimNo ratings yet

- C12 Amp2Document24 pagesC12 Amp2maaian.iancuNo ratings yet

- 7-1 Overall Block DiagramDocument4 pages7-1 Overall Block DiagramCraig KalinowskiNo ratings yet

- CJ Instrucoes 8051Document6 pagesCJ Instrucoes 8051Luz Do Mundo PijamasNo ratings yet

- Lecture 26Document8 pagesLecture 26VINAYNo ratings yet

- Exercise - 4: EE443 - Embedded SystemsDocument4 pagesExercise - 4: EE443 - Embedded SystemscraticNo ratings yet

- Quad Power Amplifier With Built-In Voltage Converter: DescriptionDocument10 pagesQuad Power Amplifier With Built-In Voltage Converter: DescriptionbakaninhaNo ratings yet

- Atmega16 Enc28j60 WebserverDocument1 pageAtmega16 Enc28j60 WebserverTaher VohraNo ratings yet

- EE 739 Processor Design: Assignment 1 Vikas Jha 11D070024Document8 pagesEE 739 Processor Design: Assignment 1 Vikas Jha 11D070024VikasJhaNo ratings yet

- LPC 17xx ADC: Done byDocument13 pagesLPC 17xx ADC: Done byabu taherNo ratings yet

- Labv ModbusDocument5 pagesLabv ModbusNaat ZiedNo ratings yet

- Embedded SystemsDocument12 pagesEmbedded SystemsAl-Amin BhuiyanNo ratings yet

- IC 8155 InformationDocument13 pagesIC 8155 InformationKajol PhadtareNo ratings yet

- SD DataLoggerDocument1 pageSD DataLoggerSadikul FuadNo ratings yet

- Memory Reference Instructions ExecutionDocument13 pagesMemory Reference Instructions ExecutionAditya Singh100% (1)

- LMC-SSC2E16-01 Serial: User ManualDocument12 pagesLMC-SSC2E16-01 Serial: User ManualFred ShihNo ratings yet

- Intel CPU: Ddriii 800/1066/1333 Ddriii 800/1066/1333 Ics9Lrs3197AklftDocument50 pagesIntel CPU: Ddriii 800/1066/1333 Ddriii 800/1066/1333 Ics9Lrs3197Aklftdrop9721No ratings yet

- BSC Presentation VenezuelaDocument38 pagesBSC Presentation VenezuelaEddy NietoNo ratings yet

- Compaq Presario CQ45 SchematicsDocument48 pagesCompaq Presario CQ45 Schematicsmeng798651No ratings yet

- Embedded Systems: Prolific Systems and Technologies PVT LTDDocument17 pagesEmbedded Systems: Prolific Systems and Technologies PVT LTDJanmejaya MishraNo ratings yet

- The 8085 Chip: Ee309: Computer Organization, Architecture and MicroprocessorsDocument8 pagesThe 8085 Chip: Ee309: Computer Organization, Architecture and MicroprocessorsShashank DubeyNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Exercises in Electronics: Operational Amplifier CircuitsFrom EverandExercises in Electronics: Operational Amplifier CircuitsRating: 3 out of 5 stars3/5 (1)

- Programmable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysFrom EverandProgrammable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINo ratings yet

- DSP c28xDocument27 pagesDSP c28xalex6668No ratings yet

- EC6703 Embedded and Real Time SystemsDocument168 pagesEC6703 Embedded and Real Time Systemsramkumar100% (1)

- Abb-Plc Structure Text PDFDocument75 pagesAbb-Plc Structure Text PDFMicheleNo ratings yet

- Certificate in IT SyllabusDocument2 pagesCertificate in IT SyllabusKareemAdams9029No ratings yet

- Eti MCQ FinalDocument296 pagesEti MCQ FinalShubham waghule0% (1)

- Central Processing UnitDocument4 pagesCentral Processing UnitAvisek shresthaNo ratings yet

- Computer Organisation PYQ 2010 TO 2022 3RD SEM CSE ITDocument52 pagesComputer Organisation PYQ 2010 TO 2022 3RD SEM CSE ITKAJI AZAD ALINo ratings yet

- Technical Reference ManualDocument216 pagesTechnical Reference ManualpavankrishnatNo ratings yet

- Dealing With Multiple Machine Architectures (84273)Document3 pagesDealing With Multiple Machine Architectures (84273)tes firstNo ratings yet

- Xtensa ISADocument662 pagesXtensa ISADurga PrasadNo ratings yet

- Old SyllabusDocument54 pagesOld SyllabusShivraj C ShekharNo ratings yet

- Self-Paced Learning Module: Senior High SchoolDocument8 pagesSelf-Paced Learning Module: Senior High Schoolvhenzhar saycoNo ratings yet

- CA S8 AssemblyDocument87 pagesCA S8 AssemblyVani VasudevanNo ratings yet

- Delta Compact Modular Mid-Range PLC AS SeriesDocument52 pagesDelta Compact Modular Mid-Range PLC AS SeriesXiaofeng XuNo ratings yet

- 196 01176 0 HT48C06Document37 pages196 01176 0 HT48C06trattoriapizzeriapassioneNo ratings yet

- Logical Instructions in 8086 Micro ProcessorDocument21 pagesLogical Instructions in 8086 Micro ProcessorGANGADHARA SAIPRASANNANo ratings yet

- 9618 s22 QP 13 PDFDocument16 pages9618 s22 QP 13 PDFSunnatbek Meliqo'ziyevNo ratings yet

- Institute of Aeronautical Engineering (Autonomous) : Electronics and Communication EngineeringDocument23 pagesInstitute of Aeronautical Engineering (Autonomous) : Electronics and Communication EngineeringMano HarNo ratings yet

- PLC Teco Tp02Manual (En)Document282 pagesPLC Teco Tp02Manual (En)sunhuynhNo ratings yet

- Module 3 (Part1)Document28 pagesModule 3 (Part1)vidhya_bineeshNo ratings yet

- Topic On Micro Controller and It'S ApplicationDocument7 pagesTopic On Micro Controller and It'S ApplicationKhaleda AkterNo ratings yet

- PIC Microprocessor Circuit DesignDocument308 pagesPIC Microprocessor Circuit Designcybhunter007No ratings yet

- Lecture 8 FSMDocument41 pagesLecture 8 FSMrahulNo ratings yet

- Chapter 3.1 - Instruction SetDocument30 pagesChapter 3.1 - Instruction SetcudarunNo ratings yet

- COA Unit-1Document284 pagesCOA Unit-1Amanuel DagetNo ratings yet

- Microprocessor and Interfacing Devices/Peripherals: 8086 Instructions SetDocument24 pagesMicroprocessor and Interfacing Devices/Peripherals: 8086 Instructions Setvikas chawlaNo ratings yet

- 01 BasicsDocument19 pages01 Basicsasakr8481No ratings yet

Hardwired Controler Brief

Hardwired Controler Brief

Uploaded by

Deepak majhiOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Hardwired Controler Brief

Hardwired Controler Brief

Uploaded by

Deepak majhiCopyright:

Available Formats

Hard-wired Controller

Hardware components-

Memory (4096*16bit)

MDR,AC -16bit

MAR, PC -12bit

(PC with (E,L,I,C), MAR with (E,L,I,C), and MDR with(E,L,I) signals)

Input output registers- INP, OUP - 8bit

ALU works with AC(E,L) only and carry is stored in flag E

Interrupt flag R (R sets When IE is set and any or both of FGI/FGO set)(when processor s interrupted , interrupt cycle reset R)

Interrupt Enable Flip flop is IE (set / reset by instruction ION / IOF)

Input and Output operation also set/reset flags FGI and FGO

(FGI set when external device write data in INP register. When INP is read by processor FGI resets )

(FGO is reset by processor when new data is written in OUP. Set by external device when it reads OUP)

A sequence Counter(SC) generates 8 clocks (SC is reset by instruction after its completion. Disable signal to Clock is controlled by instruction HLT.

Clock is enabled from external switch)

Following instructions are incorporated-

memory reference instructions-

AND, ADD, LDA, STA, BUN(branch unconditional), BSA(branch and save return address), ISZ (increment memory and skip next instruction if memory

becomes zero)

(these are MRI. Memory can be referred directly (given address contains info. ) or indirectly (given address contains the address where the info. Is stored ) )

Non MRI -Register based instructions-

CLA (AC=0), CLE(E=0), CMA(AC=1's complement of A), CME(E=1's complement of E), CIR(AC rotates right with E),CIL(AC rotates LEFT with

E),INC(Ac=AC+1), SPA(skip next instruction if A15=0),SNA(skip next instruction if A15=1),SZA(skip next instruction if AC=0),SZE(skip next instruction if

E=0),HLT(disable sequence generator)

Non MRI -I/O based instructions-

IN,OUT,SKI(skip next instruction if FGI=1),SKO(skip next instruction if FGO=1),ION(enable IE F/F),IOF(disable IE F/F)

Format of16-bit instruction-

15 14 12 11 0

I opcode Address/non mri inst. bits

3-bits of opcode selects one of the 7 mri instruction(opcode bits- 000 to 110) or non mri instructions(111)

I in case of mri , identifies direct(I=0) or indirect (I=1) instructions

in case of non-mri instructions register ref. (I=0) or I/O ref.(I=1) instructions

12-bit , in mri refers address, in case of non-mri it identifies one of register or I/O instruction

Flow chart of normal instruction execution-

Flow chart of interrupt execution-

Micro operations of hardwired controller

(normal execution R=0)

RT0 : MAR <- PC

RT1 : MDR<- M[MAR] , PC <- PC+1

RT2 : MAR <- MDR(11-0), I <- MDR(15), Decoder <-MDR(14-12)

(interrupt execution when R=1, first two memory locations for interrupt handling data and instruction)

RT0 : MAR <- 0, MDR<-PC

RT1 : M[MAR] <- MDR

RT2 : PC <- 0

RT3 : PC <- 1 , IEN <- 0 ,R <- 0 ;Reset

(In non-mri instruction, when I=0, T3,T4 cycle is idle)

D7IT3 : MDR <- M[MAR]

D7IT4 : MAR <- MDR

memory reference Instructions

AND BUN

D0T5 : MDR <- M[MAR] D4T5 : PC <-MAR ; Reset

D0T6 :AC <-AC . MDR ; Reset

ADD BSA

D1T5 : MDR <- M[MAR] D5T5 : MDR <-PC

D1T6 : AC <-AC + MDR ,E <-Cout ; Reset D5T6 : M[MAR]<- MDR; MAR <-MAR+1

D5T7 : PC <-MAR ; Reset

LDA ISZ

D2T5 : MDR <- M[MAR] D6T5 : MDR <- M[MAR]

D2T6 : AC <-MDR ; Reset D6T6 : MDR <-MDR+1

D6T7 : M[MAR] <-MDR; if MDR=0 then PC<-PC+1 : Reset

STA

D3T5 : MDR <-AC ; Reset

D3T6 : M[MAR] <-MDR ; Reset

Register instructions- I/O instructions-

D7I (conditional for register reference instruction) D7I (conditional for I/O reference instruction) Address

Address bits- b11 to b0 used to identify particular bits- b11 to b0 used to identify particular instruction

instruction D7IT3b11 – IN ; AC< INP, FGI=0; Reset

D7IT3b11 - CLA ; AC<-0; Reset D7IT3b10 – OUT ; OUP<-AC, FGO=0; Reset

D7IT3b10 - CLE ; E<-0; Reset D7IT3b9 – SKI ; if FGI =1 ,PC<-PC+1 ; Reset

D7IT3b9 - CMA ; AC<- 1's complement of AC; Reset D7IT3b8 – SKO ; if FGO =1 ,PC<-PC+1 ; Reset

D7IT3b8 - CME ; E<- 1's complement of E; Reset D7IT3b7 – ION ; IE=1 ; Reset

D7IT3b7 – CIR ; A15<-E,...............E<-A0; Reset D7IT3b6 – IOF ; IE=0 ; Reset

D7IT3b6 – CIL ; A0<-E,...............E<-A15; Reset

D7IT3b5 – INC ; AC<- AC+1; Reset

D7IT3b4 – SPA ; if A15=0 , PC<-PC+1 ; Reset

D7IT3b3 – SNA ; if A15=1 , PC<-PC+1 ; Reset

D7IT3b2 – SZA ; if AC=0 , PC<-PC+1 ; Reset

D7IT3b1 – SZE ; if E=0 , PC<-PC+1 ; Reset

D7IT3b0 – HLT ;disable clock

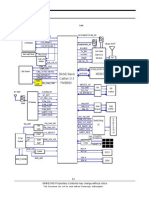

Logical circuit for Control signals using logic gates (OR gate , AND gate) with decoded bits of MDR and output of sequence counter as input

example for PC- has four control signals – enable(read), load(write),increment and clear with sequence counter and decoded bits of the MDR

PC(E) – T0+D5T5

PC(L) - D4T5+D5T7

PC(I)- RT1+RT3+D6T7(MDR)+D7IT3b4(A15)+D7IT3b3(A15)+D7IT3b2(AC)+D7IT3b1(E)+D7IT3b9(FGI)+D7IT3b8(FGO)

PC(C) - RT2

Design combinational Logical circuit using these control signals for PC

MAR- has four control signals – enable(read), load(write),increment, clear and sequence counter

MDR- has three control signals – enable(read), load(write),increment, and sequence counter

Memory- has two control signals – enable(read), load(write),

AC -

Circuit for interrupt ( R and IE flags)

(T0 .T1 .T2 ). (IE).(FGI+FGO) sets R flag

Complete schematic diagram showing all hardware components ,and logic circuit to generate control signals -

You might also like

- Chapter1 - Basic Concepts & Computer - EvolutionDocument67 pagesChapter1 - Basic Concepts & Computer - EvolutionElias HedamoNo ratings yet

- Thumb-2 Instruction SetDocument11 pagesThumb-2 Instruction SetSai Keerthana DNo ratings yet

- CS501-Advance Computer Architecture: Solved MCQS From Final Term PapersDocument27 pagesCS501-Advance Computer Architecture: Solved MCQS From Final Term Papersmuhammad zulqarnainNo ratings yet

- Hardwired Controler BriefDocument2 pagesHardwired Controler BriefAKSHAT GARGNo ratings yet

- Basic Computer OrganizationMemory Reference InstructionsDocument9 pagesBasic Computer OrganizationMemory Reference InstructionsHARI HARAN REDDYNo ratings yet

- ch5 SolDocument9 pagesch5 Solblue_fire_englandNo ratings yet

- Samsung Plasma Training ManualDocument57 pagesSamsung Plasma Training Manualedsel72100% (2)

- Mk7a25p v06Document53 pagesMk7a25p v06אור מהללאל בן השםNo ratings yet

- Unit 2 Mcu PDFDocument12 pagesUnit 2 Mcu PDFatulNo ratings yet

- Lecture 29Document10 pagesLecture 29Roopali AgarwalNo ratings yet

- Chapter SevenDocument29 pagesChapter Sevenremi1989No ratings yet

- Lecture 24Document8 pagesLecture 24Roopali AgarwalNo ratings yet

- Week 04Document68 pagesWeek 04aroosa naheedNo ratings yet

- Design Task 1 Final LabDocument15 pagesDesign Task 1 Final Labrazorblademk2No ratings yet

- Lecture 21Document10 pagesLecture 21VINAYNo ratings yet

- Lecture 22Document8 pagesLecture 22VINAYNo ratings yet

- CombinepdfDocument14 pagesCombinepdfDuoDrenchNo ratings yet

- Lab 14Document10 pagesLab 14ubaidNo ratings yet

- PS2 EE SIO InfoDocument5 pagesPS2 EE SIO InfozokiNo ratings yet

- MicroControllers HandbookDocument13 pagesMicroControllers Handbookjhon doeNo ratings yet

- About 2G Integration (CIG, Alarms, Dump)Document4 pagesAbout 2G Integration (CIG, Alarms, Dump)Aziz AbassiNo ratings yet

- Hcs12 Instruction Set SummaryDocument15 pagesHcs12 Instruction Set SummaryRedduan HarisNo ratings yet

- Ccs-Picc - HTML: // LCD Module ConnectionsDocument5 pagesCcs-Picc - HTML: // LCD Module ConnectionsagreykatoNo ratings yet

- Basic Computer Organization and DesignDocument35 pagesBasic Computer Organization and DesignVinay KumarNo ratings yet

- CA SolutionDocument14 pagesCA SolutionSaba InamNo ratings yet

- Sechtor300 Job AidDocument10 pagesSechtor300 Job AidGreg WilliamsNo ratings yet

- Lecture-31 6. Rcond: This Is A Conditional Return Statement. It Is Also A Part ofDocument7 pagesLecture-31 6. Rcond: This Is A Conditional Return Statement. It Is Also A Part ofWilliamNo ratings yet

- F 818Document9 pagesF 818Eric YangNo ratings yet

- ph208 Up Slides 1bDocument6 pagesph208 Up Slides 1bHarshita TripathiNo ratings yet

- Lecture-25 7. SUB R: This Is A Single Byte Instruction. The Meaning of TheDocument9 pagesLecture-25 7. SUB R: This Is A Single Byte Instruction. The Meaning of TheWilliamNo ratings yet

- 08 GT E2530 Tshoo 7Document44 pages08 GT E2530 Tshoo 7Fabiomarferreira100% (1)

- Pic 16 F 628Document20 pagesPic 16 F 628Merényi Oszkár100% (1)

- General Description: MK7A25PDocument53 pagesGeneral Description: MK7A25Pאור מהללאל בן השםNo ratings yet

- Bapatla Engineering College Dept. of EceDocument9 pagesBapatla Engineering College Dept. of Ecevenkat1115No ratings yet

- ADCTest 2Document4 pagesADCTest 2JasonNo ratings yet

- Question No. 2 How Snmpv3 Enhances Security Compared To Snmpv2? Question No. 3 A) Define Rmon B) What Are The Benefits of Rmon ?Document32 pagesQuestion No. 2 How Snmpv3 Enhances Security Compared To Snmpv2? Question No. 3 A) Define Rmon B) What Are The Benefits of Rmon ?shravaniNo ratings yet

- 6803 Instruction Set (68HC11 Subset)Document93 pages6803 Instruction Set (68HC11 Subset)Saukani HalimNo ratings yet

- C12 Amp2Document24 pagesC12 Amp2maaian.iancuNo ratings yet

- 7-1 Overall Block DiagramDocument4 pages7-1 Overall Block DiagramCraig KalinowskiNo ratings yet

- CJ Instrucoes 8051Document6 pagesCJ Instrucoes 8051Luz Do Mundo PijamasNo ratings yet

- Lecture 26Document8 pagesLecture 26VINAYNo ratings yet

- Exercise - 4: EE443 - Embedded SystemsDocument4 pagesExercise - 4: EE443 - Embedded SystemscraticNo ratings yet

- Quad Power Amplifier With Built-In Voltage Converter: DescriptionDocument10 pagesQuad Power Amplifier With Built-In Voltage Converter: DescriptionbakaninhaNo ratings yet

- Atmega16 Enc28j60 WebserverDocument1 pageAtmega16 Enc28j60 WebserverTaher VohraNo ratings yet

- EE 739 Processor Design: Assignment 1 Vikas Jha 11D070024Document8 pagesEE 739 Processor Design: Assignment 1 Vikas Jha 11D070024VikasJhaNo ratings yet

- LPC 17xx ADC: Done byDocument13 pagesLPC 17xx ADC: Done byabu taherNo ratings yet

- Labv ModbusDocument5 pagesLabv ModbusNaat ZiedNo ratings yet

- Embedded SystemsDocument12 pagesEmbedded SystemsAl-Amin BhuiyanNo ratings yet

- IC 8155 InformationDocument13 pagesIC 8155 InformationKajol PhadtareNo ratings yet

- SD DataLoggerDocument1 pageSD DataLoggerSadikul FuadNo ratings yet

- Memory Reference Instructions ExecutionDocument13 pagesMemory Reference Instructions ExecutionAditya Singh100% (1)

- LMC-SSC2E16-01 Serial: User ManualDocument12 pagesLMC-SSC2E16-01 Serial: User ManualFred ShihNo ratings yet

- Intel CPU: Ddriii 800/1066/1333 Ddriii 800/1066/1333 Ics9Lrs3197AklftDocument50 pagesIntel CPU: Ddriii 800/1066/1333 Ddriii 800/1066/1333 Ics9Lrs3197Aklftdrop9721No ratings yet

- BSC Presentation VenezuelaDocument38 pagesBSC Presentation VenezuelaEddy NietoNo ratings yet

- Compaq Presario CQ45 SchematicsDocument48 pagesCompaq Presario CQ45 Schematicsmeng798651No ratings yet

- Embedded Systems: Prolific Systems and Technologies PVT LTDDocument17 pagesEmbedded Systems: Prolific Systems and Technologies PVT LTDJanmejaya MishraNo ratings yet

- The 8085 Chip: Ee309: Computer Organization, Architecture and MicroprocessorsDocument8 pagesThe 8085 Chip: Ee309: Computer Organization, Architecture and MicroprocessorsShashank DubeyNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Exercises in Electronics: Operational Amplifier CircuitsFrom EverandExercises in Electronics: Operational Amplifier CircuitsRating: 3 out of 5 stars3/5 (1)

- Programmable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysFrom EverandProgrammable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINo ratings yet

- DSP c28xDocument27 pagesDSP c28xalex6668No ratings yet

- EC6703 Embedded and Real Time SystemsDocument168 pagesEC6703 Embedded and Real Time Systemsramkumar100% (1)

- Abb-Plc Structure Text PDFDocument75 pagesAbb-Plc Structure Text PDFMicheleNo ratings yet

- Certificate in IT SyllabusDocument2 pagesCertificate in IT SyllabusKareemAdams9029No ratings yet

- Eti MCQ FinalDocument296 pagesEti MCQ FinalShubham waghule0% (1)

- Central Processing UnitDocument4 pagesCentral Processing UnitAvisek shresthaNo ratings yet

- Computer Organisation PYQ 2010 TO 2022 3RD SEM CSE ITDocument52 pagesComputer Organisation PYQ 2010 TO 2022 3RD SEM CSE ITKAJI AZAD ALINo ratings yet

- Technical Reference ManualDocument216 pagesTechnical Reference ManualpavankrishnatNo ratings yet

- Dealing With Multiple Machine Architectures (84273)Document3 pagesDealing With Multiple Machine Architectures (84273)tes firstNo ratings yet

- Xtensa ISADocument662 pagesXtensa ISADurga PrasadNo ratings yet

- Old SyllabusDocument54 pagesOld SyllabusShivraj C ShekharNo ratings yet

- Self-Paced Learning Module: Senior High SchoolDocument8 pagesSelf-Paced Learning Module: Senior High Schoolvhenzhar saycoNo ratings yet

- CA S8 AssemblyDocument87 pagesCA S8 AssemblyVani VasudevanNo ratings yet

- Delta Compact Modular Mid-Range PLC AS SeriesDocument52 pagesDelta Compact Modular Mid-Range PLC AS SeriesXiaofeng XuNo ratings yet

- 196 01176 0 HT48C06Document37 pages196 01176 0 HT48C06trattoriapizzeriapassioneNo ratings yet

- Logical Instructions in 8086 Micro ProcessorDocument21 pagesLogical Instructions in 8086 Micro ProcessorGANGADHARA SAIPRASANNANo ratings yet

- 9618 s22 QP 13 PDFDocument16 pages9618 s22 QP 13 PDFSunnatbek Meliqo'ziyevNo ratings yet

- Institute of Aeronautical Engineering (Autonomous) : Electronics and Communication EngineeringDocument23 pagesInstitute of Aeronautical Engineering (Autonomous) : Electronics and Communication EngineeringMano HarNo ratings yet

- PLC Teco Tp02Manual (En)Document282 pagesPLC Teco Tp02Manual (En)sunhuynhNo ratings yet

- Module 3 (Part1)Document28 pagesModule 3 (Part1)vidhya_bineeshNo ratings yet

- Topic On Micro Controller and It'S ApplicationDocument7 pagesTopic On Micro Controller and It'S ApplicationKhaleda AkterNo ratings yet

- PIC Microprocessor Circuit DesignDocument308 pagesPIC Microprocessor Circuit Designcybhunter007No ratings yet

- Lecture 8 FSMDocument41 pagesLecture 8 FSMrahulNo ratings yet

- Chapter 3.1 - Instruction SetDocument30 pagesChapter 3.1 - Instruction SetcudarunNo ratings yet

- COA Unit-1Document284 pagesCOA Unit-1Amanuel DagetNo ratings yet

- Microprocessor and Interfacing Devices/Peripherals: 8086 Instructions SetDocument24 pagesMicroprocessor and Interfacing Devices/Peripherals: 8086 Instructions Setvikas chawlaNo ratings yet

- 01 BasicsDocument19 pages01 Basicsasakr8481No ratings yet