Professional Documents

Culture Documents

MP9943

MP9943

Uploaded by

techgamebr85Original Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

MP9943

MP9943

Uploaded by

techgamebr85Copyright:

Available Formats

MP9943

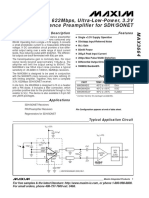

High Efficiency 3A Peak, 36V,

Synchronous Step Down Converter

The Future of Analog IC Technology With Power Good

DESCRIPTION FEATURES

The MP9943 is a high-frequency, synchronous, Wide 4V to 36V Continuous Operating Input

rectified, step-down, switch-mode converter Range

with built-in power MOSFETs. It offers a very 85mΩ/55mΩ Low RDS(ON) Internal Power

compact solution to achieve a 3A peak output MOSFETs

current with excellent load and line regulation High-Efficiency Synchronous Mode Operation

over a wide input supply range. The MP9943 410kHz Switching Frequency

has synchronous mode operation for higher Synchronizes from 200kHz to 2.2MHz

efficiency over the output current load range. External Clock

Current-mode operation provides fast transient High Duty Cycle for Automotive Cold-crank

response and eases loop stabilization. Internal Power-Save Mode

Internal Soft-Start

Full protection features include over-current

protection and thermal shutdown. Power Good Indicator

Over Current Protection and Hiccup

The MP9943 requires a minimal number of Thermal Shutdown

readily-available standard external components, Output Adjustable from 0.8V

and is available in a space-saving QFN-8 Available in an QFN-8 (3mmx3mm)

(3mmx3mm) package. package

APPLICATIONS

General Consumer

Multi-Function Printers (MFP)

Distributed Power Systems

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green

status, please visit MPS website under Quality Assurance. “MPS” and “The

Future of Analog IC Technology” are Registered Trademarks of Monolithic

Power Systems, Inc.

TYPICAL APPLICATION

MP9943 Rev.1.1 www.MonolithicPower.com 1

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

ORDERING INFORMATION

Part Number* Package Top Marking

MP9943GQ QFN-8 (3mmх3mm) See Below

* For Tape & Reel, add suffix –Z (e.g. MP9943GQ–Z);

TOP MARKING

AMG: product code of MP9943GQ;

Y: year code;

LLL: lot number;

PACKAGE REFERENCE

TOP VIEW

FB 1 8 PG

VCC 2 7 IN

EN/SYNC 3 6 SW

BST 4 5 GND

QFN-8 (3mmх3mm)

MP9943 Rev.1.1 www.MonolithicPower.com 2

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

ABSOLUTE MAXIMUM RATINGS (1) Thermal Resistance

(5)

θJA θJC

VIN .................................................. -0.3V to 40V QFN-8 (3mmx3mm) ............... 55 ...... 13... °C/W

VSW .................................................. -0.3V to 41V

Notes:

VBS ......................................................... VSW+6V 1) Absolute maximum ratings are rated under room temperature

All Other Pins ................................ -0.3V to 6V (2) unless otherwise noted. Exceeding these ratings may

(3) damage the device.

Continuous Power Dissipation (TA = +25°C) 2) About the details of EN/SYNC pin’s ABS MAX rating, please

QFN-8 (3mmx3mm) ................................. 2.27W refer to page 12, Enable/SYNC control section.

Junction Temperature ...............................150°C 3) The maximum allowable power dissipation is a function of the

maximum junction temperature TJ (MAX), the junction-to-

Lead Temperature ....................................260°C ambient thermal resistance θJA, and the ambient temperature

Storage Temperature ................. -65°C to 150°C TA. The maximum allowable continuous power dissipation at

any ambient temperature is calculated by PD (MAX) = (TJ

Recommended Operating Conditions(4) (MAX)-TA)/θJA. Exceeding the maximum allowable power

dissipation will cause excessive die temperature, and the

Continuous Supply Voltage VIN ........... 4V to 36V regulator will go into thermal shutdown. Internal thermal

Output Voltage VOUT .................. 0.8V to DMaxхVIN shutdown circuitry protects the device from permanent

Operating Junction Temp (TJ). . -40°C to +125°C damage.

4) The device is not guaranteed to function outside of its

operation condition.

5) Measured on JESD51-7, 4-layer PCB.

MP9943 Rev.1.1 www.MonolithicPower.com 3

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

ELECTRICAL CHARACTERISTICS

VIN = 12V, TJ = +25°C, unless otherwise noted.

Parameter Symbol Condition Min Typ Max Units

Supply Current (Shutdown) ISHDN VEN = 0V 8 μA

Supply Current (Quiescent) IQ VEN = 2V, VFB = 1V 0.5 0.7 mA

HS Switch-ON Resistance RON_HS VBST-SW=5V 85 105 mΩ

LS Switch-ON Resistance RON_LS VCC =5V 55 75 mΩ

Switch Leakage ILKG_SW VEN = 0V, VSW =12V 1 μA

Current Limit ILIMIT Under 40% Duty Cycle 3.2 4.4 5.5 A

Oscillator Frequency fSW VFB=750mV 320 410 500 kHz

Fold-Back Frequency fFB VFB<400mV 70 100 130 kHz

Maximum Duty Cycle DMAX VFB=750mV, 410kHz 92 95 %

Minimum ON Time(6) tON_MIN 70 ns

Sync Frequency Range fSYNC 0.2 2.4 MHz

Feedback Voltage VFB 778 792 806 mV

Feedback Current IFB VFB=820mV 10 100 nA

EN Rising Threshold VEN_RISING 1.15 1.4 1.65 V

EN Falling Threshold VEN_FALLING 1.05 1.25 1.45 V

EN Threshold Hysteresis VEN_HYS 150 mV

VEN=2V 4 6 μA

EN Input Current IEN

VEN=0 0 0.2 μA

VIN Under-Voltage Lockout

INUVRISING 3.3 3.5 3.7 V

Threshold-Rising

VIN Under-Voltage Lockout

INUVFALLING 3.1 3.3 3.5 V

Threshold-Falling

VIN Under-Voltage Lockout

INUVHYS 200 mV

Threshold-Hysteresis

VCC Regulator VCC ICC=0mA 4.6 4.9 5.2 V

VCC Load Regulation ICC=5mA 1.5 4 %

Soft-Start Period tSS VOUT from 10% to 90% 0.45 1. 5 2.55 ms

Thermal Shutdown (6) TSD 150 170 °C

Thermal Hysteresis (6) TSD_HYS 30 °C

PG Rising Threshold PGVth_RISING as percentage of VFB 86 90 94 %

PG Falling Threshold PGVth FALLING as percentage of VFB 80 84 88 %

MP9943 Rev.1.1 www.MonolithicPower.com 4

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

ELECTRICAL CHARACTERISTICS (continued)

VIN = 12V, TJ = +25°C, unless otherwise noted.

Parameter Symbol Condition Min Typ Max Units

PG Threshold Hysteresis PGVth_HYS as percentage of VFB 6 %

PG Rising Delay PGTd_RISING 40 90 160 μs

PG Falling Delay PGTd_FALLING 30 55 95 μs

PG Sink Current Capability VPG Sink 4mA 0.1 0.3 V

PG Leakage Current ILKG_PG 10 100 nA

Notes:

6) Derived from bench characterization. Not tested in production.

MP9943 Rev.1.1 www.MonolithicPower.com 5

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

TYPICAL PERFORMANCE CHARACTERISTICS

VIN = 12V, VOUT = 3.3V, L = 10µH, RBST=20Ω, TA = +25°C, unless otherwise noted.

MP9943 Rev.1.1 www.MonolithicPower.com 6

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

TYPICAL PERFORMANCE CHARACTERISTICS

VIN = 12V, VOUT = 3.3V, L = 10µH, RBST=20Ω, TA = +25°C, unless otherwise noted.

MP9943 Rev.1.1 www.MonolithicPower.com 7

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

TYPICAL PERFORMANCE CHARACTERISTICS

VIN = 12V, VOUT = 3.3V, L = 10µH, RBST=20Ω, TA = +25°C, unless otherwise noted.

MP9943 Rev.1.1 www.MonolithicPower.com 8

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

TYPICAL PERFORMANCE CHARACTERISTICS

VIN = 12V, VOUT = 3.3V, L = 10µH, RBST=20Ω, TA = +25°C, unless otherwise noted.

MP9943 Rev.1.1 www.MonolithicPower.com 9

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

PIN FUNCTIONS

Package

Name Description

Pin #

Feedback. Connect to the tap of an external resistor divider from the output to GND, to set

the output voltage. The frequency fold-back comparator lowers the oscillator frequency

1 FB

when the FB voltage is below 660mV to prevent current limit runaway during a short-circuit

fault condition.

Bias Supply. Decouple with 0.1μF-to-0.22μF capacitor. Select a capacitor that does not

2 VCC

exceed 0.22μF

Enable/Synchronize. EN/SYNC high to enable the MP9943. Apply an external clock to the

3 EN/SYNC

EN/SYNC pin to change the switching frequency.

Bootstrap. Requires a capacitor connected between SW and BST pins to form a floating

4 BST supply across the high-side switch driver. A 20Ω resistor placed between SW and BST cap

is strongly recommended to reduce SW spike voltage.

System Ground. This pin is the reference ground of the regulated output voltage, and PCB

5 GND

layout requires special care. For best results, connect to GND with copper traces and vias.

6 SW Switch Output. Connect with a wide PCB trace.

Supply Voltage Input. The MP9943 operates from a 4V to 36V input rail. Requires C1 to

7 IN

decouple the input rail. Connect using a wide PCB trace.

Power Good. The output of this pin is an open drain and goes high if the output voltage

8 PG

exceeds 90% of the nominal voltage.

MP9943 Rev.1.1 www.MonolithicPower.com 10

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

FUNCTIONAL BLOCK DIAGRAM

Figure 1: Functional Block Diagram

MP9943 Rev.1.1 www.MonolithicPower.com 11

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

OPERATION

Under the light load condition, the value of VCOMP

The MP9943 is a high-frequency, synchronous, is low. When VCOMP is less than VAAM and VFB is

rectified, step-down, switch-mode converter with less than VREF, VCOMP ramps up until it exceeds

built-in power MOSFETs. It offers a very compact VAAM. During this time, the internal clock is

solution to achieve 3A peak output current with blocked, thus the MP9943 skips some pulses for

excellent load and line regulation over a wide PFM (Pulse Frequency Modulation) mode and

input supply range. achieves the light load power save.

When MP9943 operates in a fixed-frequency,

peak-current–control mode to regulate the output

voltage. An internal clock initiates a PWM cycle.

The integrated high-side power MOSFET turns

on and remains on until its current reaches the

value set by the COMP voltage. When the power

switch is off, it remains off until the next clock

cycle starts. If the current in the power MOSFET Figure 2: Simplified AAM Control Logic

does not reach the current value set by COMP

within 95% of one PWM period, the power Enable/SYNC control

MOSFET will be forced to turn off. EN/SYNC is a digital control pin that turns the

Internal Regulator regulator on and off: Drive EN/SYNC high to turn

The 5V internal regulator power most of the on the regulator, drive it low to turn it off. An

internal circuitries. This regulator is supplied by internal 500kΩ resistor from EN/SYNC to GND

the VIN input and operates in the full VIN range: allows EN/SYNC to be floated to shut down the

When VIN exceeds 5.0V, the output of the chip.

regulator is in full regulation; when VIN falls below The EN/SYNC pin is clamped internally using a

5.0V, the output of the regulator decreases 6.5V series Zener diode, as shown in Figure 3.

following the VIN. A 0.1uF decoupling ceramic Connect the EN/SYNC input pin through a pullup

capacitor is needed at the pin. resistor to any voltage connected to the VIN pin—

Error Amplifier the pullup resistor limits the EN/SYNC input

The error amplifier compares the FB pin voltage current to less than 150µA.

against the internal 0.8V reference (REF) and For example, with 12V connected to VIN, RPULLUP

outputs a COMP voltage—this COMP voltage ≥ (12V – 6.5V) ÷ 150µA = 36.7kΩ.

controls the power MOSFET current. The

Connecting the EN/SYNC pin directly to a

optimized internal compensation network

voltage source without any pullup resistor

minimizes the external component count and

requires limiting voltage amplitude to ≤6V to

simplifies the control loop design.

prevent damage to the Zener diode.

Power Save Mode for Light Load Condition

The MP9943 has AAM (Advanced Asynchronous

Modulation) power-save mode for light load. The

AAM threshold is fixed internally. Under the

heavy load condition, the VCOMP is higher than

VAAM. When the clock goes high, the high-side

power MOSFET turns on and remains on until Figure 3: 6.5V-Type Zener Diode

VILsense reaches the value set by the COMP Connect an external clock with a range of

voltage. The internal clock resets every time 200kHz to 2.2MHz 2ms after output voltage is set

when VCOMP is higher than VAAM. to synchronize the internal clock rising edge to

the external clock rising edge. The pulse width of

external clock signal should be less than 2μs.

MP9943 Rev.1.1 www.MonolithicPower.com 12

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

Under-Voltage Lockout enough voltage headroom to facilitate charging.

Under-voltage lockout (UVLO) protects the chip As long as VIN is significantly higher than SW, the

from operating at an insufficient supply voltage. bootstrap capacitor remains charged. When the

The MP9943 UVLO comparator monitors the HS-FET is on, VIN ≈ VSW, so the bootstrap

output voltage of the internal regulator, VCC. The capacitor can’t be charged. When the LS-FET is

UVLO rising threshold is about 3.5V while its on, VIN−VSW reaches its maximum for fast

falling threshold is 3.3V. charging. When there is no inductor current,

Internal Soft-Start VSW=VOUT, so the difference between VIN and

The soft-start prevents the converter output VOUT can charge the bootstrap capacitor. The

voltage from overshooting during startup. When floating driver has its own UVLO protection, with

the chip starts, the internal circuitry generates a a rising threshold of 2.2V and hysteresis of

soft-start voltage (SS) that ramps up from 0V to 150mV. A 20Ω resistor placed between SW and

1.2V. When SS is lower than REF, SS overrides BST cap is strongly recommended to reduce SW

REF so the error amplifier uses SS as the spike voltage.

reference. When SS exceeds REF, the error

amplifier uses REF as the reference. The SS

time is internally set to 1.5ms.

Over-Current Protection and Hiccup

The MP9943 has cycle-by-cycle over current limit

when the inductor current peak value exceeds

the set current limit threshold. If the output

voltage starts to drop until FB is below the Under-

Voltage (UV) threshold—typically 84% below the

reference—the MP9943 enters hiccup mode to

periodically restart the part. This protection mode Figure 4: Internal Bootstrap Charging Circuit

is especially useful when the output is dead-

shorted to ground. The average short-circuit Startup and Shutdown

current is greatly reduced to alleviate the thermal If both VIN and VEN/SYNC exceed their appropriate

issue and to protect the regulator. The MP9943 thresholds, the chip starts: The reference block

exits the hiccup mode once the over-current starts first, generating stable reference voltage

condition is removed. and currents, and then the internal regulator is

Thermal Shutdown enabled. The regulator provides stable supply for

Thermal shutdown prevents the chip from the remaining circuitries.

operating at exceedingly high temperatures. Three events can shut down the chip: VEN/SYNC

When the silicon die temperature exceeds 170°C, low, VIN low, and thermal shutdown. In the

it shuts down the whole chip. When the shutdown procedure, the signaling path is first

temperature drops below its lower threshold blocked to avoid any fault triggering. The COMP

(typically 140°C) the chip is enabled again. voltage and the internal supply rail are then

Floating Driver and Bootstrap Charging pulled down. The floating driver is not subject to

An external bootstrap capacitor power the this shutdown command.

floating-power-MOSFET driver. A dedicated Power Good

internal regulator (see Figure 4) charges and

regulates the bootstrap capacitor voltage to ~5V. The MP9943 has power good (PG) output. The

When the voltage between the BST and SW PG pin is the open drain of a MOSFET. It should

nodes drops below regulation, a PMOS pass be connected to VCC or some other voltage

transistor connected from VIN to BST turns on. source through a resistor (e.g. 100kΩ). In the

The charging current path is from VIN, BST and presence of an input voltage, the MOSFET turns

then to SW. The external circuit should provide on so that the PG pin is pulled to low before SS

MP9943 Rev.1.1 www.MonolithicPower.com 13

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

is ready. After VFB reaches 90%×REF, the PG pin

is pulled high after a delay, typically 90μs. When

VFB drops to 84%×REF, the PG pin is pulled low.

Also, PG is pulled low if thermal shutdown or

EN/SYNC is pulled low.

MP9943 Rev.1.1 www.MonolithicPower.com 14

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

APPLICATION INFORMATION

Setting the Output Voltage Where ∆IL is the inductor ripple current.

The external resistor divider sets the output

Choose the inductor ripple current to be

voltage (see Typical Application on page 1).

approximately 30% of the maximum load current.

Choose R7 around 41.2kΩ. R8 is then given by:

The maximum inductor peak current is:

R7 IL

R8

VOUT IL(MAX) ILOAD

1 2

0.792V

Use a larger inductor for improved efficiency

The T-type network—as shown in Figure —is under light-load conditions—below 100mA.

highly recommended when VOUT is low.

VIN UVLO Setting

RT R7 MP9943 has internal fix under voltage lock out

(UVLO) threshold: rising threshold is 3.5V while

R8

falling threshold is about 3.3V. For the application

needs higher UVLO point, external resistor

divider between EN/SYNC and IN as shown in

Figure 6 can be used to get higher equivalent

Figure 5: T-Type Network

UVLO threshold.

RT+R7 is used to set the loop bandwidth.

Basically, higher RT+R7, lower bandwidth. To

VIN IN

ensure the loop stability, it is strongly

recommended to limit the bandwidth lower than REN_UP

40kHz based on the 410kHz default fsw. Table 1 EN/SYNC

lists the recommended T-type resistors value for

common output voltages. REN_DOWN 500k

Table 1: Resistor Selection for Common Output

Voltages(7)

VOUT (V) R7 (kΩ) R8 (kΩ) RT (kΩ)

3.3 41.2 (1%) 13 (1%) 51 (1%) Figure 6: Adjustable UVLO using EN/SYNC divider

5 41.2 (1%) 7.68 (1%) 51 (1%) The UVLO threshold can be computed from

Notes: below two equations:

7) The recommended parameters is basing on 410kHz switching

frequency, different input voltage, output inductor value and REN_UP

output capacitor value may affect the select of R7, R8 and RT. INUVRISING (1 ) VEN_RISING

For other components’ parameters, please refer to TYPICAL 500k//R EN_DOWN

APPLICATION CIRCUITS on page 19.

REN_UP

Selecting the Inductor INUVFALLING (1 ) VEN_FALLING

500k//R EN_DOWN

Use a 1µH-to-10µH inductor with a DC current

rating of at least 25% percent higher than the Where VEN_RISING=1.4V, VEN_FALLING=1.25V.

maximum load current for most applications. For

When choose REN_UP, make sure it is big enough

highest efficiency, an inductor with small DC

to limit the current flows into EN/SYNC pin lower

resistance is recommended. For most designs,

than 150uA.

the inductance value can be derived from the

following equation.

VOUT (VIN VOUT )

L1

VIN IL fOSC

MP9943 Rev.1.1 www.MonolithicPower.com 15

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

ESR electrolytic capacitors. For best results, use

Selecting the Input Capacitor

low ESR capacitors to keep the output voltage

The input current to the step-down converter is

ripple low. The output voltage ripple can be

discontinuous, therefore requires a capacitor is to

estimated by:

supply the AC current to the step-down converter

while maintaining the DC input voltage. Use low VOUT VOUT 1

VOUT 1 RESR

ESR capacitors for the best performance. Use fS L1 VIN 8 fS C2

ceramic capacitors with X5R or X7R dielectrics

for best results because of their low ESR and Where L1 is the inductor value and RESR is the

small temperature coefficients. equivalent series resistance (ESR) value of the

output capacitor.

For most application, a 22µF ceramic capacitor is

sufficient to maintain the DC input voltage. And it For ceramic capacitors, the capacitance

is strongly recommended to use another lower dominates the impedance at the switching

value capacitor (e.g. 1µF) with small package frequency, and the capacitance causes the

size (0603) to absorb high frequency switching majority of the output voltage ripple. For

noise. Make sure place the small size capacitor simplification, the output voltage ripple can be

as close to IN and GND pins as possible (see estimated by:

PCB LAYOUT section). VOUT V

∆VOUT 1 OUT

Since C1 absorbs the input switching current, it 8 fS L1 C2

2

VIN

requires an adequate ripple current rating. The

RMS current in the input capacitor can be For tantalum or electrolytic capacitors, the ESR

estimated by: dominates the impedance at the switching

frequency. For simplification, the output ripple

VOUT VOUT can be approximated to:

I C1 ILOAD 1

VIN VIN

VOUT V

∆VOUT 1 OUT RESR

The worse case condition occurs at VIN = 2VOUT, fS L1 VIN

where:

The characteristics of the output capacitor also

I affect the stability of the regulation system. The

IC1 LOAD

2 MP9943 can be optimized for a wide range of

capacitance and ESR values.

For simplification, choose an input capacitor with

an RMS current rating greater than half of the The characteristics of the output capacitor also

maximum load current. affect the stability of the regulation system. The

MP9943 can be optimized for a wide range of

The input capacitor can be electrolytic, tantalum

capacitance and ESR values.

or ceramic. When using electrolytic or tantalum

capacitors, add a small, high quality ceramic BST Resistor and External BST Diode

capacitor (e.g. 1μF) placed as close to the IC as A 20Ω resistor in series with BST capacitor is

possible. When using ceramic capacitors, make recommended to reduce the SW spike voltage.

sure that they have enough capacitance to Higher resistance is better for SW spike

provide sufficient charge to prevent excessive reduction, but will compromise the efficiency on

voltage ripple at input. The input voltage ripple the other hand.

caused by capacitance can be estimated by: BST voltage may become insufficient at some

ILOAD V V particular specs. In this case an external

VIN OUT 1 OUT

fS C1 VIN VIN bootstrap diode can enhance the efficiency of the

regulator and avoid BST voltage insufficient at

Selecting the Output Capacitor light load PFM operation. The BST voltage

The output capacitor (C2) maintains the DC insufficient is more likely to happen at given

output voltage. Use ceramic, tantalum, or low- either of following conditions:

MP9943 Rev.1.1 www.MonolithicPower.com 16

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

VIN is below 5V Notes:

8) The recommended layout is based on the Figure 9 Typical

VOUT is 5V or 3.3V; and Duty cycle is high: Application circuit on page 19.

VOUT

D= >65%

VIN

In these cases, if BST voltage insufficient

happens, the output ripple voltage may become

extremely large at light load condition, add an

external BST diode from the VCC pin or VOUT to

BST pin, as shown in Figure 7.

Top Layer

Figure 7: Optional External Bootstrap Diode to

Enhance Efficiency

The recommended external BST diode is

1N4148, and the BST capacitor value is 0.1µF to

1μF.

PCB Layout(8)

PCB layout, especially the input capacitor and

VCC capacitor placement, is very important to

achieve stable operation. For the best results,

follow these guidelines:

1) Place the ceramics input capacitor as close to

Bottom Layer

IN and GND pins as possible, especially the

small package size (0603) input bypass capacitor. Figure 8: Recommended PCB Layout

Keep the connection of input capacitor and IN pin

as short and wide as possible.

2) Place the VCC capacitor to VCC pin and GND

pin as close as possible. Make the trace length of

VCC pin-VCC capacitor anode-VCC capacitor

cathode-chip GND pin as short as possible.

3) Use large ground plane directly connect to

GND pin. Add vias near the GND pin if bottom

layer is ground plane.

4) Route SW, BST away from sensitive analog

areas such as FB.

5) Place the T-type feedback resistor close to

chip to ensure the trace which connects to FB pin

as the short as possible.

MP9943 Rev.1.1 www.MonolithicPower.com 17

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

Design Example

Below is a design example following the

application guidelines for the specifications:

Table 2: Design Example

VIN 12V

VOUT 5V

IOUT 3A Peak

The detailed application schematic is shown in

Figure 9. The typical performance and circuit

waveforms have been shown in the Typical

Performance Characteristics section. For more

device applications, please refer to the related

Evaluation Board Datasheets.

MP9943 Rev.1.1 www.MonolithicPower.com 18

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

TYPICAL APPLICATION CIRCUITS

Figure 9: 12VIN, 5V/3A Peak Output

Figure 10: 12VIN, 3.3V/3A Peak Output

MP9943 Rev.1.1 www.MonolithicPower.com 19

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

MP9943 – 36V, 3A PEAK SYNCHRONOUS STEP-DOWN CONVERTER

PACKAGE INFORMATION

QFN-8 (3mm x 3mm)

NOTICE: The information in this document is subject to change without notice. Users should warrant and guarantee that third

party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not

assume any legal responsibility for any said applications.

MP9943 Rev.1.0 www.MonolithicPower.com 20

7/4/2017 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

You might also like

- ESP - ArtificialLiftProductCatalog - Q2 GE OIL GAS PDFDocument315 pagesESP - ArtificialLiftProductCatalog - Q2 GE OIL GAS PDFFRANCISCO DAMMERNo ratings yet

- MP8719 6600xt SaphireDocument22 pagesMP8719 6600xt Saphiretechgamebr85No ratings yet

- Synchronous Step Down Converter: High Efficiency 3A, 24V, 500KhzDocument16 pagesSynchronous Step Down Converter: High Efficiency 3A, 24V, 500KhzAnonymous 8bbVmLtQNo ratings yet

- MP6515Document13 pagesMP6515gaatje niks aanNo ratings yet

- U1 Xbox OneDocument14 pagesU1 Xbox OneCheckpoint Game CenterNo ratings yet

- MP1488Document11 pagesMP1488Jaime Andres Aranguren CardonaNo ratings yet

- LM3478MM PDFDocument22 pagesLM3478MM PDFkarimNo ratings yet

- 2A, 55V, 100Khz Step-Down ConverterDocument12 pages2A, 55V, 100Khz Step-Down Convertermichael8710No ratings yet

- 100V Input, 1A High Power LED Driver: The Future of Analog IC TechnologyDocument10 pages100V Input, 1A High Power LED Driver: The Future of Analog IC TechnologyAdrian WongNo ratings yet

- Primary-Side Control, Offline LED Controller With Active PFC, NTC and PWM DimmingDocument19 pagesPrimary-Side Control, Offline LED Controller With Active PFC, NTC and PWM Dimmingzuffflor_925748656No ratings yet

- Description Features: LTC3440 Micropower Synchronous Buck-Boost DC/DC ConverterDocument22 pagesDescription Features: LTC3440 Micropower Synchronous Buck-Boost DC/DC ConverterOsama YaseenNo ratings yet

- Fast Turn-Off Intelligent Rectifier With No Need For Auxiliary Winding Description FeaturesDocument14 pagesFast Turn-Off Intelligent Rectifier With No Need For Auxiliary Winding Description FeaturesKwun Hok ChongNo ratings yet

- 2A, 24V Input, 600Khz 2/3-Cell Switching Li-Ion Battery ChargerDocument16 pages2A, 24V Input, 600Khz 2/3-Cell Switching Li-Ion Battery Charger123No ratings yet

- MP6003 r1.01Document15 pagesMP6003 r1.01nan keNo ratings yet

- MP3398A - r1.05 Driver Les Board Flaco BellohorizonteDocument20 pagesMP3398A - r1.05 Driver Les Board Flaco BellohorizonteAndres AlegriaNo ratings yet

- MP3431 r1.0Document25 pagesMP3431 r1.0nan keNo ratings yet

- 24V, High Current Synchronous Step-Down Converter: The Future of Analog IC TechnologyDocument20 pages24V, High Current Synchronous Step-Down Converter: The Future of Analog IC TechnologyRinaldyNo ratings yet

- 2.8V-22V V, 3A I, 4-Switch Integrated Buck-Boost Converter With Fixed 5V Output Description FeaturesDocument19 pages2.8V-22V V, 3A I, 4-Switch Integrated Buck-Boost Converter With Fixed 5V Output Description FeaturesBrbrHuehue SzzNo ratings yet

- MP62550/MP62551: Precision 60mA-1.7A Programmable Current-Limited Power Distribution SwitchDocument16 pagesMP62550/MP62551: Precision 60mA-1.7A Programmable Current-Limited Power Distribution Switch이강학No ratings yet

- LTC 7803Document38 pagesLTC 7803sahil.padhiyar18No ratings yet

- MP4569Document17 pagesMP4569Jesús Miguel LemNo ratings yet

- Tps 560430Document33 pagesTps 560430Danil StefanovNo ratings yet

- MA102Document26 pagesMA102George AcostaNo ratings yet

- 3A, 28V, 385Khz Step-Down Converter: The Future of Analog Ic TechnologyDocument13 pages3A, 28V, 385Khz Step-Down Converter: The Future of Analog Ic TechnologyIoan TivgaNo ratings yet

- LM34940Document27 pagesLM34940Anonymous oyUAtpKNo ratings yet

- NB676 DatasheetDocument19 pagesNB676 DatasheetRudy BudimanNo ratings yet

- Description Features: Step Up, 4 Strings, Max. 350ma/string Analog and PWM Dimming, White LED ControllerDocument20 pagesDescription Features: Step Up, 4 Strings, Max. 350ma/string Analog and PWM Dimming, White LED Controllersivanka ranganaNo ratings yet

- MP4462Document20 pagesMP4462Esteban RodriguezNo ratings yet

- MP4462DN Step-Down ConverterDocument21 pagesMP4462DN Step-Down ConverterahmedNo ratings yet

- High Current Power Half Bridge: The Future of Analog IC TechnologyDocument8 pagesHigh Current Power Half Bridge: The Future of Analog IC Technologyقناة احترف بنفسكNo ratings yet

- MPM80 Series Data Sheet: 2 A Non-Isolated Buck Converter ModuleDocument20 pagesMPM80 Series Data Sheet: 2 A Non-Isolated Buck Converter ModuleytnateNo ratings yet

- LM2621 Low Input Voltage, Step-Up DC-DC Converter: 1 Features 3 DescriptionDocument17 pagesLM2621 Low Input Voltage, Step-Up DC-DC Converter: 1 Features 3 DescriptionSatyashiba Sundar JenaNo ratings yet

- Service Manual: ModelDocument44 pagesService Manual: Modelsupertiger15No ratings yet

- Buck Converter 101Document55 pagesBuck Converter 101ed251No ratings yet

- Max 3664Document12 pagesMax 3664srinivasanNo ratings yet

- lp2985 NDocument41 pageslp2985 NCarlos AlexandreNo ratings yet

- Aerosemi: Features General DescriptionDocument9 pagesAerosemi: Features General DescriptionCurut BerutNo ratings yet

- MIC94305 500ma Switch With Ripple BlockerDocument20 pagesMIC94305 500ma Switch With Ripple BlockerHaidong KimNo ratings yet

- Design Case Study: Designing A Power Supply For A Portable, Wireless Contact ManagerDocument6 pagesDesign Case Study: Designing A Power Supply For A Portable, Wireless Contact ManagerJonathan JaegerNo ratings yet

- Max 16169Document12 pagesMax 16169dcastrelos2000No ratings yet

- 24V, High Current Synchronous Step-Down Converter: The Future of Analog IC TechnologyDocument22 pages24V, High Current Synchronous Step-Down Converter: The Future of Analog IC TechnologyEnzoquirozNo ratings yet

- TinyNode Users Manual Rev11 01Document30 pagesTinyNode Users Manual Rev11 01fantomagaNo ratings yet

- Boundary Mode PFC Controller: The Future of Analog IC TechnologyDocument14 pagesBoundary Mode PFC Controller: The Future of Analog IC TechnologydistefanoNo ratings yet

- Mpxh6400a 185587Document12 pagesMpxh6400a 185587TDFRIOGRANDENo ratings yet

- 3129fc DatasheetDocument30 pages3129fc DatasheetVịnh DemoNo ratings yet

- (0 - P) (Dirac) Sampling Tps62231-q1Document27 pages(0 - P) (Dirac) Sampling Tps62231-q1Sarhro ELNo ratings yet

- Offline, Primary-Side Regulator With CC/CV Control and A 700V MOSFETDocument21 pagesOffline, Primary-Side Regulator With CC/CV Control and A 700V MOSFETsluz2000No ratings yet

- A1308 and A1309 DatasheetDocument12 pagesA1308 and A1309 DatasheetjeremyNo ratings yet

- A3121 2 3 Datasheet PDFDocument9 pagesA3121 2 3 Datasheet PDFAsad IqbalNo ratings yet

- Max931 Max934Document16 pagesMax931 Max934pre freedaNo ratings yet

- Max 6901 EtatDocument18 pagesMax 6901 Etatrt23.kysliuk.artemNo ratings yet

- Fitipower-Integrated-Tech-FR9889SPCTR C516194 4Document13 pagesFitipower-Integrated-Tech-FR9889SPCTR C516194 4Nam TàoNo ratings yet

- 300 W Stylish & Slim Sound Bar: Service ManualDocument43 pages300 W Stylish & Slim Sound Bar: Service ManualSergey OvcharovNo ratings yet

- Simple Success With Conducted EMI and Radiated EMI For LMR160X0Document8 pagesSimple Success With Conducted EMI and Radiated EMI For LMR160X0joseteNo ratings yet

- MFJ 2015 Ham Radio CatalogDocument140 pagesMFJ 2015 Ham Radio CatalogBogdan GrigoreNo ratings yet

- Discontinued Product: Full-Bridge Power MOSFET ControllerDocument13 pagesDiscontinued Product: Full-Bridge Power MOSFET ControllerJoão C VieiraNo ratings yet

- Datasheet LTC3728L & LTC3728LX PDFDocument32 pagesDatasheet LTC3728L & LTC3728LX PDFSelmar CavalcantiNo ratings yet

- CCFL INVERTER MODULES LXMG1618!12!41 DatasheetDocument6 pagesCCFL INVERTER MODULES LXMG1618!12!41 DatasheetVladimir LevchenkoNo ratings yet

- Tps 73125Document18 pagesTps 73125mekki1No ratings yet

- Model MF4000: MEMS Mass Flow MetersDocument13 pagesModel MF4000: MEMS Mass Flow MetersStanzaPelangiNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Up 9505Document40 pagesUp 9505techgamebr85No ratings yet

- UP1962SDocument14 pagesUP1962Stechgamebr85No ratings yet

- RT8125C 6XDocument17 pagesRT8125C 6Xtechgamebr85No ratings yet

- Rt8816a-06 Gtx1070 Gigabyte MemoriasDocument21 pagesRt8816a-06 Gtx1070 Gigabyte Memoriastechgamebr85No ratings yet

- Sic 632Document19 pagesSic 632techgamebr85No ratings yet

- Tps 51218Document27 pagesTps 51218techgamebr85No ratings yet

- NCP 4208Document30 pagesNCP 4208techgamebr85No ratings yet

- FDMF 6823 DCDocument19 pagesFDMF 6823 DCtechgamebr85No ratings yet

- [de Gruyter Frontiers in Computational Intelligence, 12] Neeraj Priyadarshi, Sanjeevikumar Padmanaban, Kamal Kant Hiran, - Artificial Intelligence and Internet of Things for Renewable Energy Systems (2021, De GruyteDocument320 pages[de Gruyter Frontiers in Computational Intelligence, 12] Neeraj Priyadarshi, Sanjeevikumar Padmanaban, Kamal Kant Hiran, - Artificial Intelligence and Internet of Things for Renewable Energy Systems (2021, De Gruytekurts010No ratings yet

- Zork I - ManualDocument29 pagesZork I - Manualmarcela2803No ratings yet

- Em03 - Machine LearningDocument14 pagesEm03 - Machine LearningVed Prakash SahNo ratings yet

- Tower SP, The (USA)Document26 pagesTower SP, The (USA)Tsamis IoannisNo ratings yet

- IR24 Inter-PLMN RoamingDocument13 pagesIR24 Inter-PLMN RoamingVishav Preet SinghNo ratings yet

- Software Development Learning Path - Board InfinityDocument22 pagesSoftware Development Learning Path - Board InfinityNirupam NishantNo ratings yet

- Early Digital Computer Art at Bell Telephone Laboratories, IncorporatedDocument11 pagesEarly Digital Computer Art at Bell Telephone Laboratories, IncorporatedLily FakhreddineNo ratings yet

- Instant Download Understanding Motor Controls 3rd Edition Herman Solutions Manual PDF Full ChapterDocument9 pagesInstant Download Understanding Motor Controls 3rd Edition Herman Solutions Manual PDF Full ChapterElizabethPhillipsfztqc100% (9)

- Internal Job Posting Application: ASSOCIATE INFORMATION (Complete All Information)Document3 pagesInternal Job Posting Application: ASSOCIATE INFORMATION (Complete All Information)Shtep GonzoNo ratings yet

- Bioinicia: Electrospinning SpecialistDocument4 pagesBioinicia: Electrospinning SpecialistOriana González HernándezNo ratings yet

- E-Medical: Revenue Cycle Management (RCM) SolutionDocument23 pagesE-Medical: Revenue Cycle Management (RCM) SolutionJehan ZebNo ratings yet

- USA Resume Akshay ShahDocument4 pagesUSA Resume Akshay ShahAkshay ShahNo ratings yet

- This Study Resource Was: Moles 0.00691Document2 pagesThis Study Resource Was: Moles 0.00691Remar Jhon PaineNo ratings yet

- Project - W&Solar Charging MobileDocument5 pagesProject - W&Solar Charging MobilehamzaNo ratings yet

- UntitledDocument2 pagesUntitledTaufiq Setya Rifa'iNo ratings yet

- Discovery 20: Configure Syslog: Task 1: Configure The Router To Log To ServerDocument2 pagesDiscovery 20: Configure Syslog: Task 1: Configure The Router To Log To ServerIonut StanciuNo ratings yet

- LabVIEW Lecture 1 - Navigating LabVIEWDocument74 pagesLabVIEW Lecture 1 - Navigating LabVIEWSuaid Tariq BalghariNo ratings yet

- Waec Syllabus For Building ConstructionDocument7 pagesWaec Syllabus For Building ConstructionOpadijo Adekunle ToheebNo ratings yet

- PDF Isuzu 4jj1 30 Pinout - CompressDocument3 pagesPDF Isuzu 4jj1 30 Pinout - CompressBecker Orlando Perez FIallosNo ratings yet

- NGINX Playbook - Secure API Connectivity CP 011223Document9 pagesNGINX Playbook - Secure API Connectivity CP 011223Phuong TranNo ratings yet

- Internal To WiproDocument17 pagesInternal To WiproVIMAL KUMAR CHAUHANNo ratings yet

- Open Labs Production Station ManualDocument126 pagesOpen Labs Production Station ManualEduardo Soares GuiaNo ratings yet

- Project LibraryDocument76 pagesProject Libraryrocky2463.singhNo ratings yet

- Lethal Service - Quick Guide - Pressure Vessel EngineeringDocument4 pagesLethal Service - Quick Guide - Pressure Vessel EngineeringVilas AndhaleNo ratings yet

- Iot Questions For AssignmentsDocument1 pageIot Questions For AssignmentsKumar ChaitanyaNo ratings yet

- Element of MultimediaDocument2 pagesElement of MultimediatoceqNo ratings yet

- User Manual of TC-170 Smart OTDRDocument2 pagesUser Manual of TC-170 Smart OTDRserti sertinNo ratings yet

- Basug BasicTasksDocument640 pagesBasug BasicTasksdebendra128nitr100% (1)

- ExovoDocument357 pagesExovoreatonautoNo ratings yet

![[de Gruyter Frontiers in Computational Intelligence, 12] Neeraj Priyadarshi, Sanjeevikumar Padmanaban, Kamal Kant Hiran, - Artificial Intelligence and Internet of Things for Renewable Energy Systems (2021, De Gruyte](https://imgv2-2-f.scribdassets.com/img/document/673126539/149x198/dd99d6c35d/1695483638?v=1)