Professional Documents

Culture Documents

PIC16F87XA: 2.2.2.8 PCON Register

PIC16F87XA: 2.2.2.8 PCON Register

Uploaded by

vitor valeOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

PIC16F87XA: 2.2.2.8 PCON Register

PIC16F87XA: 2.2.2.8 PCON Register

Uploaded by

vitor valeCopyright:

Available Formats

PIC16F87XA

2.2.2.8 PCON Register Note: BOR is unknown on Power-on Reset. It

The Power Control (PCON) register contains flag bits must be set by the user and checked on

to allow differentiation between a Power-on Reset subsequent Resets to see if BOR is clear,

(POR), a Brown-out Reset (BOR), a Watchdog Reset indicating a brown-out has occurred. The

(WDT) and an external MCLR Reset. BOR status bit is a “don’t care” and is not

predictable if the brown-out circuit is dis-

abled (by clearing the BODEN bit in the

configuration word).

REGISTER 2-8: PCON REGISTER (ADDRESS 8Eh)

U-0 U-0 U-0 U-0 U-0 U-0 R/W-0 R/W-1

— — — — — — POR BOR

bit 7 bit 0

bit 7-2 Unimplemented: Read as ‘0’

bit 1 POR: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 BOR: Brown-out Reset Status bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

2003 Microchip Technology Inc. DS39582B-page 29

PIC16F87XA

2.3 PCL and PCLATH Note 1: There are no status bits to indicate stack

The Program Counter (PC) is 13 bits wide. The low overflow or stack underflow conditions.

byte comes from the PCL register which is a readable 2: There are no instructions/mnemonics

and writable register. The upper bits (PC<12:8>) are called PUSH or POP. These are actions

not readable, but are indirectly writable through the that occur from the execution of the CALL,

PCLATH register. On any Reset, the upper bits of the RETURN, RETLW and RETFIE instructions

PC will be cleared. Figure 2-5 shows the two situations or the vectoring to an interrupt address.

for the loading of the PC. The upper example in the

figure shows how the PC is loaded on a write to PCL 2.4 Program Memory Paging

(PCLATH<4:0> → PCH). The lower example in the

figure shows how the PC is loaded during a CALL or All PIC16F87XA devices are capable of addressing a

GOTO instruction (PCLATH<4:3> → PCH). continuous 8K word block of program memory. The

CALL and GOTO instructions provide only 11 bits of

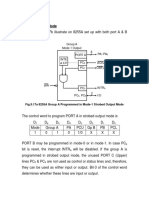

FIGURE 2-5: LOADING OF PC IN address to allow branching within any 2K program

DIFFERENT SITUATIONS memory page. When doing a CALL or GOTO instruction,

the upper 2 bits of the address are provided by

PCH PCL

PCLATH<4:3>. When doing a CALL or GOTO instruc-

tion, the user must ensure that the page select bits are

12 8 7 0 Instruction with programmed so that the desired program memory

PC PCL as

Destination page is addressed. If a return from a CALL instruction

PCLATH<4:0> 8 (or interrupt) is executed, the entire 13-bit PC is popped

5 ALU

off the stack. Therefore, manipulation of the

PCLATH<4:3> bits is not required for the RETURN

PCLATH instructions (which POPs the address from the stack).

PCH PCL Note: The contents of the PCLATH register are

12 11 10 8 7 0 unchanged after a RETURN or RETFIE

PC GOTO,CALL instruction is executed. The user must

rewrite the contents of the PCLATH regis-

PCLATH<4:3> 11

2 Opcode <10:0> ter for any subsequent subroutine calls or

GOTO instructions.

PCLATH Example 2-1 shows the calling of a subroutine in

page 1 of the program memory. This example assumes

that PCLATH is saved and restored by the Interrupt

2.3.1 COMPUTED GOTO Service Routine (if interrupts are used).

A computed GOTO is accomplished by adding an offset

to the program counter (ADDWF PCL). When doing a EXAMPLE 2-1: CALL OF A SUBROUTINE

table read using a computed GOTO method, care IN PAGE 1 FROM PAGE 0

should be exercised if the table location crosses a PCL ORG 0x500

memory boundary (each 256-byte block). Refer to the BCF PCLATH,4

application note, AN556, “Implementing a Table Read” BSF PCLATH,3 ;Select page 1

(DS00556). ;(800h-FFFh)

CALL SUB1_P1 ;Call subroutine in

2.3.2 STACK : ;page 1 (800h-FFFh)

:

The PIC16F87XA family has an 8-level deep x 13-bit ORG 0x900 ;page 1 (800h-FFFh)

wide hardware stack. The stack space is not part of SUB1_P1

either program or data space and the stack pointer is not : ;called subroutine

readable or writable. The PC is PUSHed onto the stack ;page 1 (800h-FFFh)

when a CALL instruction is executed, or an interrupt :

causes a branch. The stack is POP’ed in the event of a RETURN ;return to

RETURN, RETLW or a RETFIE instruction execution. ;Call subroutine

PCLATH is not affected by a PUSH or POP operation. ;in page 0

;(000h-7FFh)

The stack operates as a circular buffer. This means that

after the stack has been PUSHed eight times, the ninth

push overwrites the value that was stored from the first

push. The tenth push overwrites the second push (and

so on).

DS39582B-page 30 2003 Microchip Technology Inc.

PIC16F87XA

2.5 Indirect Addressing, INDF and A simple program to clear RAM locations 20h-2Fh

FSR Registers using indirect addressing is shown in Example 2-2.

The INDF register is not a physical register. Addressing EXAMPLE 2-2: INDIRECT ADDRESSING

the INDF register will cause indirect addressing. MOVLW 0x20 ;initialize pointer

Indirect addressing is possible by using the INDF reg- MOVWF FSR ;to RAM

ister. Any instruction using the INDF register actually NEXT CLRF INDF ;clear INDF register

accesses the register pointed to by the File Select Reg- INCF FSR,F ;inc pointer

ister, FSR. Reading the INDF register itself, indirectly BTFSS FSR,4 ;all done?

GOTO NEXT ;no clear next

(FSR = 0) will read 00h. Writing to the INDF register

CONTINUE

indirectly results in a no operation (although status bits : ;yes continue

may be affected). An effective 9-bit address is obtained

by concatenating the 8-bit FSR register and the IRP bit

(Status<7>) as shown in Figure 2-6.

FIGURE 2-6: DIRECT/INDIRECT ADDRESSING

Direct Addressing Indirect Addressing

RP1:RP0 6 From Opcode 0 IRP 7 FSR Register 0

Bank Select Location Select Bank Select Location Select

00 01 10 11

00h 80h 100h 180h

Data

Memory(1)

7Fh FFh 17Fh 1FFh

Bank 0 Bank 1 Bank 2 Bank 3

Note 1: For register file map detail, see Figure 2-3.

2003 Microchip Technology Inc. DS39582B-page 31

PIC16F87XA

NOTES:

DS39582B-page 32 2003 Microchip Technology Inc.

PIC16F87XA

3.0 DATA EEPROM AND FLASH 3.1 EEADR and EEADRH

PROGRAM MEMORY The EEADRH:EEADR register pair can address up to

The data EEPROM and Flash program memory is read- a maximum of 256 bytes of data EEPROM or up to a

able and writable during normal operation (over the full maximum of 8K words of program EEPROM. When

VDD range). This memory is not directly mapped in the selecting a data address value, only the LSByte of the

register file space. Instead, it is indirectly addressed address is written to the EEADR register. When select-

through the Special Function Registers. There are six ing a program address value, the MSByte of the

SFRs used to read and write this memory: address is written to the EEADRH register and the

LSByte is written to the EEADR register.

• EECON1

If the device contains less memory than the full address

• EECON2

reach of the address register pair, the Most Significant

• EEDATA bits of the registers are not implemented. For example,

• EEDATH if the device has 128 bytes of data EEPROM, the Most

• EEADR Significant bit of EEADR is not implemented on access

• EEADRH to data EEPROM.

When interfacing to the data memory block, EEDATA

holds the 8-bit data for read/write and EEADR holds the

3.2 EECON1 and EECON2 Registers

address of the EEPROM location being accessed. EECON1 is the control register for memory accesses.

These devices have 128 or 256 bytes of data EEPROM

Control bit, EEPGD, determines if the access will be a

(depending on the device), with an address range from

program or data memory access. When clear, as it is

00h to FFh. On devices with 128 bytes, addresses from

when reset, any subsequent operations will operate on

80h to FFh are unimplemented and will wraparound to

the data memory. When set, any subsequent

the beginning of data EEPROM memory. When writing

operations will operate on the program memory.

to unimplemented locations, the on-chip charge pump

will be turned off. Control bits, RD and WR, initiate read and write or

erase, respectively. These bits cannot be cleared, only

When interfacing the program memory block, the

set, in software. They are cleared in hardware at com-

EEDATA and EEDATH registers form a two-byte word

pletion of the read or write operation. The inability to

that holds the 14-bit data for read/write and the EEADR

clear the WR bit in software prevents the accidental,

and EEADRH registers form a two-byte word that holds

premature termination of a write operation.

the 13-bit address of the program memory location

being accessed. These devices have 4 or 8K words of The WREN bit, when set, will allow a write or erase

program Flash, with an address range from 0000h to operation. On power-up, the WREN bit is clear. The

0FFFh for the PIC16F873A/874A and 0000h to 1FFFh WRERR bit is set when a write (or erase) operation is

for the PIC16F876A/877A. Addresses above the range interrupted by a MCLR or a WDT Time-out Reset dur-

of the respective device will wraparound to the ing normal operation. In these situations, following

beginning of program memory. Reset, the user can check the WRERR bit and rewrite

the location. The data and address will be unchanged

The EEPROM data memory allows single-byte read and

in the EEDATA and EEADR registers.

write. The Flash program memory allows single-word

reads and four-word block writes. Program memory Interrupt flag bit, EEIF in the PIR2 register, is set when

write operations automatically perform an erase-before- the write is complete. It must be cleared in software.

write on blocks of four words. A byte write in data EECON2 is not a physical register. Reading EECON2

EEPROM memory automatically erases the location will read all ‘0’s. The EECON2 register is used

and writes the new data (erase-before-write). exclusively in the EEPROM write sequence.

The write time is controlled by an on-chip timer. The

Note: The self-programming mechanism for Flash

write/erase voltages are generated by an on-chip

program memory has been changed. On

charge pump, rated to operate over the voltage range

previous PIC16F87X devices, Flash pro-

of the device for byte or word operations.

gramming was done in single-word erase/

When the device is code-protected, the CPU may write cycles. The newer PIC18F87XA

continue to read and write the data EEPROM memory. devices use a four-word erase/write

Depending on the settings of the write-protect bits, the cycle. See Section 3.6 “Writing to Flash

device may or may not be able to write certain blocks Program Memory” for more information.

of the program memory; however, reads of the program

memory are allowed. When code-protected, the device

programmer can no longer access data or program

memory; this does NOT inhibit internal reads or writes.

2003 Microchip Technology Inc. DS39582B-page 33

You might also like

- Sirona C3+ Dental Unit - Service ManualDocument90 pagesSirona C3+ Dental Unit - Service Manualperla_canto_1100% (2)

- IC3 ModulesDocument9 pagesIC3 ModulesSuhaimi SimponNo ratings yet

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosFrom EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosRating: 5 out of 5 stars5/5 (1)

- Assembly Language Short Notes by VuDocument16 pagesAssembly Language Short Notes by VuSyed HadiNo ratings yet

- Dell Inspiron 1750 - SchematicsDocument59 pagesDell Inspiron 1750 - SchematicsAnonymous i1XrU6jzo0No ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (1)

- DCSA P3 Asset List Risk Assessment Framework ExamplesDocument5 pagesDCSA P3 Asset List Risk Assessment Framework ExamplesRikin ParekhNo ratings yet

- Toolmaster TM10 eDocument8 pagesToolmaster TM10 eMaskub Ulul KhrtNo ratings yet

- Tblread With 16CDocument5 pagesTblread With 16CSri RamNo ratings yet

- Implementing A Table Read: ImplementationDocument5 pagesImplementing A Table Read: ImplementationadilNo ratings yet

- Zilog Z80 Pio User S Manual: Chapter 1. IntroductionDocument22 pagesZilog Z80 Pio User S Manual: Chapter 1. IntroductionMustafa UrluNo ratings yet

- PTN5100 PHY Programming Guide V0.1Document103 pagesPTN5100 PHY Programming Guide V0.1JustinNo ratings yet

- Doc-A.14-Text Editor On A LCD Using At89c51 Micro Controller and KeyboardDocument48 pagesDoc-A.14-Text Editor On A LCD Using At89c51 Micro Controller and KeyboardRockson Kwame AgyemanNo ratings yet

- PROJECT REPORT (Jan 3rd - Jan 8)Document7 pagesPROJECT REPORT (Jan 3rd - Jan 8)Rahul SampathNo ratings yet

- PIC18 Assembly Language ProgrammingDocument14 pagesPIC18 Assembly Language ProgrammingxyzzyzNo ratings yet

- PIC 16F877A Microcontroller Core Features: Unit 6Document10 pagesPIC 16F877A Microcontroller Core Features: Unit 6Altaaf MulaniNo ratings yet

- MT Datasheet CroppedDocument107 pagesMT Datasheet Croppedbasar.metin2No ratings yet

- Dell Inspiron 1427 SchematicsDocument58 pagesDell Inspiron 1427 SchematicsAndrei SimionescuNo ratings yet

- Pic:Micro-Controller Architecture & Instruction Set: ECE Department, DTUDocument19 pagesPic:Micro-Controller Architecture & Instruction Set: ECE Department, DTUgauravlodhi983No ratings yet

- 5 InterruptsDocument9 pages5 InterruptsTam PhamNo ratings yet

- Micro II and Embedded Systems: Introduction To PIC MicrocontrollerDocument22 pagesMicro II and Embedded Systems: Introduction To PIC Microcontrollerxkurt358792No ratings yet

- Pic Micro ControllersDocument3 pagesPic Micro ControllersSaurabh RastogiNo ratings yet

- Interrupt - IO Part1Document20 pagesInterrupt - IO Part1aesyopNo ratings yet

- Ppi 8255Document163 pagesPpi 8255Taufik Mage3No ratings yet

- Frequency MeterDocument48 pagesFrequency MeterSumit AgarwalNo ratings yet

- Unit Iii I/O Part A: InterfacingDocument54 pagesUnit Iii I/O Part A: Interfacingmariyal eceNo ratings yet

- Lecture-53 Mode 2: (Strobed Bidirectional Bus I/O)Document6 pagesLecture-53 Mode 2: (Strobed Bidirectional Bus I/O)Shrey MisraNo ratings yet

- 80C51 Family Hardware Description 80C51 FamilyDocument24 pages80C51 Family Hardware Description 80C51 FamilyABDElrahmanJamalMohaNo ratings yet

- 8085 MCQDocument20 pages8085 MCQniteshNo ratings yet

- Pertemuan 7 Organisasi Input / OutputDocument29 pagesPertemuan 7 Organisasi Input / OutputYason Timothy HamdaniNo ratings yet

- Description of MicrocontrollerDocument29 pagesDescription of Microcontrollervinayreddy23291No ratings yet

- MKT3811 Week4 03.11.2021 RDocument62 pagesMKT3811 Week4 03.11.2021 REmirhan AlmaNo ratings yet

- MP MC Unit IVDocument26 pagesMP MC Unit IVS D NagulanNo ratings yet

- An Introduction To The PIC Microcontroller: EE2801 - Lecture 19Document9 pagesAn Introduction To The PIC Microcontroller: EE2801 - Lecture 19Reddy BabuNo ratings yet

- PIC16F87XA: 3.7 Protection Against Spurious Write 3.8 Operation During Code-ProtectDocument5 pagesPIC16F87XA: 3.7 Protection Against Spurious Write 3.8 Operation During Code-Protectvitor valeNo ratings yet

- MICROCONTROLLERDocument123 pagesMICROCONTROLLERgaming999905No ratings yet

- Lecture-52 Strobed Output ModeDocument8 pagesLecture-52 Strobed Output ModeShrey MisraNo ratings yet

- Dell Inspiron 1545 Wistron DR1 (Roberts)Document58 pagesDell Inspiron 1545 Wistron DR1 (Roberts)Geoffrey M. Gitau100% (1)

- DELL Inspiron N4020Document88 pagesDELL Inspiron N4020Deddy SuyantoNo ratings yet

- Acer Aspire 8730Document51 pagesAcer Aspire 8730Sadun CaymazNo ratings yet

- BCS302 Unit-3 (Part-II)Document8 pagesBCS302 Unit-3 (Part-II)dp06vnsNo ratings yet

- Unit Ii: PIC MicrocontrollersDocument59 pagesUnit Ii: PIC MicrocontrollersbalaNo ratings yet

- AN1010Document20 pagesAN1010Eslam H. YehiaNo ratings yet

- Flash Microcontroller Architectural: FeaturesDocument18 pagesFlash Microcontroller Architectural: FeaturessyedfahimakhtarNo ratings yet

- Good Luck !: Dr. Atif NsourDocument8 pagesGood Luck !: Dr. Atif NsourFatima AldrweeshNo ratings yet

- A Brief Introduction of Micro Controllers 8051Document64 pagesA Brief Introduction of Micro Controllers 8051Pradeep Varma0% (1)

- Micro ControllerDocument21 pagesMicro Controllerkrishn_blazeNo ratings yet

- M 29 F 200 BBDocument22 pagesM 29 F 200 BBThong ChanNo ratings yet

- 881 AsmDocument23 pages881 AsmFrang JabardNo ratings yet

- Pic Microcontroller 2.1 Pic It Is A Family of Modified Harvard Architecture Microcontrollers MadeDocument16 pagesPic Microcontroller 2.1 Pic It Is A Family of Modified Harvard Architecture Microcontrollers MadeSuresh KumarNo ratings yet

- 8086Document16 pages8086SanthaKumar IsaacNo ratings yet

- PIC MicrocontrollersDocument6 pagesPIC Microcontrollersfinalprojectslttc finalprojectslttcNo ratings yet

- ELEC 2441 - Computer Organization and MicroprocessorsDocument18 pagesELEC 2441 - Computer Organization and MicroprocessorsBillyNo ratings yet

- 8255 InterfaceDocument42 pages8255 InterfaceAalu YadavNo ratings yet

- PIC MicrocontrollersDocument35 pagesPIC Microcontrollersanbuelectrical100% (1)

- 8-Bit Microcontroller With 2K Bytes Flash AT89C2051: FeaturesDocument14 pages8-Bit Microcontroller With 2K Bytes Flash AT89C2051: FeaturesMinhdung PhanNo ratings yet

- Network with Practical Labs Configuration: Step by Step configuration of Router and Switch configurationFrom EverandNetwork with Practical Labs Configuration: Step by Step configuration of Router and Switch configurationNo ratings yet

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkFrom EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Iosif Stefan Octavian - Cantec SfantDocument247 pagesIosif Stefan Octavian - Cantec SfantCamelia MurguNo ratings yet

- Report Title: Smoke and Natural Gas Detector An Iot Device Prepared By: Hassan Ali ButtDocument11 pagesReport Title: Smoke and Natural Gas Detector An Iot Device Prepared By: Hassan Ali ButtHasanNo ratings yet

- WI FI VikramDocument13 pagesWI FI VikramSyed NaseerNo ratings yet

- DSE7510 Data Sheet PDFDocument2 pagesDSE7510 Data Sheet PDFKrishna Pardeshi100% (1)

- cd1753b 05 Dfu EngDocument40 pagescd1753b 05 Dfu EngrahimahmedNo ratings yet

- ADC10D040 Dual 10-Bit, 40 MSPS, 267 MW A/D Converter: General Description FeaturesDocument28 pagesADC10D040 Dual 10-Bit, 40 MSPS, 267 MW A/D Converter: General Description FeaturesskiziltoprakNo ratings yet

- Prepared By: Megha Naruka 07CS000042Document21 pagesPrepared By: Megha Naruka 07CS000042Sparsh GuptaNo ratings yet

- Transcell TCS 3LCD User GuideENGLISH REV13Document20 pagesTranscell TCS 3LCD User GuideENGLISH REV13Gudalupe Flores MoralesNo ratings yet

- President Lincoln BibleDocument31 pagesPresident Lincoln BibleGeorge Andreas Manthopoulos100% (1)

- Lec 5Document8 pagesLec 5Elisée NdjabuNo ratings yet

- Release Notes Lyft Software 2.0r5Document2 pagesRelease Notes Lyft Software 2.0r5afiqhashim89No ratings yet

- Operating Systems ENN 205Document14 pagesOperating Systems ENN 205Mohit KumarNo ratings yet

- NotepadDocument4 pagesNotepadprithrajNo ratings yet

- Computer OrganizationDocument1 pageComputer Organizationkatta vishodhanaNo ratings yet

- Linux Lab UnlockDocument277 pagesLinux Lab UnlockNavneet KishoreNo ratings yet

- AISC 360-10 Specification For Structural Steel Buildings - Errata To 1st Printing PDFDocument10 pagesAISC 360-10 Specification For Structural Steel Buildings - Errata To 1st Printing PDFCarlo DizonNo ratings yet

- Eclipse IDE Tutorial: Lars VogelDocument23 pagesEclipse IDE Tutorial: Lars VogelBabu ChaudharyNo ratings yet

- ARTERY NuggetX USER MANUALDocument2 pagesARTERY NuggetX USER MANUALaiaiyayaNo ratings yet

- UPDPCL6Win 3100MUDocument5 pagesUPDPCL6Win 3100MURaluca MarinescuNo ratings yet

- Chapter 10 ExamDocument10 pagesChapter 10 ExamOngHongTeckNo ratings yet

- Asad Irfan CV For CSR TeraDataDocument3 pagesAsad Irfan CV For CSR TeraDataAsad IrfanNo ratings yet

- COMOS Quickstart DeveloperDocument27 pagesCOMOS Quickstart DeveloperCristi CrseNo ratings yet

- Manual CivCity RomeDocument38 pagesManual CivCity RomeLuciana RodriguesNo ratings yet

- Merni Instrumenti PDFDocument108 pagesMerni Instrumenti PDFMareHCNo ratings yet

- Ec8691 - Microprocessors and Microcontrollers: Question BankDocument5 pagesEc8691 - Microprocessors and Microcontrollers: Question Bankrkkumar07No ratings yet

- Penawaran lb1 BNPTDocument2 pagesPenawaran lb1 BNPTAgus OgeNo ratings yet