Professional Documents

Culture Documents

MC74F544

MC74F544

Uploaded by

ir.setia.utamaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

MC74F544

MC74F544

Uploaded by

ir.setia.utamaCopyright:

Available Formats

MC74F544

OCTAL REGISTERED

TRANSCEIVER, INVERTING,

3-STATE

OCTAL REGISTERED

The MC74F544 Octal Registered Transceivers contain two sets of D-Type

TRANSCEIVER, INVERTING,

latches for temporary storage of data flowing in either direction. Separate

Latch Enable (LEAB, LEBA) and Enable (OEAB, OEBA) inputs are provided 3-STATE

for each register to permit independent control of inputting and outputting in FAST SCHOTTKY TTL

either direction of data flow. The MC74F544 has an inverting data path. The

A outputs are guaranteed to sink 24 mA while the B outputs are rated for

64 mA.

• Combines 74F245 and 74F373 Type Functions in One Chip

• 8-Bit Octal Transceiver

• Inverting

• Back-to-Back Registers for Storage

• Separate Controls for Data Flow in Each Direction N SUFFIX

• Glitchless Outputs During 3-State Power Up or Power Down Operation 24

PLASTIC

• High Impedance Outputs in Power Off State 1

CASE 724-03

• A Outputs Sink 24 mA and Source 3.0 mA

• B Outputs Sink 64 mA and Source 15 mA

• See F543 for Noninverting Version

• ESD Protection > 4000 Volts

DW SUFFIX

24 SOIC

1 CASE 751E-03

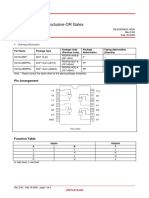

PIN ASSIGNMENT

VCC EBA B0 B1 B2 B3 B4 B5 B6 B7 LEAB OEAB

24 23 22 21 20 19 18 17 16 15 14 13

ORDERING INFORMATION

MC74FXXXN Plastic

MC74FXXXDW SOIC

1 2 3 4 5 6 7 8 9 10 11 12

LEBA OEBA A0 A1 A2 A3 A4 A5 A6 A7 EAB GND

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

VCC DC Supply Voltage 74 4.5 5.0 5.5 V

TA Operating Ambient Temperature Range 74 0 25 70 °C

IOH Output Current — High 74 — — – 3.0 / – 15 mA

IOL Output Current — Low 74 — — 24 / 64 mA

FAST AND LS TTL DATA

4-216

MC74F544

FUNCTION TABLE

Inputs

OEXX EXX LEXX Data Outputs Status

H X X X Z Outputs disabled

X H X X Z Outputs disabled

L ↑ L l Z Outputs disabled

L ↑ L h Z Data latched

L L ↑ l H

Data latched

L L ↑ h L

L L L L H

Transparent

L L L H L

L L H X NC Hold

H = HIGH voltage level: h = HIGH state must be present one set-up time before the LOW-to-HIGH transition of LEXX or EXX (XX = AB or BA): L = LOW voltage level:

l = LOW state must be present one set-up time before the LOW-to-HIGH transition of LEXX or EXX (XX = AB or BA): X = Don’t care: Z = HIGH impedance state:

NC = No Change.

FUNCTIONAL DESCRIPTION

The MC74F544 contains two sets of eight D-type latches, transition of the LEAB signal puts the A latches in the storage

with separate input and controls for each set. For data flow mode and their outputs no longer change with the A inputs.

from A to B, for example, the A-to-B Enable (EAB) input must With EAB and OEAB both LOW, the 3-State B output buffers

be LOW in order to enter data from A0 – A7 or take data from are active and reflect the inverted data present at the output

B0 – B7, as indicated in the Function Table. With EAB LOW, of the A latches. Control of data flow from B to A is similar, but

a LOW signal on the A-to-B latch enable (LEAB) input makes using the EBA, LEBA, and OEBA inputs.

the A-to-B latches transparent; a subsequent LOW-to-HIGH

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Limits Test Conditions

Symbol Parameter Min Typ Max Unit (Note 1)

VIH Input HIGH Voltage 2.0 — — V Guaranteed Input HIGH Voltage

VIL Input LOW Voltage — — 0.8 V Guaranteed Input LOW Voltage

VIK Input Clamp Diode Voltage — – 0.73 – 1.2 V VCC = MIN, IIN = – 18 mA

2.4 — — VCC = 4.5 V

A0 – A7 74 V IOH = – 3.0 mA

VOH Output HIGH Voltage 2.7 3.4 — VCC = 4.75 V

B0 – B7 74 2.0 — — V IOH = – 15 mA VCC = 4.5 V

A0 – A7 74 — 0.35 0.5 V IOL = 24 mA

VOL Output LOW Voltage VCC = MIN

B0 – B7 74 — 0.4 0.55 V IOL = 64 mA

I/O Pins — — 1.0 mA VCC = MAX, VIN = 5.5 V

Control Pins — — 100 µA VCC = MAX, VIN = 7.0 V

IIH Input HIGH Current

Control Pins — — 20 µA

VCC = MAX, VIN = 2.7 V

I/O Pins — — 70 µA

EAB, EBA — — – 1.2

IIL Input LOW Current mA VCC = MAX, VIN = 0.5 V

Other Inputs — — – 0.6

IOZH Off-State Output Current — — 70 µA VCC = MAX, VOUT = 2.7 V

Off-State Output Current,

IOZL — — – 600 µA VCC = MAX, VOUT = 0.5 V

Low-Level Voltage Applied

An Outputs – 60 — –150

IOS Output Short Circuit Current (Note 2) mA VCC = MAX, VOUT = 0 V

Bn Outputs – 100 — –225

ICCH — 70 105

ICC Total Supply Current ICCL — 95 130 mA VCC = MAX

ICCZ — 95 125

NOTES:

1. For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.

2. Not more than one output should be shorted at a time, nor for more than 1 second.

FAST AND LS TTL DATA

4-217

MC74F544

AC ELECTRICAL CHARACTERISTICS

74F 74F

TA = + 25°C TA = 0 °C to + 70°C

VCC = + 5.0 V VCC = + 5.0 V ± 10%

CL = 50 pF CL = 50 pF

Symbol Parameter Min Typ Max Min Max Unit

Propagation Delay

tPLH 2.0 — 9.5 2.0 10.5

Transparent Mode ns

tPHL 2.0 — 6.5 2.0 7.5

An to Bn or Bn to An

tPLH Propagation Delay 6.0 — 13 6.0 14.5

ns

tPHL LEBA to An 4.0 — 9.5 4.0 10.5

tPLH Propagation Delay 6.0 — 13 6.0 14.5

ns

tPHL LEAB to Bn 4.0 — 9.5 4.0 10.5

Output Enable Time

tPZH 3.0 — 9.0 3.0 10

OEBA or OEAB to An or Bn ns

tPZL 4.0 — 10.5 4.0 12

EBA or EAB to An or Bn

Output Disable Time

tPHZ 1.5 — 8.0 1.5 9.0

OEBA or OEAB to An or Bn ns

tPLZ 1.5 — 7.5 1.5 8.5

EBA or EAB to An or Bn

AC OPERATING REQUIREMENTS

74F 74F

TA = + 25°C TA = 0°C to + 70°C

VCC = + 5.0 V VCC = + 5.0 V ± 10%

CL = 50 pF CL = 50 pF

Symbol Parameter Min Typ Max Min Typ Max Unit

ts(H) Setup Time, HIGH or LOW 3.0 — — 3.0 — —

ns

ts(L) An or Bn to LEBA or LEAB 3.0 — — 3.0 — —

th(H) Hold Time, HIGH or LOW 3.0 — — 3.0 — —

ns

th(L) An to Bn to LEBA or LEAB 3.0 — — 3.0 — —

tw(L) Latch Enable, B to A

6.0 — — 7.5 — — ns

Pulse Width, LOW

FAST AND LS TTL DATA

4-218

MC74F544

LOGIC DIAGRAM

DETAIL A

D Q B0

LE D

A0 Q LE

A1 B1

A2 B2

A3 B3

A4 DETAIL A X 7 B4

A5 B5

A6 B6

A7 B7

OEBA

OEAB

EBA

EAB

LEBA

LEAB

NOTE:

Please note that this diagram is provided only for the understanding of logic

operations and should not be used to estimate propagation delays.

FAST AND LS TTL DATA

4-219

You might also like

- CD4538Document11 pagesCD4538Sridhar MohanNo ratings yet

- 3 To 8 Line Decoder: Order CodesDocument10 pages3 To 8 Line Decoder: Order CodesSero StivNo ratings yet

- 74ACT573Document11 pages74ACT573Hamzah AlbrakaniNo ratings yet

- Sn74lvc157a q1Document14 pagesSn74lvc157a q1Gabriel aquinoNo ratings yet

- Quad 2 Channel Multiplexer (3-State) : PD CC oDocument10 pagesQuad 2 Channel Multiplexer (3-State) : PD CC oSero StivNo ratings yet

- Quad 2 Channel Multiplexer (3-State) : Order CodesDocument12 pagesQuad 2 Channel Multiplexer (3-State) : Order CodesSero StivNo ratings yet

- MM74HC4538 Dual Retriggerable Monostable Multivibrator: General DescriptionDocument10 pagesMM74HC4538 Dual Retriggerable Monostable Multivibrator: General DescriptionAlex WongNo ratings yet

- MM74HC574 3-STATE Octal D-Type Edge-Triggered Flip-Flop: General Description FeaturesDocument8 pagesMM74HC574 3-STATE Octal D-Type Edge-Triggered Flip-Flop: General Description Featureskumar_santosh1989100% (1)

- Datasheet PDFDocument4 pagesDatasheet PDFMauricio MontañoNo ratings yet

- Low Voltage Quad 2 Channel Multiplexer: PD CCDocument8 pagesLow Voltage Quad 2 Channel Multiplexer: PD CCjoelpalzaNo ratings yet

- MM74HCT373 - MM74HCT374 3-STATE Octal D-Type Latch - 3-STATE Octal D-Type Flip-FlopDocument11 pagesMM74HCT373 - MM74HCT374 3-STATE Octal D-Type Latch - 3-STATE Octal D-Type Flip-FlopJose CNo ratings yet

- Octal D-Type Flip Flop With Clear: Order CodesDocument12 pagesOctal D-Type Flip Flop With Clear: Order CodesSero StivNo ratings yet

- MM74HC123A FairchildSemiconductorDocument9 pagesMM74HC123A FairchildSemiconductorАлексей ГомоновNo ratings yet

- 74ACQ244 - 74ACTQ244 Quiet Series Octal Buffer/Line Driver With 3-STATE OutputsDocument10 pages74ACQ244 - 74ACTQ244 Quiet Series Octal Buffer/Line Driver With 3-STATE OutputsStuxnetNo ratings yet

- M54HC393 M74HC393: Dual Binary CounterDocument12 pagesM54HC393 M74HC393: Dual Binary CounternooorNo ratings yet

- 74LVX245 Low Voltage Octal Bidirectional Transceiver: General Description FeaturesDocument6 pages74LVX245 Low Voltage Octal Bidirectional Transceiver: General Description FeaturesStuxnetNo ratings yet

- 54F/74F544 Octal Registered Transceiver: General Description FeaturesDocument10 pages54F/74F544 Octal Registered Transceiver: General Description FeaturesnooorNo ratings yet

- SMD-DatasheetDocument8 pagesSMD-DatasheetAhmed Sherif CupoNo ratings yet

- Data Sheet: 74AHC373 74AHCT373Document21 pagesData Sheet: 74AHC373 74AHCT373quasemanobrasNo ratings yet

- Data Sheet: 74HC/HCT540Document7 pagesData Sheet: 74HC/HCT540Diego GrisalesNo ratings yet

- 74LCX245 Low Voltage Bidirectional Transceiver With 5V Tolerant Inputs and OutputsDocument14 pages74LCX245 Low Voltage Bidirectional Transceiver With 5V Tolerant Inputs and OutputsozmeenNo ratings yet

- Data Sheet: 74HC/HCT240Document7 pagesData Sheet: 74HC/HCT240ALFREDO MORALESNo ratings yet

- DM54LS73A/DM74LS73A Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops With Clear and Complementary OutputsDocument6 pagesDM54LS73A/DM74LS73A Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops With Clear and Complementary Outputs4ew018No ratings yet

- MLK II Hardware.Document78 pagesMLK II Hardware.Venkatesh KumarNo ratings yet

- CD40174BC - CD40175BC Hex D-Type Flip-Flop - Quad D-Type Flip-FlopDocument7 pagesCD40174BC - CD40175BC Hex D-Type Flip-Flop - Quad D-Type Flip-FlopCristian MancholaNo ratings yet

- Octal Bus Buffer With 3 State Outputs (Non Inverted) : PD CC oDocument9 pagesOctal Bus Buffer With 3 State Outputs (Non Inverted) : PD CC ocriman45No ratings yet

- 74VHCT139A: Dual 2 To 4 Decoder/DemultiplexerDocument8 pages74VHCT139A: Dual 2 To 4 Decoder/DemultiplexerCyro PereiraNo ratings yet

- SN75176BDocument12 pagesSN75176Bjnfgames1No ratings yet

- 3 To 8 Line Decoder: PD CC oDocument9 pages3 To 8 Line Decoder: PD CC oSero StivNo ratings yet

- Datasheet LVC4245Document8 pagesDatasheet LVC4245AdamTrisnoizeAgustianNo ratings yet

- Data Sheet: HEF40244B BuffersDocument6 pagesData Sheet: HEF40244B BuffersvanmarteNo ratings yet

- Data Sheet: HEF40244B BuffersDocument6 pagesData Sheet: HEF40244B BuffersDaniel Norberto DemariaNo ratings yet

- 74LVC244A/74LVCH244A: Octal Buffer/line Driver With 5-Volt Tolerant Inputs/outputs (3-State) TitleDocument10 pages74LVC244A/74LVCH244A: Octal Buffer/line Driver With 5-Volt Tolerant Inputs/outputs (3-State) TitleDarleiDuarteNo ratings yet

- 74HC151 PDFDocument11 pages74HC151 PDFJacob JayaseelanNo ratings yet

- 74 Vhcu 04Document11 pages74 Vhcu 04COZLNo ratings yet

- Driver IC IntroduceDocument48 pagesDriver IC IntroducespotNo ratings yet

- HD74LS86: Quadruple 2-Input Exclusive-OR GatesDocument5 pagesHD74LS86: Quadruple 2-Input Exclusive-OR GatesRamírez López Erik SandroNo ratings yet

- DatasheetDocument6 pagesDatasheetStuxnetNo ratings yet

- TC74HC238AP, TC74HC238AF: 3-To-8 Line DecoderDocument8 pagesTC74HC238AP, TC74HC238AF: 3-To-8 Line DecoderAriangel MasoNo ratings yet

- DM74LS73A Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops With Clear and Complementary OutputsDocument5 pagesDM74LS73A Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops With Clear and Complementary OutputsJoão AlmeidaNo ratings yet

- Quad Set-Reset Latch SN54/74LS279: Low Power SchottkyDocument5 pagesQuad Set-Reset Latch SN54/74LS279: Low Power Schottkytzf32799No ratings yet

- 74AC244 - 74ACT244 Octal Buffer/Line Driver With 3-STATE OutputsDocument10 pages74AC244 - 74ACT244 Octal Buffer/Line Driver With 3-STATE OutputsshohratNo ratings yet

- 74VHC244 Octal Buffer/Line Driver With 3-STATE Outputs: General Description FeaturesDocument8 pages74VHC244 Octal Buffer/Line Driver With 3-STATE Outputs: General Description FeaturesrzvNo ratings yet

- Data Sheet: 74HC/HCT541Document7 pagesData Sheet: 74HC/HCT541adilNo ratings yet

- DM74LS194A 4-Bit Bidirectional Universal Shift RegisterDocument6 pagesDM74LS194A 4-Bit Bidirectional Universal Shift Registerhayssam100% (1)

- M54HC259 M74HC259: 8 Bit Addressable LatchDocument12 pagesM54HC259 M74HC259: 8 Bit Addressable LatchnooorNo ratings yet

- LVC 244a NXPDocument17 pagesLVC 244a NXPChethan RajNo ratings yet

- 74HCT4045NDocument5 pages74HCT4045NQuien SabeNo ratings yet

- DatasheetDocument14 pagesDatasheetFernando Rodriguez RuizNo ratings yet

- 74HC HCT132 CNV 2Document9 pages74HC HCT132 CNV 2Diego de Leon CenozNo ratings yet

- Data Sheet: 74HC/HCT251Document7 pagesData Sheet: 74HC/HCT251kennyfernandezNo ratings yet

- 74HC-HCT251x Eng DatasheetDocument7 pages74HC-HCT251x Eng Datasheetjohn9999_502754No ratings yet

- SN74HC4851-Q1 8-Channel Analog Multiplexer/Demultiplexer With Injection-Current Effect ControlDocument20 pagesSN74HC4851-Q1 8-Channel Analog Multiplexer/Demultiplexer With Injection-Current Effect ControlJoil LeandroNo ratings yet

- MM74HC74A Dual D-Type Flip-Flop With Preset and Clear: Features General DescriptionDocument11 pagesMM74HC74A Dual D-Type Flip-Flop With Preset and Clear: Features General DescriptionAle MorenoNo ratings yet

- 74LS194Document6 pages74LS194ChanjayNo ratings yet

- 74LS107 JK Flip FlopDocument7 pages74LS107 JK Flip FlopQuartz AlexanderNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- ECO Timing Optimization Using Spare Cells2Document31 pagesECO Timing Optimization Using Spare Cells2Siva RaoNo ratings yet

- 7 Parallel Adder Subs TractorDocument3 pages7 Parallel Adder Subs TractorSohil VohraNo ratings yet

- Which Cell Has Lowest Area Among Hvt, Lvt and Svt Cells - -CSDN博客Document1 pageWhich Cell Has Lowest Area Among Hvt, Lvt and Svt Cells - -CSDN博客AgnathavasiNo ratings yet

- MPMC Unit 2Document31 pagesMPMC Unit 2nikitaNo ratings yet

- Introducere in Programarea MicrocontrollerelorDocument49 pagesIntroducere in Programarea MicrocontrollerelorJustin PuscasuNo ratings yet

- Sequential Circuit Design: Slides ForDocument23 pagesSequential Circuit Design: Slides ForRamarao ChNo ratings yet

- Quad Differential Line Driver: FeaturesDocument4 pagesQuad Differential Line Driver: Featurespepe_aobNo ratings yet

- Parts of A Motherboard and Their FunctionDocument9 pagesParts of A Motherboard and Their FunctionAjoyNo ratings yet

- Micro WindDocument14 pagesMicro Windlak_prabNo ratings yet

- Universal Gates NANDDocument13 pagesUniversal Gates NANDAhmad BilalNo ratings yet

- Labs-VLSI Lab ManualDocument56 pagesLabs-VLSI Lab ManualAbdul Basit Awan50% (2)

- Tmax For ATPG N DiagnosisDocument23 pagesTmax For ATPG N DiagnosisUmesh ParasharNo ratings yet

- Digital SheetDocument20 pagesDigital SheetTAY CHUI SHENG100% (1)

- Pic MicrocontrollerDocument5 pagesPic MicrocontrollerFarhat AbbasNo ratings yet

- CSC 209 Notes SplitDocument57 pagesCSC 209 Notes SplitBello TaiwoNo ratings yet

- Serial Pic Programmer: Jens Dyekjar MadsenDocument1 pageSerial Pic Programmer: Jens Dyekjar MadsenJovial JovNo ratings yet

- Lab1 MultisimCircuitSimulationDocument24 pagesLab1 MultisimCircuitSimulationKata MedinaNo ratings yet

- 22m1145 Vlsidesign 1Document16 pages22m1145 Vlsidesign 1sivaNo ratings yet

- Unidentified Alarm Occurrence / Run CPU Address Error: TCD-002 TCD - 003Document1 pageUnidentified Alarm Occurrence / Run CPU Address Error: TCD-002 TCD - 003NoahNo ratings yet

- Chapter 5-Sequential Circuits, Counters and RegistersDocument99 pagesChapter 5-Sequential Circuits, Counters and RegistersSara Tilahun100% (1)

- Computer Organization and ArchitectureDocument173 pagesComputer Organization and ArchitecturesalithakkNo ratings yet

- CD 40102 BDocument13 pagesCD 40102 BPradeepa SenanayakeNo ratings yet

- Vlsi Lab Manual 2013Document64 pagesVlsi Lab Manual 2013harish33330% (1)

- Experiment 3: Boolean Algebra.Document13 pagesExperiment 3: Boolean Algebra.MOHD MU'IZZ BIN MOHD SHUKRINo ratings yet

- C5 ProbDocument4 pagesC5 ProbMihir Kumar MechNo ratings yet

- Trilithic Bts 780 GP: 1 FeaturesDocument18 pagesTrilithic Bts 780 GP: 1 FeaturesshohratNo ratings yet

- Astable Multivibrator Using TransistorsDocument24 pagesAstable Multivibrator Using TransistorsChalez ZengeretsiNo ratings yet

- Uc 1825Document23 pagesUc 1825saiful IslamNo ratings yet

- Maximum Mode 8086 SystemDocument9 pagesMaximum Mode 8086 Systemchenna838No ratings yet

- Ahp31 Ma1phDocument24 pagesAhp31 Ma1phRittal 96No ratings yet