Professional Documents

Culture Documents

MPI Module-1 4

MPI Module-1 4

Uploaded by

d4e5e5p200 ratings0% found this document useful (0 votes)

4 views3 pagesThe document discusses demultiplexing the address/data bus of a microprocessor using the 74LS373 IC. It describes a 4-step process: (1) the address is loaded onto the bus and latched by the 74LS373 IC, (2) the address is frozen at the IC output freeing the bus, (3) the full address is available and the bus is now free to be used for data, (4) data is retrieved from memory onto the now free bus. Address and data buffers in the 8085 microprocessor are also described as performing bidirectional transfer and increasing the driving capacity of signals to external chips.

Original Description:

Original Title

MPI_Module-1_4

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThe document discusses demultiplexing the address/data bus of a microprocessor using the 74LS373 IC. It describes a 4-step process: (1) the address is loaded onto the bus and latched by the 74LS373 IC, (2) the address is frozen at the IC output freeing the bus, (3) the full address is available and the bus is now free to be used for data, (4) data is retrieved from memory onto the now free bus. Address and data buffers in the 8085 microprocessor are also described as performing bidirectional transfer and increasing the driving capacity of signals to external chips.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

4 views3 pagesMPI Module-1 4

MPI Module-1 4

Uploaded by

d4e5e5p20The document discusses demultiplexing the address/data bus of a microprocessor using the 74LS373 IC. It describes a 4-step process: (1) the address is loaded onto the bus and latched by the 74LS373 IC, (2) the address is frozen at the IC output freeing the bus, (3) the full address is available and the bus is now free to be used for data, (4) data is retrieved from memory onto the now free bus. Address and data buffers in the 8085 microprocessor are also described as performing bidirectional transfer and increasing the driving capacity of signals to external chips.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 3

Module-1

Demultiplexing of the Buses:

All computer systems have three buses: (1) an address bus that provides the memory and I/O

with the memory address or the I/O port number, (2) a data bus that transfers data between the

microprocessor and the memory and I/O in the system, and (3) a control bus that provides

control signals to the memory and I/O. These buses must be present in order to interface to

memory and I/O.

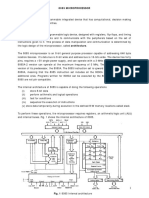

Demultiplexing of AD0-AD7 using IC 74LS373

The dual-purpose of the AD0-AD7 pins is achieved through multiplexing. In simple words,

multiplexing allows us to use the pins of a microprocessor for more than one function.

But for extracting the data and the lower 8 bits of the address, we demultiplex AD0-AD7 using

IC 74LS373. Let me explain it through an example.

First, let us get to know the working of IC 74LS373.

Circuit setup for the demultiplexing of AD0-AD7 using IC 74LS373

Let us go through the process step by step. Let us assume that instruction MOV C, A is to be

executed. For executing the instruction, the microprocessor first has to read the opcode (hex

code for the instruction) stored at 2005H. The hex code here is 4FH. You can ignore things and

just look at it as “microprocessor reading data at a memory location having the address 2005H.”

Step1

The whole process consists of 4 T states or 4 clock cycles (refer to the timing diagram above). In

the first clock cycle, the higher 8 bits of the address (20H) are loaded in A8-A15. At the same

time, the lower 8 bits of the address (05H) are issued at pins AD0-AD7. Also, the ALE signal

issued by the microprocessor is high, telling that AD0-AD7 contains the lower 8 bits of the

address. (i.e., the pins are currently functioning as address pins.)

Notice that in the circuit diagram, the ALE signal is connected to the LE (latch enable) pin of the

IC. This ensures that the address received at the input of the 74LS373 IC (05H) is reflected at its

output (i.e., the output of the 74LS373 IC is 05H).

Step2

Near the end of the first clock cycle, the ALE signal goes low. Whatever bits were there on

AD0-AD7 (in this case, 05H) at that instant are latched (frozen) in the IC. That means, those bits

are present at the output of the IC and are not affected by the values on AD0-AD7 anymore.

You see, the entire reason behind this exercise is to help the pins (AD0-AD7) carry two different

types of values on the same path. We do this by carrying one of the values first (the address),

handing it over to the IC with the latches (memory units) to hold on to, and then getting the other

set of values.

Step3

Now, all the 16 bits of the address are available. Higher 16 bits at A8-A15 and lower 8 bits at the

outputs of the IC. This means that AD0-AD7 is free now. It can now be used as the data bus.

Now, during the second and third clock cycles, 8-bit data to be fetched (4FH) is loaded on AD0-

AD7 from memory and is retrieved by the microprocessor. Note that in this step, AD0-AD7 is

being used as the data bus.

This is how the demultiplexing of AD0-AD7 works.

Address/data buffers in 8085 Microprocessor:

Address and data buffers are used for bidirectional data transfer. They perform the

unidirectional data transfer when they send out the Least Significant Byte of the address. These

buffers are only used for increasing the driving capacity of the current. Through the internal bus

data goes to the buffers. The Least Significant Byte of the address goes to the buffers from the

internal address latch to the other.

Hence the address or data are sent out on the address ranging from AD7 to AD0 can drive every

external chips, like chips of RAM, chips of EPROM, and other peripheral chips meant for

carrying the work. Likewise, all the data received by the 8085 microprocessor from the outside

is also buffered internally. The data on the range of address ranging from AD7 to AD0 also

reaches to the internal bus, from where the final destination is reached.

In fact, also in a practical microcomputer system, the driving capacity for the data pins, after the

internal buffering procedure, might not be satisfactory. So there will always be external buffer

chips to carry out the entire work.

Address buffers: These buffers are meant for unidirectional transfer of schematic addresses

which are only used for sending out the Most Significant Byte of the given address. The Most

Significant Byte of the address goes to the buffers from the address latch internally. Hence the

address sent out to the range of address ranging from AD15 to AD7 drives all the external chips,

like chips of RAM, chips of EPROM, and other peripheral chips.

Obviously in a practical microcomputer system, the driving capacity of the address pins, after

the internal buffering, might not be satisfactory. So there must be external buffer chips to carry

out the work.

You might also like

- Ukelele 3.2 TutorialDocument54 pagesUkelele 3.2 TutorialJeffersonNo ratings yet

- Global Mapper Crack 24.0 Full Version Free (64-Bit) 2023-ShortcrackDocument7 pagesGlobal Mapper Crack 24.0 Full Version Free (64-Bit) 2023-Shortcrackshortcrack.com0% (1)

- Interfacing With The ISA BusDocument12 pagesInterfacing With The ISA BusseyfiNo ratings yet

- Lecture 3Document43 pagesLecture 3Said AhmedNo ratings yet

- Experiment No. 1: Department of Electronics & Comm - EnggDocument7 pagesExperiment No. 1: Department of Electronics & Comm - EnggJaspreet KaurNo ratings yet

- EEE - BEE603 - Microprocessor and Microcontroller - Mr. K. DwarakeshDocument24 pagesEEE - BEE603 - Microprocessor and Microcontroller - Mr. K. Dwarakeshsatishcoimbato12No ratings yet

- Microprocessors and Its Applications Short AnswersDocument15 pagesMicroprocessors and Its Applications Short AnswersVidya MuthukrishnanNo ratings yet

- 8085 Microproceesor - PPTDocument59 pages8085 Microproceesor - PPTShanagonda Manoj KumarNo ratings yet

- Question Bank MPDocument58 pagesQuestion Bank MPindu7405No ratings yet

- Chapter 3Document35 pagesChapter 3ajayroyNo ratings yet

- Basic Concepts in Serial I/O Interfacing I/O DevicesDocument33 pagesBasic Concepts in Serial I/O Interfacing I/O DevicessubendNo ratings yet

- 8085 PDocument31 pages8085 PAnish ChibNo ratings yet

- 8085microproceesor ArchitectureDocument60 pages8085microproceesor ArchitecturePooja Anand JhaNo ratings yet

- 8085 ArchitectureDocument38 pages8085 ArchitectureReethu ParavadaNo ratings yet

- Malp Chapter 1Document15 pagesMalp Chapter 1Anonymous jyr4IyGRpNo ratings yet

- PIN Diagram of Intel 8085 Microprocessor - Lecture 3Document14 pagesPIN Diagram of Intel 8085 Microprocessor - Lecture 3ojasbhosale07No ratings yet

- IO InterfacingDocument13 pagesIO InterfacingKrishna SaladiNo ratings yet

- 8085 MicroprocessorDocument38 pages8085 MicroprocessorPrateek PandeyNo ratings yet

- Microprocessor 8085 ADocument134 pagesMicroprocessor 8085 ASaumya MohanNo ratings yet

- Syllabus: 8085 ArchitectureDocument25 pagesSyllabus: 8085 Architecturetamilvendhan87No ratings yet

- Microprocessor 8085 ArchitectureDocument8 pagesMicroprocessor 8085 ArchitectureHarjot KaurNo ratings yet

- Introduction To Microprocessor and Microcomputer ArchitectureDocument6 pagesIntroduction To Microprocessor and Microcomputer Architecturesri vatsaNo ratings yet

- 8085 ArchitectureDocument13 pages8085 ArchitectureShubham BokoliaNo ratings yet

- CN 320: Microprocessor and Microcontroller SystemsDocument40 pagesCN 320: Microprocessor and Microcontroller SystemsAlango Jr TzNo ratings yet

- Unit-I: 8-Bit MicroprocessorsDocument55 pagesUnit-I: 8-Bit MicroprocessorsAASTHA KIETNo ratings yet

- 20 سؤال معماريةDocument23 pages20 سؤال معماريةمصطفى شاكر محمودNo ratings yet

- 8085 ArchitectureDocument31 pages8085 Architecturevellore gatewayNo ratings yet

- Presentation 1Document23 pagesPresentation 1khushalee.chavadaNo ratings yet

- MCT Unit 2Document26 pagesMCT Unit 2Aravind RajNo ratings yet

- 8086 Interfacing-Chap 5Document36 pages8086 Interfacing-Chap 5Krishnaveni DhulipalaNo ratings yet

- Memory InterfacingDocument16 pagesMemory InterfacingTharshninipriya RajasekarNo ratings yet

- Unit IIDocument13 pagesUnit IIJuhi MauryaNo ratings yet

- 8085 MaterialDocument12 pages8085 MaterialsameerNo ratings yet

- Microprocessor 8085Document25 pagesMicroprocessor 8085hetal_limbaniNo ratings yet

- The 8085 Microprocessor ArchitectureDocument39 pagesThe 8085 Microprocessor ArchitectureAhmed YassinNo ratings yet

- 8085 MicroprocessorDocument16 pages8085 MicroprocessorVinay FelixNo ratings yet

- The 8085 Microprocessor ArchitectureDocument33 pagesThe 8085 Microprocessor Architecturemodismm330% (1)

- 20cat352 Unit 2 NotesDocument11 pages20cat352 Unit 2 NotesNehaNo ratings yet

- MM Assignmemt 1Document10 pagesMM Assignmemt 1ALL ÎÑ ÔÑÈNo ratings yet

- Peripheral InterfacingDocument32 pagesPeripheral Interfacingsulekha saxenaNo ratings yet

- 8086 Microprocessor Is An Enhanced Version of 8085microprocessor That Was Designed by Intel in 1976Document17 pages8086 Microprocessor Is An Enhanced Version of 8085microprocessor That Was Designed by Intel in 1976pradeep akellaNo ratings yet

- 8085Document56 pages8085Kunal MeherNo ratings yet

- 8085 ArchitectureDocument26 pages8085 ArchitectureLukeNo ratings yet

- MP04 - 8086 HardwareDocument12 pagesMP04 - 8086 HardwareEhmed BazNo ratings yet

- CH-6 8086 Microprocessor InterfacingDocument8 pagesCH-6 8086 Microprocessor InterfacingAnikhet MulkyNo ratings yet

- Ece 8085 MicroprocessorDocument26 pagesEce 8085 Microprocessorgourav VermaNo ratings yet

- Unit Ii 8085 Micro Processor 8085 Architecture:: ME 6702 Mechatronics Mechanical Engineering 2019-20Document26 pagesUnit Ii 8085 Micro Processor 8085 Architecture:: ME 6702 Mechatronics Mechanical Engineering 2019-20GopinathNo ratings yet

- 8085 Features, Signal DescriptionDocument13 pages8085 Features, Signal DescriptionRakesh Kumar DNo ratings yet

- Eec 503 PDFDocument22 pagesEec 503 PDFmohitNo ratings yet

- of Unit-1: Introduction To Microprocessor and Microprocessor 8085Document22 pagesof Unit-1: Introduction To Microprocessor and Microprocessor 8085abahynNo ratings yet

- 8085 Architecture IntroductionDocument25 pages8085 Architecture IntroductionMohamed Musthafa100% (1)

- Microprocessor - SGDocument15 pagesMicroprocessor - SGSugata Ghosh0% (1)

- ECE 314 Microprocessor Microcontroller Systems WK6to8 Module 1CTDDocument66 pagesECE 314 Microprocessor Microcontroller Systems WK6to8 Module 1CTDpaige forelsterNo ratings yet

- MPD e ContentsDocument112 pagesMPD e Contentsmeera joshiNo ratings yet

- Questionnaire MICROPROCESSOR PART 1 UNIT 1 and 2Document20 pagesQuestionnaire MICROPROCESSOR PART 1 UNIT 1 and 2aditya2021cs081No ratings yet

- Microprocessor - 8086Document14 pagesMicroprocessor - 8086Poet FaroukNo ratings yet

- C6713 DSP Lab Mannual 2Document40 pagesC6713 DSP Lab Mannual 2dangvuduongNo ratings yet

- Study of 8085 and Kit STS-85Document10 pagesStudy of 8085 and Kit STS-85Mohammed MansoorNo ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- The Use of Skimming and Scanning Techniques For College Students in Reading Class Destri WahyuningsihDocument4 pagesThe Use of Skimming and Scanning Techniques For College Students in Reading Class Destri Wahyuningsihkhanh linhNo ratings yet

- Gen Chem 2Document2 pagesGen Chem 2Trisha Camille MacarioNo ratings yet

- Unit Lesson 1Document6 pagesUnit Lesson 1api-547362187No ratings yet

- Aep Lesson Abstract Art Adjectives FinalDocument5 pagesAep Lesson Abstract Art Adjectives Finalapi-457854718No ratings yet

- Grammar Reference: Types of SentencesDocument2 pagesGrammar Reference: Types of SentencesJagdeepNo ratings yet

- Guided DiscoveryDocument5 pagesGuided DiscoverySvetlana ShcherbaNo ratings yet

- Matlab - Generating Sine and Cosine WavesDocument8 pagesMatlab - Generating Sine and Cosine WaveslentelsoupNo ratings yet

- Data Communication Computer Network Question BankDocument4 pagesData Communication Computer Network Question BankRAJESH100% (5)

- DLL - Mapeh 4 - Q1 - W6Document6 pagesDLL - Mapeh 4 - Q1 - W6Elmo SabioNo ratings yet

- Background of The StudyDocument7 pagesBackground of The StudyVENICE LARA SOLIVERESNo ratings yet

- OS - All-5-UnitDocument185 pagesOS - All-5-UnithariNo ratings yet

- MODULE 7 SYNTAX Plus WorksheetsDocument13 pagesMODULE 7 SYNTAX Plus WorksheetsShean Jerica Salem100% (1)

- Relative ClauseDocument7 pagesRelative ClausePianike WidiawatiNo ratings yet

- Red Hat Enterprise Virtualization 3.1 Administration Guide en USDocument374 pagesRed Hat Enterprise Virtualization 3.1 Administration Guide en USbangbus77No ratings yet

- HIWD320 Article Assessment Template PDFDocument1 pageHIWD320 Article Assessment Template PDFAlexNo ratings yet

- ELE 4613 - ProjectDocument6 pagesELE 4613 - ProjectmukulNo ratings yet

- Issue 2 Feb 2017Document24 pagesIssue 2 Feb 2017Packirisamy NeelagandamNo ratings yet

- Excerpt From The Rubaiyat by Omar KhayyamDocument12 pagesExcerpt From The Rubaiyat by Omar KhayyamElvis ViernesNo ratings yet

- Classroom ExpressionDocument6 pagesClassroom ExpressionfangartsignatureNo ratings yet

- Test 209Document31 pagesTest 209venitiaNo ratings yet

- LOD Specification 2015Document195 pagesLOD Specification 2015maison_orionNo ratings yet

- Lost City-Machu Picchu SmallDocument64 pagesLost City-Machu Picchu Smalljanhavi28No ratings yet

- Java Magazine JUnit 5 ArrivesDocument75 pagesJava Magazine JUnit 5 ArriveskottamramreddyNo ratings yet

- TOP 50 ASP QuestionsDocument5 pagesTOP 50 ASP QuestionsJohn DoeNo ratings yet

- The Ring of Gyges For GethicsDocument6 pagesThe Ring of Gyges For GethicsLei Anne GacayanNo ratings yet

- Implementing Shadowing Technique to Improve Pronunciation of English-majored Freshmen- Nguyễn Trung TàiDocument49 pagesImplementing Shadowing Technique to Improve Pronunciation of English-majored Freshmen- Nguyễn Trung TàiNguyễn Trung TàiNo ratings yet

- Installation Ceremony-ScriptDocument2 pagesInstallation Ceremony-ScriptAng Kampilan50% (2)

- DLL - English 4 - Q3 - W2Document6 pagesDLL - English 4 - Q3 - W2Raiset HermanNo ratings yet