Professional Documents

Culture Documents

EE529 Lec3

EE529 Lec3

Uploaded by

dd23015Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

EE529 Lec3

EE529 Lec3

Uploaded by

dd23015Copyright:

Available Formats

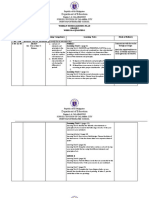

Introduction to VHDL

Dr. Shubhajit Roy Chowdhury,

School of Computing and Electrical Engineering,

Indian Institute of Technology Mandi, India

Email: src@iitmandi.ac.in

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Entities and Architecture

• Entity

– External view: Pin-out description, Interface description, I-

O port definition etc

• Architecture

– Internal view

• Structural description: Gates, wires etc.

• Behavioral description: functions, procedures, RTL

description

4

Din ENTITY mux

Dout

2 ARCHITECTURE

sel

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Ports

• Pass information through the interface which

is time-varying.

• Are signal objects

– connected together by signals

– used to pass values between concurrently active

units.

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Interface Modes

• Represent direction of value flow

• In entities, components, and blocks the

modes may be:

– IN within the design unit (both entity and body) the

value may be read, but not written.

– OUT within the design unit (both entity and body) the

value may be written, but not read.

– INOUT within the design unit (both entity and body) the

value may be both read and written.

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Modeling Interfaces

• Entity declaration

– describes the input/output ports of a module

entity name port names port mode (direction)

entity reg4 is

port ( d0, d1, d2, d3, en, clk : in bit;

q0, q1, q2, q3 : out bit );

end entity reg4; punctuation

reserved words port type

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

VHDL-87

• Omit entity at end of entity declaration

entity reg4 is

port ( d0, d1, d2, d3, en, clk : in bit;

q0, q1, q2, q3 : out bit );

end reg4;

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Format of an Architecture

architecture identifier of entity_identifier is

-- local declarations, typically signals

begin

-- concurrent statements

end identifier ;

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Three Styles of Modeling

• Structural Modeling

• Behavioral Modeling

• Dataflow Modeling

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

The Half Adder Example

entity ha is

port (A, B: in std_logic;

S,C: out std_logic);

end ha;

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Dataflow Modeling

architecture df of ha is

begin

s<=a xor b;

c<=a and b;

end df;

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Behavioral Modeling

architecture behave of ha is

begin

process(a,b)

if (a=’0’)then

c<=’0’;

if(b=’0’)then

s<=’0’;

elsif(b=’1’)then

s<=’1’;

end if;

elsif(a=’1’)then

if(b=’0’)then

s<=’1’;

c<=’0’;

elsif(b=‘1’)then

s<=’1’;

c<=’1’;

end if;

end if;

end behave;

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Structural Modeling

architecture struct of ha is

component AND2 is

port(P,Q:in std_logic;

R:out std_logic);

end component;

component XOR2 is

port(X,Y:in std_logic;

Z:out std_logic);

end component;

begin

X1:XOR2 port map (a,b,s);

A1:AND2 port map (a,b,c);

end struct;

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Mixed Style of Modeling

architecture mixed of ha is

component AND2 is

port(P,Q:in std_logic;

R:out std_logic);

end component;

begin

s<=a xor b;

A1:AND2 port map (a,b,c);

end mixed;

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Modeling Behavior

• Architecture body

– describes an implementation of an entity

– may be several per entity

• Behavioral architecture

– describes the algorithm performed by the module

– contains

• process statements, each containing

• sequential statements, including

• signal assignment statements and

• wait statements

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Behavior Example

architecture behav of reg4 is

begin

storage : process is

variable stored_d0, stored_d1, stored_d2, stored_d3 : bit;

begin

if en = '1' and clk = '1' then

stored_d0 := d0;

stored_d1 := d1;

stored_d2 := d2;

stored_d3 := d3;

end if;

q0 <= stored_d0 after 5 ns;

q1 <= stored_d1 after 5 ns;

q2 <= stored_d2 after 5 ns;

q3 <= stored_d3 after 5 ns;

wait on d0, d1, d2, d3, en, clk;

end process storage;

end architecture behav;

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Modeling Structure

• Structural architecture

– implements the module as a composition of

subsystems

– contains

• signal declarations, for internal interconnections

– the entity ports are also treated as signals

• component instances

– instances of previously declared entity/architecture pairs

• port maps in component instances

– connect signals to component ports

• wait statements

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Structure Example

bit0

d_latch

d0 q0

d q

clk

bit1

d_latch

d1 q1

d q

clk

bit2

d_latch

d2 q2

d q

clk

bit3

d_latch

d3 q3

d q

gate clk

and2

en int_clk

a y

clk

b

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Structure Example

• First declare D-latch and and-gate entities and architectures

entity d_latch is entity and2 is

port ( d, clk : in bit; q : out bit ); port ( a, b : in bit; y : out bit );

end entity d_latch; end entity and2;

architecture basic of d_latch is architecture basic of and2 is

begin begin

latch_behavior : process is and2_behavior : process is

begin begin

if clk = ‘1’ then y <= a and b after 2 ns;

q <= d after 2 ns; wait on a, b;

end if; end process and2_behavior;

wait on clk, d; end architecture basic;

end process latch_behavior;

end architecture basic;

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Structure Example

• Now use them to implement a register

architecture struct of reg4 is

signal int_clk : bit;

begin

bit0 : entity work.d_latch(basic)

port map ( d0, int_clk, q0 );

bit1 : entity work.d_latch(basic)

port map ( d1, int_clk, q1 );

bit2 : entity work.d_latch(basic)

port map ( d2, int_clk, q2 );

bit3 : entity work.d_latch(basic)

port map ( d3, int_clk, q3 );

gate : entity work.and2(basic)

port map ( en, clk, int_clk );

end architecture struct;

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Mixed Behaviour and Structure

• An architecture can contain both behavioral

and structural parts

– process statements and component instances

• collectively called concurrent statements

– processes can read and assign to signals

• Example: register-transfer-level model

– data path described structurally

– control section described behaviorally

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Mixed Example

multiplier multiplicand

shift_reg

control_ shift_

section adder

reg

product

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Mixed Example

entity multiplier is

port ( clk, reset : in bit;

multiplicand, multiplier : in integer;

product : out integer );

end entity multiplier;

architecture mixed of mulitplier is

signal partial_product, full_product : integer;

signal arith_control, result_en, mult_bit, mult_load : bit;

begin

arith_unit : entity work.shift_adder(behavior)

port map ( addend => multiplicand, augend => full_product,

sum => partial_product,

add_control => arith_control );

result : entity work.reg(behavior)

port map ( d => partial_product, q => full_product,

en => result_en, reset => reset );

...

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Mixed Example

…

multiplier_sr : entity work.shift_reg(behavior)

port map ( d => multiplier, q => mult_bit,

load => mult_load, clk => clk );

product <= full_product;

control_section : process is

-- variable declarations for control_section

-- …

begin

-- sequential statements to assign values to control signals

-- …

wait on clk, reset;

end process control_section;

end architecture mixed;

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Delays in Hardware: Inertial

The narrow pulse

vanishes.

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Delays in Hardware: (transport)

The narrow pulse appears in

the output after the delay.

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Concept of Delta Delay

When a signal assignment is made, the target signal does not acquire the

assigned value immediately.

The target value is assigned after a delay. Remembering that a signal is

scheduled to acquire a value after some time is called a transaction.

Thus, when an assignment is made, we imply that the target signal will

acquire this value after so much delay of this type.

Default amount and type of delay is zero, inertial.

Zero delay is implemented as a small delay () which goes to zero in the

limit. This has scheduling implications. Events occuring at t, t+, t+2

are all reported at t, but are time ordered as if is non zero.

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Concurrency

We handle concurrency by using an event driven architecture.

We keep track of time as a separate global variable.

Things which happen at the same time are all handled one after the other, keeping

the time value the same.

We then advance the time to the next event.

Note: The time variable has nothing to do with the time taken by the simulator to

run! It keeps track of the actual time at which multiple things would happen. These

multiple (concurrent) things are handled in an order dictated by scheduling.

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Scheduling policy

We keep a time ordered queue of signals waiting to acquire assigned values. Time is

advanced to the earliest entry in this queue and all the waiting signal assignments

scheduled for this time are made. If a signal value changes, we call it an event.

We keep track of all pieces of hardware which would be affected by this change.

(Typically, all modules to which this signal is an input). The output of each such module

is re-computed and is scheduled to appear at the output signals after appropriate

delays.

These are called transactions and are inserted in the time-ordered queue.

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Scheduling policy

For each event which occurs at a given time

All modules which are “sensitive to” this event are

simulated and their outputs are scheduled to acquire their

re-computed values at appropriate times in the time ordered queue.

This is repeated for each event which occurs at the current time.

When no events are left, we advance the time to the next earliest entry in the time

ordered queue.

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

Thank you

Dr. Shubhajit Roy Chowdhury SCEE, IIT MANDI

You might also like

- Hardware Description Language Demystified: Explore Digital System Design Using Verilog HDL and VLSI Design ToolsFrom EverandHardware Description Language Demystified: Explore Digital System Design Using Verilog HDL and VLSI Design ToolsNo ratings yet

- Introduction To VHDL: Dr. Adnan ShaoutDocument32 pagesIntroduction To VHDL: Dr. Adnan ShaoutBhargav ShahNo ratings yet

- VHDL Quick Start: Peter J. AshendenDocument42 pagesVHDL Quick Start: Peter J. AshendenTom CruseNo ratings yet

- Islamic University of Technology: EEE 4765 Embedded Systems DesignDocument20 pagesIslamic University of Technology: EEE 4765 Embedded Systems DesignAli Sami Ahmad Faqeeh 160021176No ratings yet

- Lecture 6Document20 pagesLecture 6Jawad ChowdhuryNo ratings yet

- CC317-Spring 22-Lec 09Document42 pagesCC317-Spring 22-Lec 09reem mohamedNo ratings yet

- 08 - VHDL IntroductionDocument55 pages08 - VHDL IntroductionMarlofel ParaderoNo ratings yet

- Chapter 5Document32 pagesChapter 5Kiran GunasegaranNo ratings yet

- Sri Venkateswara College of Engineering & Technology R.V.S Nagar, Chittoor M.Tech. I Semester (Decs) Digital System Design Lab List of ExperimentsDocument47 pagesSri Venkateswara College of Engineering & Technology R.V.S Nagar, Chittoor M.Tech. I Semester (Decs) Digital System Design Lab List of ExperimentssubbuNo ratings yet

- VHDL BasicsDocument21 pagesVHDL BasicsPriya PriyaNo ratings yet

- Chapter 3Document29 pagesChapter 3Kiran GunasegaranNo ratings yet

- Very High Speed Integrated Circuits Hardware Description Language) VHDL (Document16 pagesVery High Speed Integrated Circuits Hardware Description Language) VHDL (Ammar AlkindyNo ratings yet

- VHDL IntrosssprDocument176 pagesVHDL Introsssprrampravesh kumarNo ratings yet

- EE8351 Digital Logic Circuits: S.S.Harish Department of EEEDocument33 pagesEE8351 Digital Logic Circuits: S.S.Harish Department of EEEkkr kkrNo ratings yet

- Vlsi Lab PgmsDocument18 pagesVlsi Lab PgmsLavanya ViswanathanNo ratings yet

- Design Language Provide The Means by Which To Describe The Operation of Both Software Program and HardwareDocument53 pagesDesign Language Provide The Means by Which To Describe The Operation of Both Software Program and HardwareshreyaNo ratings yet

- Lec 2 (VHDL Basics)Document38 pagesLec 2 (VHDL Basics)eslam MohamedNo ratings yet

- VHDL Quick Start RLHDocument41 pagesVHDL Quick Start RLHvasanthmahadevNo ratings yet

- Digital Design Using VHDL: Reem Ibrahim, PH.DDocument14 pagesDigital Design Using VHDL: Reem Ibrahim, PH.DZeyad AymanNo ratings yet

- Custom Single Purpose Processor DesignDocument25 pagesCustom Single Purpose Processor DesignMhdNo ratings yet

- VHDLDocument14 pagesVHDLmcbNo ratings yet

- Introduction To VHDL: Prof. David Márquez ViloriaDocument30 pagesIntroduction To VHDL: Prof. David Márquez ViloriaJose Mateo Aristizabal DiazNo ratings yet

- VHDL CodingDocument30 pagesVHDL CodingKamleshNo ratings yet

- Unit2 Basic Structures of VHDLDocument43 pagesUnit2 Basic Structures of VHDLRalph Anthony Constantino PlanterasNo ratings yet

- Unit V VHDL: Entity Entity - Name Declaration Entity - NameDocument12 pagesUnit V VHDL: Entity Entity - Name Declaration Entity - NameAbii BaluuNo ratings yet

- VHDL - Introduction: CP323L1: Advance Logic DesignDocument20 pagesVHDL - Introduction: CP323L1: Advance Logic Designartnetw0rkNo ratings yet

- Unit-1 PPT-Concepts in VHDL NewDocument68 pagesUnit-1 PPT-Concepts in VHDL Newsivneshvenkatesan01No ratings yet

- CS2204 Digital Logic and State Machine Design: VHDL ProgrammingDocument64 pagesCS2204 Digital Logic and State Machine Design: VHDL ProgrammingSatya SagarNo ratings yet

- VHDL ReportDocument29 pagesVHDL ReportSalman AliNo ratings yet

- VHDL Language Reference: Appendix BDocument13 pagesVHDL Language Reference: Appendix Bberal sanghviNo ratings yet

- Digital DesignDocument13 pagesDigital DesignKarim M. AhmedNo ratings yet

- Unit 1 HDL DesignDocument93 pagesUnit 1 HDL DesignSavi AkolkarNo ratings yet

- Computer Aided Design (VHDL) EEC 272 2018 - Lec 23Document227 pagesComputer Aided Design (VHDL) EEC 272 2018 - Lec 23Eslam MuhammedNo ratings yet

- Vhdl1 Introduction To VHDL: (W2 Begins)Document28 pagesVhdl1 Introduction To VHDL: (W2 Begins)Tiga LeungNo ratings yet

- VHDL ppt1Document37 pagesVHDL ppt1mdhuq1No ratings yet

- Register-Transfer Level Design Register-Transfer Level (RTL) Is A Design Abstraction Which Models A Synchronous DigitalDocument11 pagesRegister-Transfer Level Design Register-Transfer Level (RTL) Is A Design Abstraction Which Models A Synchronous Digitalmuru54321No ratings yet

- VHDL Assignment OperatorDocument12 pagesVHDL Assignment Operatorg69xwche100% (1)

- Introduction To Verilog HDL: Presented by K.SwathiDocument35 pagesIntroduction To Verilog HDL: Presented by K.SwathiswathikomatiNo ratings yet

- VHDLDocument108 pagesVHDLRreckless RkNo ratings yet

- Introduction of VHDL: Shomal University Fall 2010Document78 pagesIntroduction of VHDL: Shomal University Fall 2010Roshdy AbdelRassoulNo ratings yet

- Unit-1 PPT-Concepts in VHDLDocument58 pagesUnit-1 PPT-Concepts in VHDLSUMASRI MNo ratings yet

- Introduction To VHDL: by BODDU LokeshDocument22 pagesIntroduction To VHDL: by BODDU LokeshKiran GunasegaranNo ratings yet

- Unit V - VHDL: Very High Speed Harware Description Language (VHDL) VHDL Coding For Arithmetic CircuitsDocument62 pagesUnit V - VHDL: Very High Speed Harware Description Language (VHDL) VHDL Coding For Arithmetic CircuitsmrpoopieNo ratings yet

- VHDL Unit - 1Document10 pagesVHDL Unit - 1hemanthperreddy123No ratings yet

- N-Bit Shift Register PDFDocument232 pagesN-Bit Shift Register PDFAnuradha KhalkhoNo ratings yet

- Dica LabDocument42 pagesDica LabSobha MuraliNo ratings yet

- VHDL Very High Speed Integrated Language: Unit VDocument41 pagesVHDL Very High Speed Integrated Language: Unit VB. MeenakshiNo ratings yet

- VHDL BasicDocument242 pagesVHDL BasicKiran GunasegaranNo ratings yet

- Tutorial 1Document29 pagesTutorial 1A'ziz MoNo ratings yet

- Design Verification Team: Prof. Chung-Yang (Ric) Huang Department of Electrical Engineering National Taiwan UniversityDocument22 pagesDesign Verification Team: Prof. Chung-Yang (Ric) Huang Department of Electrical Engineering National Taiwan UniversityengineeringhandbookNo ratings yet

- Label: FOR Identifier IN Range GENERATE Concurrent - Statements END GENERATE (Label)Document25 pagesLabel: FOR Identifier IN Range GENERATE Concurrent - Statements END GENERATE (Label)Amit SinghNo ratings yet

- ENCS 533 Advanced Digital Design: Introduction To VHDLDocument51 pagesENCS 533 Advanced Digital Design: Introduction To VHDLLalush AbujaishNo ratings yet

- Wa0000.Document35 pagesWa0000.KARTAVYANo ratings yet

- CS2204 Digital Logic and State Machine Design: VHDL ProgrammingDocument64 pagesCS2204 Digital Logic and State Machine Design: VHDL ProgrammingpecamitNo ratings yet

- Expert Systems for Engineering DesignFrom EverandExpert Systems for Engineering DesignMichael RychenerNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- Beginning jOOQ: Learn to Write Efficient and Effective Java-Based SQL Database OperationsFrom EverandBeginning jOOQ: Learn to Write Efficient and Effective Java-Based SQL Database OperationsNo ratings yet

- Multi-Sensor Fusion A PerspectiveDocument7 pagesMulti-Sensor Fusion A Perspectivedd23015No ratings yet

- Lec 3 Rigid Body MotionDocument92 pagesLec 3 Rigid Body Motiondd23015No ratings yet

- Section 4 Forward KinematicsDocument47 pagesSection 4 Forward Kinematicsdd23015No ratings yet

- Class44-46 Introduction To Enncoder-Decoder Model Attention-03-09May2023Document35 pagesClass44-46 Introduction To Enncoder-Decoder Model Attention-03-09May2023dd23015No ratings yet

- Class47 49 - AttentionBasedModels Transformers 10 15may2023Document27 pagesClass47 49 - AttentionBasedModels Transformers 10 15may2023dd23015No ratings yet

- Optimal Decision Fusion in Multiple Sensor SystemsDocument11 pagesOptimal Decision Fusion in Multiple Sensor Systemsdd23015No ratings yet

- City of Makati Vs Nippon ExpressDocument8 pagesCity of Makati Vs Nippon ExpressMarie Mariñas-delos ReyesNo ratings yet

- Pw455r With STTDocument24 pagesPw455r With STTharoub_nasNo ratings yet

- Beldara PPT Buyer 23122019Document14 pagesBeldara PPT Buyer 23122019Kaushik Rozekar-BakshiNo ratings yet

- 06-خطة الإجراءات التصحيحية-Corrective Action PlanDocument11 pages06-خطة الإجراءات التصحيحية-Corrective Action Planحسن ابو فهدNo ratings yet

- Week 6Document16 pagesWeek 6jessa lacandozeNo ratings yet

- Gaoke 3g Lte Cpe Lg6002n 0310Document2 pagesGaoke 3g Lte Cpe Lg6002n 0310glocallNo ratings yet

- 初級1 How to Use This Textbook - 1Document13 pages初級1 How to Use This Textbook - 1Mab UngNo ratings yet

- WHLP - G9 Arts Q1 Week 3&4Document3 pagesWHLP - G9 Arts Q1 Week 3&4Uricca Mari Briones SarmientoNo ratings yet

- Advantages E-Class CoupeDocument44 pagesAdvantages E-Class CoupeNasiri650% (1)

- Ce Nov 19 R17Document18 pagesCe Nov 19 R17Anonymous yO7rcec6vuNo ratings yet

- Law of Contracts IDocument29 pagesLaw of Contracts IAlok BhattNo ratings yet

- Solar Panel Repair BookDocument13 pagesSolar Panel Repair BookShiva PradhanNo ratings yet

- X-Plane Installer LogDocument3 pagesX-Plane Installer LogMarsala NistoNo ratings yet

- Apollo Over The Moon A View From OrbitDocument266 pagesApollo Over The Moon A View From OrbitBob Andrepont100% (3)

- Instruction Manual: MissionDocument93 pagesInstruction Manual: Missionamjad atayaNo ratings yet

- Gamification in Teaching PPT Final N Talaga ItoDocument35 pagesGamification in Teaching PPT Final N Talaga ItoEmerson Delima MonsantoNo ratings yet

- June 2017 (v2) QP - Paper 2 CIE Maths IGCSE PDFDocument12 pagesJune 2017 (v2) QP - Paper 2 CIE Maths IGCSE PDFgrayNo ratings yet

- Fedralism (Prashant Kirad)Document11 pagesFedralism (Prashant Kirad)shrikantmisal17No ratings yet

- Drum HandlingDocument18 pagesDrum Handlinganshu_60No ratings yet

- Java 8 - Functional InterfacesDocument3 pagesJava 8 - Functional InterfacesNahom DiresNo ratings yet

- Drop BoxDocument77 pagesDrop BoxBetty Elizabeth Moreno CarrascoNo ratings yet

- Thesis On Climate Change and Agriculture in IndiaDocument8 pagesThesis On Climate Change and Agriculture in Indiabk4pfxb7100% (1)

- Davidson Et Al-2019-Journal of Applied Behavior AnalysisDocument14 pagesDavidson Et Al-2019-Journal of Applied Behavior Analysisnermal93No ratings yet

- Written Report For Ucsp: Biological and Cultural Evolution: From Australopithecus To Homo SapiensDocument10 pagesWritten Report For Ucsp: Biological and Cultural Evolution: From Australopithecus To Homo SapiensJustin Raton ManingoNo ratings yet

- Asymptomatic HyperuricemiaDocument46 pagesAsymptomatic HyperuricemiaDivya Shree100% (1)

- SCD Define Plant LocationDocument535 pagesSCD Define Plant LocationSantosh YadavNo ratings yet

- TLS and DTLS (Notes Materials) : Mr. S P Maniraj Dr. S Suresh Mr. M PrabuDocument14 pagesTLS and DTLS (Notes Materials) : Mr. S P Maniraj Dr. S Suresh Mr. M PrabuSuresh SNo ratings yet

- Geometry NotesDocument47 pagesGeometry NoteswalczakcNo ratings yet

- Cloud Computing in Distributed System IJERTV1IS10199Document8 pagesCloud Computing in Distributed System IJERTV1IS10199Nebula OriomNo ratings yet

- Manual Spline EQDocument5 pagesManual Spline EQMaricruz CalvoNo ratings yet